S912

Datasheet

Revision: 0.1

Release date: 3/14/2017

Amlogic, Ltd.

1/554

AMLOGIC, Inc. Proprietary

Distribute to Wesion!�

S912 Datasheet

Revision 0.1

COPYRIGHT

© 2016 Amlogic, Ltd.

All rights reserved. No part of this document may be reproduced. Transmitted, transcribed, or translated into any language in

any form or by any means with the written permission of Amlogic, Ltd.

TRADEMARKS

AMLOGIC is a trademark of Amlogic, Ltd. All other trademarks and registered trademarks are property of their respective

companies.

DISCLAIMER

Amlogic Ltd. may make improvements and/or changes in this document or in the product described in this document at any

time.

This product is not intended for use in medical, life saving, or life sustaining applications.

Circuit diagrams and other information relating to products of Amlogic Ltd. are included as a means or illustrating typical

applications. Consequently, complete information sufficient for production design is not necessarily given. Amlogic makes no

representations or warranties with respect to the accuracy or completeness of the contents presented in this document.

REVISION HISTORY

Revision Date

Changes

Revision

Number

0.1

0.2

2016/10/26

2017/3/14

Initial version release

Add register RESET0_MASK~RESET7_MASK, change RESET0_LEVEL ~RESET7_LEVEL

address to 0xc11004480~ 0xc1100449c

CONTACT INFORMATION

Amlogic, Shanghai, Ltd.

2518 Mission College Blvd, Suite 120

Santa Clara, CA 95054

U.S.A.

www.amlogic.com

2/554

AMLOGIC, Ltd. Proprietary

Distribute to Wesion!�

S912 Datasheet

Revision 0.1

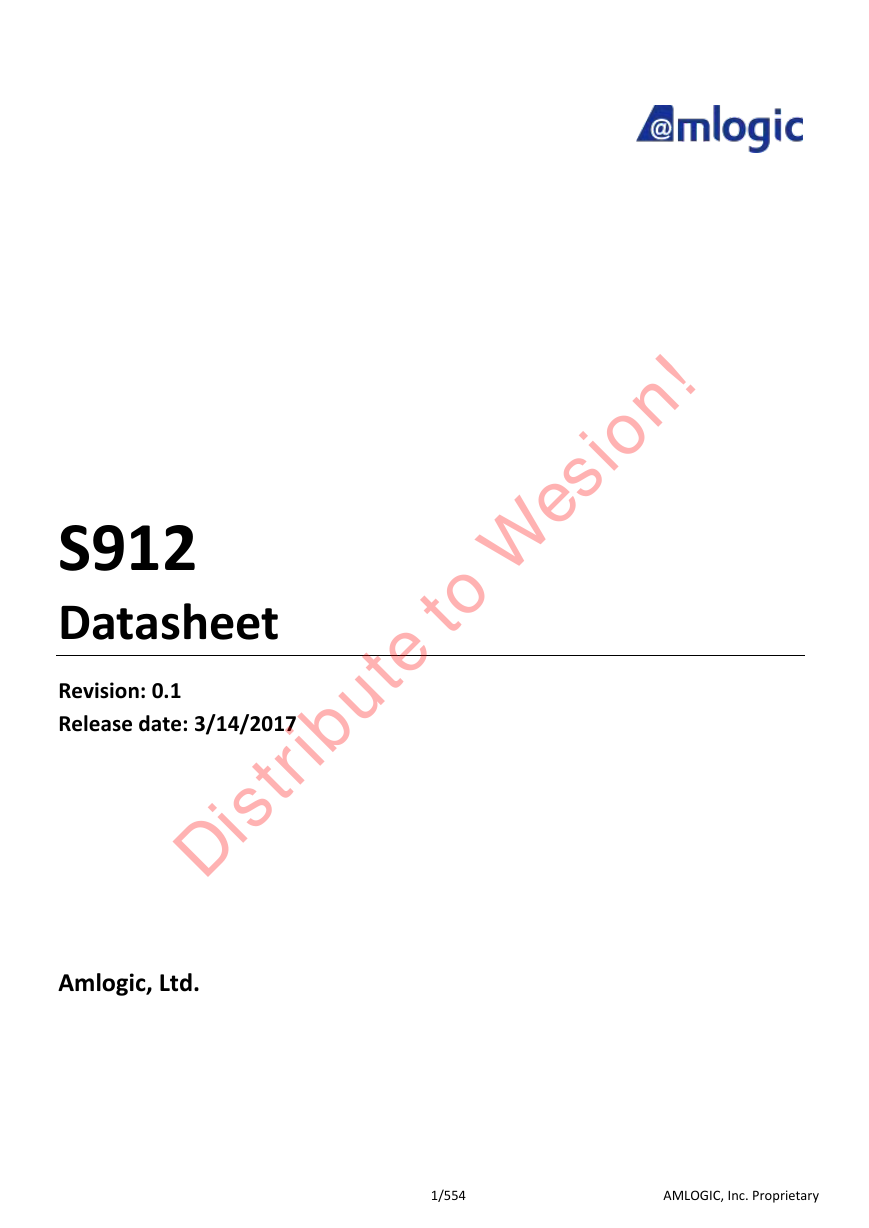

Contents

Section I About This Documentation ........................................................................................................................ 8

1. Documentation Overview .................................................................................................................................. 8

2. Acronyms and Abbreviations ............................................................................................................................. 9

Section II

General Information ............................................................................................................................. 10

3. Features ........................................................................................................................................................... 11

3.1

CPU Architecture ...................................................................................................................................... 11

3.2 GPU Architecture ...................................................................................................................................... 11

3.3

Crypto Engine ........................................................................................................................................... 11

3.4 Video Path ................................................................................................................................................ 11

3.5 Audio Path ................................................................................................................................................ 12

3.6 Memory .................................................................................................................................................... 12

3.7 Digital Television Interface ....................................................................................................................... 12

3.8

I/O Interfaces ............................................................................................................................................ 12

3.9

System Interface ....................................................................................................................................... 12

3.10

Power Management ............................................................................................................................. 12

3.11

Security ................................................................................................................................................. 13

4. System Block Diagram ..................................................................................................................................... 14

5. Pin-Out Diagram (Top view) ......................................................................................................................... 15

6. Pin Description ................................................................................................................................................. 16

7. Pin Multiplexing ............................................................................................................................................... 27

8. Signal Description ............................................................................................................................................ 31

9. Absolute Maximum Ratings ............................................................................................................................. 37

10.

Recommended Operating Conditions .......................................................................................................... 38

11.

Thermal Operating Specifications ................................................................................................................ 39

12. DC Electrical Characteristics ......................................................................................................................... 40

12.1

Normal GPIO Specifications .................................................................................................................. 40

12.2

Open Drain GPIO Specifications ............................................................................................................ 40

12.3

DDR3/DDR3L/DDR4/LPDDR2/LPDDR3 SDRAM Specifications ............................................................ 40

12.4

Recommended Oscillator Electrical Characteristics ............................................................................. 41

13.

Recommended Power on sequence ............................................................................................................ 43

14.

Power Consumption ..................................................................................................................................... 44

15. Mechanical Dimension ................................................................................................................................. 45

Section III

System ................................................................................................................................................... 47

3/554

AMLOGIC, Ltd. Proprietary

Distribute to Wesion!�

S912 Datasheet

Revision 0.1

16. Memory Map ............................................................................................................................................... 48

17.

Power Domain .............................................................................................................................................. 51

17.1

Top 1Level Power Domains .................................................................................................................. 52

17.2

A53 Power Modes ................................................................................................................................. 52

17.3

EE Top Level Power Modes ................................................................................................................... 53

17.4 Mali Power Modes ................................................................................................................................ 53

17.5

Power/Isolation/Memory Power Down Register Summary ................................................................. 54

18.

System Booting ............................................................................................................................................ 57

18.1

Overview ............................................................................................................................................... 57

18.2

Power-on Flow Chart ............................................................................................................................ 57

19.

CPU ............................................................................................................................................................... 58

19.1

Overview ............................................................................................................................................... 58

20. GPU .............................................................................................................................................................. 59

21.

Clock and Reset ............................................................................................................................................ 60

21.1

Overview ............................................................................................................................................... 60

21.2

Clock Trees ............................................................................................................................................ 60

21.3

Clock Gating .......................................................................................................................................... 66

21.4

Register Description .............................................................................................................................. 70

22. GPIO ............................................................................................................................................................. 96

22.1

Overview ............................................................................................................................................... 96

22.2

GPIO Multiplex Function ....................................................................................................................... 96

22.3

GPIO Interrupt .................................................................................................................................... 101

22.4

Register Description ............................................................................................................................ 102

23.

Interrupt Control ........................................................................................................................................ 105

23.1

Overview ............................................................................................................................................. 105

23.2

Interrupt Source .................................................................................................................................. 105

23.3

Register Description ............................................................................................................................ 109

24.

TIMER ......................................................................................................................................................... 111

24.1

Overview ............................................................................................................................................. 111

24.2

General-Purpose Timer ....................................................................................................................... 111

24.3 Watchdog Timer ................................................................................................................................. 111

24.4

Register Definitions ............................................................................................................................. 112

25.

Crypto ......................................................................................................................................................... 117

25.1

Overview ............................................................................................................................................. 117

4/554

AMLOGIC, Ltd. Proprietary

Distribute to Wesion!�

S912 Datasheet

Revision 0.1

25.2

Key Ladder .......................................................................................................................................... 117

25.3

RNG ..................................................................................................................................................... 117

25.4

EFUSE .................................................................................................................................................. 117

Section IV

Video Path ........................................................................................................................................... 118

26.

Video Input ................................................................................................................................................. 119

26.1

Overview ............................................................................................................................................. 119

26.2

Demux ................................................................................................................................................. 119

26.3

Register Definition .............................................................................................................................. 119

27.

Video Output .............................................................................................................................................. 133

27.1

Overview ............................................................................................................................................. 133

27.2

VPU ..................................................................................................................................................... 133

27.3

RDMA .................................................................................................................................................. 342

27.4

HDMI ................................................................................................................................................... 349

27.5

CVBS and LCD ...................................................................................................................................... 357

Section V

Audio Path .......................................................................................................................................... 401

28. Audio_Input ............................................................................................................................................... 402

28.1

Overview ............................................................................................................................................. 402

28.2

SPDIF ................................................................................................................................................... 402

28.3

I2S(decode) ......................................................................................................................................... 402

28.4

PCM(decode) ...................................................................................................................................... 403

28.5

PDM .................................................................................................................................................... 404

28.6

To_ddr ................................................................................................................................................. 404

28.7

Register Description ............................................................................................................................ 406

29. Audio Output .............................................................................................................................................. 420

29.1

Overview ............................................................................................................................................. 420

29.2

SPDIF(encode) ..................................................................................................................................... 420

29.3

I2S(encode) ......................................................................................................................................... 421

29.4

Audio Codec ........................................................................................................................................ 423

29.5

Register Description ............................................................................................................................ 423

Section VI Memory INTERFACE ............................................................................................................................ 442

30. DDR ............................................................................................................................................................ 443

30.1

Overview ............................................................................................................................................. 443

30.2

Register Description ............................................................................................................................ 443

31. NAND .......................................................................................................................................................... 488

5/554

AMLOGIC, Ltd. Proprietary

Distribute to Wesion!�

S912 Datasheet

Revision 0.1

31.1

Overview ............................................................................................................................................. 488

31.2

Register Definitions ............................................................................................................................. 488

32.

eMMC/SD/SDIO ......................................................................................................................................... 492

32.1

Overview ............................................................................................................................................. 492

32.2

Pin Description .................................................................................................................................... 492

32.3

eMMC/SD Mode ................................................................................................................................. 492

32.4

Clock .................................................................................................................................................... 493

32.5

Descriptor ........................................................................................................................................... 493

32.6

Timing Specification ............................................................................................................................ 495

32.7

Register Definitions ............................................................................................................................. 497

33.

SERIAL PERIPHERAL INTERFACE COMMUNICATION CONTROLLER............................................................ 502

33.1

Overview ............................................................................................................................................. 502

33.2

Features .............................................................................................................................................. 502

33.3

Functional Description ........................................................................................................................ 502

33.4

Timing Specification ............................................................................................................................ 503

33.5

Register Description ............................................................................................................................ 504

34.

SERIAL PERIPHERAL INTERFACE FLASH CONTROLLER ................................................................................ 507

34.1

Overview ............................................................................................................................................. 507

34.2

Features .............................................................................................................................................. 507

34.3

Timing Specification ............................................................................................................................ 507

34.4

Register Description ............................................................................................................................ 508

Section VII

I/O Interface ........................................................................................................................................ 516

35. UNIVERSAL SERIAL BUS .............................................................................................................................. 517

35.1

Overview ............................................................................................................................................. 517

35.2

Features .............................................................................................................................................. 517

36.

ETHERNET MAC .......................................................................................................................................... 518

36.1

Overview ............................................................................................................................................. 518

36.2

Features .............................................................................................................................................. 518

36.3

Timing Specification ............................................................................................................................ 519

36.4

Register Description ............................................................................................................................ 521

37.

SDIO ............................................................................................................................................................ 523

38.

INTER-INTEGRATED CIRCUIT (I2C) .............................................................................................................. 524

38.1

Overview ............................................................................................................................................. 524

38.2

Features .............................................................................................................................................. 524

6/554

AMLOGIC, Ltd. Proprietary

Distribute to Wesion!�

S912 Datasheet

Revision 0.1

38.3

Timing Specification ............................................................................................................................ 524

38.4

Register Description ............................................................................................................................ 525

39. UNIVERSAL ASYNCHRONOUS RECEIVER AND TRANSMITTER .................................................................... 528

39.1

Overview ............................................................................................................................................. 528

39.2

Features .............................................................................................................................................. 528

39.3

Functional Description ........................................................................................................................ 528

39.4

Register Description ............................................................................................................................ 529

40.

INFRARED REMOTE .................................................................................................................................... 532

40.1

Overview ............................................................................................................................................. 532

40.2

Decoder Functional Description ......................................................................................................... 532

40.3

NEC Infrared Transmission Protocol Example .................................................................................... 533

40.4

IR RC Output ....................................................................................................................................... 534

40.5

Register Description ............................................................................................................................ 535

41.

PULSE-WIDTH MODULATION ..................................................................................................................... 542

41.1

Overview ............................................................................................................................................. 542

41.2

Register Description ............................................................................................................................ 543

42.

SAR ADC ..................................................................................................................................................... 546

42.1

Overview ............................................................................................................................................. 546

42.2

Register Description ............................................................................................................................ 546

Section VIII

System Interface ............................................................................................................................. 551

43.

JTAG............................................................................................................................................................ 551

43.1

Overview ............................................................................................................................................. 551

43.2

Register Definition .............................................................................................................................. 551

44.

Temp Sensor............................................................................................................................................... 552

44.1

Overview ............................................................................................................................................. 552

44.2

Trimming ............................................................................................................................................. 552

44.3

Register Definition .............................................................................................................................. 553

7/554

AMLOGIC, Ltd. Proprietary

Distribute to Wesion!�

S912 Datasheet

Revision 0.1

Section I About This Documentation

1. Documentation Overview

This documentation is an overall Description of Amlogic advanced quad-core OTT/IP Set Top Box(STB) application processor

S912, providing programmers instructions from the following aspects: system, video path, audio path, memory interfaces, I/O

interfaces and system interfaces.

8/554

AMLOGIC, Ltd. Proprietary

Distribute to Wesion!�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc