LogiCORE™ IP

Endpoint Block Plus v1.6

for PCI Express®

用户指南

UG341 2008 年 3 月 24 日

R

�

R

Xilinx is disclosing this Specification to you solely for use in the development of designs to operate on Xilinx FPGAs. Except as stated

herein, none of the Specification may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in

any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior

written consent of Xilinx. Any unauthorized use of this Specification may violate copyright laws, trademark laws, the laws of privacy and

publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Specification; nor does Xilinx convey any license under its

patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of

the Specification. Xilinx reserves the right to make changes, at any time, to the Specification as deemed desirable in the sole discretion of

Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not

assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection

with the Specification.

THE SPECIFICATION IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION

IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR

ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER

EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE SPECIFICATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY,

FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES,

INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE SPECIFICATION, EVEN IF

YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN

CONNECTION WITH YOUR USE OF THE SPECIFICATION, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT

EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE SPECIFICATION. YOU ACKNOWLEDGE

THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT

MAKE AVAILABLE THE SPECIFICATION TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Specification is not designed or intended for use in the development of on-line control equipment in hazardous environments

requiring fail-safe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control,

life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for

such High-Risk Applications. You represent that use of the Specification in such High-Risk Applications is fully at your risk.

© 2006- 2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx,

Inc. All other trademarks are the property of their respective owners.

修订历史

下表所示为本技术文档的修订历史。

日期

版本

修订

2006 年

10 月 23 日

2007 年

2 月 15 日

2007 年

5 月 17 日

2007 年

8 月 8 日

2007 年

10 月 10 日

2008 年

3 月 24 日

1.1

2.0

3.0

4.0

5.0

6.0

Xilinx 最初版本。

核更新到版本 1.2 ; Xilinx 工具 9.1i。

核更新到版本 1.3,以符合 PCI-SIG。

核更新到版本 1.4 ; Xilinx 工具 9.1i,Cadence IUS v5.8。

核更新到版本 1.5 ; Cadence IUS 更新到 v6.1。

核更新到版本 1.6 ; Xilinx 工具 10.1。

www.xilinx.com/cn

Endpoint Block Plus v1.6 for PCI Express 用户指南

UG341 2008 年 3 月 24 日

�

目录

前言 : 关于本指南

目录 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

惯例 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

排版 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

联机技术文档 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

第 1 章 : 简介

关于核. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

使用 RocketIO 收发器的设计 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

推荐的设计经验. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

附加核资源. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

技术支持. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

反馈 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

核 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

技术文档 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

第 2 章 : 核概述

概述 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

协议层 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

PCI 配置空间 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

核接口 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

事务接口 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

配置接口 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

报错信号 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

第 3 章 : 生成和定制核

使用 CORE Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

基本参数设置. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

组件名称 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

参考时钟频率 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

通道数 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

接口频率 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

ID 初始值 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

类代码 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Cardbus CIS 指针 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

基址寄存器. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

基址寄存器概述 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

管理基址寄存器设置 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

配置寄存器设计. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

功能寄存器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

MSI 控制寄存器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

器件功能寄存器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

链路功能寄存器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

时隙时钟配置 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

高级设置. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

事务层模块 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

高级流量控制信用 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

高级物理层 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Endpoint Block Plus v1.6 for PCI Express 用户指南

UG341 2008 年 3 月 24 日

www.xilinx.com/cn

�

电源管理寄存器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

功率消耗 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

功率损耗 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

第 4 章 : 用核设计器件

事务接口上的 TLP 格式 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

传送出站数据包 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

接收入站数据包 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

有关接收事务接口的性能考虑事项 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

访问配置空间寄存器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

其他数据包处理要求 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

报告用户错误情况 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

电源管理 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

生成中断请求 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

链路培训:四通道和八通道端点. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

上游合作伙伴支持的通道较少 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

通道出现故障 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Block Plus 核的时钟控制和复位 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

复位 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

时钟控制 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

第 5 章 : 核的约束

用户约束文件的内容. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

元件选择约束:器件、封装和速度等级 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

用户时序约束 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

用户物理约束 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

核的管脚和 I/O 约束 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

核的物理约束 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

核的时序约束 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

需要的修改. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

器件选择. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

核的 I/O 分配 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

核的物理约束. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

核的时序约束. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Endpoint Block Plus 核重定位 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

支持的核管脚. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

附录 A: 程控输入输出示例设计

系统概述. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

PIO 硬件. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

基址寄存器支持 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

TLP 数据流 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

PIO 文件结构 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

PIO 应用 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

接收通路 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

发射通路 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Endpoint 存储器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

PIO 操作. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

www.xilinx.com/cn

Endpoint Block Plus v1.6 for PCI Express 用户指南

UG341 2008 年 3 月 24 日

�

PIO 读事务 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

PIO 写事务 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

器件资源占用率 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

提要 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

附录 B: 下行端口模型测试平台

架构 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

对设计进行仿真. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

测试选择. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

VHDL 测试选择 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Verilog 测试选择 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

波形转储. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

VHDL 流 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Verilog 流 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

输出记录. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

并行测试程序. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

测试说明. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

测试程序: pio_writeReadBack_test0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

扩展下行端口模型. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

下行端口模型 TPI 任务列表 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

附录 C: 移植考虑事项

事务接口. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

配置接口. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

系统和 PCI Express 接口. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

配置空间. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Endpoint Block Plus v1.6 for PCI Express 用户指南

UG341 2008 年 3 月 24 日

www.xilinx.com/cn

�

www.xilinx.com/cn

Endpoint Block Plus v1.6 for PCI Express 用户指南

UG341 2008 年 3 月 24 日

�

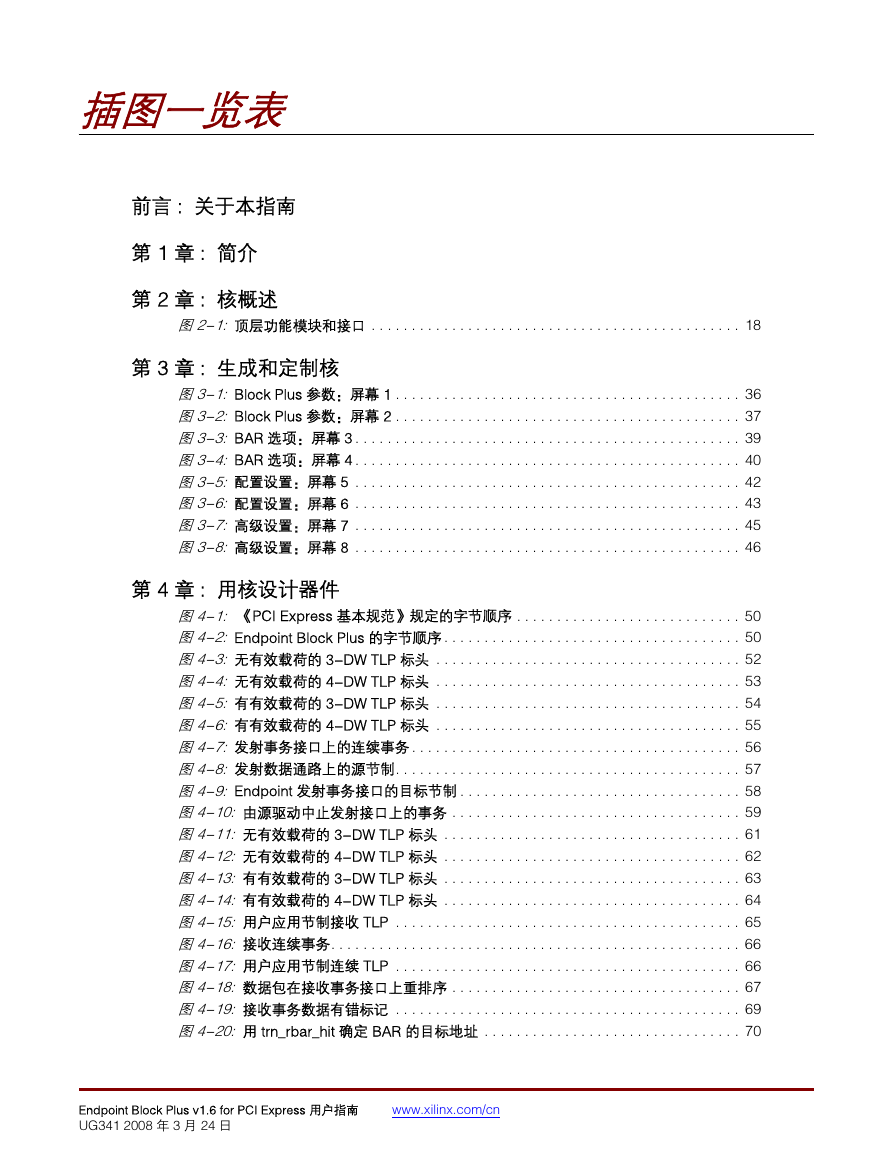

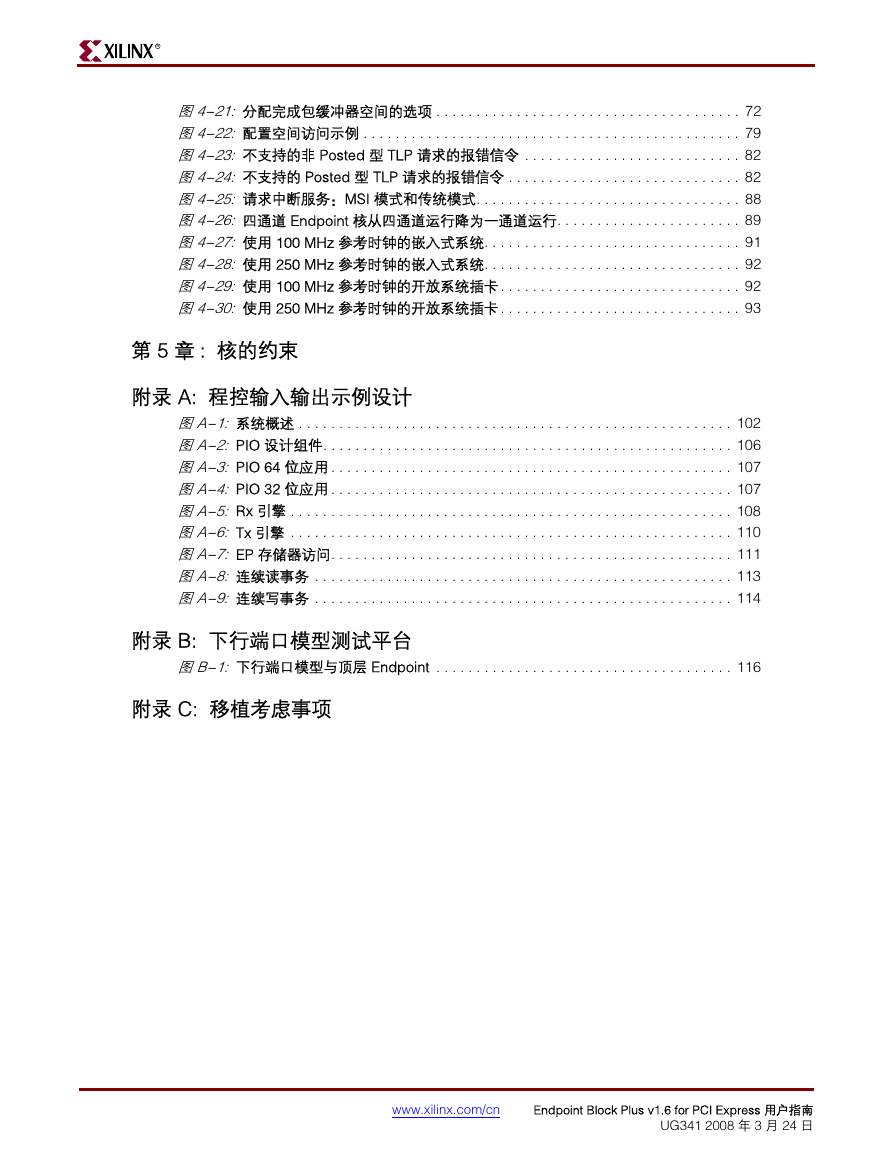

插图一览表

前言 : 关于本指南

第 1 章 : 简介

第 2 章 : 核概述

图 2-1: 顶层功能模块和接口 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

第 3 章 : 生成和定制核

图 3-1: Block Plus 参数:屏幕 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

图 3-2: Block Plus 参数:屏幕 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

图 3-3: BAR 选项:屏幕 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

图 3-4: BAR 选项:屏幕 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

图 3-5: 配置设置:屏幕 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

图 3-6: 配置设置:屏幕 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

图 3-7: 高级设置:屏幕 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

图 3-8: 高级设置:屏幕 8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

第 4 章 : 用核设计器件

图 4-1: 《PCI Express 基本规范》规定的字节顺序 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

图 4-2: Endpoint Block Plus 的字节顺序 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

图 4-3: 无有效载荷的 3-DW TLP 标头 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

图 4-4: 无有效载荷的 4-DW TLP 标头 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

图 4-5: 有有效载荷的 3-DW TLP 标头 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

图 4-6: 有有效载荷的 4-DW TLP 标头 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

图 4-7: 发射事务接口上的连续事务 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

图 4-8: 发射数据通路上的源节制. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

图 4-9: Endpoint 发射事务接口的目标节制 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

图 4-10: 由源驱动中止发射接口上的事务 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

图 4-11: 无有效载荷的 3-DW TLP 标头 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

图 4-12: 无有效载荷的 4-DW TLP 标头 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

图 4-13: 有有效载荷的 3-DW TLP 标头 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

图 4-14: 有有效载荷的 4-DW TLP 标头 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

图 4-15: 用户应用节制接收 TLP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

图 4-16: 接收连续事务. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

图 4-17: 用户应用节制连续 TLP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

图 4-18: 数据包在接收事务接口上重排序 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

图 4-19: 接收事务数据有错标记 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

图 4-20: 用 trn_rbar_hit 确定 BAR 的目标地址 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Endpoint Block Plus v1.6 for PCI Express 用户指南

UG341 2008 年 3 月 24 日

www.xilinx.com/cn

�

R

图 4-21: 分配完成包缓冲器空间的选项 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

图 4-22: 配置空间访问示例 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

图 4-23: 不支持的非 Posted 型 TLP 请求的报错信令 . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

图 4-24: 不支持的 Posted 型 TLP 请求的报错信令 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

图 4-25: 请求中断服务:MSI 模式和传统模式. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

图 4-26: 四通道 Endpoint 核从四通道运行降为一通道运行. . . . . . . . . . . . . . . . . . . . . . . 89

图 4-27: 使用 100 MHz 参考时钟的嵌入式系统. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

图 4-28: 使用 250 MHz 参考时钟的嵌入式系统. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

图 4-29: 使用 100 MHz 参考时钟的开放系统插卡 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

图 4-30: 使用 250 MHz 参考时钟的开放系统插卡 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

第 5 章 : 核的约束

附录 A: 程控输入输出示例设计

图 A-1: 系统概述 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

图 A-2: PIO 设计组件. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

图 A-3: PIO 64 位应用 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

图 A-4: PIO 32 位应用 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

图 A-5: Rx 引擎 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

图 A-6: Tx 引擎 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

图 A-7: EP 存储器访问. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

图 A-8: 连续读事务 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

图 A-9: 连续写事务 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

附录 B: 下行端口模型测试平台

图 B-1: 下行端口模型与顶层 Endpoint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

附录 C: 移植考虑事项

www.xilinx.com/cn

Endpoint Block Plus v1.6 for PCI Express 用户指南

UG341 2008 年 3 月 24 日

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc