拔河游戏机

一、 设计任务与要求

拔河游戏机用 9 个灯泡指示灯排列成一行,开机后只有中间一个点亮,

以此作为拔河的中心线,游戏双方各持一个按键,迅速地、不断地按动产

生脉冲,谁按得快,亮点向谁方向移动,不断地按,亮点不断地移动。移

到任一方终端指示灯点亮,这一方就得胜,此时双方按键均无作用,输出

保持,只有经复位后才使亮点恢复到中心线。

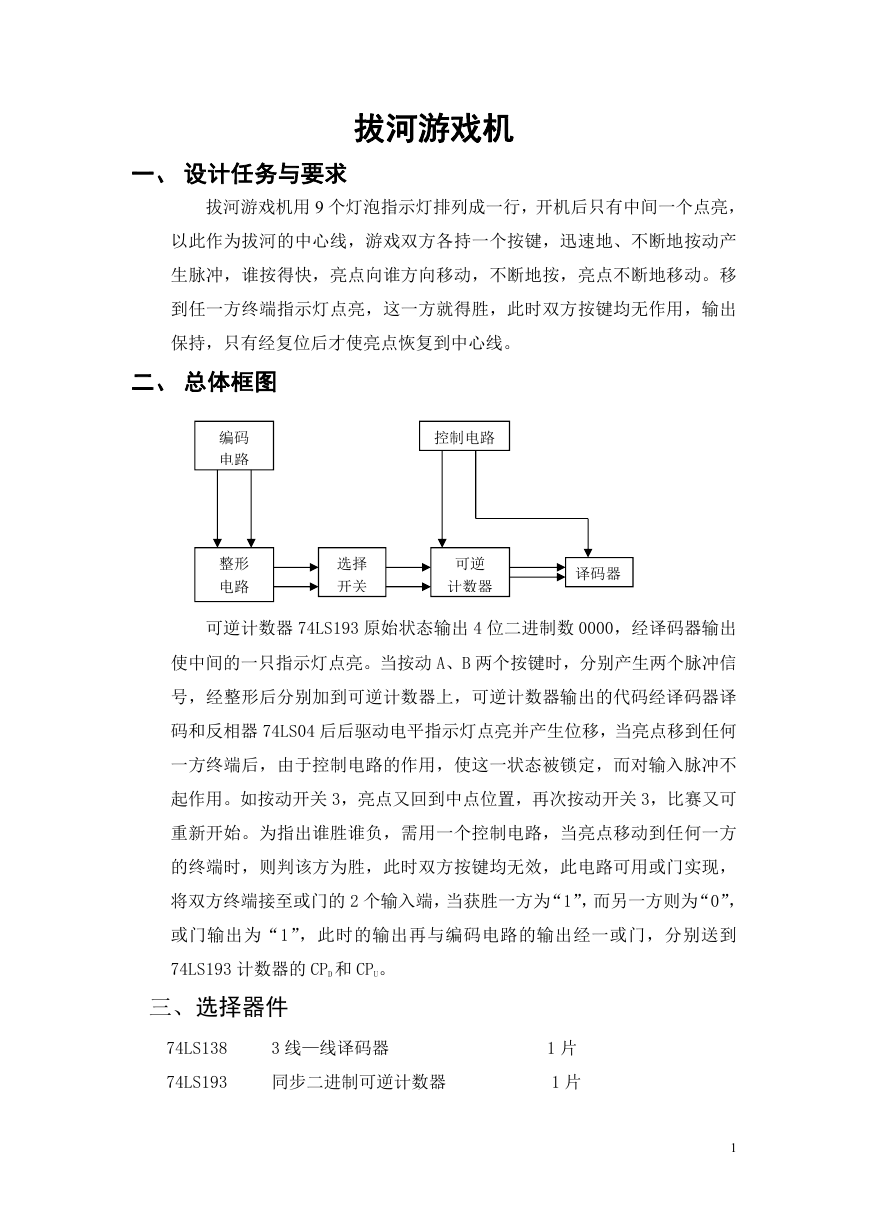

二、 总体框图

编码

电路

整形

电路

控制电路

选择

开关

可逆

计数器

译码器

可逆计数器 74LS193 原始状态输出 4 位二进制数 0000,经译码器输出

使中间的一只指示灯点亮。当按动 A、B 两个按键时,分别产生两个脉冲信

号,经整形后分别加到可逆计数器上,可逆计数器输出的代码经译码器译

码和反相器 74LS04 后后驱动电平指示灯点亮并产生位移,当亮点移到任何

一方终端后,由于控制电路的作用,使这一状态被锁定,而对输入脉冲不

起作用。如按动开关 3,亮点又回到中点位置,再次按动开关 3,比赛又可

重新开始。为指出谁胜谁负,需用一个控制电路,当亮点移动到任何一方

的终端时,则判该方为胜,此时双方按键均无效,此电路可用或门实现,

将双方终端接至或门的 2 个输入端,当获胜一方为“1”,而另一方则为“0”,

或门输出为“1”,此时的输出再与编码电路的输出经一或门,分别送到

74LS193 计数器的 CPD 和 CPU。

三、选择器件

74LS138

3 线—线译码器

74LS193

同步二进制可逆计数器

1 片

1 片

1

�

74LS00

74LS04

74LS08

74LS32

电阻

四 2 输入与非门

六反向器

四 2 输入与门

四 2 输入或门

1 KΩ

100Ω

开关

单刀双掷开关

单刀单掷开关

下面详细介绍这些器件

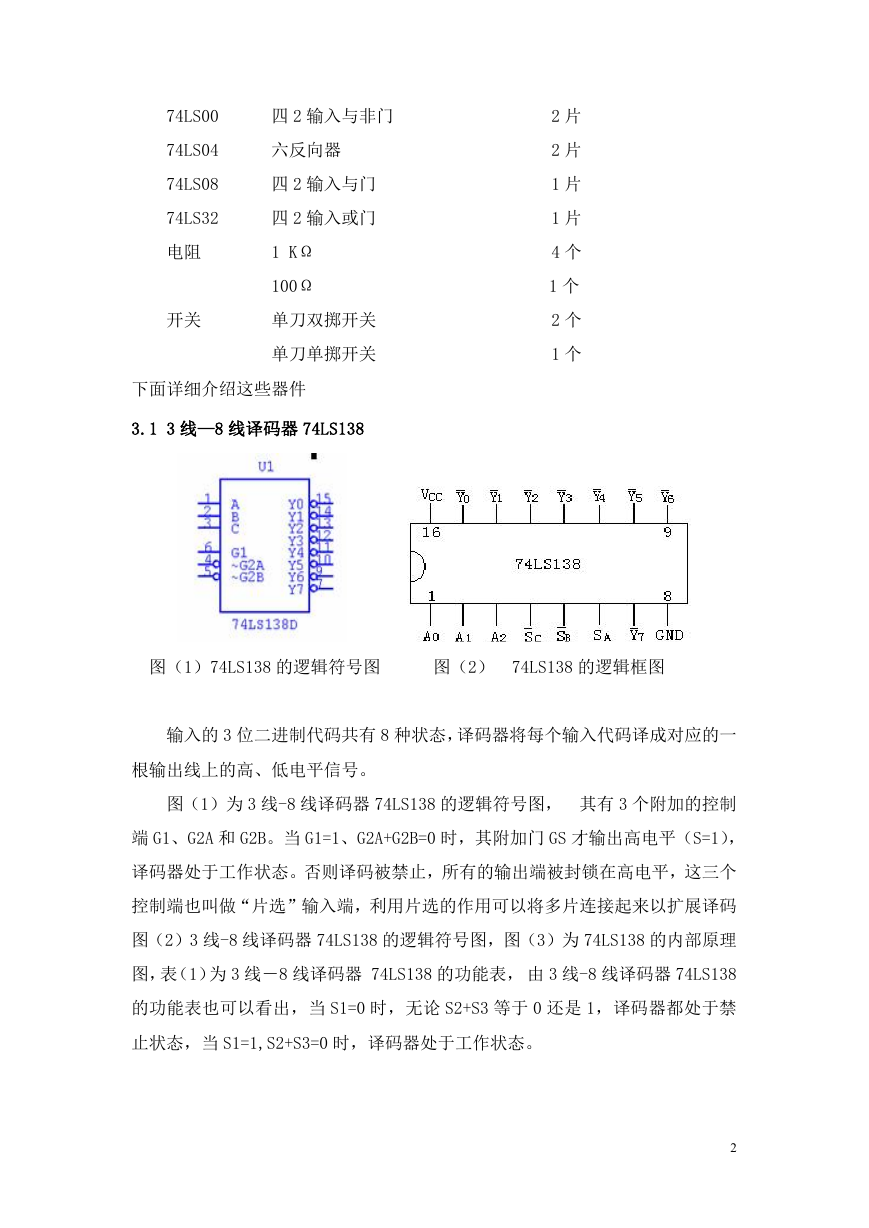

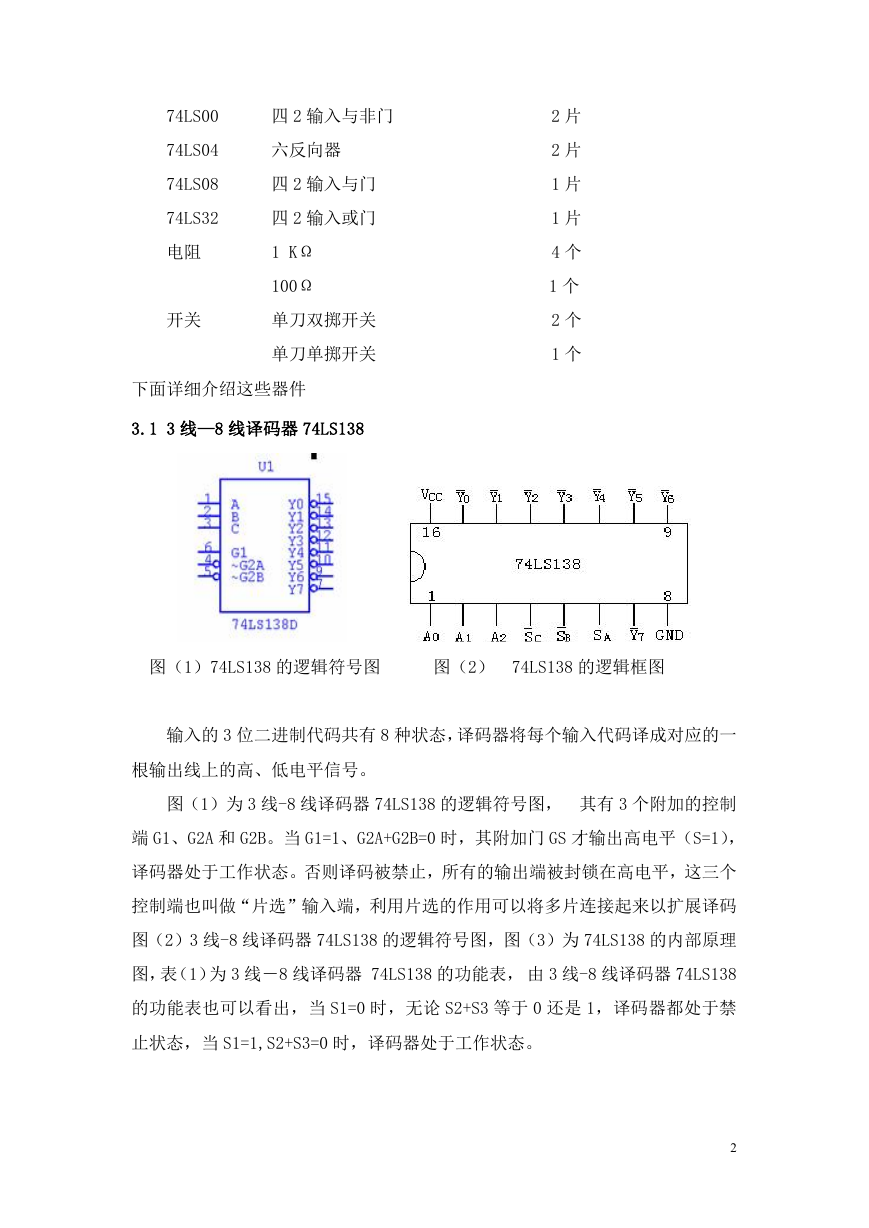

3.1 3 线—8 线译码器 74LS138

2 片

2 片

1 片

1 片

4 个

1 个

2 个

1 个

图(1)74LS138 的逻辑符号图

图(2) 74LS138 的逻辑框图

输入的 3 位二进制代码共有 8 种状态,译码器将每个输入代码译成对应的一

根输出线上的高、低电平信号。

图(1)为 3 线-8 线译码器 74LS138 的逻辑符号图, 其有 3 个附加的控制

端 G1、G2A 和 G2B。当 G1=1、G2A+G2B=0 时,其附加门 GS 才输出高电平(S=1),

译码器处于工作状态。否则译码被禁止,所有的输出端被封锁在高电平,这三个

控制端也叫做“片选”输入端,利用片选的作用可以将多片连接起来以扩展译码

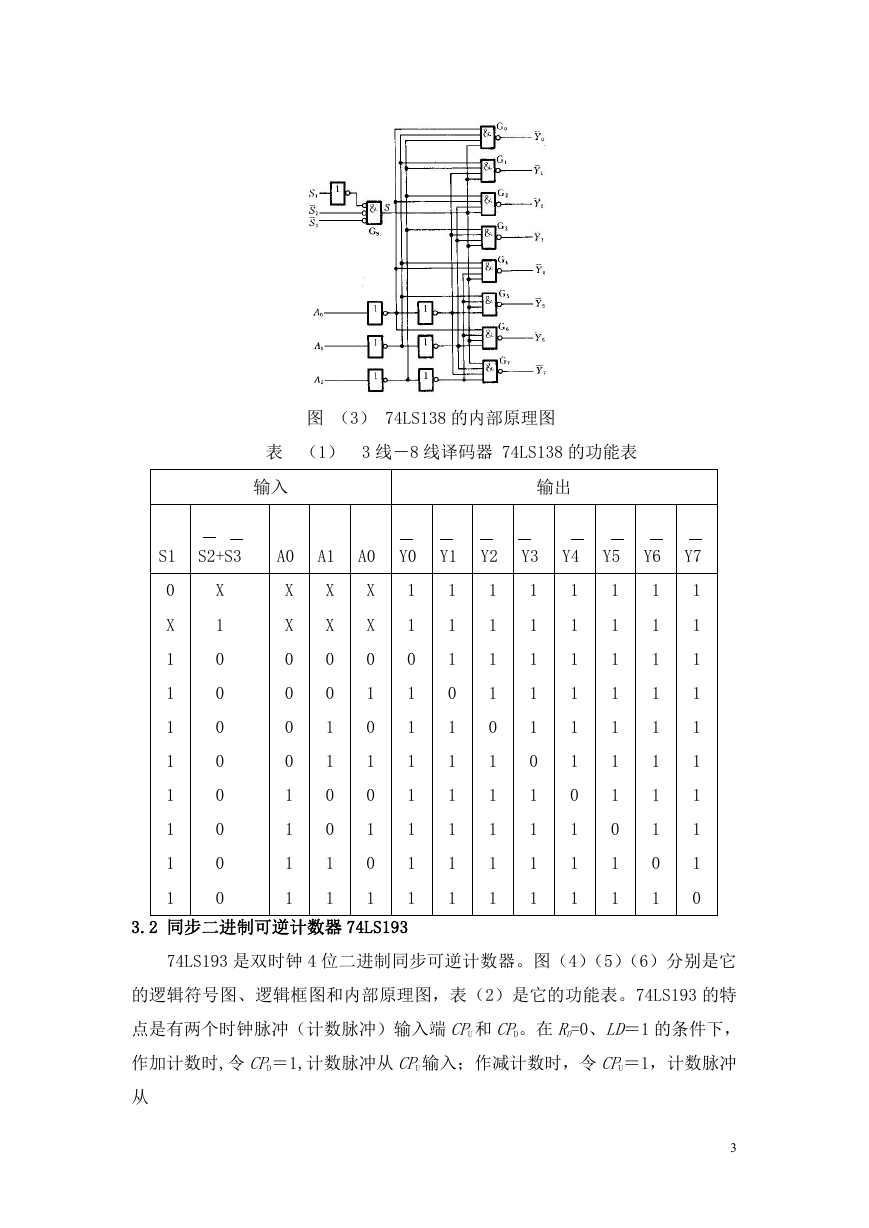

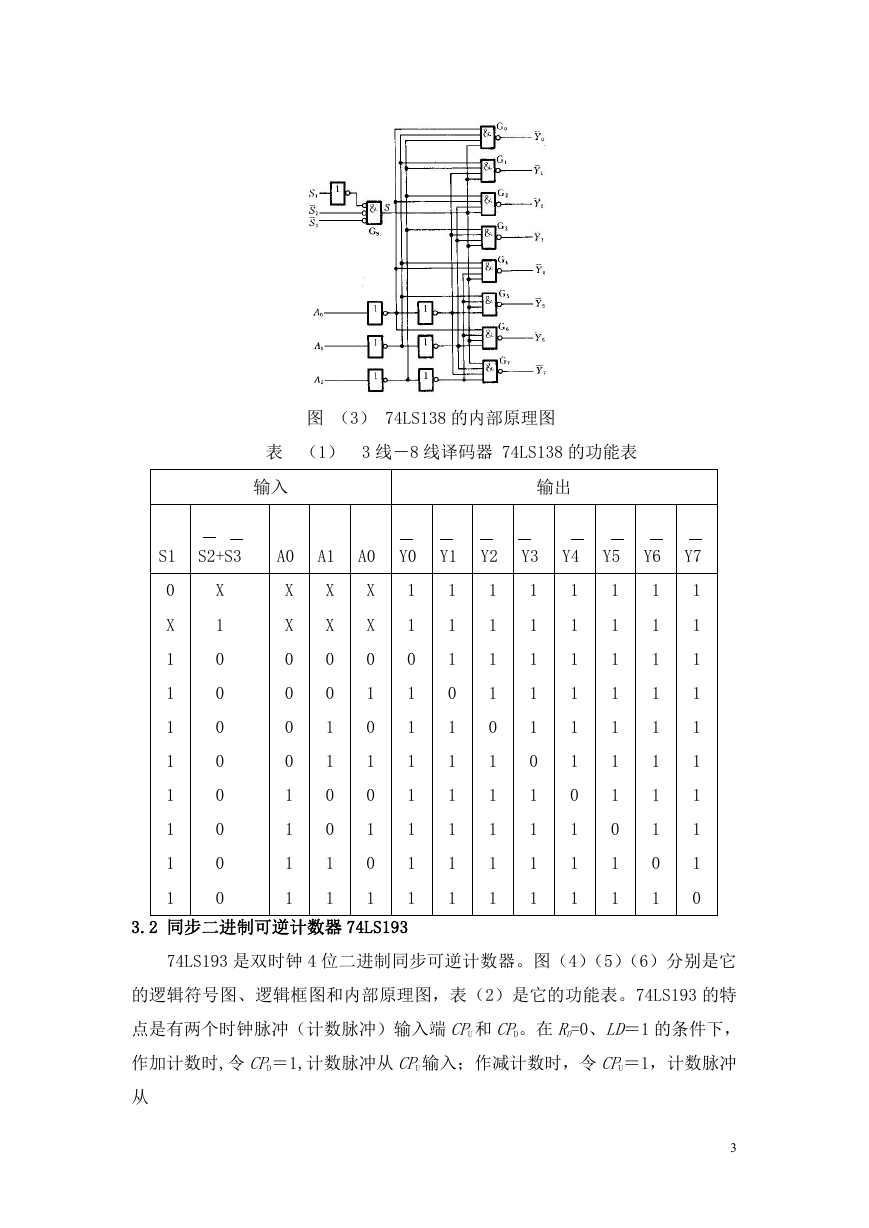

图(2)3 线-8 线译码器 74LS138 的逻辑符号图,图(3)为 74LS138 的内部原理

图,表(1)为 3 线-8 线译码器 74LS138 的功能表, 由 3 线-8 线译码器 74LS138

的功能表也可以看出,当 S1=0 时,无论 S2+S3 等于 0 还是 1,译码器都处于禁

止状态,当 S1=1,S2+S3=0 时,译码器处于工作状态。

2

�

图 (3) 74LS138 的内部原理图

表 (1) 3 线-8 线译码器 74LS138 的功能表

输入

输出

S1

S2+S3

A0

A1

A0

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

0

X

1

1

1

1

1

1

1

1

X

1

0

0

0

0

0

0

0

0

X

X

0

0

0

0

1

1

1

1

X

X

0

0

1

1

0

0

1

1

X

X

0

1

0

1

0

1

0

1

1

1

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

0

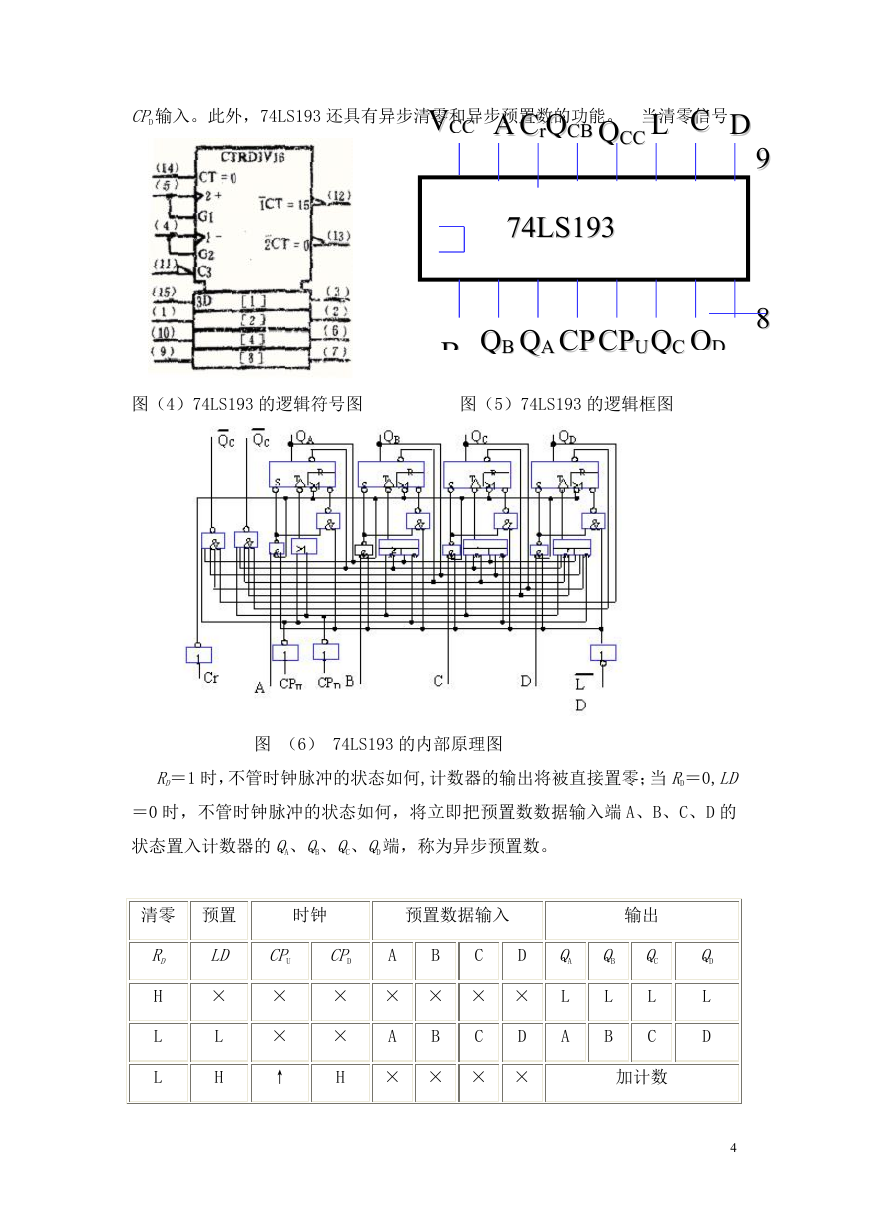

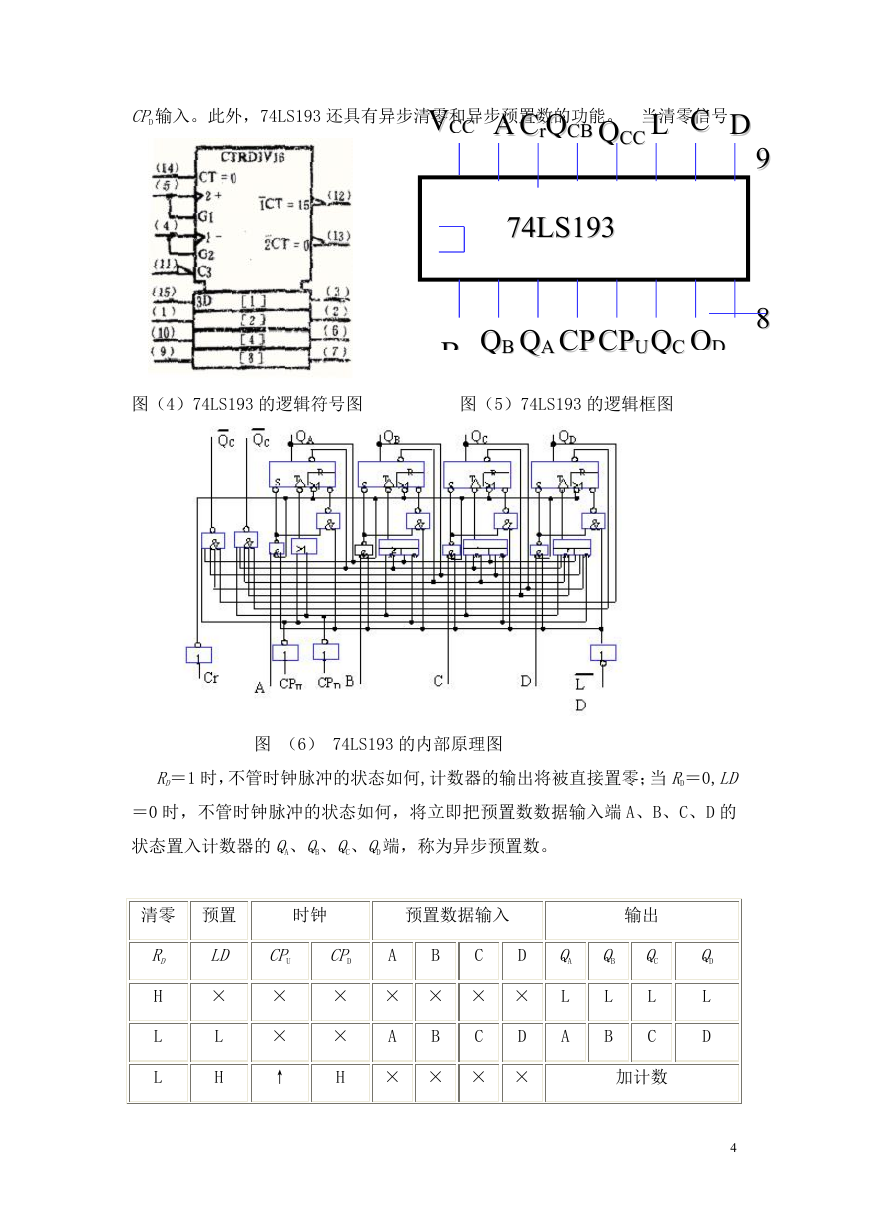

3.2 同步二进制可逆计数器 74LS193

74LS193 是双时钟 4 位二进制同步可逆计数器。图(4)(5)(6)分别是它

的逻辑符号图、逻辑框图和内部原理图,表(2)是它的功能表。74LS193 的特

点是有两个时钟脉冲(计数脉冲)输入端 CPU 和 CPD。在 RD=0、LD=1 的条件下,

作加计数时,令 CPD=1,计数脉冲从 CPU 输入;作减计数时,令 CPU=1,计数脉冲

从

3

�

CPD 输入。此外,74LS193 还具有异步清零和异步预置数的功能。 当清零信号

VVCCCC

AA

QQCBCBCCrr

QQCCCC

LL

CC

74LS1933

74LS19

QQBB QQAA

CPCP CPCPUU

QQCC QQDD

BB

图(4)74LS193 的逻辑符号图

图(5)74LS193 的逻辑框图

DD

99

88

图 (6) 74LS193 的内部原理图

RD=1 时,不管时钟脉冲的状态如何,计数器的输出将被直接置零;当 RD=0,LD

=0 时,不管时钟脉冲的状态如何,将立即把预置数数据输入端 A、B、C、D 的

状态置入计数器的 QA、QB、QC、QD 端,称为异步预置数。

清零 预置

时钟

预置数据输入

输出

CPU

CPD

A

B

C

D

QA

QB

QC

RD

H

L

L

LD

×

L

H

×

×

↑

×

H

× × × × × L

A

B

C

D

A

L

B

L

C

× × × ×

加计数

QD

L

D

4

�

L

H

H

↑ × × × ×

减计数

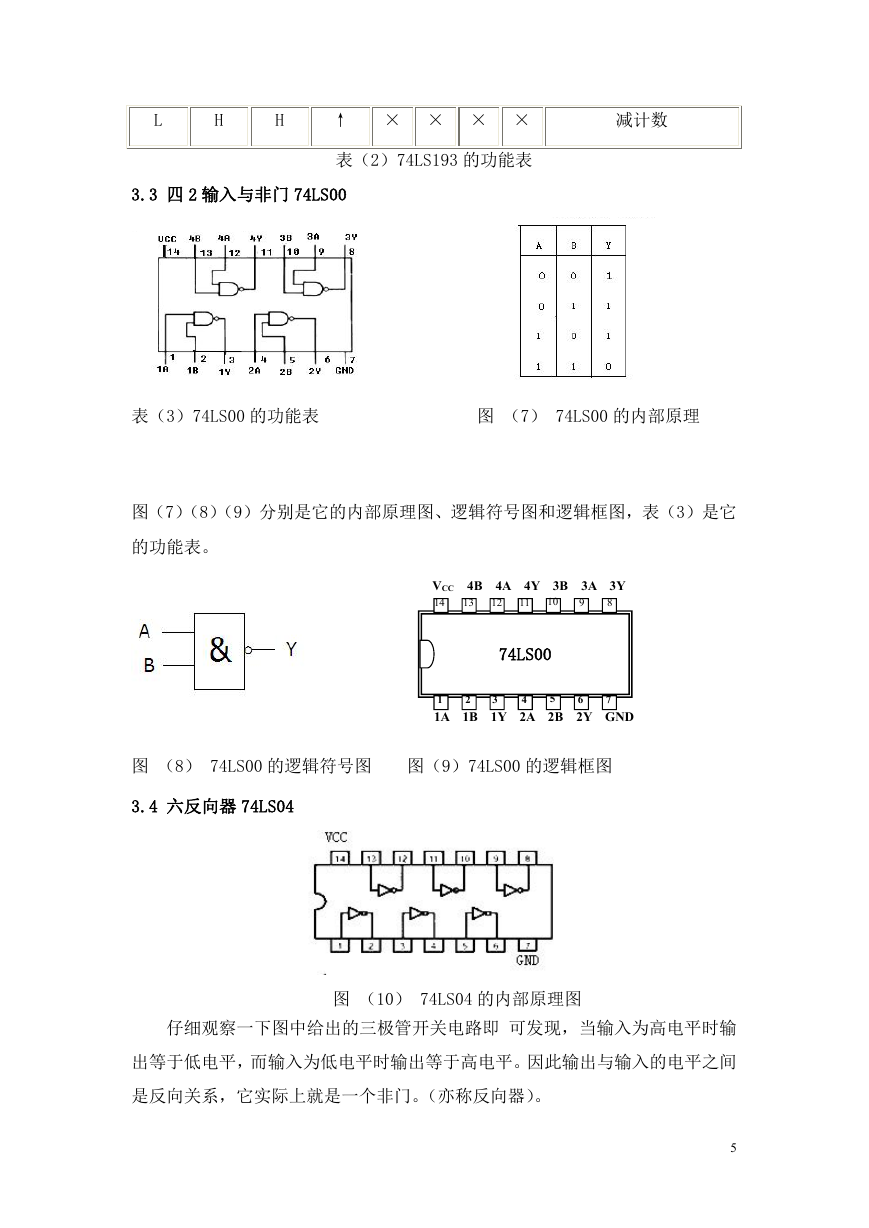

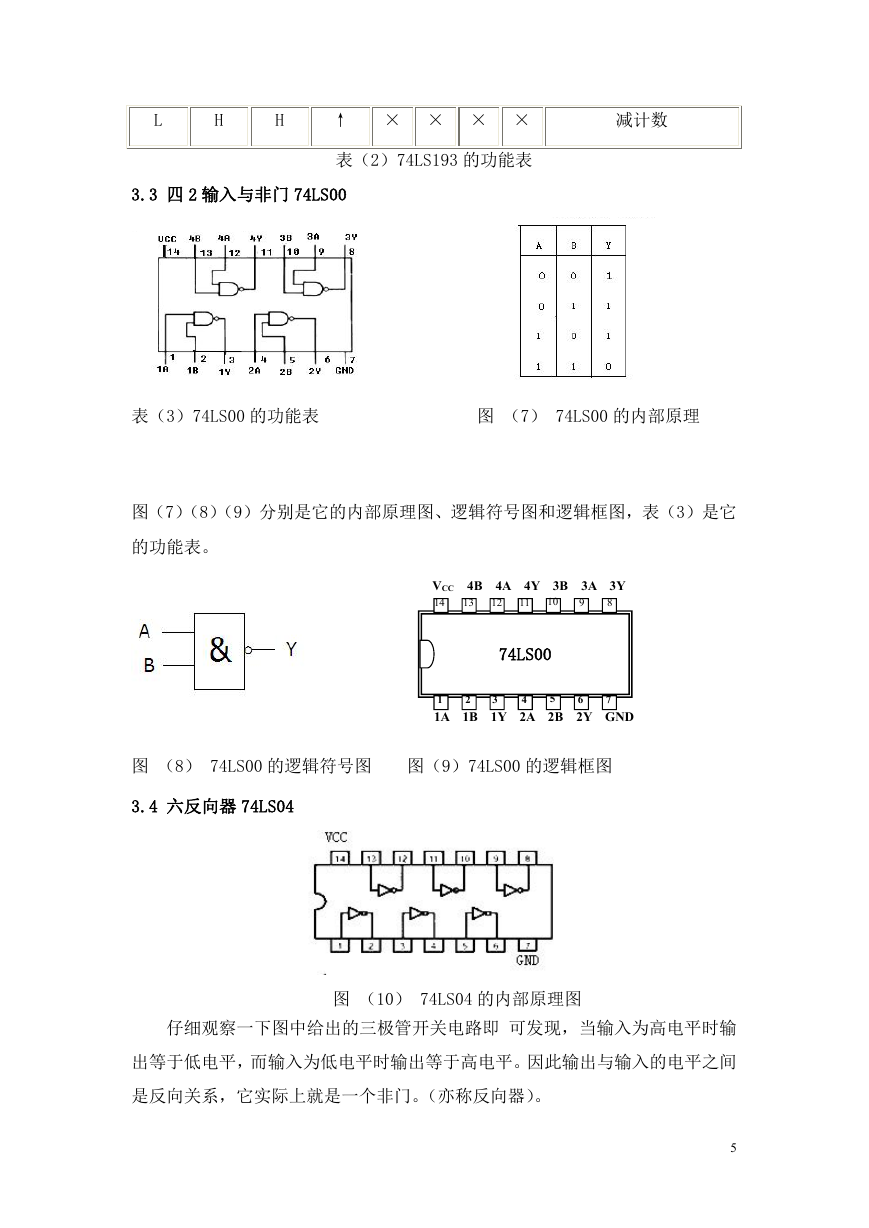

3.3 四 2 输入与非门 74LS00

表(2)74LS193 的功能表

表(3)74LS00 的功能表

图 (7) 74LS00 的内部原理

图(7)(8)(9)分别是它的内部原理图、逻辑符号图和逻辑框图,表(3)是它

的功能表。

VCC

14

4B 4A 4Y 3B 3A 3Y

13

12

10

11

9

8

74LS00

2

1

1A 1B 1Y 2A 2B 2Y GND

3

4

6

5

7

图 (8) 74LS00 的逻辑符号图

图(9)74LS00 的逻辑框图

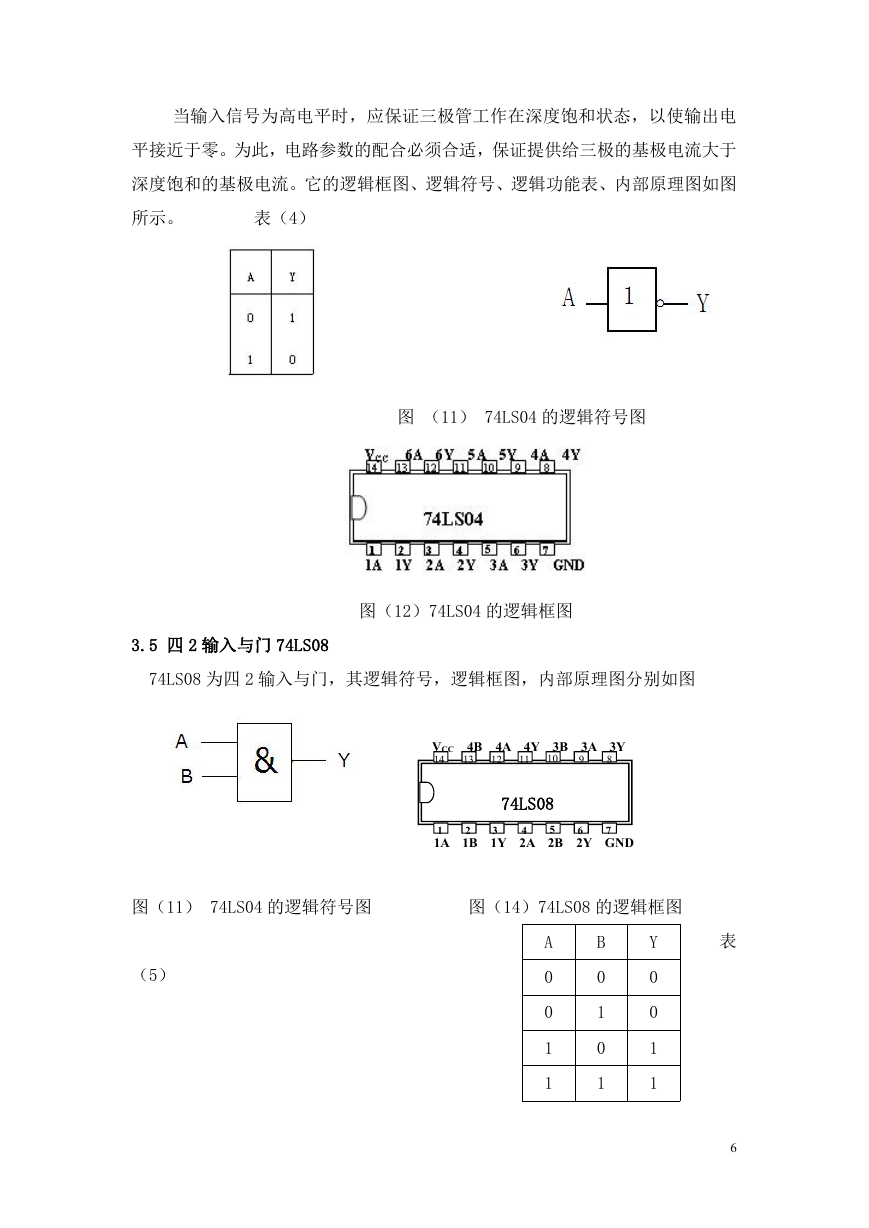

3.4 六反向器 74LS04

图 (10) 74LS04 的内部原理图

仔细观察一下图中给出的三极管开关电路即 可发现,当输入为高电平时输

出等于低电平,而输入为低电平时输出等于高电平。因此输出与输入的电平之间

是反向关系,它实际上就是一个非门。(亦称反向器)。

5

�

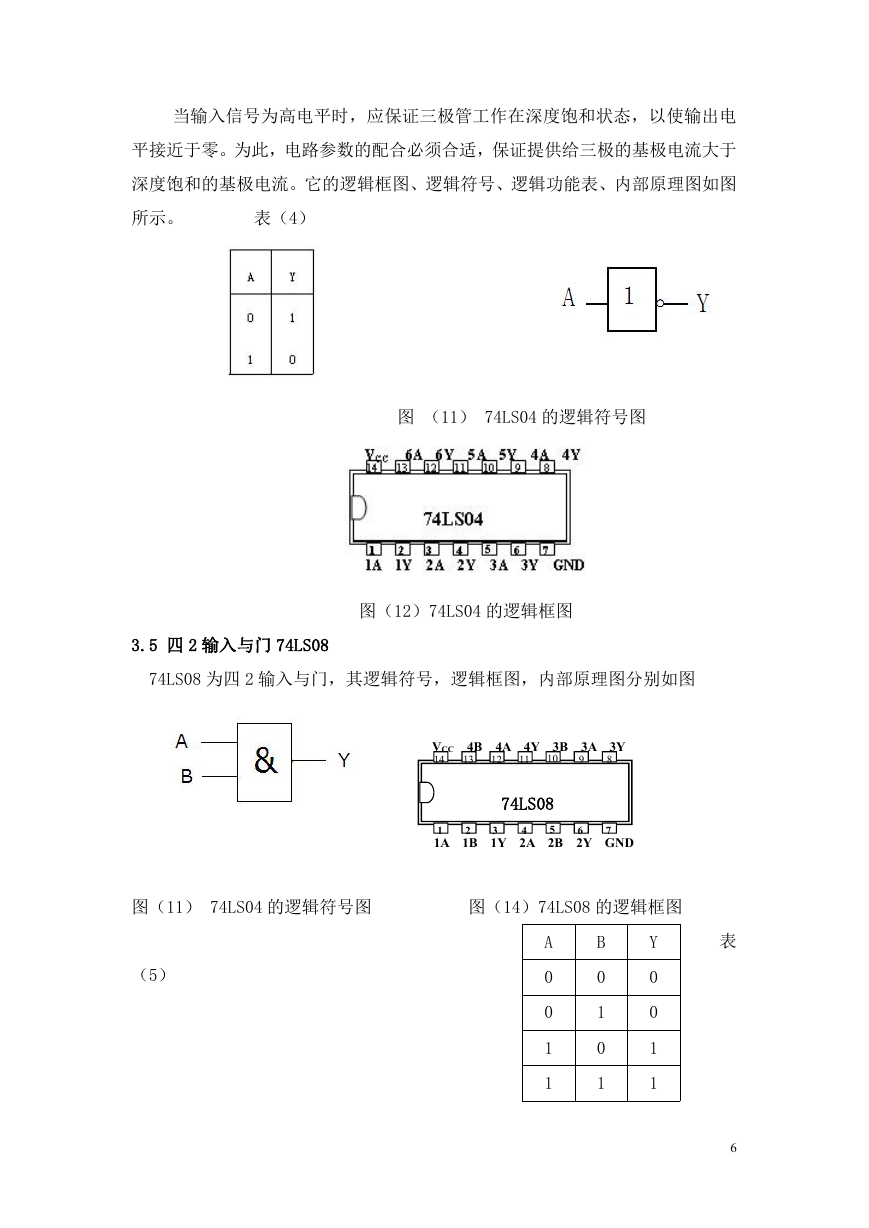

当输入信号为高电平时,应保证三极管工作在深度饱和状态,以使输出电

平接近于零。为此,电路参数的配合必须合适,保证提供给三极的基极电流大于

深度饱和的基极电流。它的逻辑框图、逻辑符号、逻辑功能表、内部原理图如图

所示。

表(4)

图 (11) 74LS04 的逻辑符号图

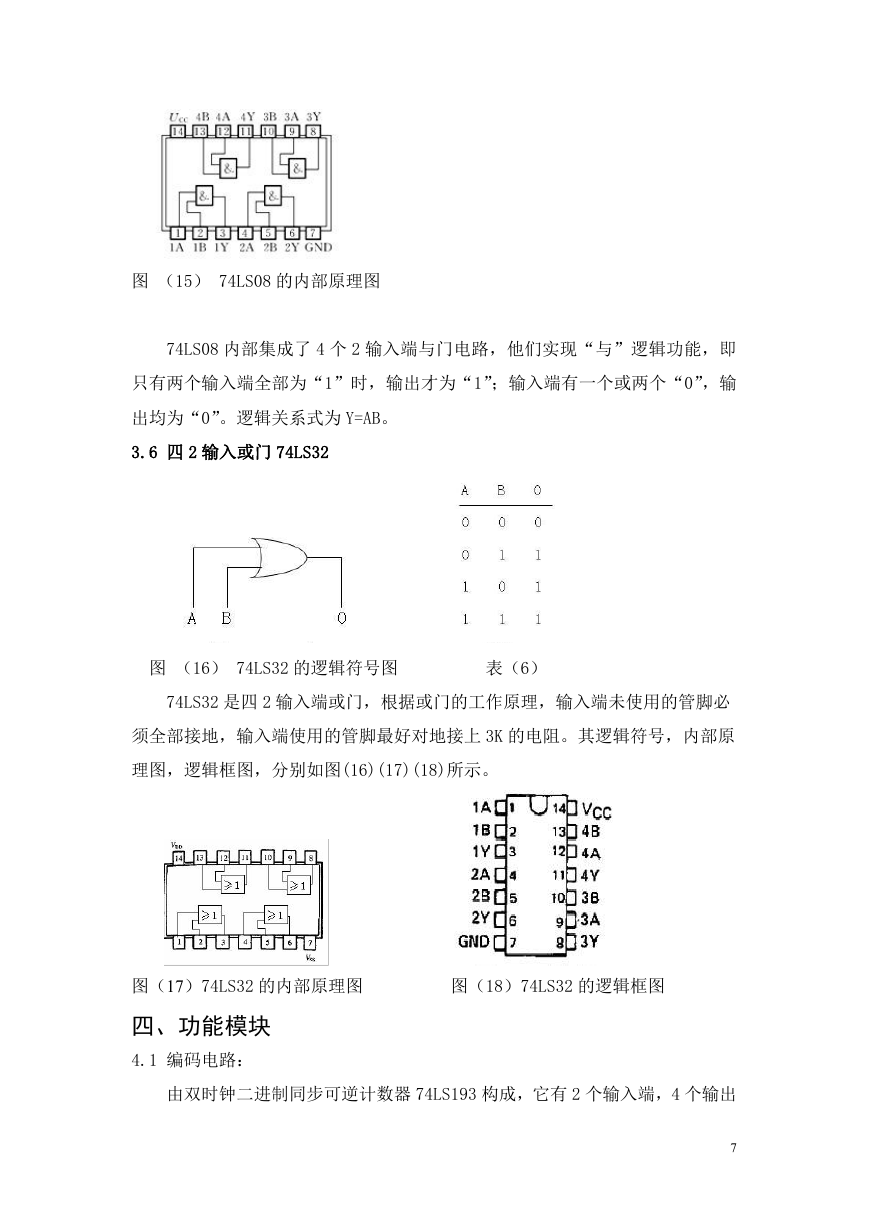

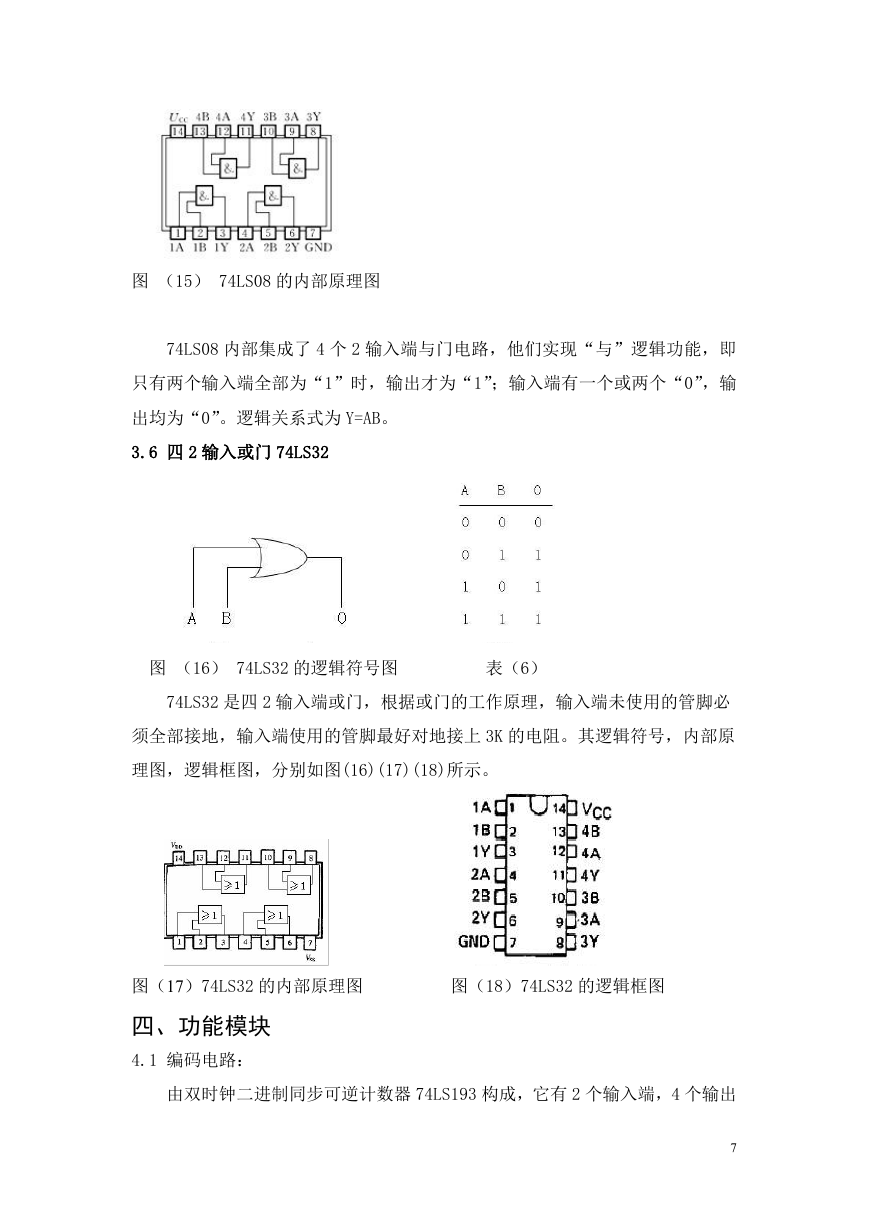

3.5 四 2 输入与门 74LS08

图(12)74LS04 的逻辑框图

74LS08 为四 2 输入与门,其逻辑符号,逻辑框图,内部原理图分别如图

VCC

14

4B 4A 4Y 3B 3A 3Y

13

12

10

11

9

8

74LS08

2

1

1A 1B 1Y 2A 2B 2Y GND

3

4

6

5

7

图(11) 74LS04 的逻辑符号图

图(14)74LS08 的逻辑框图

(5)

A

0

0

1

1

B

0

1

0

1

Y

0

0

1

1

表

6

�

图 (15) 74LS08 的内部原理图

74LS08 内部集成了 4 个 2 输入端与门电路,他们实现“与”逻辑功能,即

只有两个输入端全部为“1”时,输出才为“1”;输入端有一个或两个“0”,输

出均为“0”。逻辑关系式为 Y=AB。

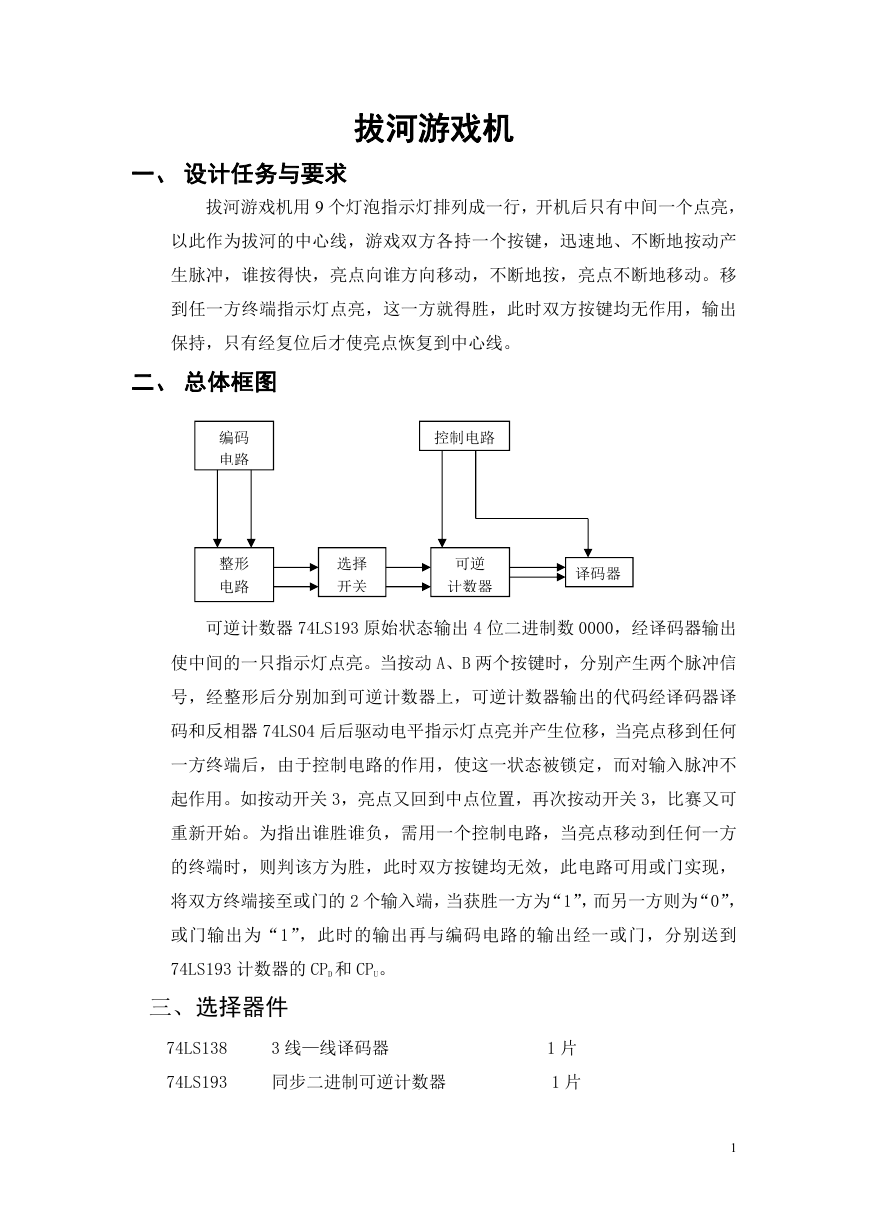

3.6 四 2 输入或门 74LS32

图 (16) 74LS32 的逻辑符号图

表(6)

74LS32 是四 2 输入端或门,根据或门的工作原理,输入端未使用的管脚必

须全部接地,输入端使用的管脚最好对地接上 3K 的电阻。其逻辑符号,内部原

理图,逻辑框图,分别如图(16)(17)(18)所示。

图(17)74LS32 的内部原理图

图(18)74LS32 的逻辑框图

四、功能模块

4.1 编码电路:

由双时钟二进制同步可逆计数器 74LS193 构成,它有 2 个输入端,4 个输出

7

�

端,能进行加/减计数。74LS193 的特点是有两个时钟脉冲(计数脉冲)输入端

CPU 和 CPD。在 RD=0、LD=1 的条件下,作加计数时,令 CPD=1,计数脉冲从 CPU 输

入;作减计数时,令 CPU=1,计数脉冲从 CPD 输入。此外,74LS193 还具有异步

清零和异步预置数的功能。当清零信号 RD=1 时,不管时钟脉冲的状态如何,计

数器的输出将被直接置零;当 RD=0,LD=0 时,不管时钟脉冲的状态如何,将立

即把预置数数据输入端 A、B、C、D 的状态置入计数器的 QA、QB、QC、QD 端,称为

异步预置数。图(19)为编码电路图,不断的按动按键 A、B,给电路加脉冲,

图(19)编码电路图

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc