1100 MMAACC

Ethernet

RS-485CAN

Internet TCP/IP

USB 2.0IEEE 1394

x

x

x

x

x

FPGA

FPGA MAC

10.1

IEEE 802.3 LANLocal Area

Network CSMA/CD

CSMA/CD Carrier sense multiple Access with Collision Detection

IEEE 802.3

10.1.1

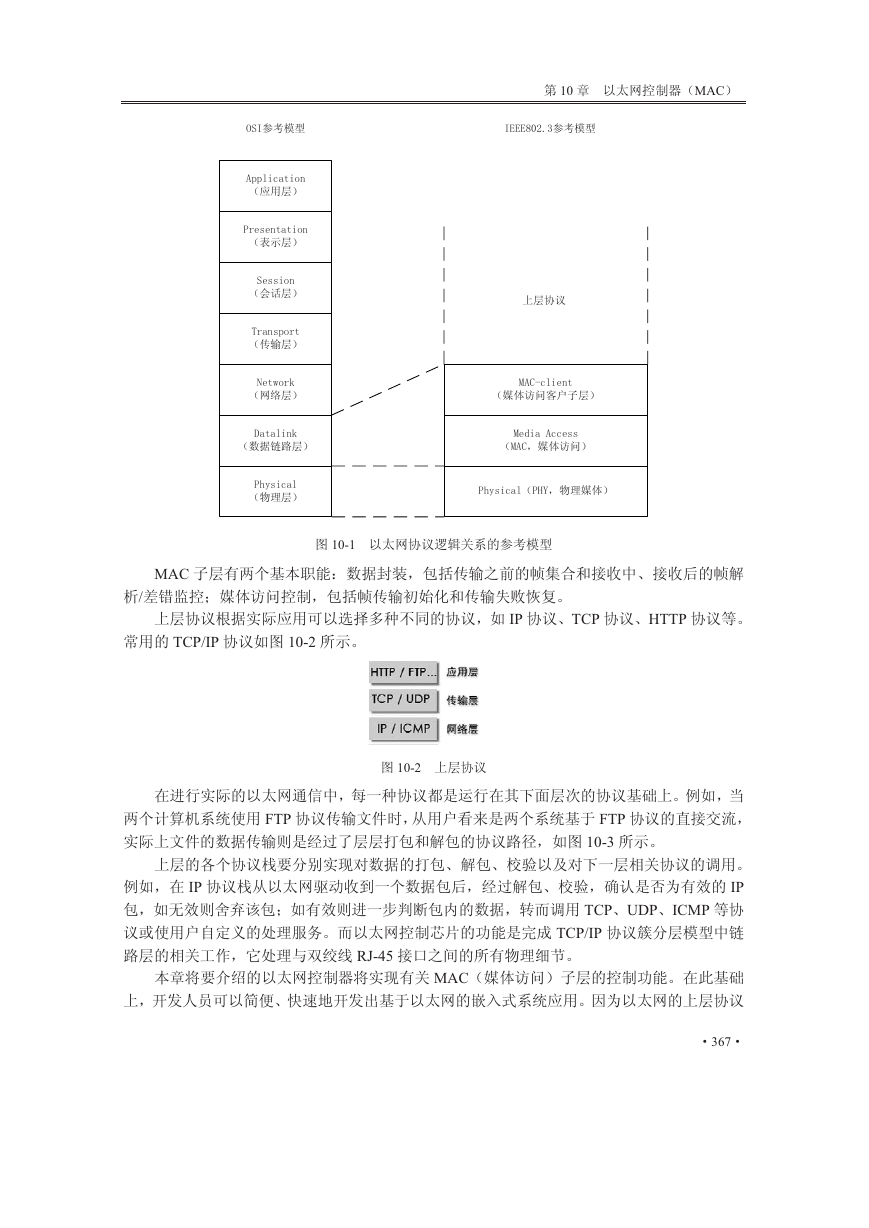

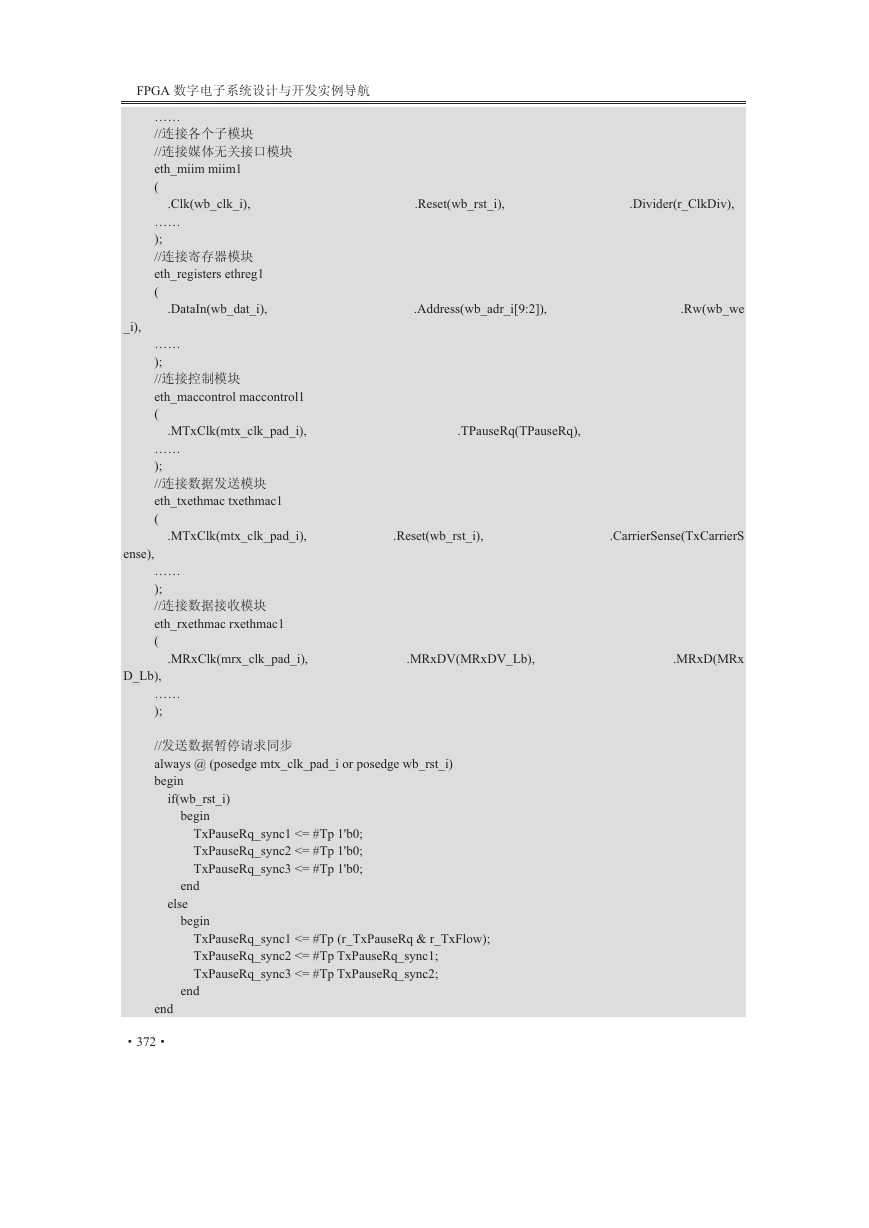

OSI Open System Interconnect Reference Model

10-1

4

x 10 Mbit/s10Base-T

x 100 Mbit/s

x 1000 Mbit/s 802.3z

x 10 IEEE 802.3ae

�

10 MAC

10-1

MAC

/

IP TCP HTTP

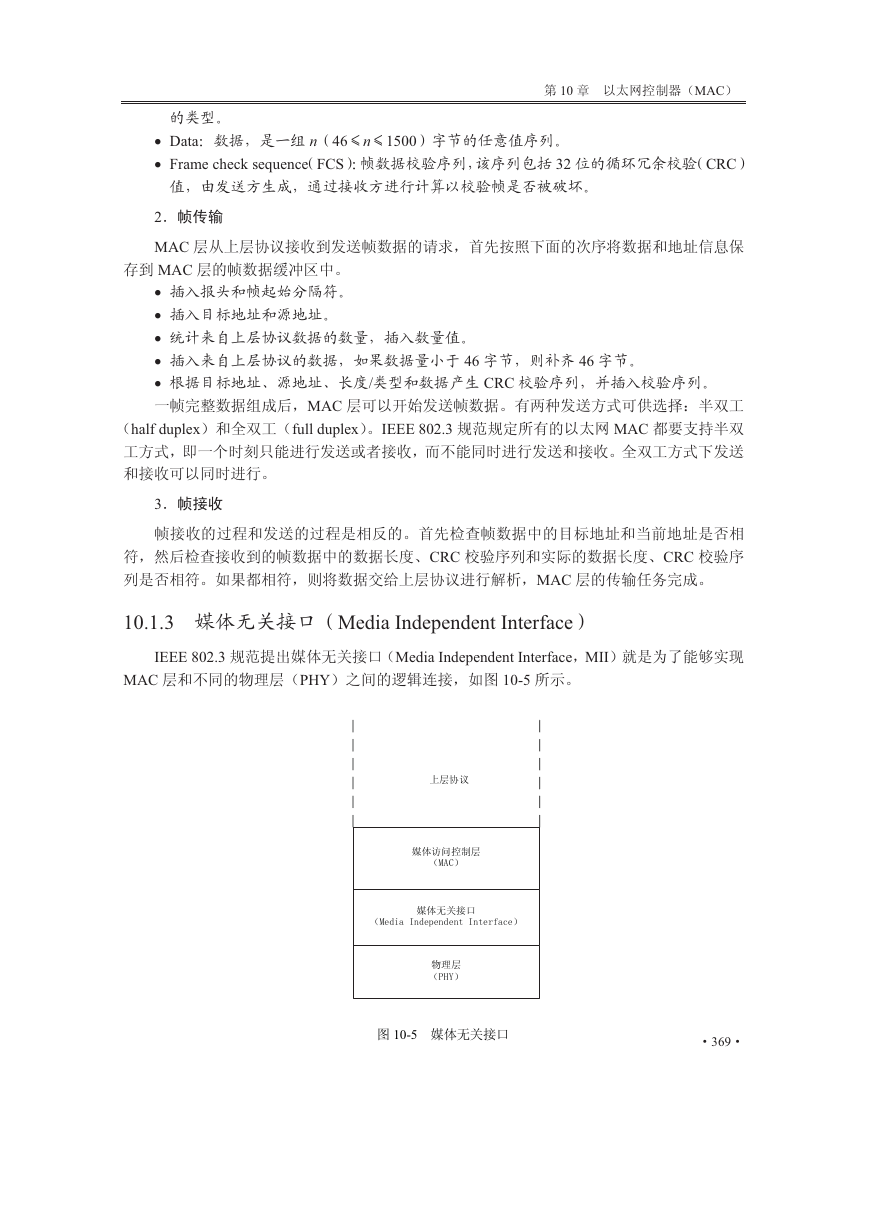

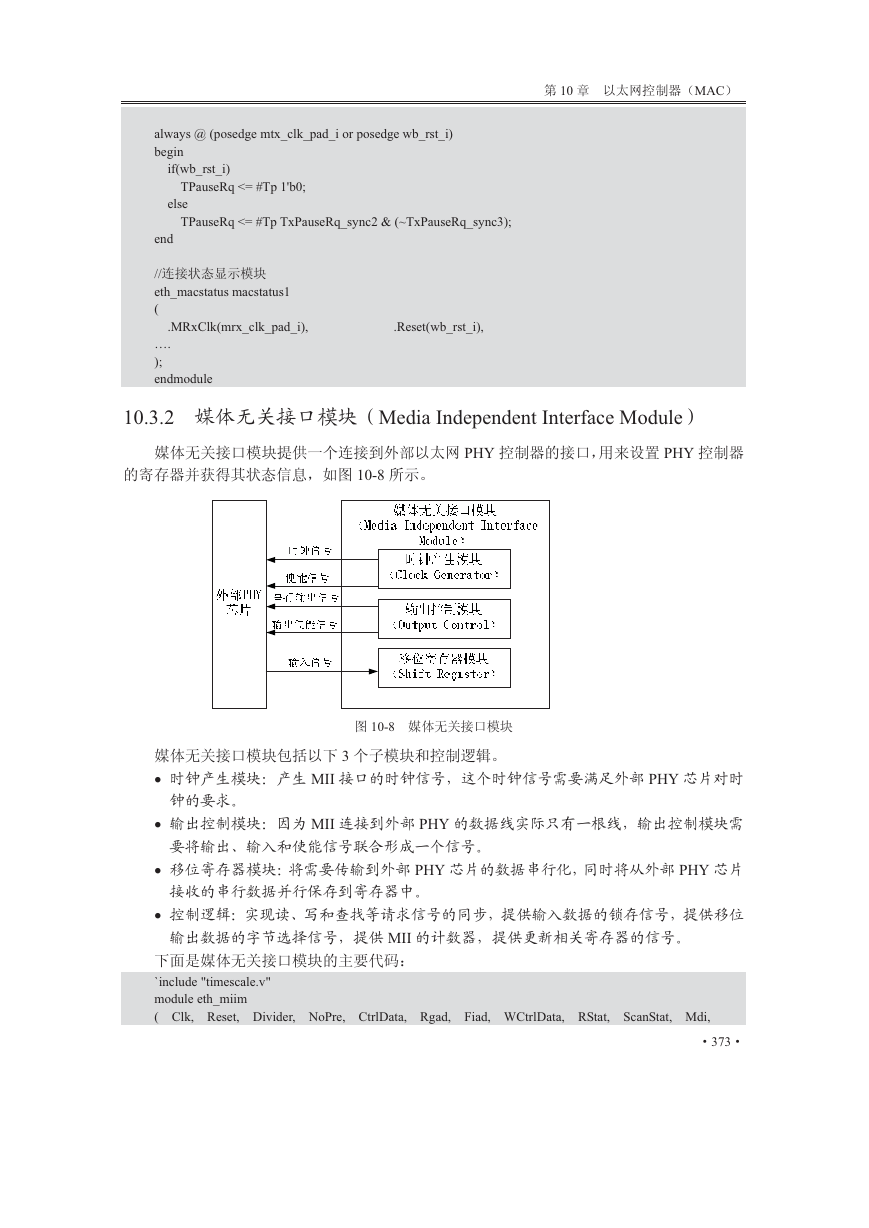

TCP/IP 10-2

10-2

FTP FTP

10-3

IP IP

TCPUDPICMP

TCP/IP

RJ-45

MAC

367

�

FPGA

MAC

10-3 FTP

10.1.2 MAC

MAC

IEEE 802.3

1

IEEE 802.3 MAC 10-4

10-4

x PreamblePRE 1 0

x Start-of-frame delimiterSFD 1 0

1

x Destination AddressDA

x Source AddressSA

x Length/Type/ MAC

368

�

10 MAC

x Data n46n1500

x Frame check sequenceFCS 32 CRC

2

MAC

MAC

x

x

x

x 46 46

x / CRC

MAC

half duplexfull duplexIEEE 802.3 MAC

3

CRC CRC

MAC

10.1.3 Media Independent Interface

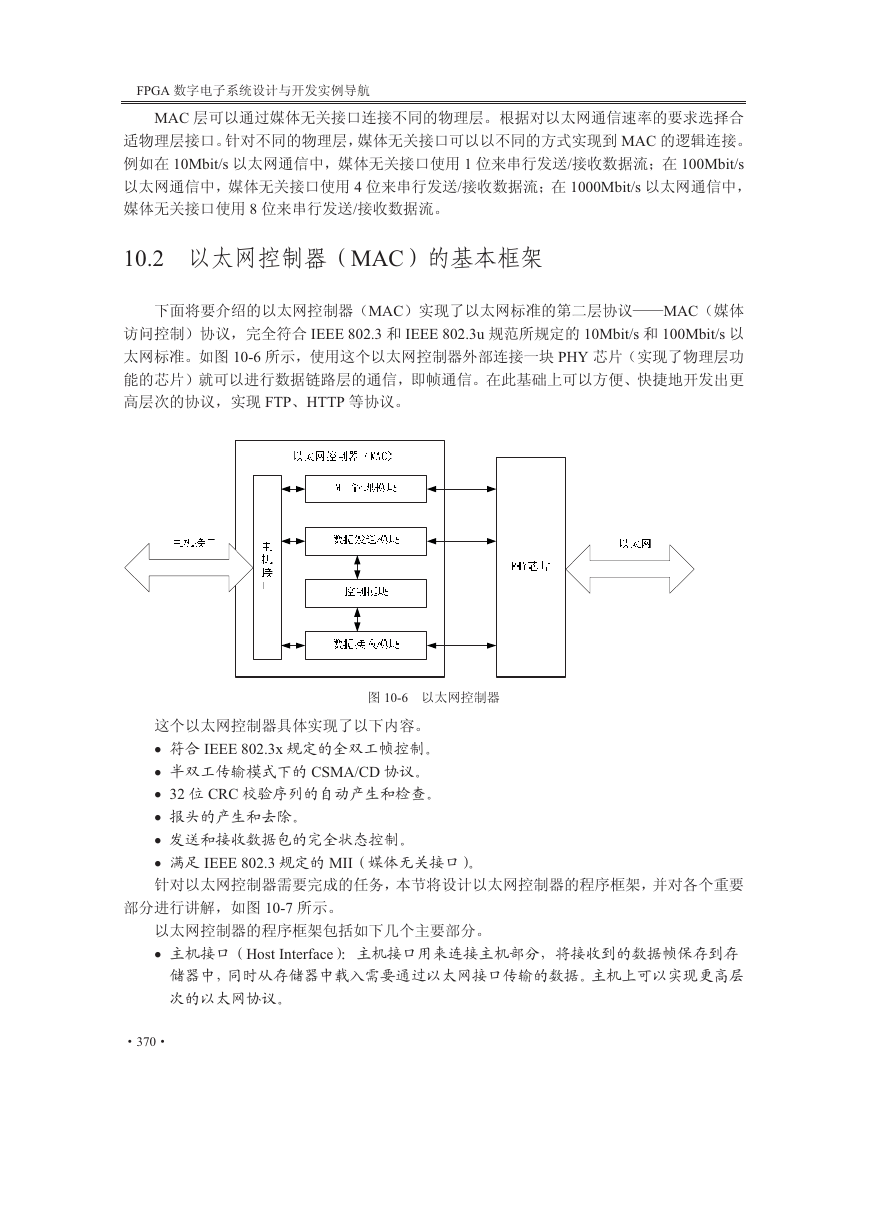

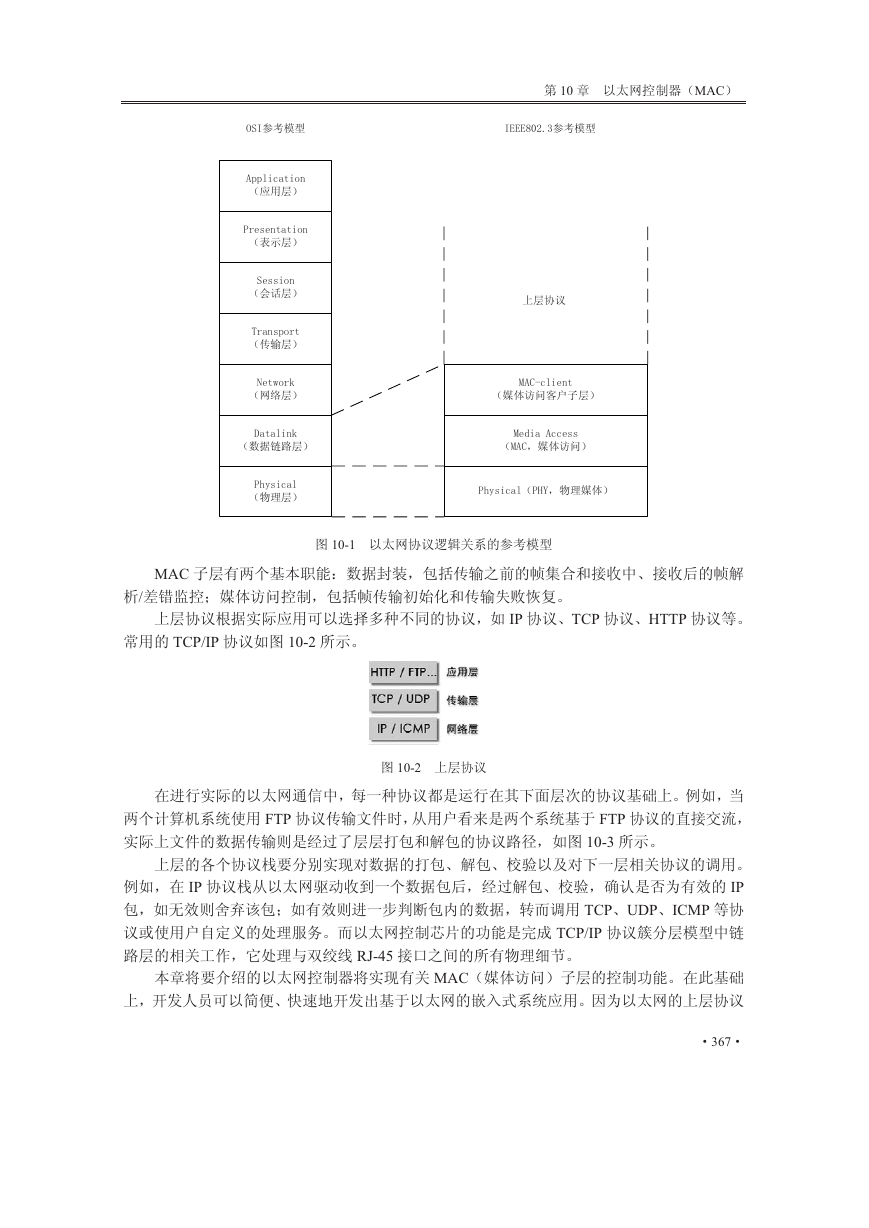

IEEE 802.3 Media Independent InterfaceMII

MAC PHY 10-5

�

��

!"45��

�

!"#$�%

�

+,

�

2 10-5 !"#$�%

369

�

FPGA

MAC

MAC

10Mbit/s 1 / 100Mbit/s

4 / 1000Mbit/s

8 /

10.2 MAC

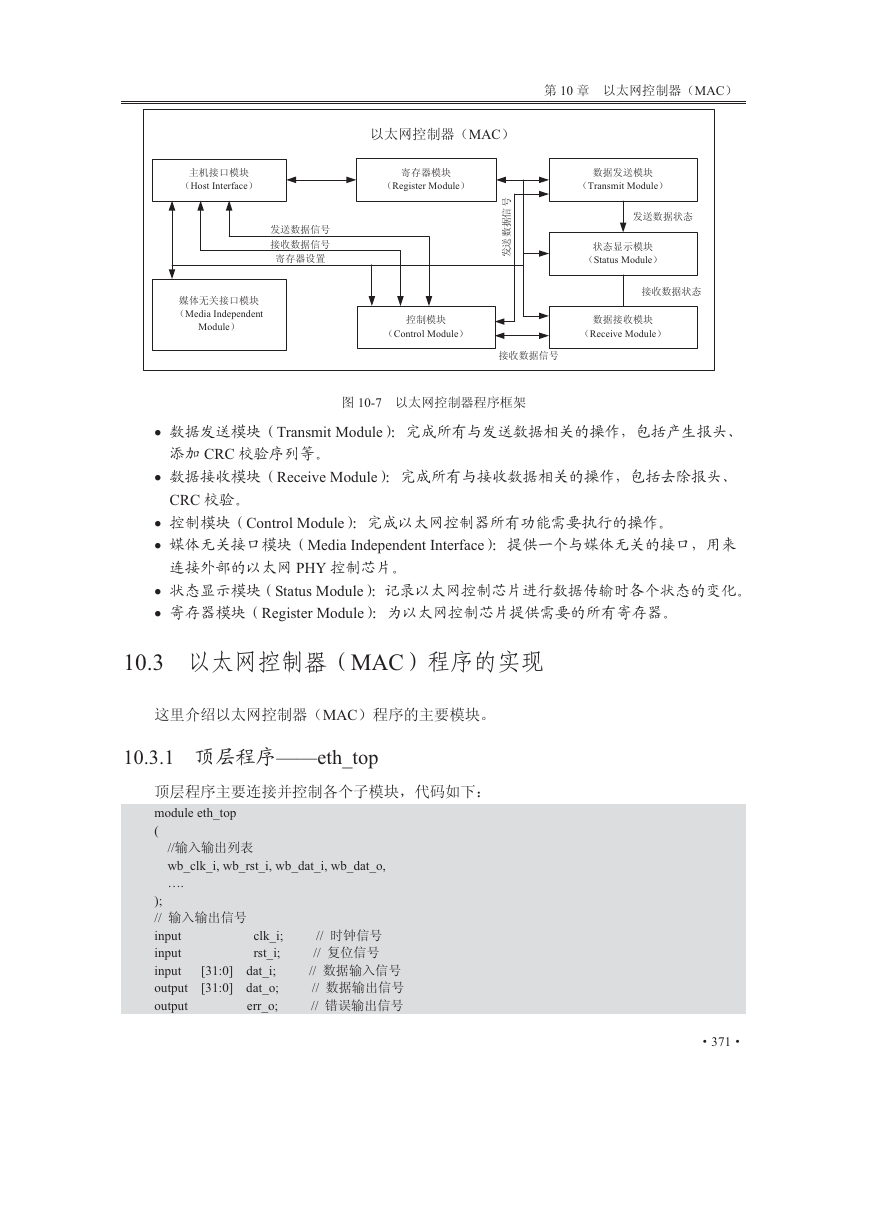

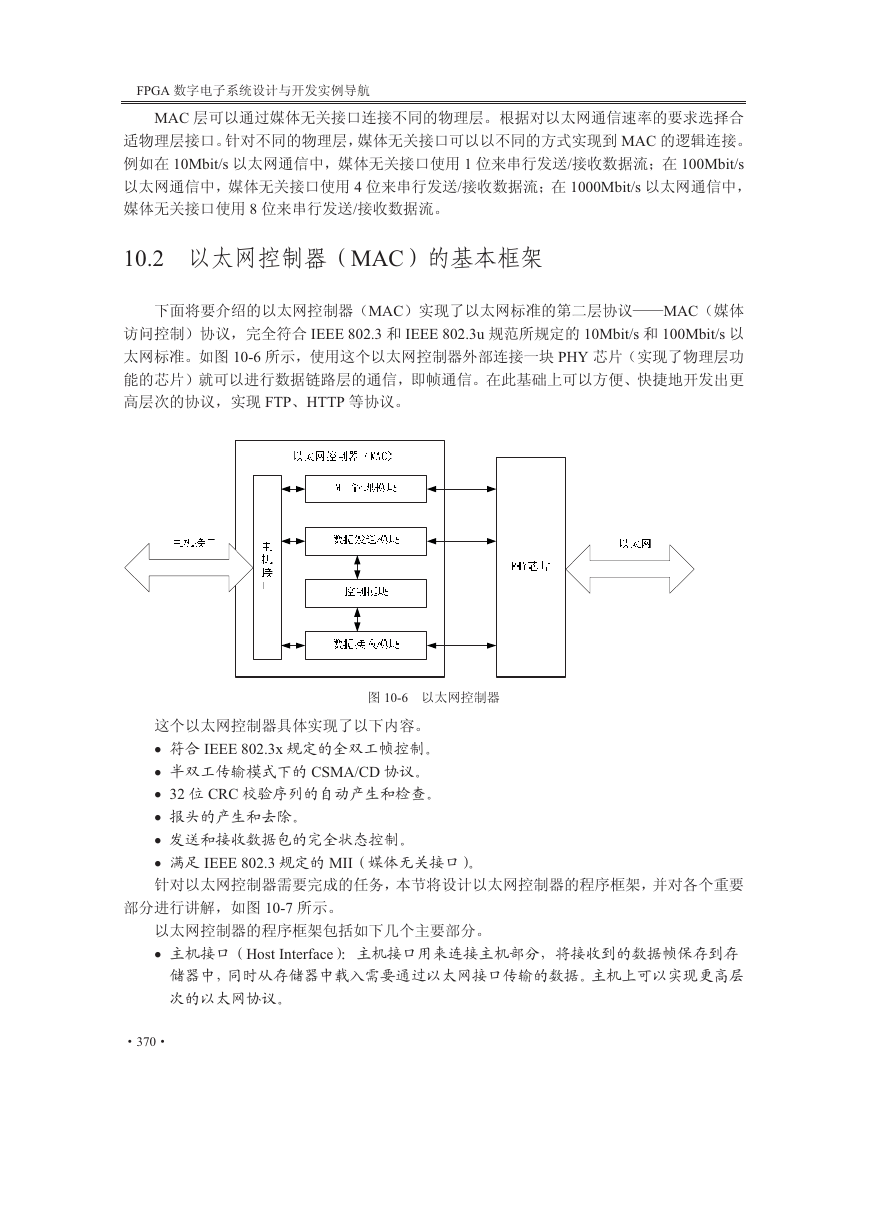

MACMAC

IEEE 802.3 IEEE 802.3u 10Mbit/s 100Mbit/s

10-6 PHY

FTPHTTP

10-6

x IEEE 802.3x

x CSMA/CD

x 32 CRC

x

x

x IEEE 802.3 MII

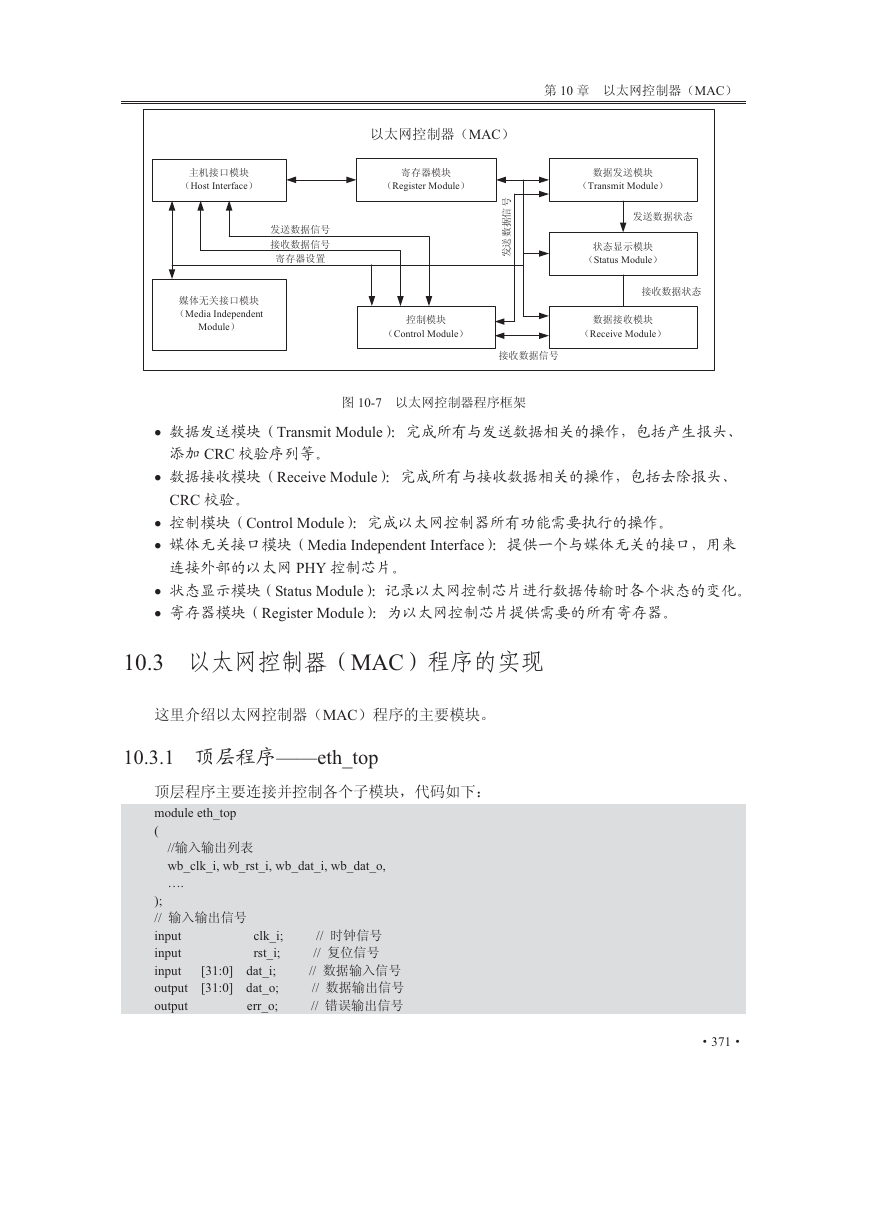

10-7

x Host Interface

370

�

10 MAC

MAC

Host Interface

Register Module

Transmit Module

Media Independent

Module

Status Module

Control Module

Receive Module

10-7

x Transmit Module

CRC

x Receive Module

CRC

x Control Module

x Media Independent Interface

PHY

x Status Module

x Register Module

10.3 MAC

MAC

10.3.1 ——eth_top

module eth_top

(

//

wb_clk_i, wb_rst_i, wb_dat_i, wb_dat_o,

….

);

//

input clk_i; //

input rst_i; //

input [31:0] dat_i; //

output [31:0] dat_o; //

output err_o; //

371

�

FPGA

_i),

……

//

//

eth_miim miim1

(

.Clk(wb_clk_i), .Reset(wb_rst_i), .Divider(r_ClkDiv),

……

);

//

eth_registers ethreg1

(

.DataIn(wb_dat_i), .Address(wb_adr_i[9:2]), .Rw(wb_we

……

);

//

eth_maccontrol maccontrol1

(

.MTxClk(mtx_clk_pad_i), .TPauseRq(TPauseRq),

……

);

//

eth_txethmac txethmac1

(

.MTxClk(mtx_clk_pad_i), .Reset(wb_rst_i), .CarrierSense(TxCarrierS

ense),

……

);

//

eth_rxethmac rxethmac1

(

.MRxClk(mrx_clk_pad_i), .MRxDV(MRxDV_Lb), .MRxD(MRx

D_Lb),

……

);

//

always @ (posedge mtx_clk_pad_i or posedge wb_rst_i)

begin

if(wb_rst_i)

begin

TxPauseRq_sync1 <= #Tp 1'b0;

TxPauseRq_sync2 <= #Tp 1'b0;

TxPauseRq_sync3 <= #Tp 1'b0;

end

else

begin

TxPauseRq_sync1 <= #Tp (r_TxPauseRq & r_TxFlow);

TxPauseRq_sync2 <= #Tp TxPauseRq_sync1;

TxPauseRq_sync3 <= #Tp TxPauseRq_sync2;

end

end

372

�

10 MAC

always @ (posedge mtx_clk_pad_i or posedge wb_rst_i)

begin

if(wb_rst_i)

TPauseRq <= #Tp 1'b0;

else

TPauseRq <= #Tp TxPauseRq_sync2 & (~TxPauseRq_sync3);

end

//

eth_macstatus macstatus1

(

.MRxClk(mrx_clk_pad_i), .Reset(wb_rst_i),

….

);

endmodule

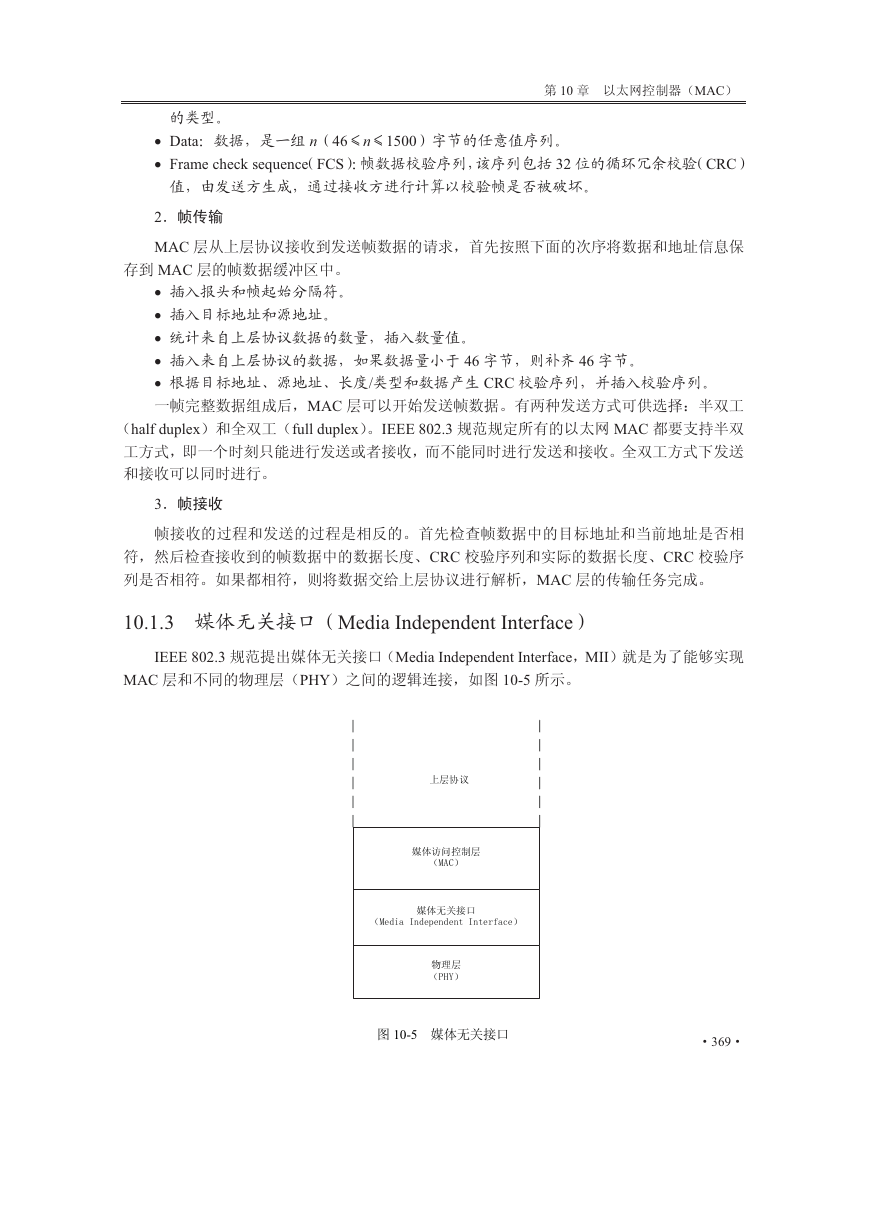

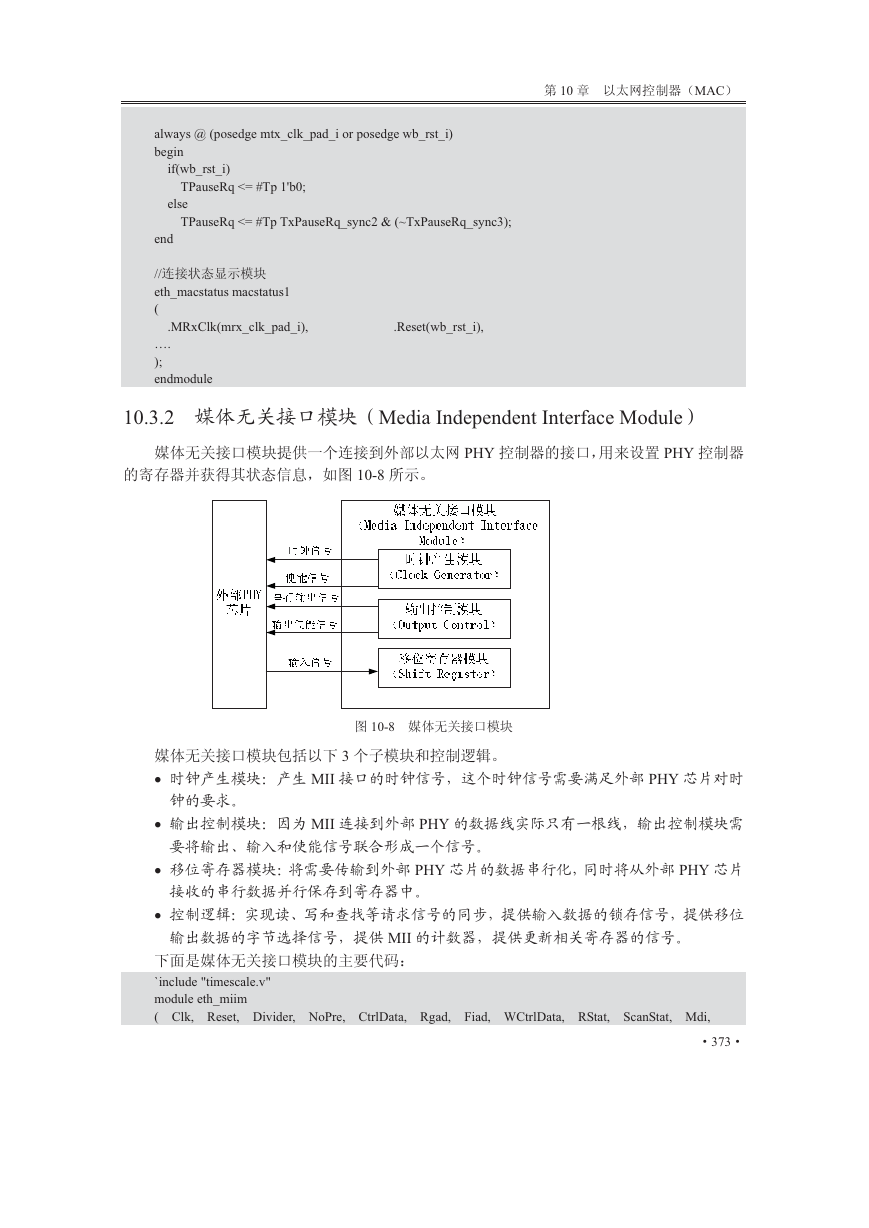

10.3.2 Media Independent Interface Module

PHY PHY

10-8

10-8

3

x MII PHY

x MII PHY

x PHY PHY

x

MII

`include "timescale.v"

module eth_miim

( Clk, Reset, Divider, NoPre, CtrlData, Rgad, Fiad, WCtrlData, RStat, ScanStat, Mdi,

373

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc