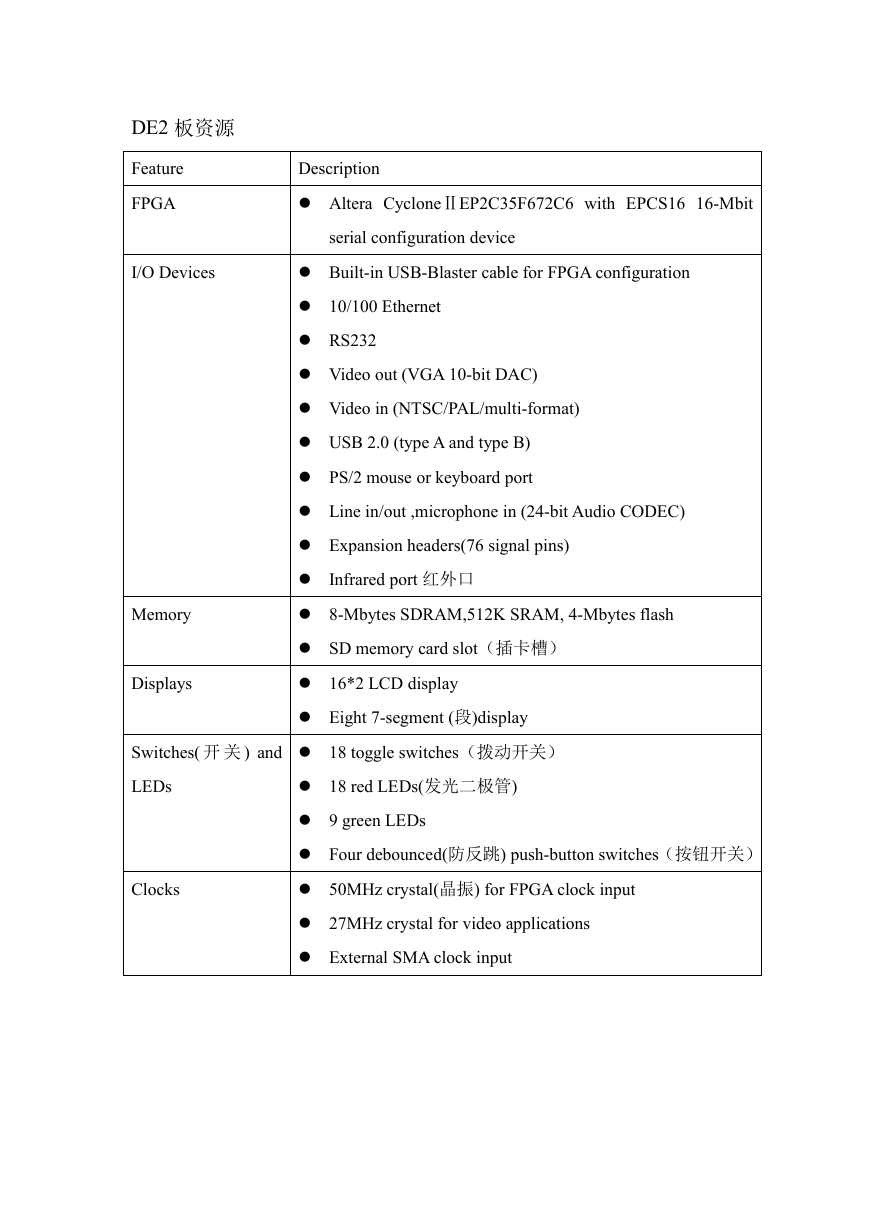

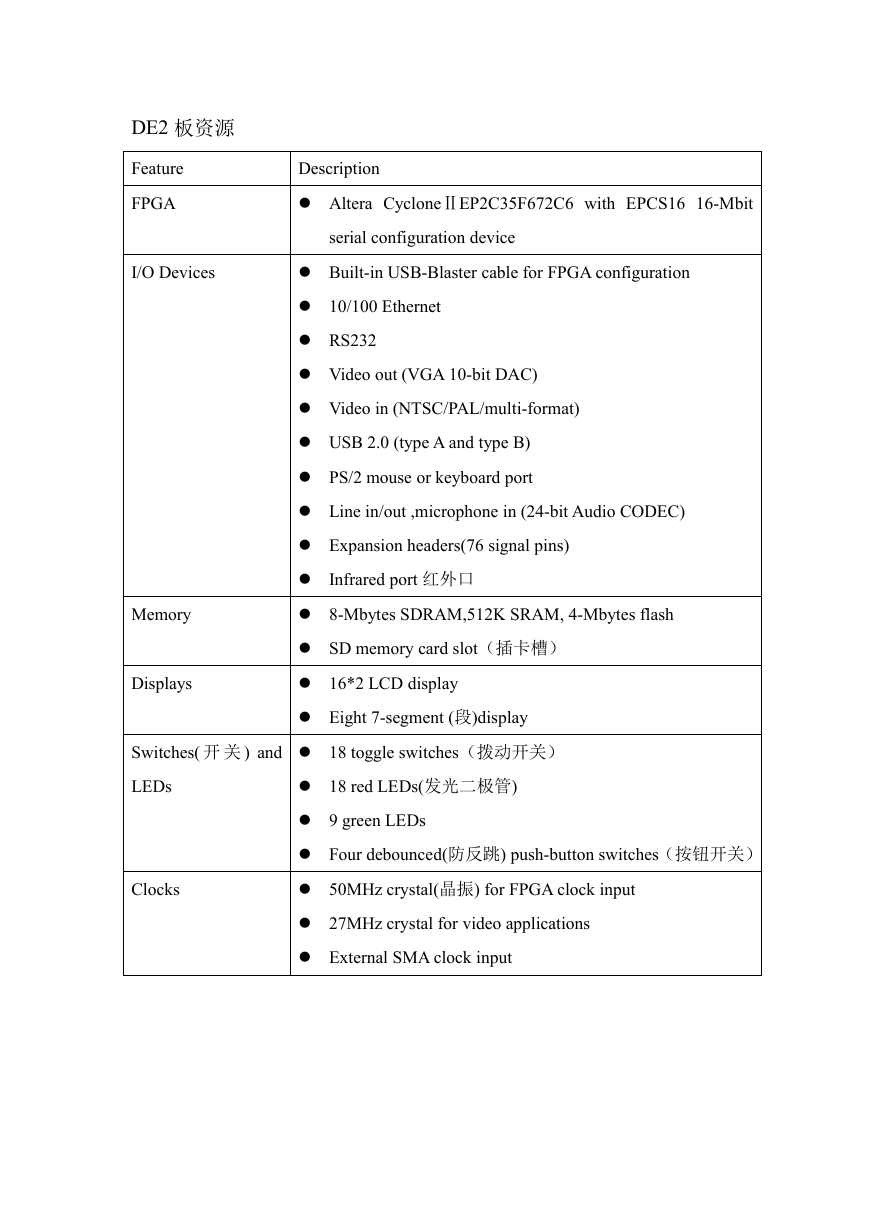

DE2 板资源

Feature

FPGA

I/O Devices

Memory

Displays

Switches( 开 关 ) and

LEDs

Clocks

Description

Altera CycloneⅡEP2C35F672C6 with EPCS16 16-Mbit

serial configuration device

Built-in USB-Blaster cable for FPGA configuration

10/100 Ethernet

RS232

Video out (VGA 10-bit DAC)

Video in (NTSC/PAL/multi-format)

USB 2.0 (type A and type B)

PS/2 mouse or keyboard port

Line in/out ,microphone in (24-bit Audio CODEC)

Expansion headers(76 signal pins)

Infrared port 红外口

8-Mbytes SDRAM,512K SRAM, 4-Mbytes flash

SD memory card slot(插卡槽)

16*2 LCD display

Eight 7-segment (段)display

18 toggle switches(拨动开关)

18 red LEDs(发光二极管)

9 green LEDs

Four debounced(防反跳) push-button switches(按钮开关)

50MHz crystal(晶振) for FPGA clock input

27MHz crystal for video applications

External SMA clock input

�

主要包含的步骤:

设计输入:——可通过电路原理图,或硬件描述语言(VHDL、Verilog)的

方式将所需要的电路输入到 CAD 软件中

综合——将所输入的设计转换成由若干逻辑单元(LE)互联构成的电路,这

些 LE 位于 FPGA 器件中,他们是具有通用性的基本电路模块;

功能仿真——测试综合后的电路在逻辑功能上的正确性,功能仿真不考虑任

何时序问题

布局布线(Fitting)——确定所设计的电路使用到的 LE 的布局方式及相关

连线

时序(Timing)分析、时序仿真——分析布局布线后的电路沿不同路径的传

输时延,以提供电路的预期性能指标;检验和估计往电路输入节点施加各种

测试信号时的实际输出结果

编程和配置——设置 FPGA 内部的开关(用于配置 LE 的电路功能和创建所

需的连线)将所设计的电路实现到一个物理的 FPGA 器件中。这一步一般由

厂商所提供的软硬件工具来完成。再将设计实现到一个 FPGA 器件方面而言,

编程和配置这两个术语经常通用。

主要步骤:

�

1. 创建工程

2. 绘制原理图(或编写代码)

3. 编译包含综合布局布线等

4. 分配引脚

5. 方针和时序分析

6. 配置 FPGA

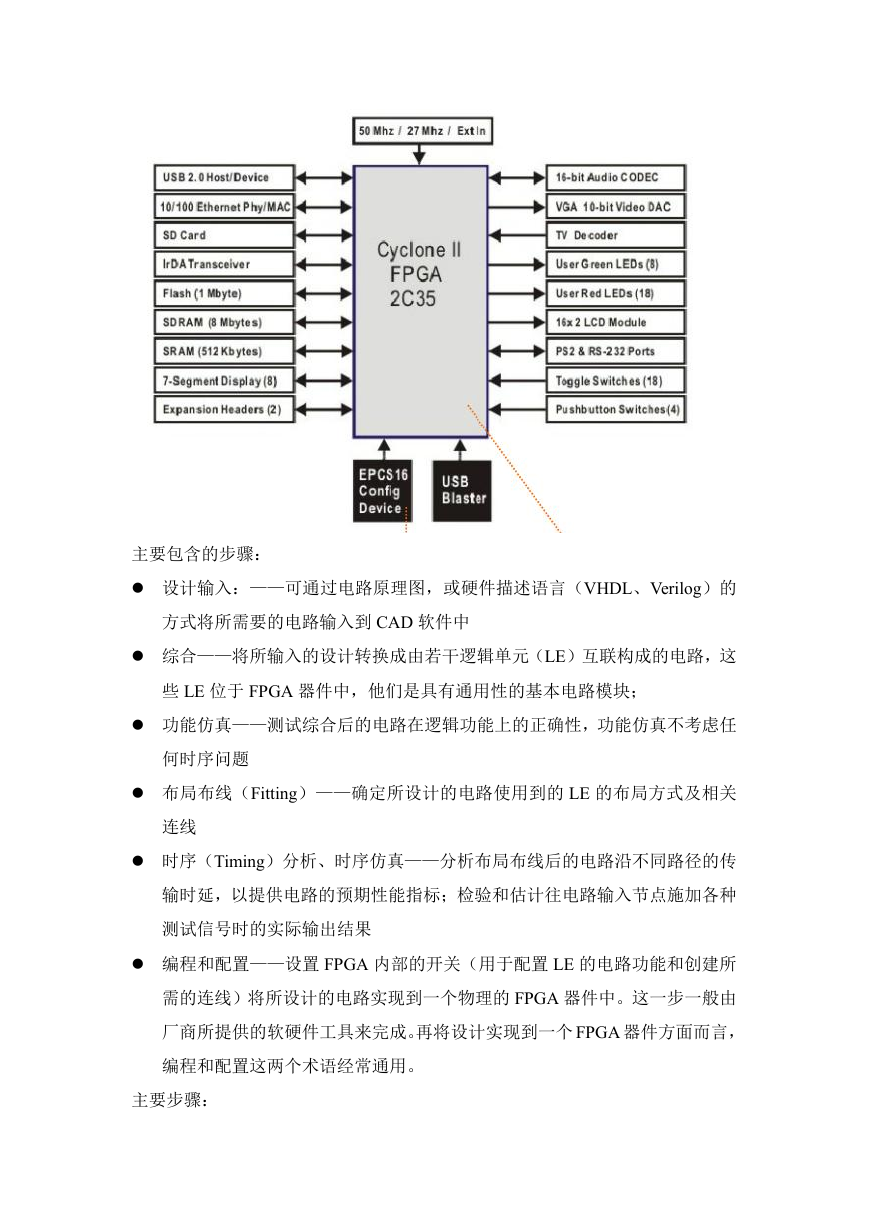

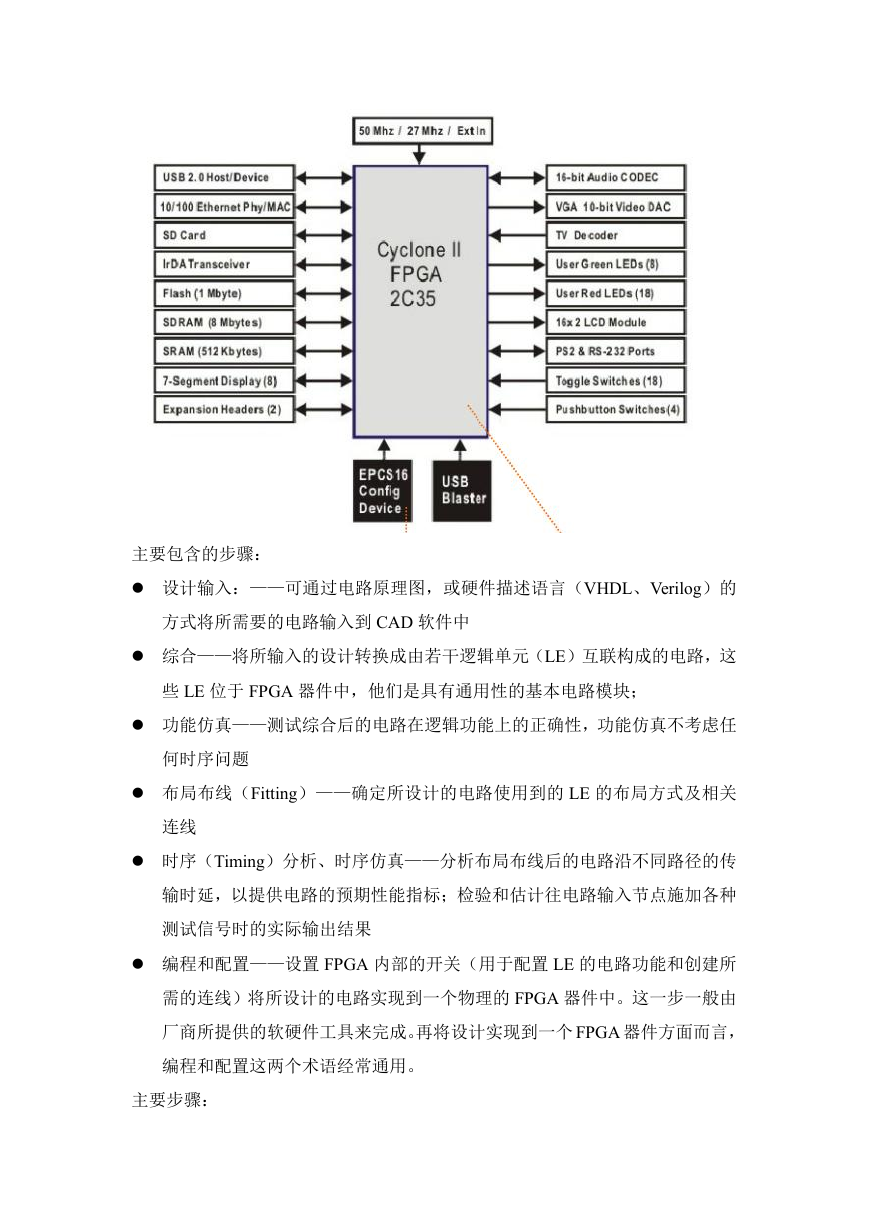

DE2 的资源非常丰富,包括:

1. 核心的 FPGA 芯片-Cyclone II 2C35 F672C6,从名称可以看出,它包含有 35

千个 LE,在 Altera 的芯片系列中,不算最多,但也绝对够用。Altera 下载控制芯片-

EPCS16 以及 USB-Blaste 对 Jtag 的支持。

2.存储用的芯片有: 512-KB SRAM,8-Mbyte SDRAM,4-Mbyte Flash

memory

3. 经典 IO 配置:拥有 4 个按钮,18 个拨动开关,18 个红色发光二极管,9 个

绿色发光二极管,8 个七段数码管,16*2 字符液晶显示屏

4. 超强多媒体:24 位 CD 音质音频芯片 WM8731(Mic 输入+LineIn+ 标准音

频输出),视频解码芯片(支持 NTSC/PAL 制式),带有高速 DAC 视屏输出 VGA

模块。

5.更多标准接口:通用串行总线 USB 控制模块以及 A、B 型接口,SD Card

接口,IrDA 红外模块, 10/100M 自适应以太网络适配器,RS-232 标准串口,

PS/2 键盘接口

6.其他:50M,27M 晶振各一个,支持外部时钟, 80 针带保护电路的外接 IO

7.此外还有:配套的光盘资料,QutuarsII6 软件,NiosII 6.0IDE,例程与说明

文档。

DE2 的使用

关于 DE2 资料光盘的使用

主要的可以参看他的用户手册,里面有关于 DE2 的资料的详细使用说明,

板子的电路原理图,模块图,管脚图,和各个模块的 Datasheet 等等。

可以这样来看:

DE2_System:

\Datasheet

来自各个芯片厂商。

DE2 板子上的各个模块的详细的官方 Datasheet,

\DE2_demonstrations 丰 富 的 例 程 , 里 面 很 多 适 用 的 例 子 , 比 如

SD_Music_Player.等

�

\DE2_lab_exercises

DE2 提供的试验内容,里面有很详细的操作步骤截

图。

DE2 板子资料,包括布线,电路板的资料

例如详细的讲解 SOPC Builder 的使用。

\DE2_schematics

\DE2_tutorials

\DE2_user_manual 用户使用指南与手册.综合的说明。

\Altera_Debug_Client DE2 的调试工具,可以直接下载 Nios 处理器的汇

编代码,C 语言代码等。

\DE2_control_panel

DE2 控制面板,直接操作 DE2 板子上的各个模块

的工作状态。

程序下载方法

第一种称为 RUN 模式,需要将板上 RUN/PROG 开关(LCD 旁)拨

到 RUN,是用 USB-Blaster 直接将 sof 文件烧到 Cyclone FPGA 芯片,这样掉

电之后就没有了,重启后需要再次烧写。

第二种模式为 AS 模式,将 RUN/PROG 开关拨到 PROG 模式,然后

在 Qutuars 下载模式设置为 AS 模式,选择 pof 文件下载,这样直接下载到

EPCS16 Configure 芯片中,每次复位,会根据 EPCS16 里面的内容重新烧写

Cyclone II 芯片。

关于管脚分配

当我们创建一个 FPGA 用户系统的时候,到最后要做的工作就是下载,在

下载之前必须根据芯片的型号分配管脚,这样才能将程序中特定功能的管脚与实

际中的 FPGA 片外硬件电路一一对应。

通常的管脚分配使用的是拖拽法,然而在一个庞大的系统中,这样是非常

的不现实,可以使用 CSV 文件分配法,方法是在 Qurtus II 的 Assignment 菜单

下面的 Import Assignment 项中,定位到要分配的管脚文件即可(对于做 Nios

核 必 的 通 用 管 脚 分 配 , 可 以 参 照

de2_system\DE2_lab_exercises\DE2_pin_assignments.csv 文件),这里有个

前提,就是你的顶层文件管脚命名必须与 CSV 文件中管脚一致。所以顶层文件

如果用 Verilog 来写的话那将更加的方便,当然这是对于对于做 Nios 核而言的,

你可以直接从 Demo 中拷贝一个顶层文件作为你的顶层。只要稍加修改即可,

�

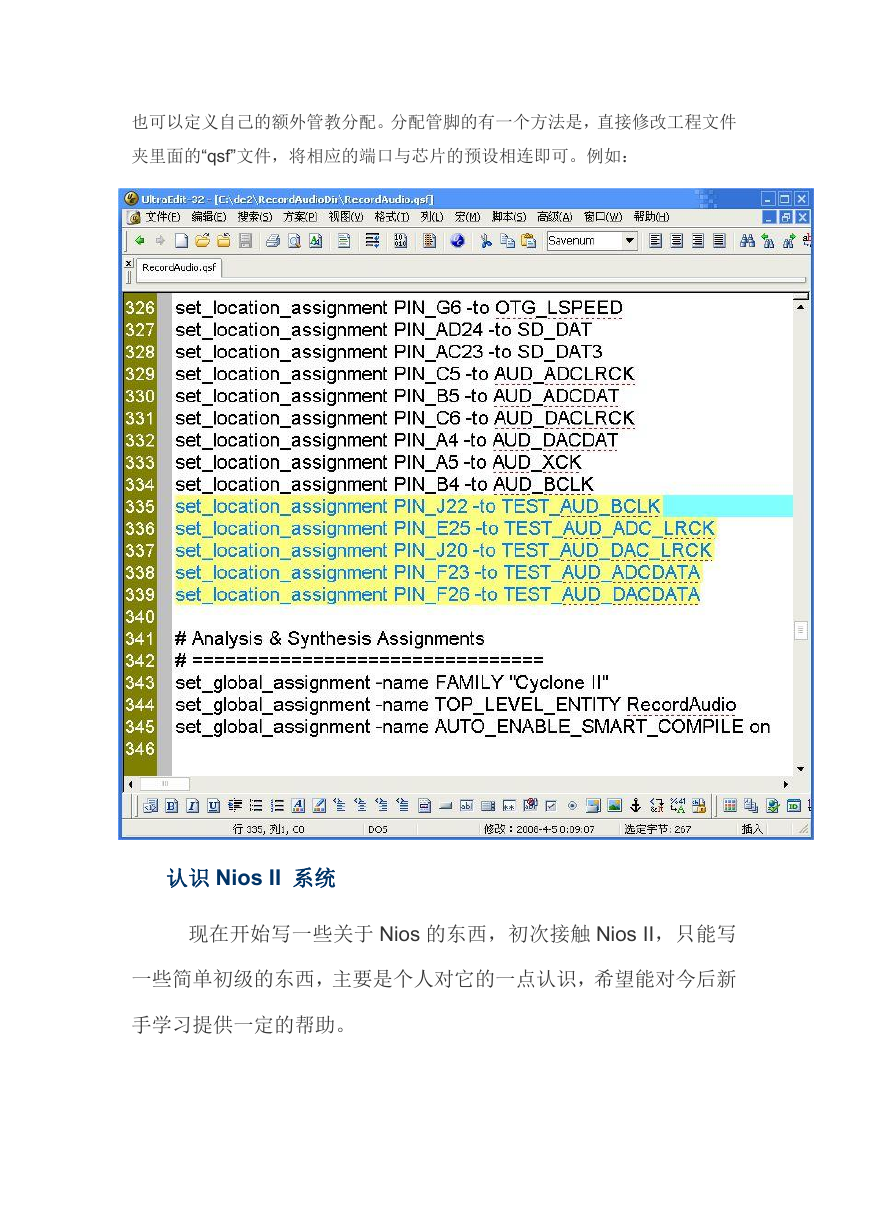

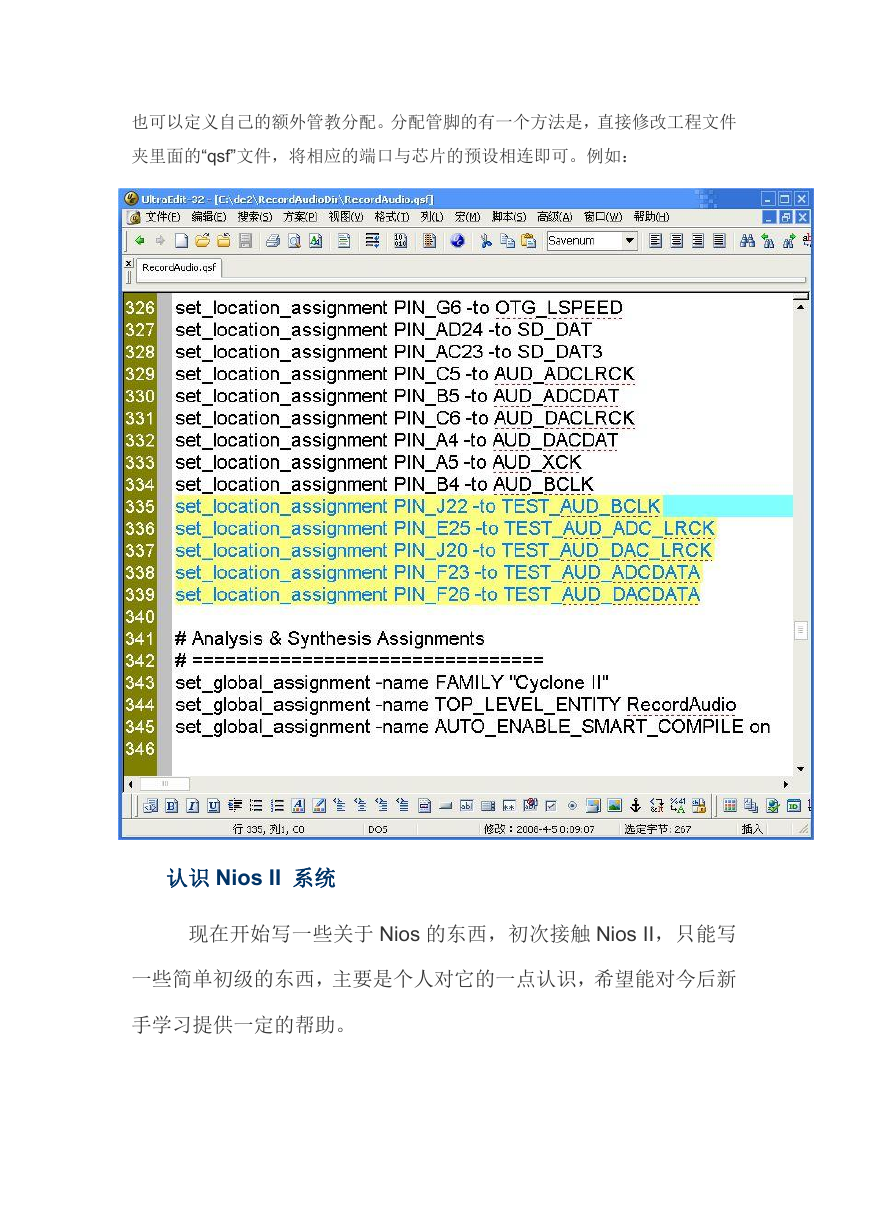

也可以定义自己的额外管教分配。分配管脚的有一个方法是,直接修改工程文件

夹里面的“qsf”文件,将相应的端口与芯片的预设相连即可。例如:

认识 Nios II 系统

现在开始写一些关于 Nios 的东西,初次接触 Nios II,只能写

一些简单初级的东西,主要是个人对它的一点认识,希望能对今后新

手学习提供一定的帮助。

�

Nios II ,准确的说,是一个 IP 核,即知识产权核,使用特定的

硬件描叙语言写成的一堆代码罢了,如果不将它烧到特定的 FPGA

或者 CPLD 芯片中是没有任何意义的。

Altera 的 NiosII 软核,说白了就是一个 CPU,内部像其他处理器

一样,都包括指令解码,地址译码,指令队列,中断管理,总线时须

控制,DMA 控制等等。

NiosII 还支持最多两套用户自定义指令集,者可以有用户自定义

模块来实现。

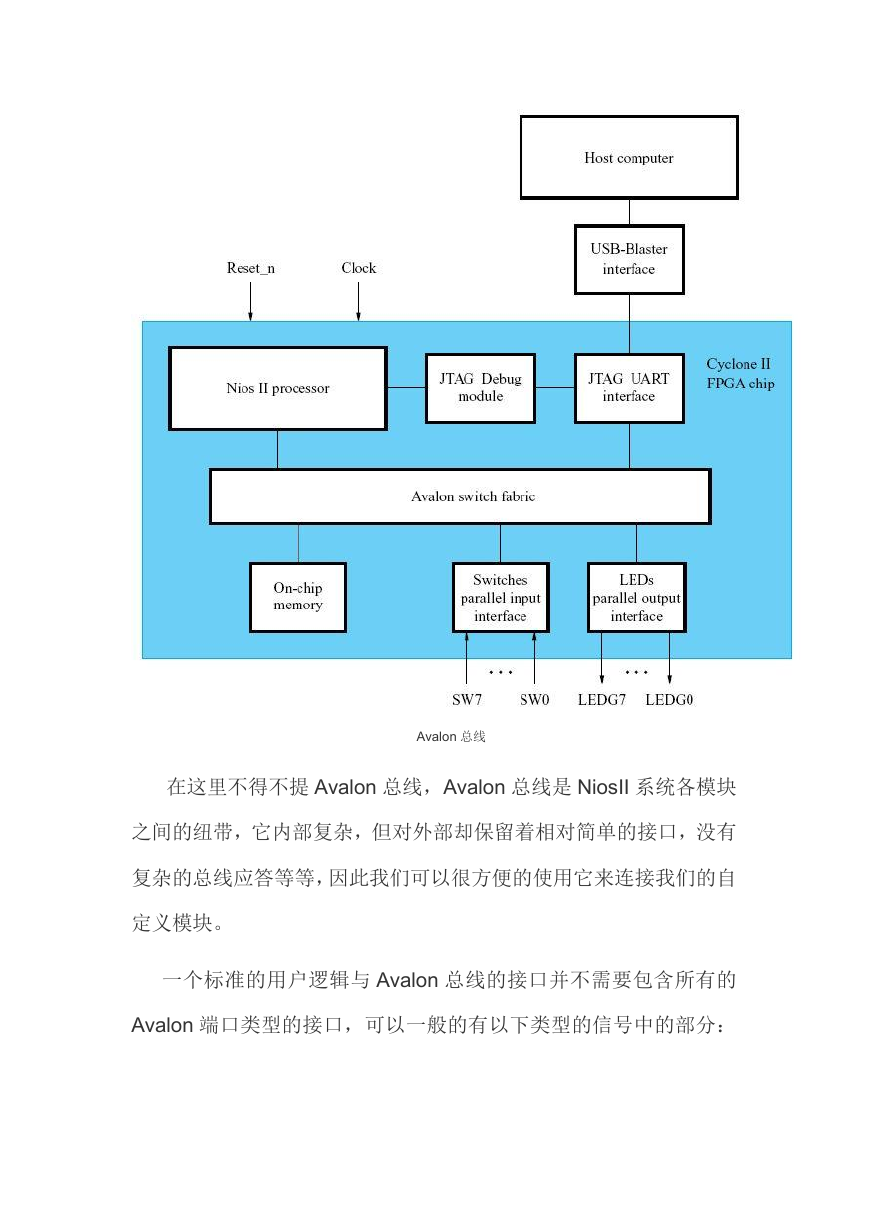

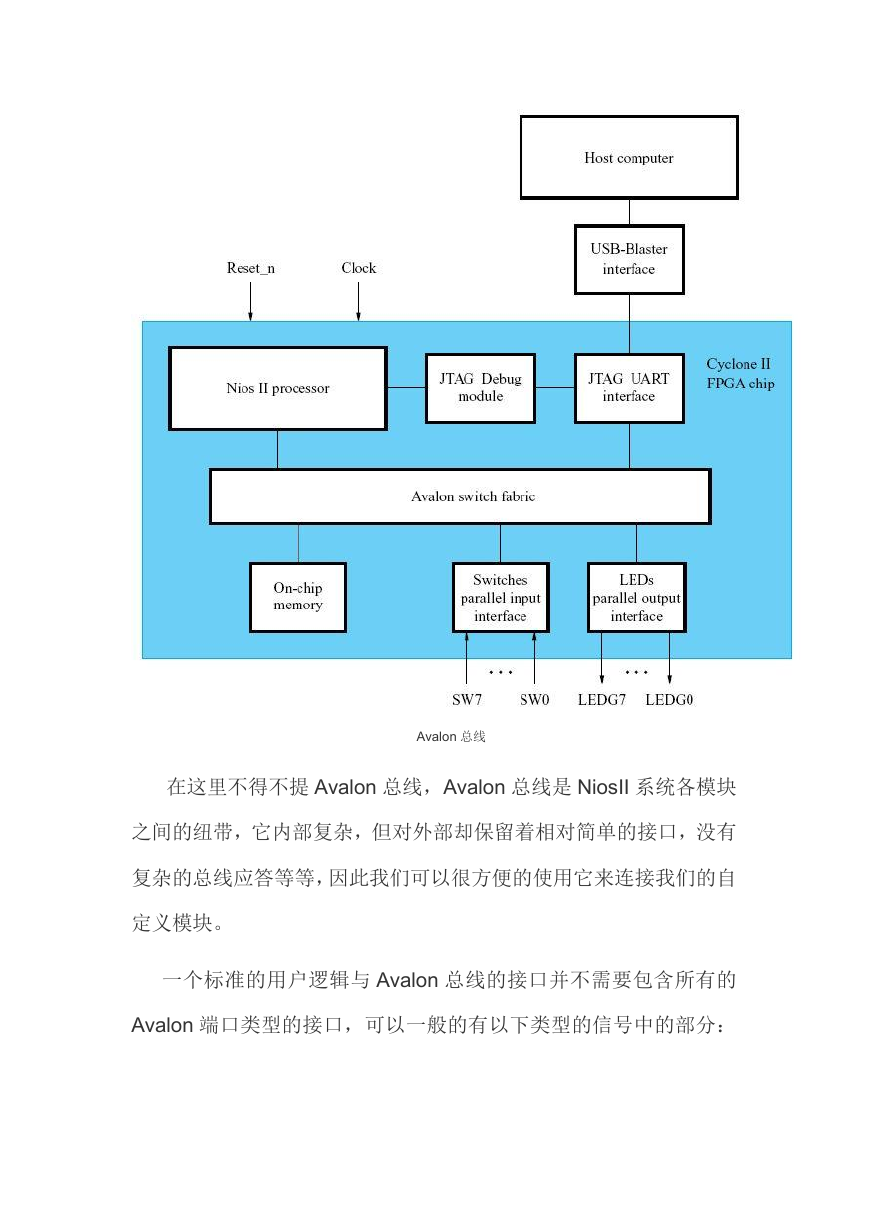

一个 Nios 系统应该至少包括一个 Nios CPU,1 个片上 RAM

(Onchip-RAM),当然还可以添加其他厂商的 IP Core 和自定义用

户逻辑。这些模块共同使用者一块包含有大量逻辑阵列的 FPGA 芯

片 , 组 成 片 上 可 编 程 系 统 , 也 称 为 SOPC ( System On

Programmable Chip)。

这个片上系统然后与外电路连接,构成一个具有特定功能的完整的用

户系统。下面给出一个 NiosII 系统的典型模块图:

�

Avalon 总线

在这里不得不提 Avalon 总线,Avalon 总线是 NiosII 系统各模块

之间的纽带,它内部复杂,但对外部却保留着相对简单的接口,没有

复杂的总线应答等等,因此我们可以很方便的使用它来连接我们的自

定义模块。

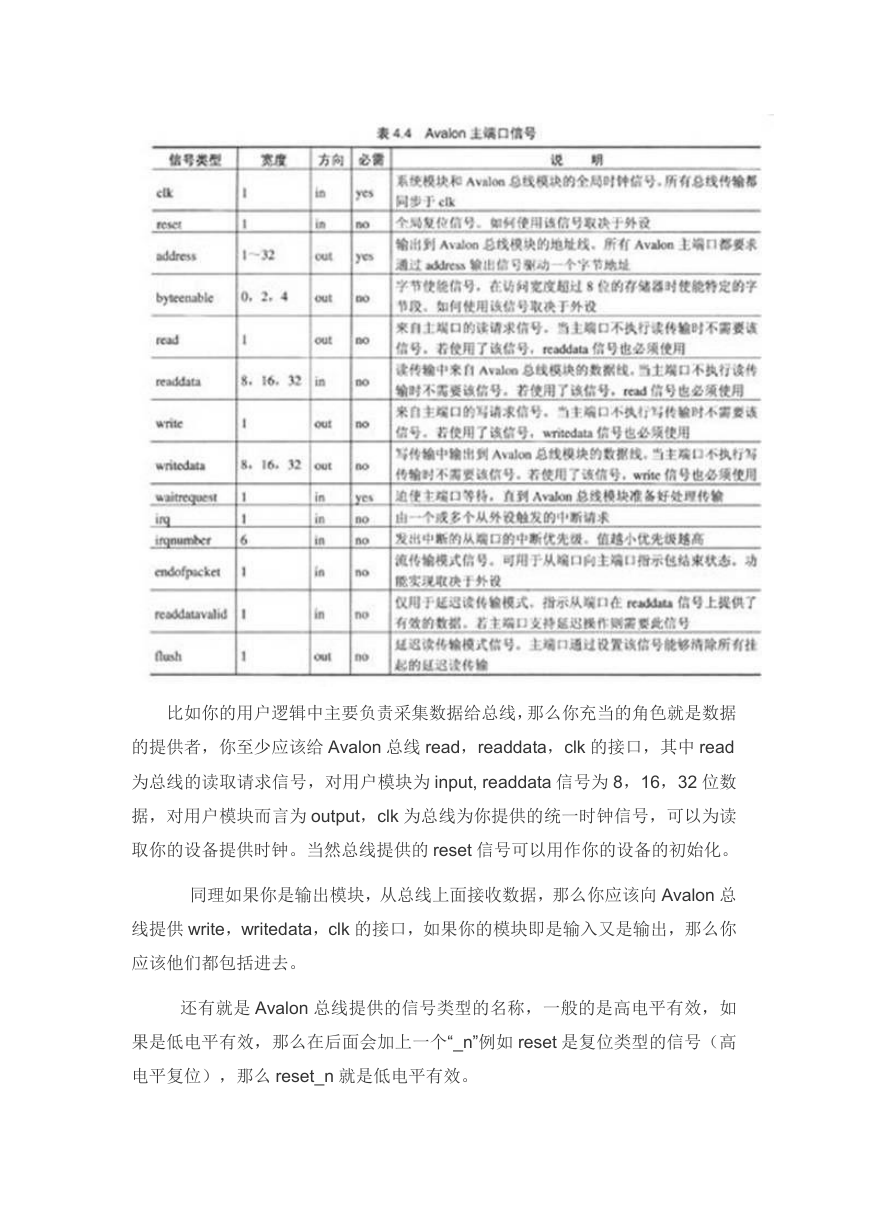

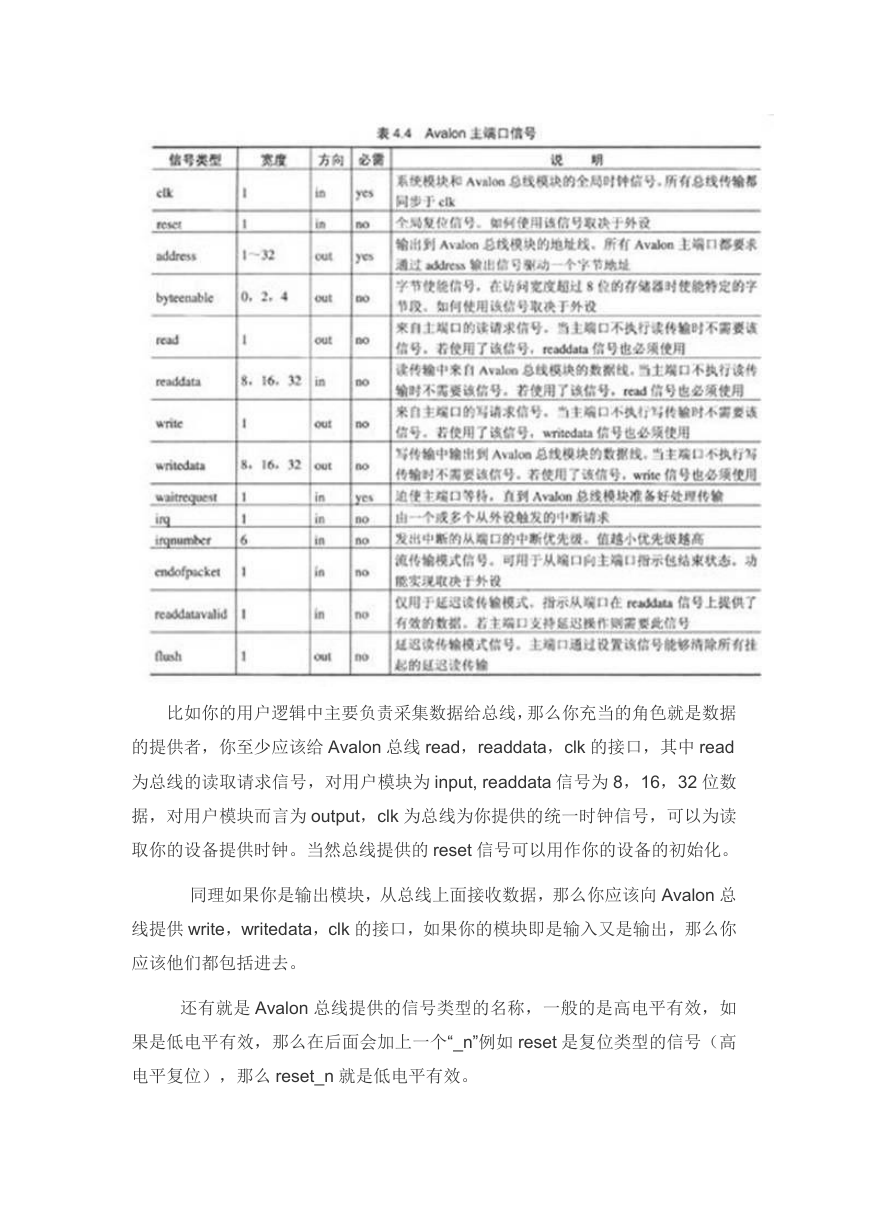

一个标准的用户逻辑与 Avalon 总线的接口并不需要包含所有的

Avalon 端口类型的接口,可以一般的有以下类型的信号中的部分:

�

比如你的用户逻辑中主要负责采集数据给总线,那么你充当的角色就是数据

的提供者,你至少应该给 Avalon 总线 read,readdata,clk 的接口,其中 read

为总线的读取请求信号,对用户模块为 input, readdata 信号为 8,16,32 位数

据,对用户模块而言为 output,clk 为总线为你提供的统一时钟信号,可以为读

取你的设备提供时钟。当然总线提供的 reset 信号可以用作你的设备的初始化。

同理如果你是输出模块,从总线上面接收数据,那么你应该向 Avalon 总

线提供 write,writedata,clk 的接口,如果你的模块即是输入又是输出,那么你

应该他们都包括进去。

还有就是 Avalon 总线提供的信号类型的名称,一般的是高电平有效,如

果是低电平有效,那么在后面会加上一个“_n”例如 reset 是复位类型的信号(高

电平复位),那么 reset_n 就是低电平有效。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc