Low Power Methodology

Manual

For System-on-Chip Design

�

Michael Keating • David Flynn • Robert Aitken •

Alan Gibbons • Kaijian Shi

Low Power Methodology

Manual

For System-on-Chip Design

�

David Flynn

ARM Limited

Cambridge

United Kingdom

Alan Gibbons

Synopsys, Inc.

Northampton

United Kingdom

Michael Keating

Synopsys, Inc.

Palo Alto, CA

USA

Robert Aitken

ARM, Inc.

Almaden, CA

USA

Kaijian Shi

Synopsys, Inc.

Dallas, TX

USA

e-ISBN 978-0-387-71819-4

Library of Congress Control Number: 2007928355

ISBN 978-0-387-71818-7

Printed on acid-free paper.

Copyright © 2007 by Synopsys, Inc. & ARM Limited. All rights reserved.

All rights reserved. This work may not be translated or copied in whole or in part without the written

permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY

10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in

connection with any form of information storage and retrieval, electronic adaptation, computer software,

or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this

publication of trade names, trademarks, service marks and similar terms, even if they are not identified as

such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary

rights.

9 8 7 6 5 4 3 2 1

springer.com

�

TRADEMARKS

Synopsys and NanoSim are registered trademarks of Synopsys, Inc.

ARM and AMBA are registered trademarks of ARM Limited.

ARM926EJ-S, ARM1176JZF-S, AHB and APB are trademarks of

ARM Limited. Artisan and Artisan Components are registered

trademarks of ARM Physical IP, Inc.

“ARM” is used to represent ARM Holdings plc; its operating company

ARM Limited; and the regional subsidiaries ARM INC.; ARM KK;

ARM Korea Ltd.; ARM Taiwan; ARM France SAS; ARM Consulting

(Shanghai) Co. Ltd.; ARM Belgium N.V.; AXYS Design Automation

Inc.; AXYS GmbH; ARM Embedded Technologies Pvt. Ltd.; and

ARM, Inc. and ARM Norway, AS.

All other brands or product names are the property of their respective

holders.

DISCLAIMER

All content included in this Low Power Methodology Manual is the

result of the combined efforts of ARM Limited and Synopsys, Inc.

Because of the possibility of human or mechanical error, neither the

authors, ARM Limited, Synopsys, Inc., nor any of their affiliates,

including but not limited to Springer Science+Business Media, LLC,

guarantees the accuracy, adequacy or completeness of any information

contained herein and are not responsible for any errors or omissions, or

for the results obtained from the use of such information. THERE

ARE NO EXPRESS OR IMPLIED WARRANTIES, INCLUDING,

BUT

OF

MERCHANTABILITY OR FITNESS FOR A PARTICULAR

PURPOSE relating to the Low Power Methodology Manual. In no

event shall the authors, ARM Limited, Synopsys, Inc., or their

affiliates be liable for any indirect, special or consequential damages in

connection with the information provided herein.

WARRANTIES

NOT

LIMITED

TO,

�

Table of Contents

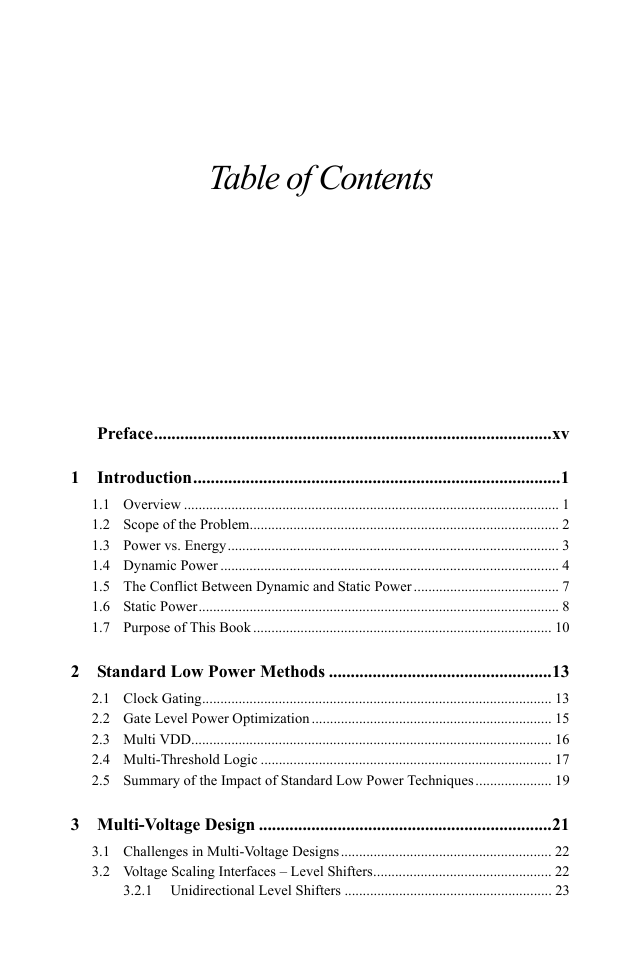

Preface...........................................................................................xv

1 Introduction....................................................................................1

1.1 Overview ....................................................................................................... 1

1.2 Scope of the Problem..................................................................................... 2

1.3 Power vs. Energy........................................................................................... 3

1.4 Dynamic Power ............................................................................................. 4

1.5 The Conflict Between Dynamic and Static Power........................................ 7

1.6 Static Power................................................................................................... 8

1.7 Purpose of This Book .................................................................................. 10

2 Standard Low Power Methods ...................................................13

2.1 Clock Gating................................................................................................ 13

2.2 Gate Level Power Optimization .................................................................. 15

2.3 Multi VDD................................................................................................... 16

2.4 Multi-Threshold Logic ................................................................................ 17

2.5 Summary of the Impact of Standard Low Power Techniques..................... 19

3 Multi-Voltage Design ...................................................................21

3.1 Challenges in Multi-Voltage Designs.......................................................... 22

3.2 Voltage Scaling Interfaces – Level Shifters................................................. 22

3.2.1 Unidirectional Level Shifters ......................................................... 23

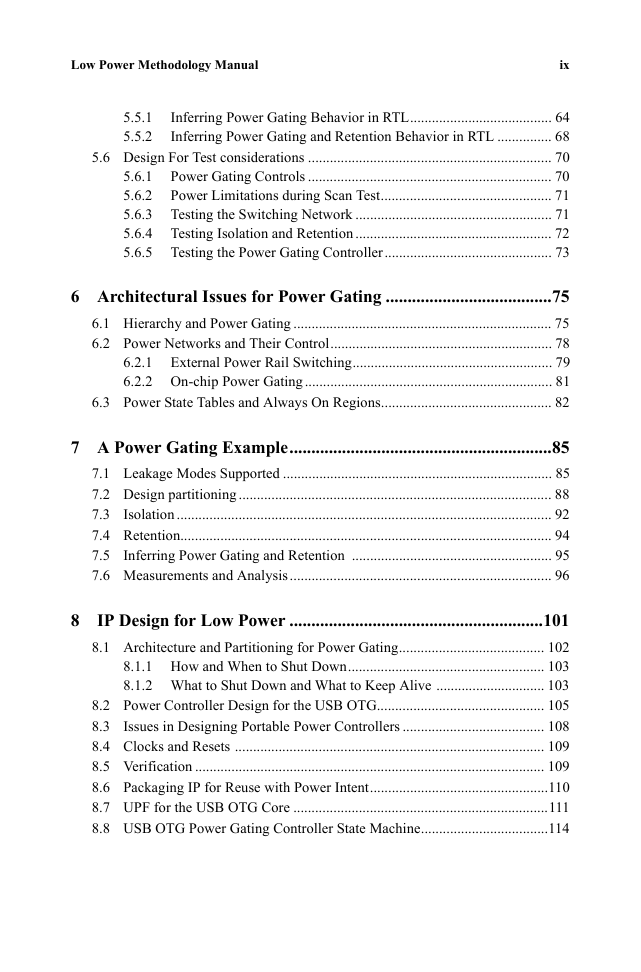

�

viii

Low Power Methodology Manual

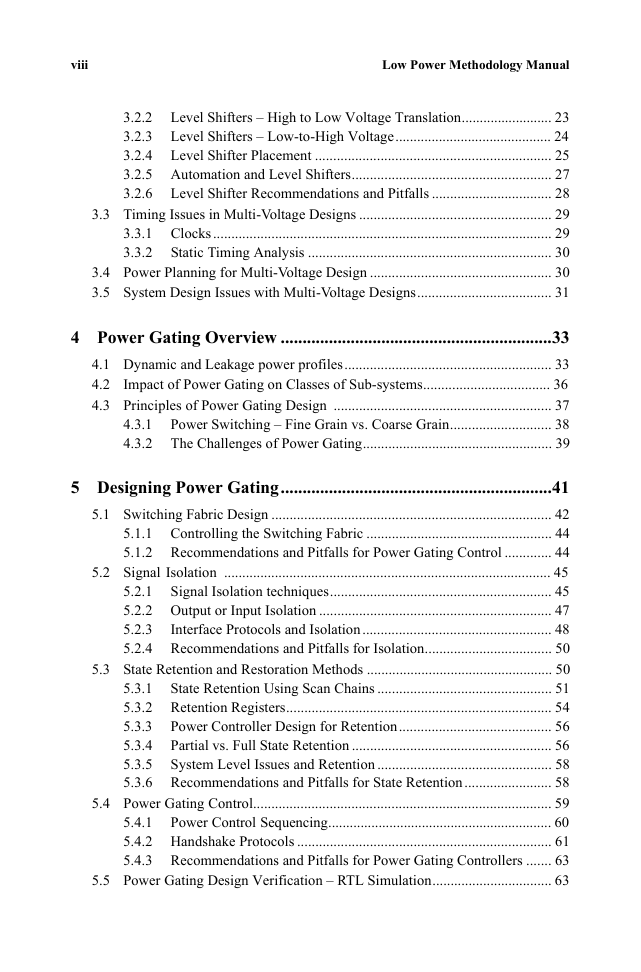

Level Shifters – High to Low Voltage Translation......................... 23

3.2.2

Level Shifters – Low-to-High Voltage........................................... 24

3.2.3

Level Shifter Placement ................................................................. 25

3.2.4

3.2.5 Automation and Level Shifters....................................................... 27

3.2.6

Level Shifter Recommendations and Pitfalls ................................. 28

3.3 Timing Issues in Multi-Voltage Designs ..................................................... 29

3.3.1 Clocks............................................................................................. 29

Static Timing Analysis ................................................................... 30

3.3.2

3.4 Power Planning for Multi-Voltage Design .................................................. 30

3.5 System Design Issues with Multi-Voltage Designs..................................... 31

4 Power Gating Overview ..............................................................33

4.1 Dynamic and Leakage power profiles......................................................... 33

4.2

Impact of Power Gating on Classes of Sub-systems................................... 36

4.3 Principles of Power Gating Design ............................................................ 37

Power Switching – Fine Grain vs. Coarse Grain............................ 38

The Challenges of Power Gating.................................................... 39

4.3.1

4.3.2

5.3

5.2

5 Designing Power Gating..............................................................41

5.1 Switching Fabric Design ............................................................................. 42

5.1.1 Controlling the Switching Fabric ................................................... 44

Recommendations and Pitfalls for Power Gating Control ............. 44

5.1.2

Signal Isolation .......................................................................................... 45

5.2.1

Signal Isolation techniques............................................................. 45

5.2.2 Output or Input Isolation ................................................................ 47

5.2.3

Interface Protocols and Isolation.................................................... 48

5.2.4 Recommendations and Pitfalls for Isolation................................... 50

State Retention and Restoration Methods ................................................... 50

5.3.1

State Retention Using Scan Chains ................................................ 51

5.3.2 Retention Registers......................................................................... 54

5.3.3

Power Controller Design for Retention.......................................... 56

Partial vs. Full State Retention ....................................................... 56

5.3.4

System Level Issues and Retention ................................................ 58

5.3.5

Recommendations and Pitfalls for State Retention........................ 58

5.3.6

Power Gating Control.................................................................................. 59

Power Control Sequencing.............................................................. 60

5.4.1

5.4.2 Handshake Protocols ...................................................................... 61

Recommendations and Pitfalls for Power Gating Controllers ....... 63

5.4.3

Power Gating Design Verification – RTL Simulation................................. 63

5.4

5.5

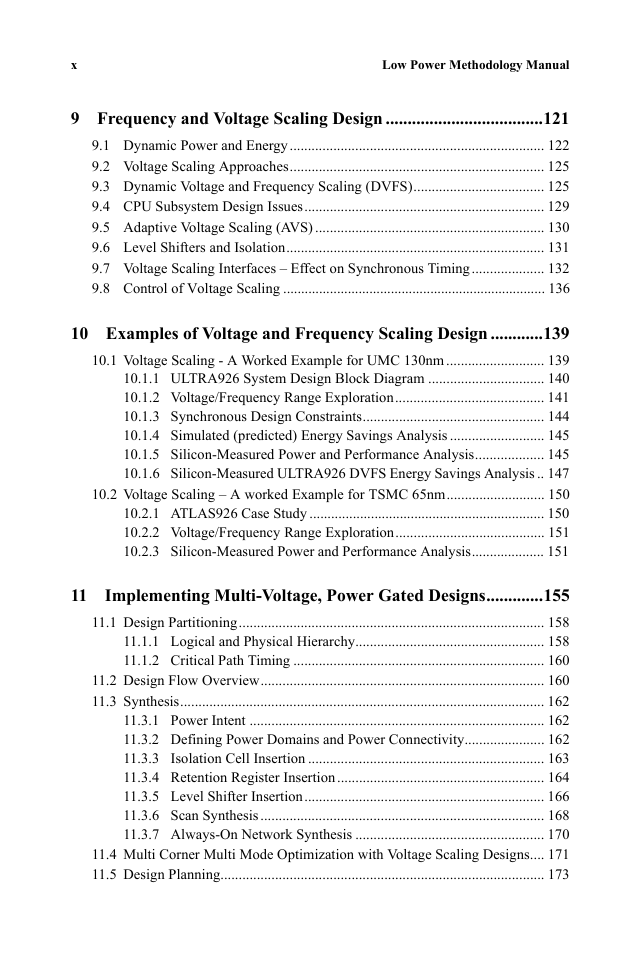

�

Low Power Methodology Manual

ix

5.5.1

5.5.2

Inferring Power Gating Behavior in RTL....................................... 64

Inferring Power Gating and Retention Behavior in RTL ............... 68

5.6 Design For Test considerations ................................................................... 70

Power Gating Controls ................................................................... 70

Power Limitations during Scan Test............................................... 71

Testing the Switching Network ...................................................... 71

Testing Isolation and Retention ...................................................... 72

Testing the Power Gating Controller.............................................. 73

5.6.1

5.6.2

5.6.3

5.6.4

5.6.5

6 Architectural Issues for Power Gating ......................................75

6.1 Hierarchy and Power Gating ....................................................................... 75

Power Networks and Their Control............................................................. 78

6.2

External Power Rail Switching....................................................... 79

6.2.1

On-chip Power Gating.................................................................... 81

6.2.2

6.3 Power State Tables and Always On Regions............................................... 82

7 A Power Gating Example............................................................85

Leakage Modes Supported .......................................................................... 85

7.1

7.2 Design partitioning ...................................................................................... 88

7.3 Isolation ....................................................................................................... 92

7.4 Retention...................................................................................................... 94

7.5 Inferring Power Gating and Retention ....................................................... 95

7.6 Measurements and Analysis........................................................................ 96

8 IP Design for Low Power ..........................................................101

8.1 Architecture and Partitioning for Power Gating........................................ 102

8.1.1 How and When to Shut Down...................................................... 103

What to Shut Down and What to Keep Alive .............................. 103

8.1.2

8.2 Power Controller Design for the USB OTG.............................................. 105

8.3 Issues in Designing Portable Power Controllers ....................................... 108

8.4 Clocks and Resets ..................................................................................... 109

8.5 Verification ................................................................................................ 109

8.6 Packaging IP for Reuse with Power Intent.................................................110

8.7 UPF for the USB OTG Core ......................................................................111

8.8 USB OTG Power Gating Controller State Machine...................................114

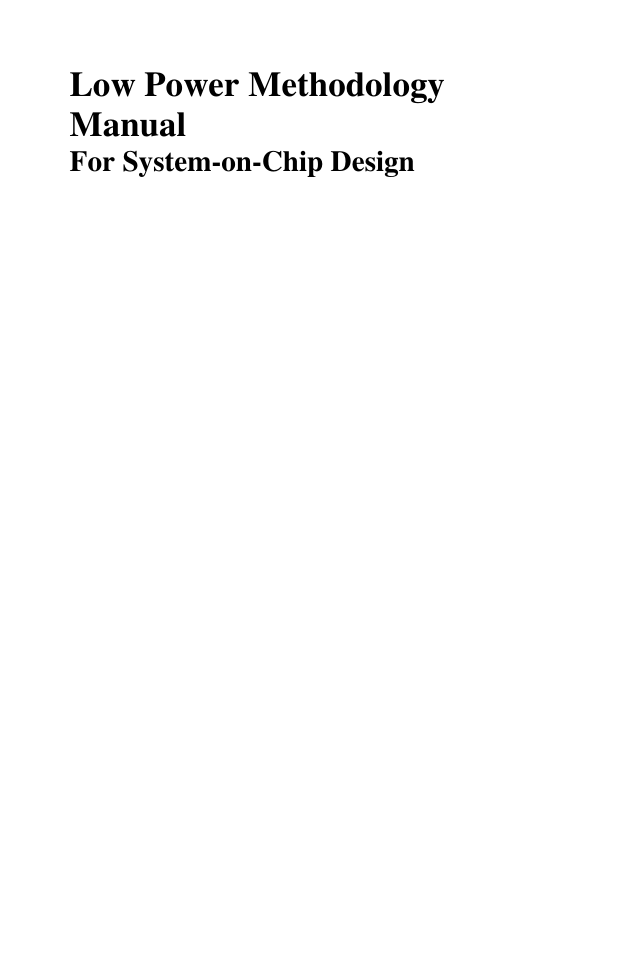

�

x

Low Power Methodology Manual

9 Frequency and Voltage Scaling Design ....................................121

9.1 Dynamic Power and Energy...................................................................... 122

9.2 Voltage Scaling Approaches...................................................................... 125

9.3 Dynamic Voltage and Frequency Scaling (DVFS).................................... 125

9.4 CPU Subsystem Design Issues.................................................................. 129

9.5 Adaptive Voltage Scaling (AVS) ............................................................... 130

9.6 Level Shifters and Isolation....................................................................... 131

9.7 Voltage Scaling Interfaces – Effect on Synchronous Timing.................... 132

9.8

Control of Voltage Scaling ......................................................................... 136

10 Examples of Voltage and Frequency Scaling Design ............139

10.1 Voltage Scaling - A Worked Example for UMC 130nm ........................... 139

10.1.1 ULTRA926 System Design Block Diagram ................................ 140

Voltage/Frequency Range Exploration......................................... 141

10.1.2

10.1.3 Synchronous Design Constraints.................................................. 144

10.1.4 Simulated (predicted) Energy Savings Analysis .......................... 145

Silicon-Measured Power and Performance Analysis................... 145

10.1.5

Silicon-Measured ULTRA926 DVFS Energy Savings Analysis .. 147

10.1.6

10.2 Voltage Scaling – A worked Example for TSMC 65nm........................... 150

ATLAS926 Case Study ................................................................. 150

Voltage/Frequency Range Exploration......................................... 151

Silicon-Measured Power and Performance Analysis.................... 151

10.2.1

10.2.2

10.2.3

11 Implementing Multi-Voltage, Power Gated Designs.............155

11.1 Design Partitioning.................................................................................... 158

11.1.1 Logical and Physical Hierarchy.................................................... 158

11.1.2 Critical Path Timing ..................................................................... 160

11.2 Design Flow Overview.............................................................................. 160

11.3 Synthesis.................................................................................................... 162

11.3.1 Power Intent ................................................................................. 162

11.3.2 Defining Power Domains and Power Connectivity...................... 162

11.3.3 Isolation Cell Insertion ................................................................. 163

11.3.4 Retention Register Insertion......................................................... 164

11.3.5 Level Shifter Insertion.................................................................. 166

11.3.6 Scan Synthesis.............................................................................. 168

11.3.7 Always-On Network Synthesis .................................................... 170

11.4 Multi Corner Multi Mode Optimization with Voltage Scaling Designs.... 171

11.5 Design Planning......................................................................................... 173

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc