本科毕业设计(论文)

题

目: 基于锁相环的数字

频率合成器的研究

院: 信息科学技术学院

业: 电子信息工程

级: 1008021 班

号: 100802128

学

专

班

学

学生姓名: 张慧贤

指导教师:封维忠 职 称:教授

二 O 一 四 年 五 月 十五 日

�

基于锁相环的数字频率合成器

摘 要

伴随着数字通信体系的发展,锁相环的使用愈来愈普及,它用于通讯的接收机当中,其

作用是对接收到的信号进行处理,并从当中提取出某个时钟的相位消息,即关于再次接收

到的信号,仿造出一个时钟信号,使得这两个信号从某种角度来看是相对同步的。

此外,锁相环在频率合成中也具有十分关键的作用。频率合成的参考频率是一个或少

许的高准确度和高稳定度的频率,以此来导出多个或大批的输出频率,这些输出频率的准

确度与稳定度与参考频率是大致一样的。锁相环在通讯、雷达、测控等电子系统中有着很

普遍的应用。锁相环( PLL ) 是频率合成器的最主要部件,锁相环的主要组成部分是相位

比较器( PD) 、压控振荡器( VCO) 、环路滤波器( LP)和参考频率源。

锁相环电路是一种使用外部输入的参考信号来控制环路内部振荡信号反馈控制的电

路。数字锁相环频率发生器根据频率范围和频率间隔的改变可根据具体需要来进行调节,

且输出的信号频率具有较高稳定性和准确性, 可作为离散信号源进行广泛的使用, 也可

用在集成电路中。另外,如用单片机的编程来对分频器的置数端进行控制, 则可以更加方

便的实现频率的调节。

关键词:锁相环;频率合成;反馈控制;分频器

�

Based on the digital phase-locked loop frequency synthesizer

ABSTRACT

With the development of the digital communication system,The Phase-locked loop applied

more and more widely,It is used for the communication receiver,Its role is to process the signals

received, to extract from it a clock phase information,Namely for the received signal, the generic

a clock signal, make the two signals from a certain perspective is synchronous (or coherent).

The phase-locked loop also play an important role in the frequency synthesis, frequency

synthesis is based on one or a small amount of high accuracy and high stability of the standard

frequency reference frequency, multiple or lots of output frequency has been derived, the

accuracy and stability of the output is in line with the reference frequency. In communication,

radar, measurement and control, instrument table, etc have widely used in electronic systems.

Phase-locked loop (PLL) is the core component of a frequency synthesizer, mainly by the phase

comparator (PD), voltage controlled oscillator (VCO), loop filter (LP) and a reference frequency

source.

Phase-locked loop use external input reference signal control loop internal oscillation

signal feedback control circuit. Digital phase locked loop frequency generator due to the

frequency range and frequency interval can be adjusted according to the specific needs, and the

output signal frequency with high stability and accuracy, and can be widely used as discrete

signal source, can also be used for integration. In addition, if use single chip microcomputer to

control the load end of the frequency divider, the adjustment of the frequency can be more easily.

Key words:Phase-locked loop;Frequency synthesis; Feedback control; Divider

�

目录

1 绪论…………………………………………………………………………………..........……………...1

1.1 课题研究的目的及意义……………………………………………………..........................………1

1.2 课题国内外研究的现状和发展趋势..................................................................................................1

1.2.1 锁相环的发展......................……..……….........................….….…………..………..………1

1.2.2 锁相环的国内外研究现状.......................................................................................................2

1.3 锁相环数字频率合成器的工作原理..................................................................................................3

1.3.1 锁相环路的组成与模型............................................................................................................3

1.3.2 设计基本原理及系统框架.......................................................................................................5

1.3.3 主要技术指标...........................................................................................................................6

1.4 论文的主要研究内容和点..................................................................................................................6

1.4.1 主要内容...................................................................................................................................6

1.4.2 主要特点....................................................................................................................................7

2 设计方案….................................…………………………………………………………………………8

2.1 系统分析..................………………………………………………..................……………………8

2.1.1 设计要求.......………..............................................…………………………………………8

2.1.2 可行性分析.............................................................................................................................8

2.2 总体方案设计.....................…………...……………………………………………………………8

2.2.1 系统的组成框图设计............................ .................................................................................8

3 硬件设计……………………………………………………………………………............................…11

3.1 信号源的设计…............................………………………………………………………………...11

3.1.1 555 方波发生器原理…..................................……………………………………………...11

3.1.2 555 信号输入电路..................................................................................................................12

3.2 N 分频的设计…......................…………………………………………………………………..…13

3.3 锁相环参数设计...............................................................................................................................14

4 软件仿真....................................................................................................................................................16

4.1 Protuse 简介.......................................................................................................................................16

4.2 555 信号输入电路的仿真.................................................................................................................16

4.3 总锁相环数字频率合成器的电路仿真...........................................................................................16

5 硬件焊接与调试........................................................................................................................................18

�

5.1 硬件焊接...........................................................................................................................................18

5.1.1 信号源部分电路的焊接..........................................................................................................18

5.1.2 频率合成部分电路的焊接......................................................................................................18

5.2 电路板的调试.....................................................................................................................................19

5.2.1 电路的调试..............................................................................................................................19

5.2.2 数据的测量与分析..................................................................................................................20

6 软件设计....................................................................................................................................................22

6.1 单片机的选择.....................................................................................................................................22

6.2 ATMEL89C51 简介.............................................................................................................................22

6.3 单片机键盘控制计数器.....................................................................................................................23

6.3.1 4×4 矩阵键盘..........................................................................................................................23

6.3.2 矩阵键盘的设计......................................................................................................................24

6.4 单片机液晶显示测频率......................................................................................................................24

6.4.1 1602 液晶显示模块..................................................................................................................25

6.4.2 频率计的设计..........................................................................................................................25

结论 ..............................................…………………………………………….............................……...…26

致谢 ...............................................................................................…………………………………...……27

参考文献.........................................................................…………………………………………………...28

附录 A ...........................................................................................................................................................29

附录 B............................................................................................................................................................35

�

南京林业大学本科生毕业设计(论文)

1 绪论

1.1 课题研究的目的及意义

频率合成器有三种模式,分别为直接式频率合成器、直接数字式频率合成器及锁相频

率合成器。前两种属于开环系统,是以有频率改变时间短,分辨率高等优点。而第三种锁

相频率合成器是一种闭环系统,其频率转换时间和分辨率均不如前两种好,但它的优点是

构造简单,制作成本低。并且输出频率的准确度与前两种不分上下。因此,对锁相环频率

计的研究是十分有意义的。

本毕业设计的主要目的是采用锁相环 CD4046 和可编程二进制 1/N 计数器 CD4522 设计

一种数字频率合成器,设计电路,焊接调试,并在此基础上进行拓展,采用单片机控制分

频器的置数端和显示部分。

1.2 课题国内外研究的现状和发展趋势

1.2.1 锁相环的发展

锁相环结合了自动频率控制技术和自动相位控制技术,人们对锁相环最初的研究开始

于 20 世纪 30 年代,无线电技术在三十年代就开始进入了早起的发展。法国工程师贝尔赛

什(Bellescize)于 1932 发表了一篇关于锁相环路的数学描述和同步检波论,这是历史

上第一次公开发表的对锁相环路的数学描述。锁相技术最初被用于同步接收中,为同步检

波提供了一个与输入信号的载波同频率的本地参考信号,由于这项技术的发展,同步检波

开始能够在低信噪比条件下进行工作,且大大削弱了大信号检波时失真的弊端。所以才得

到了大家的关注,但由于电路设计较为复杂且应用成本较高,早当时没有获得大量的应用。

到了 1943 年,锁相环路第一次在黑白电视接收机烦人同步电路中进行应用,它能够

有效的抑制外部噪声对同步信号的干扰,从而防止因为噪声干扰信号引起的扫描随机触发

而使画面抖动的状况。此后,锁相电路在彩色电视接收机中被用来同步彩色脉冲串。自此,

锁相环路开始获得了使用。

到了五十年代,伴随着空间技术的发展,杰费(Jaffe)和里希廷成功使用锁相环路

来作为导弹信标的跟踪滤波器。他们第一次发表了含有噪声效应的锁相环路线性理论分析

的文章,并成功处理了锁相环路最佳设计的方案。空间技术的发展促进了锁相环理论的进

一步研究大大促进了锁相技术的发展,人们对锁相环路极其理论也有了更深一步的探究。

第 1 页 共 41 页

页

�

南京林业大学本科生毕业设计(论文)

到了六十年代,维特比(Witerbi)钻研了无噪声锁相环路的非线性理论问题,发表

了关于相干通信原理的文章。锁相环最初是分立元件构建,由于技术和成本问题,所以它

只是应用于航天,航空,军事和精密测量仪器。直到 1965 年,伴随半导体技术快速的发

展,第一块锁相环芯片应运而生,之后锁相环才成为一个低成本的多功能组件开始大批应

用于许多的领域。

70 年代,林特赛(Undsy)和查理斯(Chanes)在进行了许多实验的基础上开始了有

噪声的一阶,二阶及高阶 PLL 的非线性理论的研究分析。随着人们对锁相技术的理论和应

用开始了广泛而深刻的探究,数字电路开始代替鉴相器部分,其余的部分仍为模拟电路,

这类锁相环就是最初的数字锁相环(DPLL)。随着数模混合锁相环技能和理论的不断完善

发展,其成为了锁相环的主流。

现在,随着低成本的通信行业,低功耗,高带宽,高数据传输率的要求,集成电路不

断向高集成度,低功耗方向发展。主要的挑战是设计一个合适的电压控制振荡器和分频器。

对于这方面的研究,设计师们一直在提出不同的技术,譬如将压控振荡器和分频器由原来

的串接改进成堆叠结构,DH-PLl 结构等等,由于技术人员的不断探索,锁相环技术的不断

提高,现在具有 50GHz 环锁相环的工作频率。

1.2.2 锁相环的国内外研究现状

LMx243x 系列锁相环芯片,由美国国家半导体在 2003 年 6 月推出,其操作频率达到了

3GHz 以上,适用于无线局域网,移动电话及基站等多种应用方案。

PLL 系列芯片产品由富士通公司研发,大部分在无线通信系统中,设计频率合成器,

用来产生本地震荡。该系列产品覆盖了从 100Mhz 到 6GHz 很宽的频率带宽,。富士通使用

自己的 BiCMOS RF 工艺。同时它也有其他相关的产品,如 VCO,Resonators 等。该公司的

PLL 共有三类可以选择。

2007 年底,我国的浩凯微电子有限公司研发出了具有完全自主知识产权的高性能时钟

锁相环 IP 系列产品,目前该系列产品已通过了 MPW 硅验证。该锁相环系列选用全新的结

构,独一无二的高荷泵和差分 VCO 的设计,通过抑制电源和衬底噪声对 VCO 的影响来保证

PLL 有很低的噪声,差分 VCO 的特别设计能够使输出时钟维持在 50%的占空,因为不要倍

频震荡,VCO 本身的功耗可降为常规设计的四分之一,使功耗得到了有效的降低。与国外

比起来,我国的 IC 设计水平相对较为落后,模拟研发的环节更是薄弱。因此,PLL 的技术

几乎被国外垄断,国内很少有企业掌握高性能的 PLL 技术的核心,产品更是少。

第 2 页 共 41 页

页

�

1.3 锁相环数字频率合成器的工作原理

南京林业大学本科生毕业设计(论文)

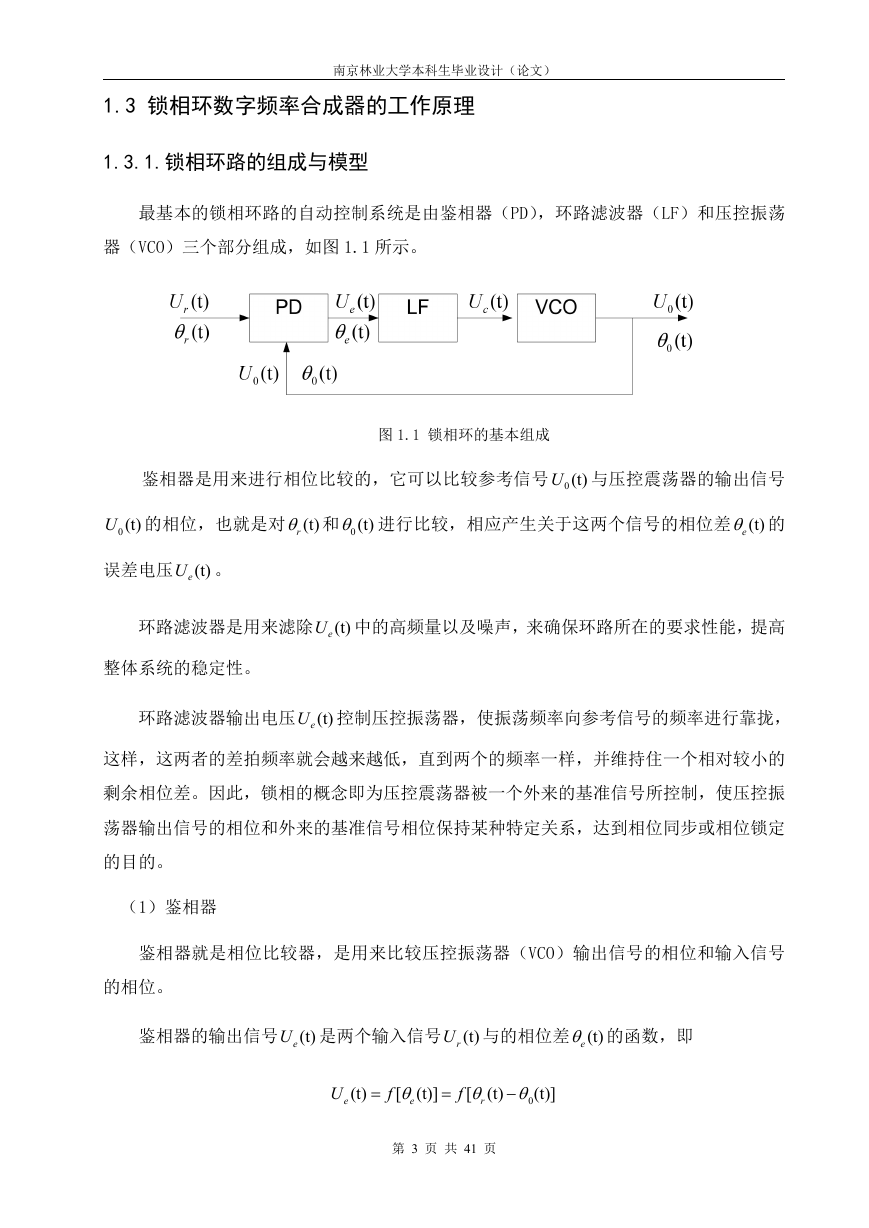

1.3.1.锁相环路的组成与模型

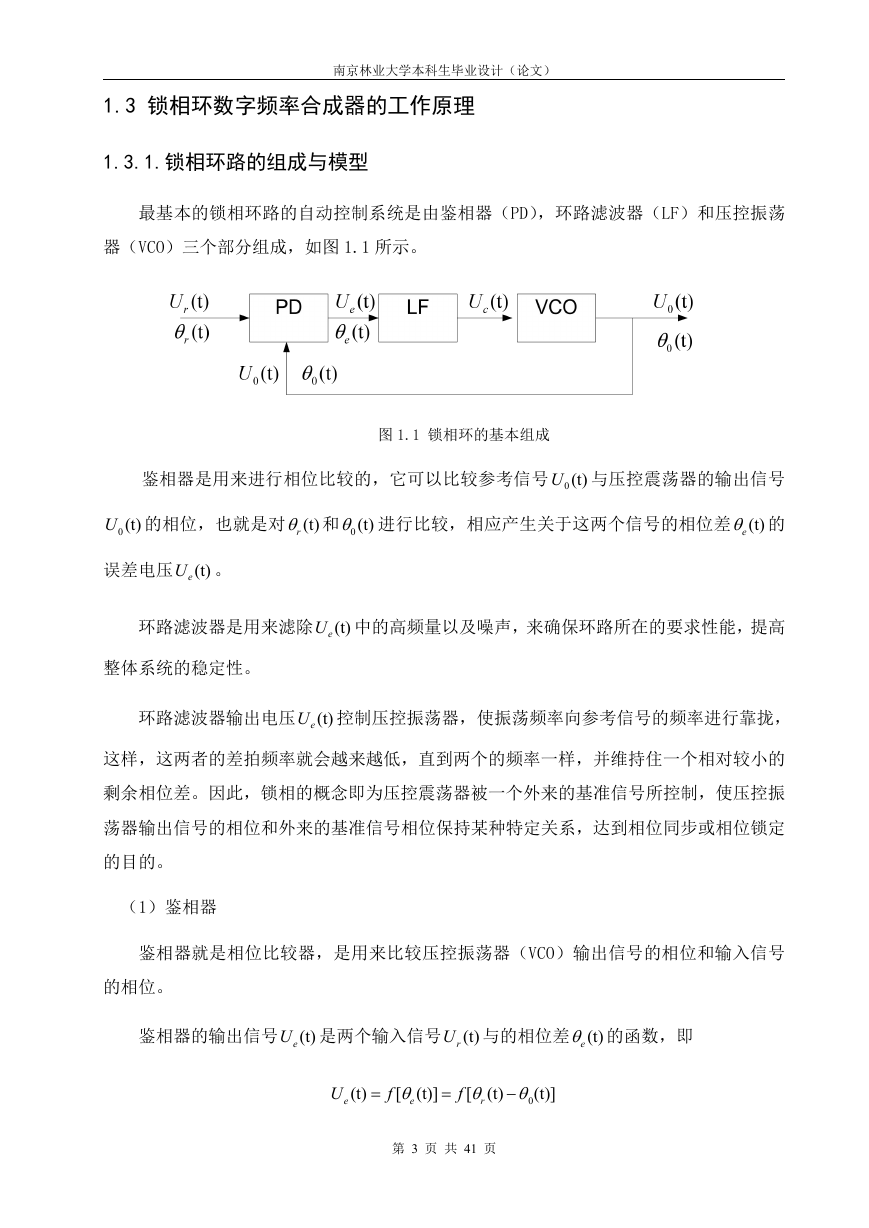

最基本的锁相环路的自动控制系统是由鉴相器(PD),环路滤波器(LF)和压控振荡

器(VCO)三个部分组成,如图 1.1 所示。

图 1.1 锁相环的基本组成

鉴相器是用来进行相位比较的,它可以比较参考信号 0(t)U 与压控震荡器的输出信号

0(t)U 的相位,也就是对 (t)

r 和 0(t) 进行比较,相应产生关于这两个信号的相位差 (t)

e 的

误差电压 (t)

eU 。

环路滤波器是用来滤除 (t)

eU 中的高频量以及噪声,来确保环路所在的要求性能,提高

整体系统的稳定性。

环路滤波器输出电压 (t)

eU 控制压控振荡器,使振荡频率向参考信号的频率进行靠拢,

这样,这两者的差拍频率就会越来越低,直到两个的频率一样,并维持住一个相对较小的

剩余相位差。因此,锁相的概念即为压控震荡器被一个外来的基准信号所控制,使压控振

荡器输出信号的相位和外来的基准信号相位保持某种特定关系,达到相位同步或相位锁定

的目的。

(1)鉴相器

鉴相器就是相位比较器,是用来比较压控振荡器(VCO)输出信号的相位和输入信号

的相位。

鉴相器的输出信号 (t)

eU 是两个输入信号 (t)

rU 与的相位差 (t)

e 的函数,即

U

e

(t)

f

[

e

(t)]

f

[

0

r

(t)

(t)]

第 3 页 共 41 页

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc