2

2

2

2

2

2

第 37 卷第 4 期

2007 年 8 月

微 电 子 学

Microelect ronics

Vol

37 , No . 4

Aug

2007

Matlab 环境下的全数字锁相环仿真模型

(东南大学 国家专用集成电路系统工程技术研究中心 , 南京 210096)

陈 鑫 , 邓小莺

摘 要 : 由于锁相环工作频率高 ,用 SPICE 对锁相环进行仿真 ,数据量大 ,仿真时间长。而在设计

初期 ,往往并不需要很精确的结果。因此 ,为了提高锁相环设计效率 ,有必要为其建立一个高效的仿

真模型。在总结前人提出的一些锁相环仿真模型的基础上 ,用 Matlab 语言构建了一种新的适用于全

数字锁相环的仿真模型 ;对全数字锁相环版图进行了 SPICE 仿真 ,与该模型的仿真结果相验证。

关键词 : 全数字锁相环 ; Matlab ; 仿真模型

中图分类号 : TN402 ; TN79 + 2 文献标识码 : A 文章编号 :1004

3365 (2007) 04

0489

05

Behavioral Modeling of All

Digital PLL in Matlab Environment

( N ational A S I C S ystem En gi neeri ng Research Center , S out heast Uni versit y , N anj i n g 210096 , P. R. Chi na)

C H EN Xin , D EN G Xiao

ying

Abstract : In order to reduce design time , a high efficiency model is needed for PLL design. Based on previous

models for PLL , a new behavioral model for all

digital PLL in Matlab environment is presented. And a SPICE simu

lation is made on layout of the all

Key words : All

EEACC : 1265Z

locked loop ; Matlab ; Behavioral model

digital PLL for comparison.

digital p hase

1 引 言

最近几年 ,片上系统 ( SOC) 获得了长足的发

展 。作为时钟恢复电路和频率合成电路的核心部

件 ———锁相环电路 ( PLL) ,也受到了广泛的关注 。

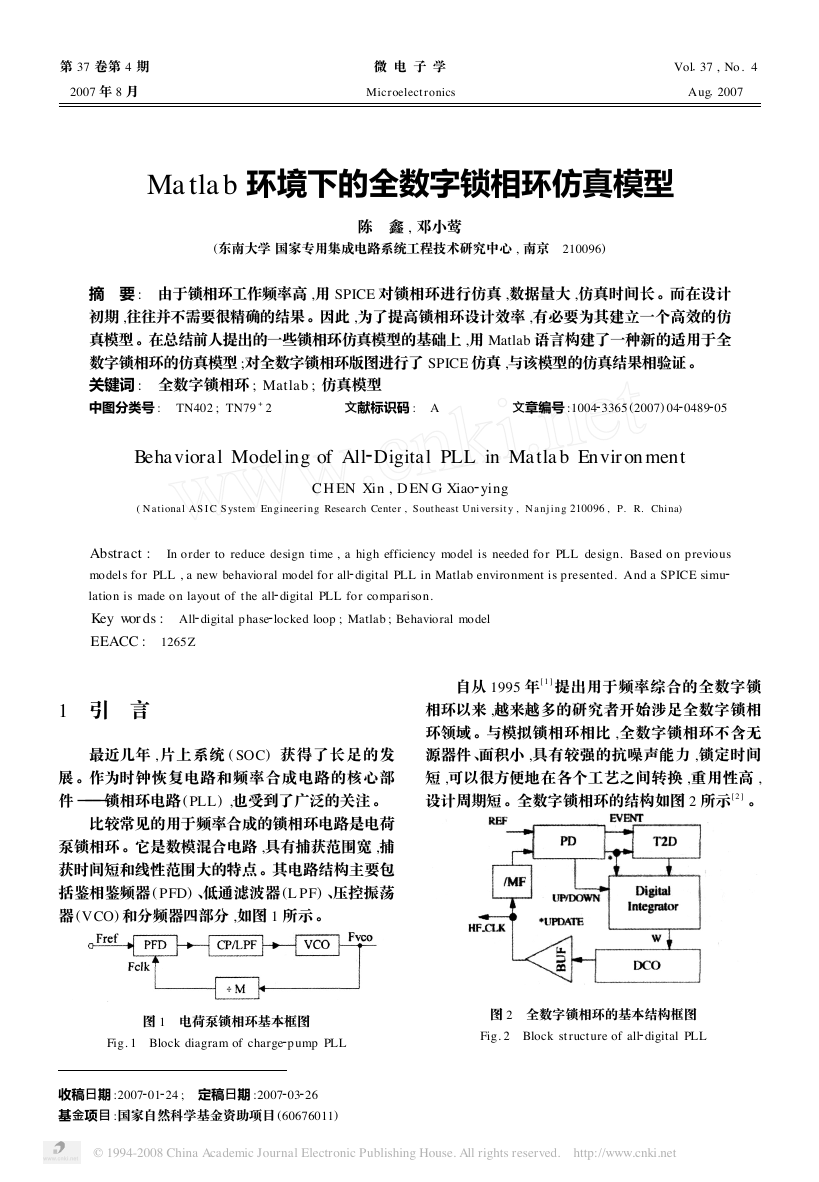

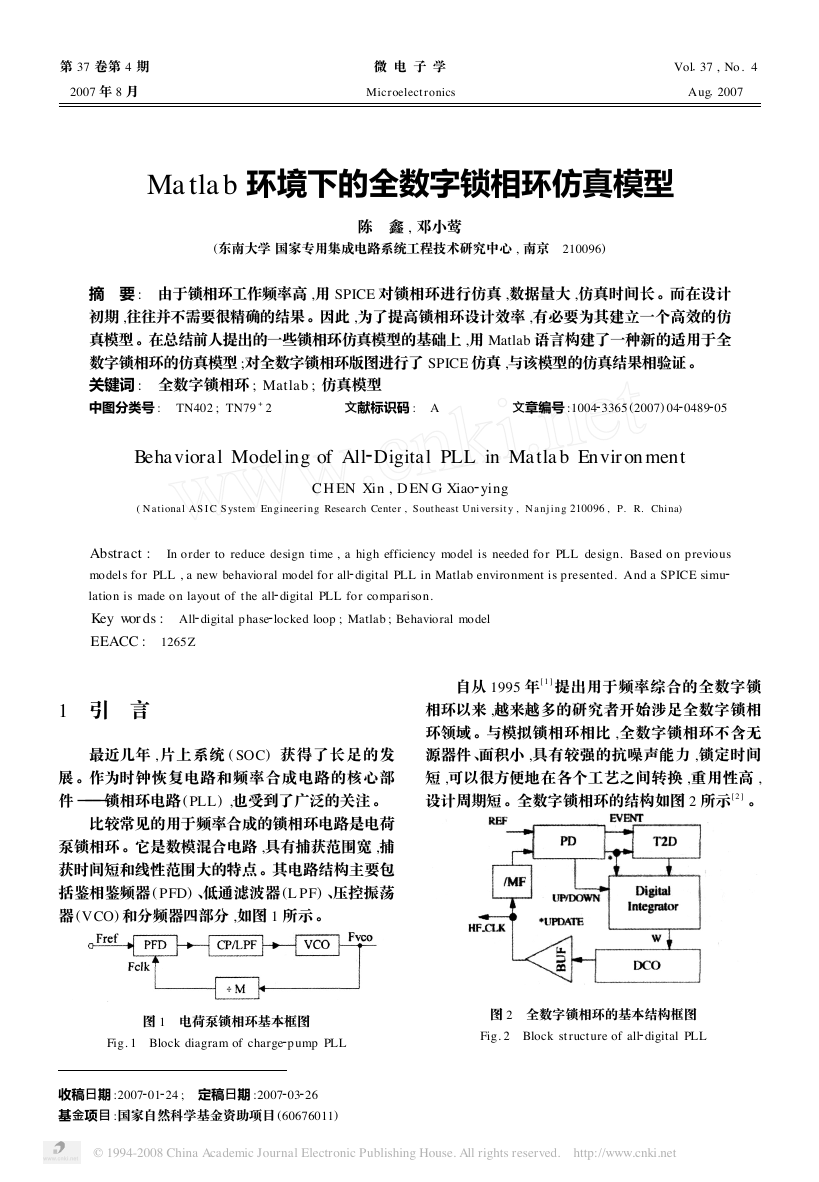

比较常见的用于频率合成的锁相环电路是电荷

泵锁相环 。它是数模混合电路 ,具有捕获范围宽 ,捕

获时间短和线性范围大的特点 。其电路结构主要包

括鉴相鉴频器 ( PFD) 、低通滤波器 (L PF) 、压控振荡

器 (VCO) 和分频器四部分 ,如图 1 所示 。

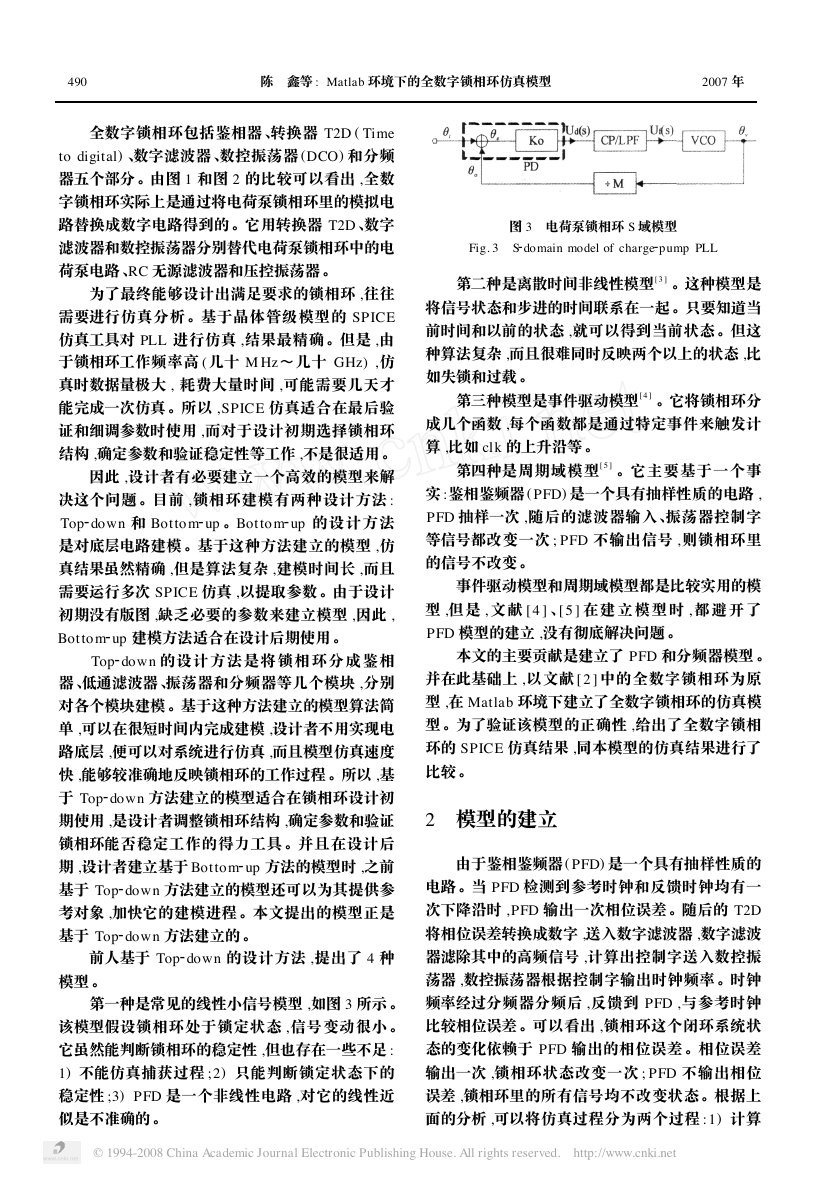

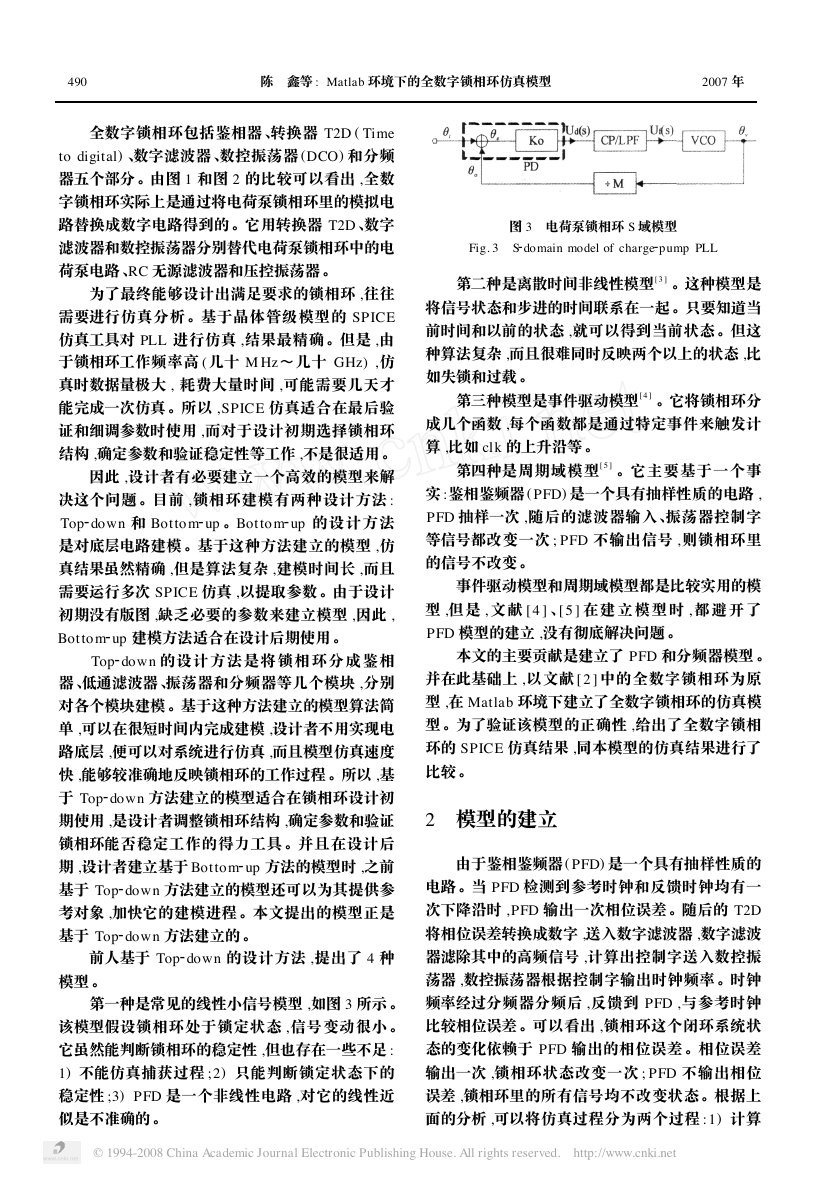

自从 1995 年[ 1 ] 提出用于频率综合的全数字锁

相环以来 ,越来越多的研究者开始涉足全数字锁相

环领域 。与模拟锁相环相比 ,全数字锁相环不含无

源器件 、面积小 ,具有较强的抗噪声能力 ,锁定时间

短 ,可以很方便地在各个工艺之间转换 ,重用性高 ,

设计周期短 。全数字锁相环的结构如图 2 所示[ 2 ] 。

图 1 电荷泵锁相环基本框图

Fig. 1 Block diagram of charge

pump PLL

图 2 全数字锁相环的基本结构框图

Fig. 2 Block structure of all

digital PLL

收稿日期 :2007

基金项目 :国家自然科学基金资助项目 (60676011)

24 ; 定稿日期 :2007

26

01

03

© 1994-2008 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

�

490

陈 鑫等 : Matlab 环境下的全数字锁相环仿真模型

2007 年

全数字锁相环包括鉴相器 、转换器 T2D ( Time

to digital) 、数字滤波器 、数控振荡器 (DCO) 和分频

器五个部分 。由图 1 和图 2 的比较可以看出 ,全数

字锁相环实际上是通过将电荷泵锁相环里的模拟电

路替换成数字电路得到的 。它用转换器 T2D 、数字

滤波器和数控振荡器分别替代电荷泵锁相环中的电

荷泵电路 、RC 无源滤波器和压控振荡器 。

down 和 Bottom

up 。Bottom

Top

为了最终能够设计出满足要求的锁相环 ,往往

需要进行仿真分析 。基于晶体管级模型的 SPICE

仿真工具对 PLL 进行仿真 ,结果最精确 。但是 ,由

于锁相环工作频率高 (几十 M Hz~几十 GHz) ,仿

真时数据量极大 , 耗费大量时间 ,可能需要几天才

能完成一次仿真 。所以 , SPICE 仿真适合在最后验

证和细调参数时使用 ,而对于设计初期选择锁相环

结构 ,确定参数和验证稳定性等工作 ,不是很适用 。

因此 ,设计者有必要建立一个高效的模型来解

决这个问题 。目前 ,锁相环建模有两种设计方法 :

up 的设计方法

Top

是对底层电路建模 。基于这种方法建立的模型 ,仿

真结果虽然精确 ,但是算法复杂 ,建模时间长 ,而且

需要运行多次 SPICE 仿真 ,以提取参数 。由于设计

初期没有版图 ,缺乏必要的参数来建立模型 ,因此 ,

Bottom

up 建模方法适合在设计后期使用 。

down 的设计方法是将锁相 环分 成鉴 相

器 、低通滤波器 、振荡器和分频器等几个模块 ,分别

对各个模块建模 。基于这种方法建立的模型算法简

单 ,可以在很短时间内完成建模 ,设计者不用实现电

路底层 ,便可以对系统进行仿真 ,而且模型仿真速度

快 ,能够较准确地反映锁相环的工作过程 。所以 ,基

于 Top

down 方法建立的模型适合在锁相环设计初

期使用 ,是设计者调整锁相环结构 ,确定参数和验证

锁相环能否稳定工作的得力工具 。并且在设计后

期 ,设计者建立基于 Bottom

up 方法的模型时 ,之前

基于 Top

down 方法建立的模型还可以为其提供参

考对象 ,加快它的建模进程 。本文提出的模型正是

基于 Top

down 方法建立的 。

前人基于 Top

down 的设计方法 ,提出了 4 种

模型 。

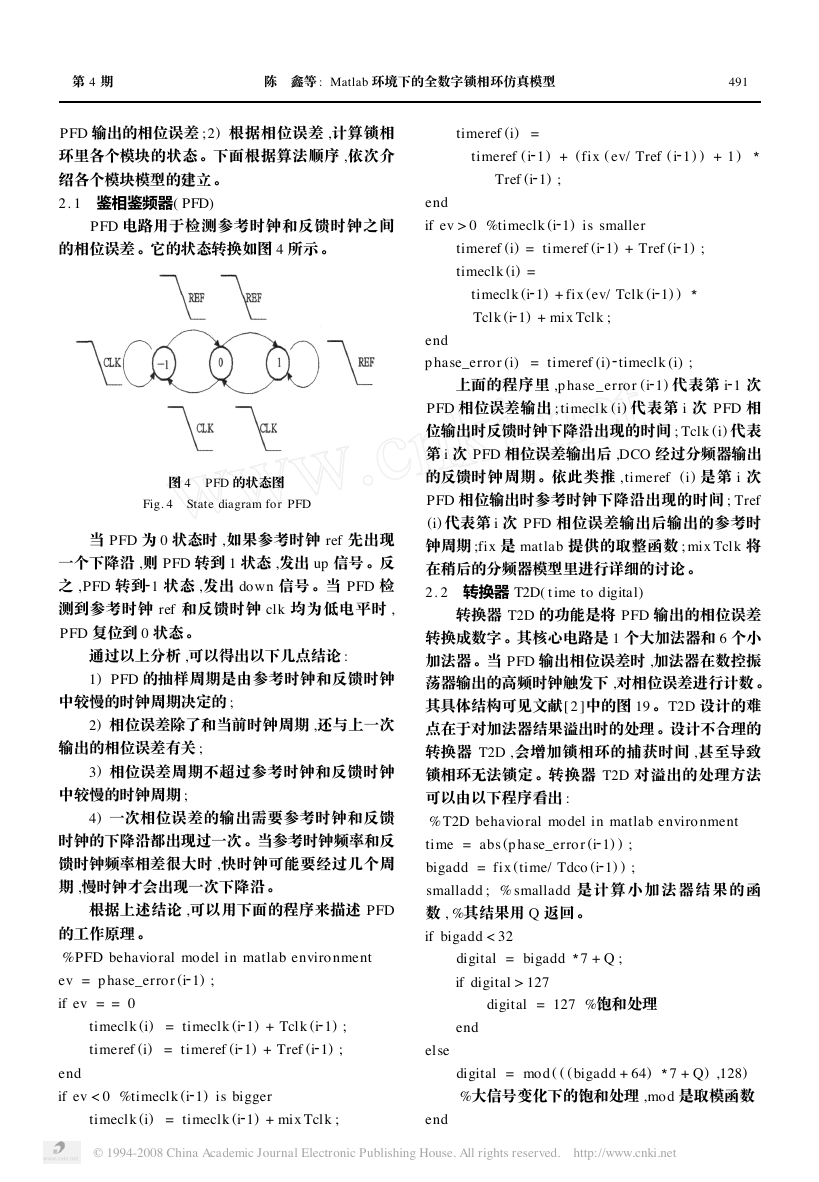

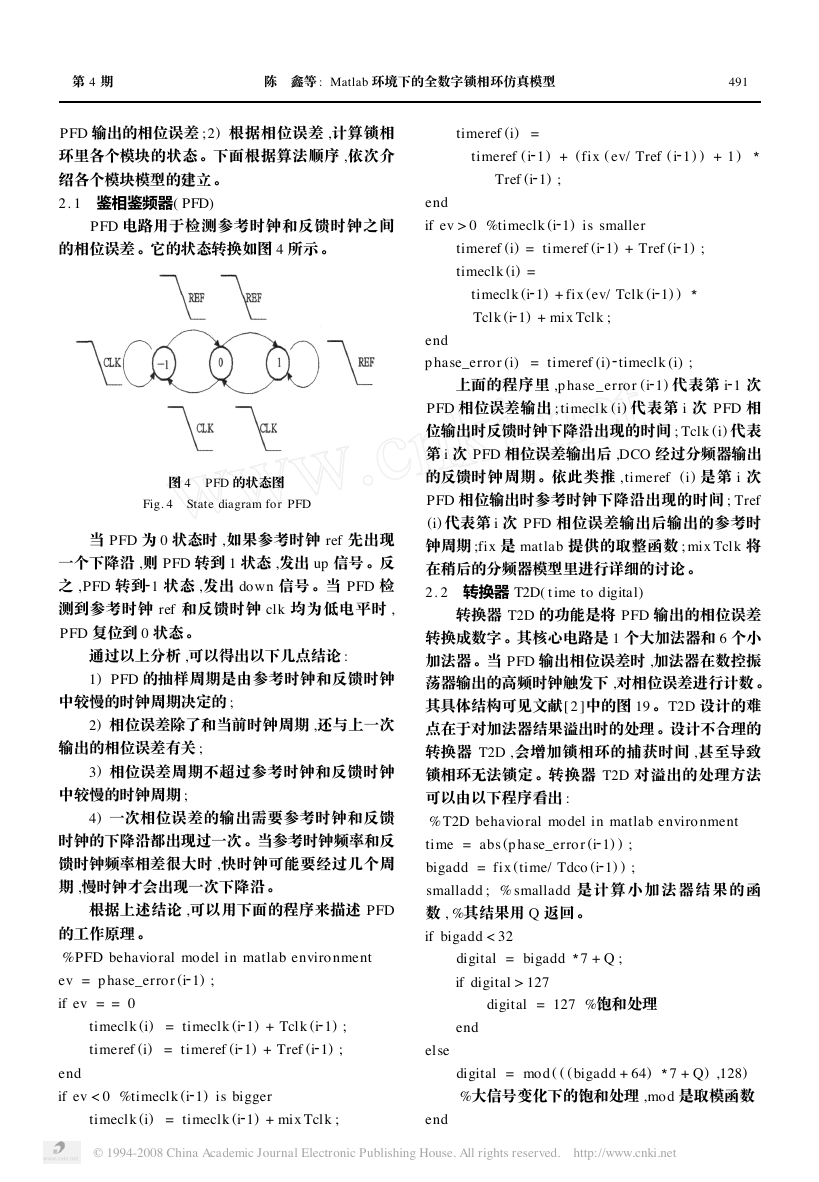

第一种是常见的线性小信号模型 ,如图 3 所示 。

该模型假设锁相环处于锁定状态 ,信号变动很小 。

它虽然能判断锁相环的稳定性 ,但也存在一些不足 :

1) 不能仿真捕获过程 ; 2) 只能判断锁定状态下的

稳定性 ;3) PFD 是一个非线性电路 ,对它的线性近

似是不准确的 。

图 3 电荷泵锁相环 S 域模型

Fig. 3 S

domain model of charge

pump PLL

第二种是离散时间非线性模型[ 3 ] 。这种模型是

将信号状态和步进的时间联系在一起 。只要知道当

前时间和以前的状态 ,就可以得到当前状态 。但这

种算法复杂 ,而且很难同时反映两个以上的状态 ,比

如失锁和过载 。

第三种模型是事件驱动模型[ 4 ] 。它将锁相环分

成几个函数 ,每个函数都是通过特定事件来触发计

算 ,比如 clk 的上升沿等 。

第四种是周期域模型[ 5 ] 。它主要基于一个事

实 :鉴相鉴频器 ( PFD) 是一个具有抽样性质的电路 ,

PFD 抽样一次 ,随后的滤波器输入 、振荡器控制字

等信号都改变一次 ; PFD 不输出信号 ,则锁相环里

的信号不改变 。

事件驱动模型和周期域模型都是比较实用的模

型 ,但是 , 文 献 [ 4 ] 、[ 5 ] 在 建 立 模 型 时 , 都 避 开 了

PFD 模型的建立 ,没有彻底解决问题 。

本文的主要贡献是建立了 PFD 和分频器模型 。

并在此基础上 ,以文献 [ 2 ] 中的全数字锁相环为原

型 ,在 Matlab 环境下建立了全数字锁相环的仿真模

型 。为了验证该模型的正确性 ,给出了全数字锁相

环的 SPICE 仿真结果 ,同本模型的仿真结果进行了

比较 。

2 模型的建立

由于鉴相鉴频器 ( PFD) 是一个具有抽样性质的

电路 。当 PFD 检测到参考时钟和反馈时钟均有一

次下降沿时 , PFD 输出一次相位误差 。随后的 T2D

将相位误差转换成数字 ,送入数字滤波器 ,数字滤波

器滤除其中的高频信号 ,计算出控制字送入数控振

荡器 ,数控振荡器根据控制字输出时钟频率 。时钟

频率经过分频器分频后 ,反馈到 PFD ,与参考时钟

比较相位误差 。可以看出 ,锁相环这个闭环系统状

态的变化依赖于 PFD 输出的相位误差 。相位误差

输出一次 ,锁相环状态改变一次 ; PFD 不输出相位

误差 ,锁相环里的所有信号均不改变状态 。根据上

面的分析 ,可以将仿真过程分为两个过程 : 1) 计算

© 1994-2008 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

�

2

第 4 期

2

2

陈 鑫等 : Matlab 环境下的全数字锁相环仿真模型

3

491

2

2

2

PFD 输出的相位误差 ;2) 根据相位误差 ,计算锁相

环里各个模块的状态 。下面根据算法顺序 ,依次介

绍各个模块模型的建立 。

2. 1 鉴相鉴频器( PFD)

PFD 电路用于检测参考时钟和反馈时钟之间

的相位误差 。它的状态转换如图 4 所示 。

图 4 PFD 的状态图

Fig. 4 State diagram for PFD

当 PFD 为 0 状态时 ,如果参考时钟 ref 先出现

一个下降沿 ,则 PFD 转到 1 状态 ,发出 up 信号 。反

之 ,PFD 转到

1 状态 ,发出 down 信号 。当 PFD 检

测到参考时钟 ref 和反馈时钟 clk 均为低电平时 ,

PFD 复位到 0 状态 。

通过以上分析 ,可以得出以下几点结论 :

1) PFD 的抽样周期是由参考时钟和反馈时钟

中较慢的时钟周期决定的 ;

2) 相位误差除了和当前时钟周期 ,还与上一次

输出的相位误差有关 ;

3) 相位误差周期不超过参考时钟和反馈时钟

中较慢的时钟周期 ;

4) 一次相位误差的输出需要参考时钟和反馈

时钟的下降沿都出现过一次 。当参考时钟频率和反

馈时钟频率相差很大时 ,快时钟可能要经过几个周

期 ,慢时钟才会出现一次下降沿 。

根据上述结论 ,可以用下面的程序来描述 PFD

的工作原理 。

%PFD behavioral model in matlab environment

ev = p hase_error (i

if ev = = 0

1) ;

timeclk (i) = timeclk (i

timeref (i) = timeref (i

1) + Tclk (i

1) + Tref (i

1) ;

1) ;

end

if ev < 0 %timeclk (i

1) is bigger

timeclk (i) = timeclk (i

1) + mix Tclk ;

timeref (i) =

timeref (i

Tref (i

1) + (fix ( ev/ Tref ( i

1) ;

1) ) + 1)

end

if ev > 0 %timeclk (i

1) is smaller

timeref (i) = timeref (i

timeclk (i) =

timeclk (i

1) + fix (ev/ Tclk (i

1) )

1) + Tref (i

1) ;

Tclk (i

1) + mix Tclk ;

end

p hase_error (i) = timeref (i)

timeclk (i) ;

1) 代表第 i

上面的程序里 ,p hase_error (i

1 次

PFD 相位误差输出 ; timeclk (i) 代表第 i 次 PFD 相

位输出时反馈时钟下降沿出现的时间 ; Tclk (i) 代表

第 i 次 PFD 相位误差输出后 ,DCO 经过分频器输出

的反馈时钟周期 。依此类推 , timeref

(i) 是第 i 次

PFD 相位输出时参考时钟下降沿出现的时间 ; Tref

(i) 代表第 i 次 PFD 相位误差输出后输出的参考时

钟周期 ;fix 是 matlab 提供的取整函数 ; mix Tclk 将

在稍后的分频器模型里进行详细的讨论 。

2. 2 转换器 T2D( time to digital)

转换器 T2D 的功能是将 PFD 输出的相位误差

转换成数字 。其核心电路是 1 个大加法器和 6 个小

加法器 。当 PFD 输出相位误差时 ,加法器在数控振

荡器输出的高频时钟触发下 ,对相位误差进行计数 。

其具体结构可见文献[ 2 ]中的图 19 。T2D 设计的难

点在于对加法器结果溢出时的处理 。设计不合理的

转换器 T2D ,会增加锁相环的捕获时间 ,甚至导致

锁相环无法锁定 。转换器 T2D 对溢出的处理方法

可以由以下程序看出 :

%T2D behavioral model in matlab enviro nment

time = abs (p hase_error (i

bigadd = fix (time/ Tdco (i

smalladd ; % smalladd 是计算 小加 法器结 果的 函

数 , %其结果用 Q 返回 。

if bigadd < 32

1) ) ;

1) ) ;

7 + Q ;

digital = bigadd

if digital > 127

digital = 127 %饱和处理

end

else

end

digital = mod ( ( (bigadd + 64)

7 + Q) ,128)

%大信号变化下的饱和处理 ,mod 是取模函数

© 1994-2008 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

�

3

492

陈 鑫等 : Matlab 环境下的全数字锁相环仿真模型

2007 年

2. 3 数字低通滤波器

数字低通滤波器和模拟滤波器的作用一样 ,都

是滤除高频信号 ,降低振荡器输出频率的抖动 。文

献[ 2 ]中所用的滤波器传输函数为 :

F( z) =

1 - 0. 5 Z - 1

1 - Z - 1

(1)

将滤波器传输函数 ( (1) 式) 转换到差分公式 :

y ( n) = y ( n - 1) + x ( n) - 0. 5 x ( n - 1)

(2)

通过 (2) 式 ,可以很容易地推出数字低通滤波器

模型 ,这里不再赘述 。

2. 4 数控振荡器( DCO)

数控振荡器的电路是奇数个反相器首尾相连组

成一个振荡环 。为了得到可调的输出频率 ,可以在

每一级反相器上并联大量的反相器 。这些反相器由

控制字来决定关还是开 ,进而改变每一级的延时 ,以

达到改变振荡频率的效果 。

通常 ,设计者会用

f osc = f 0 + Kosc w ( n)

(3)

建立振荡器模型 。但是 , 在实际锁相环电路中 , Kosc

并不是一个常数 ,它是随振荡器输出频率的变化而

变化的 。因此 ,如果振荡器采用 (3) 式这个模型 ,则

整个模型的误差很大 。本文 DCO 的模型是根据理

论计算 ,以查找表的形式建立起来的 。限于篇幅 ,这

里不再详细叙述 。

2. 5 分频器

分频器的作用是将振荡器的输出频率分频输

出 。一般的建模者往往会忽视这个模块模型的建

立 ,简单地用

f = f osc / M

或者

T = Tosc

M

(4)

(5)

来代替 (假设其分频系数为 M) 。

上述公式在 PLL 锁定状态下是近似成立的 ,但

是 ,当 PLL 处于捕获状态时误差很大 。这是由分频

器的工作原理决定的 。分频器本质上是一个模值可

变的计数器 ,假设其模值为 N 。振荡器每输出一个

周期 ,分频器里的计数值加 1 ,当计数值达到 N 时 ,

分频器的输出电平取反 。很容易看出 ,当振荡器输

出信号的周期不变时 ,分频器输出时钟的周期为 :

2 N

T = Tosc

(6)

但是 ,当振荡器输出信号的周期变化很大时 ,

(6) 式很明显是不成立的 。因此 ,在锁相环处于捕获

状态时 ,不能根据 (4) 式或 (5) 式建立分频器模型 。

本文建立的模型如下 :

%Divider behavioral model in matlab environment

%该锁相环相位输出到振荡器输出时钟周期改变需

要三个振荡周期

delayn = 3 ;

ev = p hase_error (i

if ev < 0 %timeclk (i

1) is bigger

1) ;

1) + (M

Tdco (i

mix Tclk = delayn

Tdco (i) ; % M 是分频系数

% Tdco (i) 代表第 i 次 PFD 输出相位误差后 ,

%DCO 输出时钟的周期

delayn)

end

if ev > 0 %timeclk (i

1) is smaller

1) ) ;

delta = mod (ev , Tclk (i

smalln = fix (delta/ Tdco (i

mix Tclk = (smalln + delayn)

(M

delayn)

smalln

Tdco (i) ;

1) ) ;

Tdco (i

1) +

end

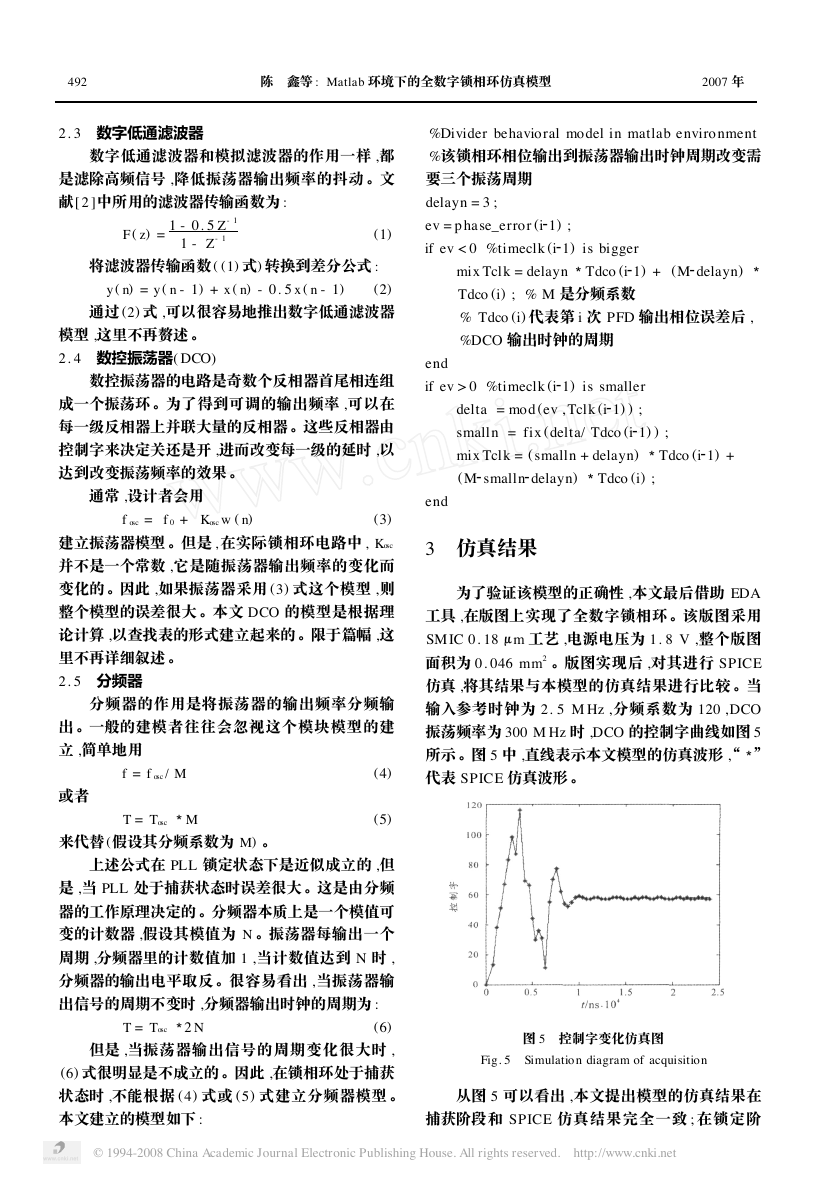

3 仿真结果

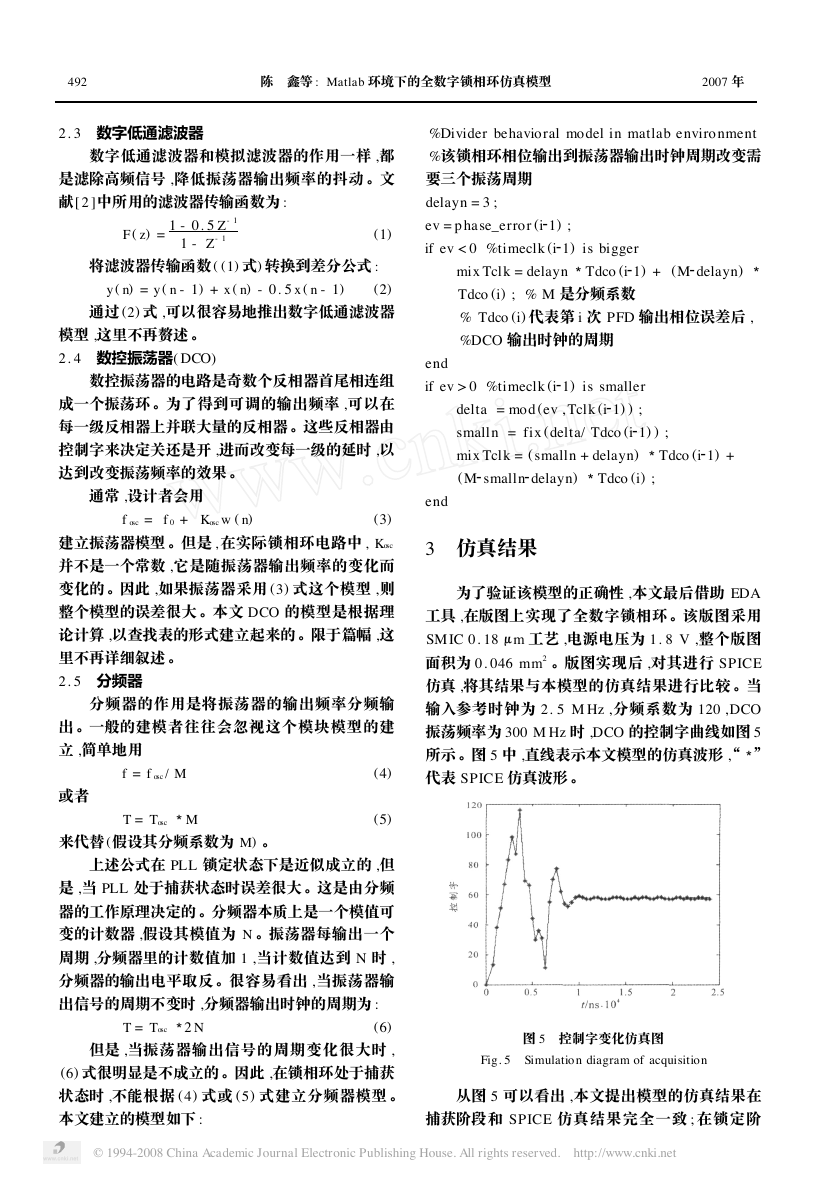

为了验证该模型的正确性 ,本文最后借助 EDA

工具 ,在版图上实现了全数字锁相环 。该版图采用

SM IC 0. 18μm 工艺 ,电源电压为 1. 8 V ,整个版图

面积为 0. 046 mm2 。版图实现后 ,对其进行 SPICE

仿真 ,将其结果与本模型的仿真结果进行比较 。当

输入参考时钟为 2. 5 M Hz ,分频系数为 120 ,DCO

振荡频率为 300 M Hz 时 ,DCO 的控制字曲线如图 5

所示 。图 5 中 ,直线表示本文模型的仿真波形 ,“

”

代表 SPICE 仿真波形 。

图 5 控制字变化仿真图

Fig. 5 Simulation diagram of acquisition

从图 5 可以看出 ,本文提出模型的仿真结果在

捕获阶段和 SPICE 仿真结果完全一致 ; 在锁定阶

© 1994-2008 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

�

2

2

2

493

2

第 4 期

陈 鑫等 : Matlab 环境下的全数字锁相环仿真模型

段 ,本文模型与 SPICE 仿真结果略有出入 。这是因

为本模型是自顶向下建模的 ,没有涉及到具体电路 。

但是 ,控制字的差错最多也只是 1 位偏差 ,因此 ,该

模型的精度在设计初期是可以接受的 。更精确的仿

真模型有赖于下一步的工作 ,即在本文模型的帮助

下 ,建立基于 Bottom

up 方法的仿真模型 。

4 结 论

本文基于 PFD 具有抽样性质的原理 ,以文献

[ 2 ]中的全数字锁相环为原型 ,建立了 Matlab 环境

下的全数字锁相环模型 。从仿真结果看 ,本文提出

的模型与实际全数字锁相环电路的 SPICE 模型基

本一致 ,可以在设计初期起到替代 SPICE 仿真 ,缩

短设计周期 ,提高设计效率的作用 。此外 ,该模型还

具有一定的拓展性 ,可以仿真参考时钟抖动对锁相

环的影响 ,并利用 Matlab 强大的可视化图形表现功

能 ,以直观的形式显示出来 。另外 ,由于电荷泵锁相

环也用到 PFD 和分频器 ,因此 ,本文建立 PFD 和分

频器模型的思想对电荷泵锁相环模型的建立也有着

一定的参考意义 。

(上接第 488 页)

6 结 论

本文介绍了一种改进的测试输入波形 ,很好地

解决了正弦波的频率波动问题 ,抑制了输入噪声对

ADC 的干扰 。由于其精确的频率设定能力 ,这种方

法可以用在实时片上测试系统中 。对相干采样的结

果直接进行傅里叶变换 ,减少了加窗所带来的软件

和硬件开销 。改进的傅里叶变换方法能够有效地提

高数据处理精度 , 更好地反映 ADC 的精度 , 提高

ADC 测试的准确性 。

参 考 文 献 :

参 考 文 献 :

[ 1 ]

[ 2 ]

[ 3 ]

422.

locked loop with 50

performance microp rocessors [J ].

digital

cycle lock time suitable for

IEEE J Sol

J IM D , GERALD G , J IM L , et al. An all

p hase

high

Sta Circ , 1995 , 30 (4) : 412

T HOMAS O , PETER N. A digitally controlled PLL

for SoC applications [J ].

IEEE J Sol Sta Circ , 2004 ,

39 (5) : 751

PASCAL A , MIC HA EL P K , C HRISTIAN M , et al.

Behavioral modeling of charge pump p hased locked

loop s [ C] / /

In : Proc IEEE Int Symp Circ and Syst .

Orlando , FL , U SA. 1999 , Vol. 1 : 375

760.

378.

[ 4 ] DIEGO A , VAL EN TINO L , CARL A V. Behavioral

analysis of charge

In : Proc IEEE

Int Symp Circ and Syst . Rio de J aneiro , Brazil. 1995 ,

Vol. 2 : 13

pump PLL’s [ C] / /

16.

[ 5 ] NORMAN K J . Cycle

locked loop s [ C] / / Southwest Symp Mixed

Design. San Diego , CA , U SA. 2000 : 77

82.

domain simulator for phase

Signal

作者简介 :陈 鑫 (1982 - ) ,男 (汉族) ,江

苏镇江人 ,博士研究生 ,2005 年于东南大

学电子工程学院获学士学位 ,研究方向为

片上系统 ( SOC) 。

78.

[ 3 ] KOLL

sine wave test s of ADCs [ C] / /

IEEE Instrum and

Measur Technol Conf . Anchorage , A K , U SA , 2002 :

73

R I. Evaluation of sine wave test s of ADC’s

f rom windowed data [J ]. Computer Standard Inter

face , 2000 , 22 (5) : 261

268.

[ 4 ] XI Jiang

tao , C H IC HARO J F. A new algorithm for

imp roving the accuracy of periodic signal analysis [J ].

IEEE Trans Instrum and Measur , 1996 , 45 (4) : 827

831.

[ 5 ] 陈莉莉 ,周斌. A/ D 转换芯片的测试环境构成及测试

方法[J ]. 电子技术应用 ,2002 , 28 (12) : 26

29.

[ 6 ] 陈向东 ,黄庆华. 应用 MA TL AB 的矩形时间窗频谱

泄漏分析[J ]. 微计算机信息 (测控自动化) ,2006 , 22

(7

1) : 298

299.

[ 1 ] HARRIS F J . On the use of windows for harmonic

analysis with the discrete Fourier transform [J ]. Proc

IEEE , 1978 , 66 (1) : 51

83.

[ 2 ] BL A IR J J , Nevada B. Selecting test f requencies for

作者简介 :孙 杰 (1982 - ) ,男 (汉族) ,河

南信阳人 ,硕士研究生 ,主要研究方向为

ADC 测试方法及测试系统实现 。

© 1994-2008 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc