Quartus II Handbook, Volume 3 6-28

时钟约束(Clock Specification):

约束所有时钟(包括你的设计中特有的时钟)对准确的时序分析结果而言是

必不可少的。Quartus II TimeQuest Timing Analyzer为各种各样的时钟配置和典型

时钟提供许多SDC命令。

这个章节将介绍 SDC 可用的应用编程接口,以及描述指定的时钟特性。

时钟(Clocks)

使用 create_clock 命令为任何 register, port 或 pin 进行时钟特性描述,使其具

有独一的时钟特性。例 6–2 展示了 create_clock 命令:

Example 6–2. create_clock Command

create_clock

-period

[-name ]

[-waveform ]

[-add]

Table 6–6. create_clock Command Options

选项

-period

[-name ]

[-waveform ]

[-add]

描述

指定时钟周期

指定时钟名称(不一定是约束时钟的节点名称)

指定时钟上升沿/下降沿

可以对一个时钟节点进行多个时钟约束

指定你要约束的时钟(目标节点)

Example 6–3 约束时钟频率 100MHz,占空比 50%,0ns 上升沿,5ns 下降沿。

�Example 6–3. 100MHz Clock Creation

create_clock –period 10 –waveform { 0 5 } clk

Example 6–4 和上例相差 90 度的相位。

Example 6–4. 100MHz Shifted by 90 Degrees Clock Creation

create_clock –period 10 –waveform { 2.5 7.5 } clk_sys

使用 create_clock 命令 约束时钟 缺省的 source Latency 值为 0 。Quartus II

TimeQuest Timing Analyzer 自动为非虚拟时钟(non-virtual clocks)计算时钟网络

延时(clock’s network latency)。

Quartus II Handbook, Volume 3 6-29

生成时钟(Generated Clocks)

Quartus II TimeQuest Timing Analyzer 可以把修改或改变主时钟(或者引入时

钟)特性的分频时钟、波纹时钟和电路作为生成时钟。

你可以定义这些电路的输出作为生成时钟。这些定义可以让 Quartus II

TimeQuest Timing Analyzer 分析这些时钟以及关联的时钟网络延时(network

latency)。

使用 create_generated_clock 命令定义生成时钟。

Example 6–5. create_generated_clock Command

create_generated_clock

[-name

]

-source

[-edges ]

[-edge_shift ]

[-divide_by ]

[-multiply_by ]

[-duty_cycle ]

[-add]

[-invert]

�[-master_clock

]

[-phase ]

[-offset ]

Table 6–7. create_generated_clock Command Options

选项

-name

-source

-edges |

-edge_shift

-divide_by

|

-multiply_by

-duty_cycle

-add

-invert

-master_clock

-phase

-offset

描述

生成时钟名

指定被设定的时钟节点

-edges 指定和主时钟的上升沿和下降沿有关的新的

上升沿和下降沿

-divide_by 和-multiply_by 要素是基于第一个时钟上

升沿,通过设定来延长或者缩短指定要素的

波形

指定生成时钟的占空比

允许你对同一个管脚添加多个时钟约束

用于主管脚上有多个时钟存在时指定一个主时钟

指定生成时钟的相位

指定生成时钟的偏移

指定被分配到的目标管脚

源延时是由于从主时钟(不一定是主管脚)开始的时钟网络延时所致。你可

以使用 set_clock_latency –source 命令约束源延时。

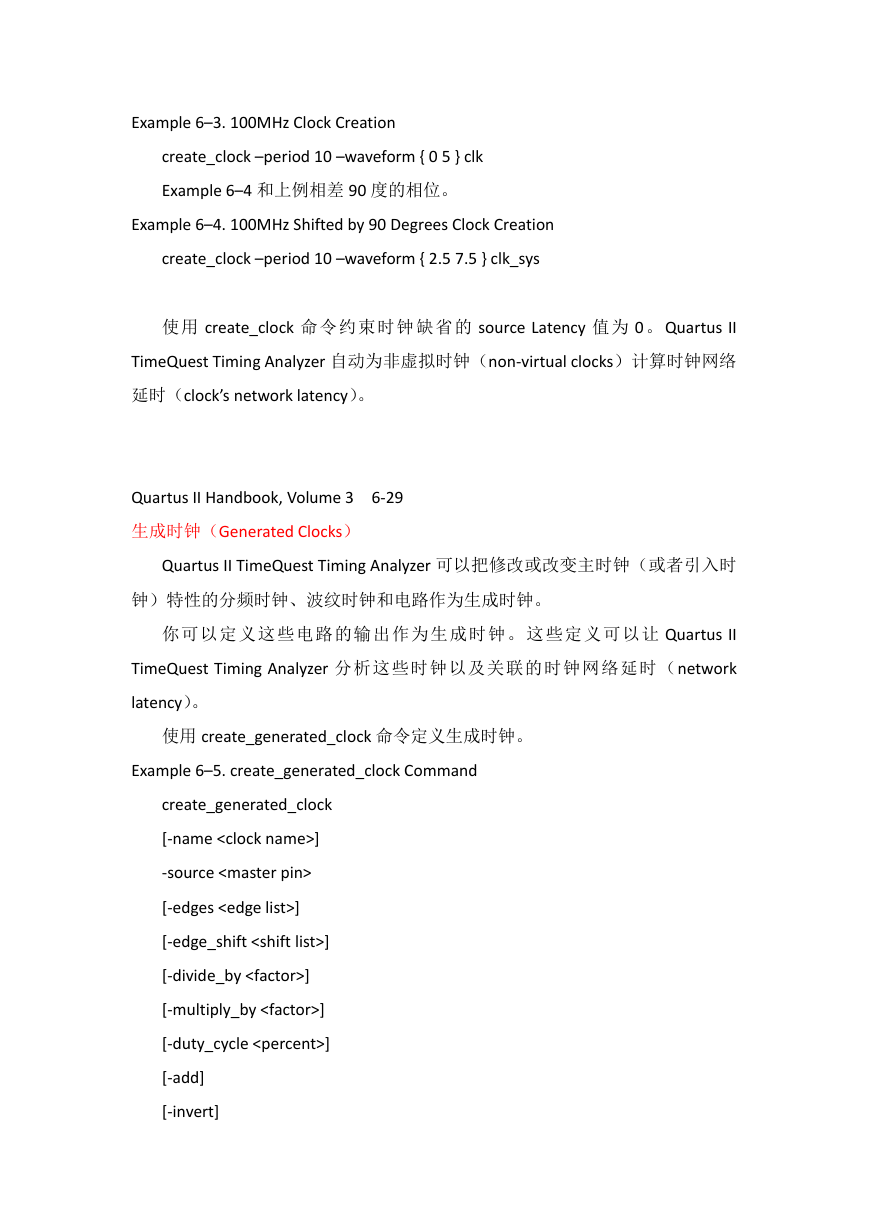

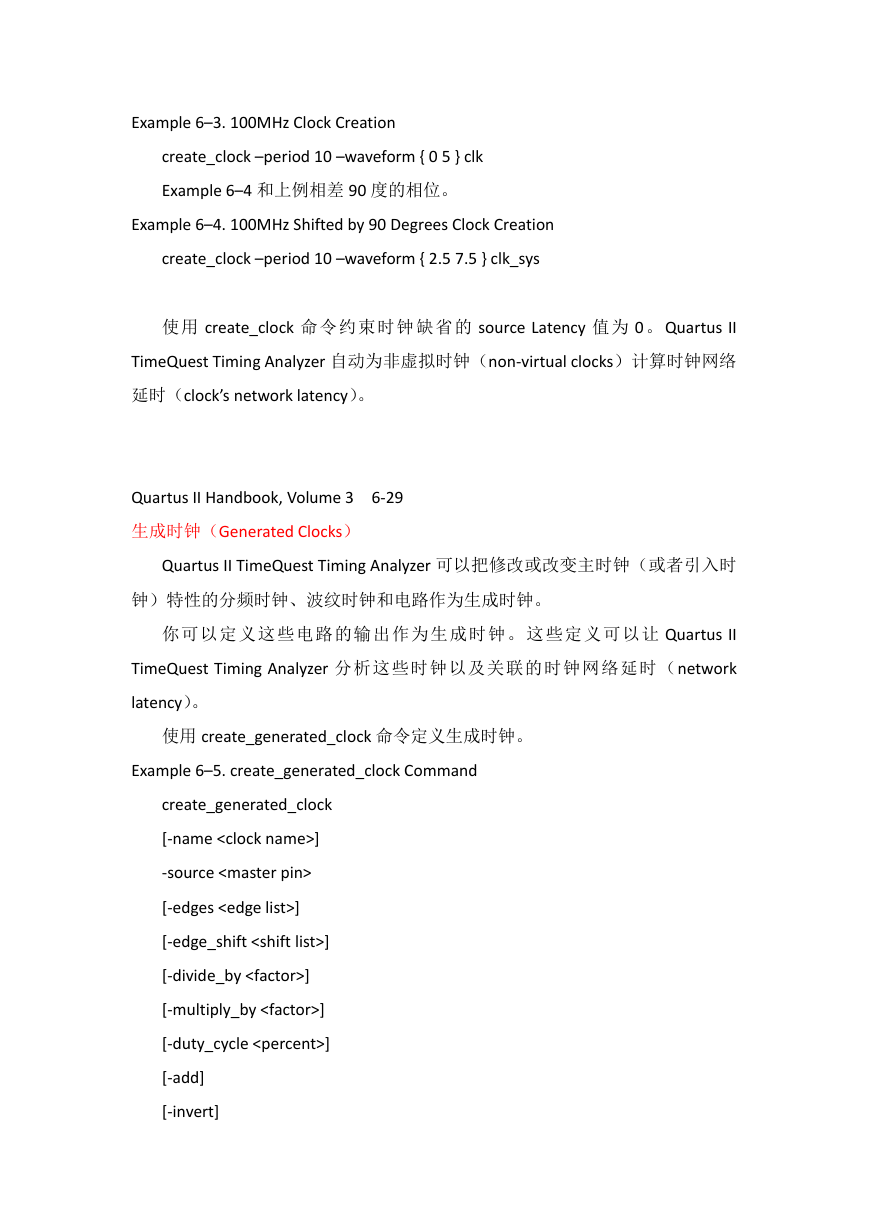

Figure 6–17 展示了如何产生一个基于 10ns 时钟的反向生成时钟:

Figure 6–17. Generating an Inverted Clock

create_clock -period 10 [get_ports clk]

create_generated_clock -divide_by 1 -invert -source [get_registers clk] \

[get_registers gen|clkreg]

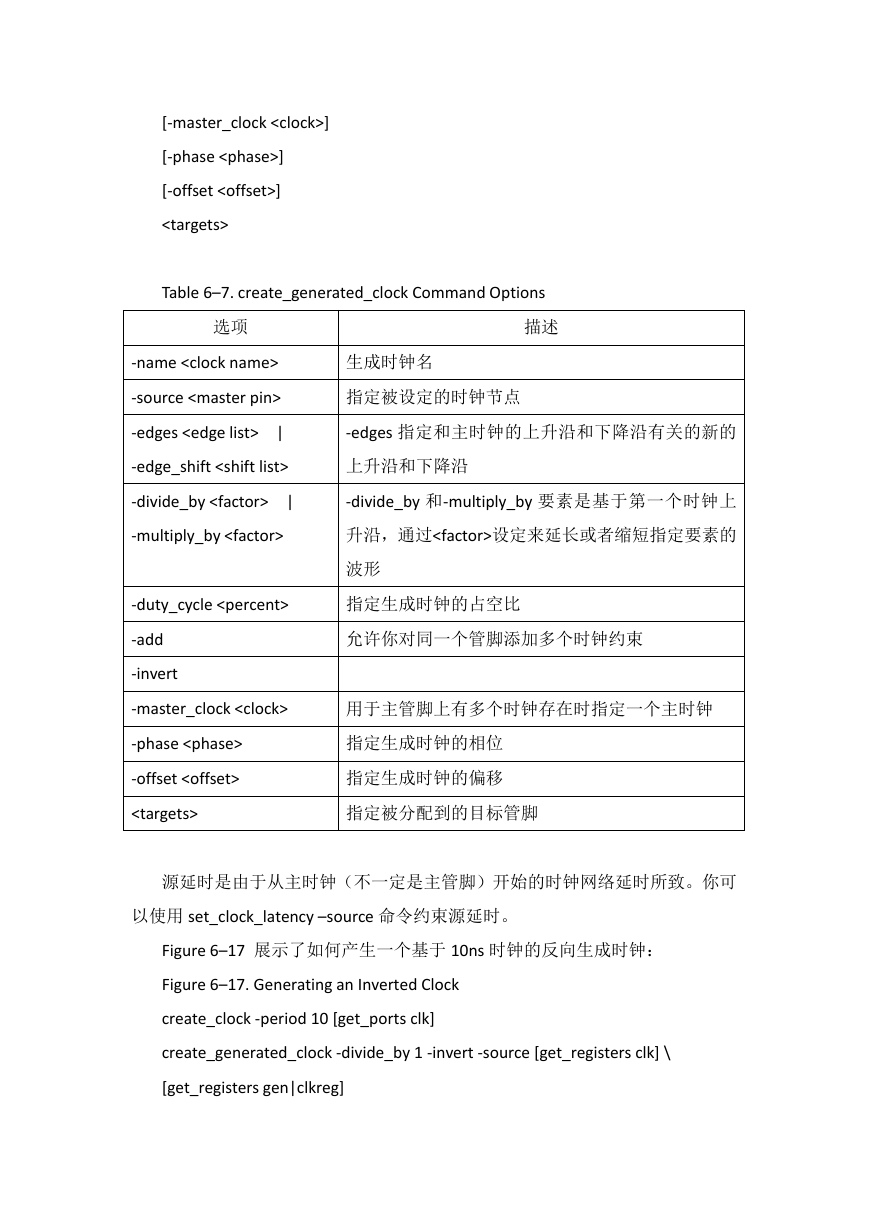

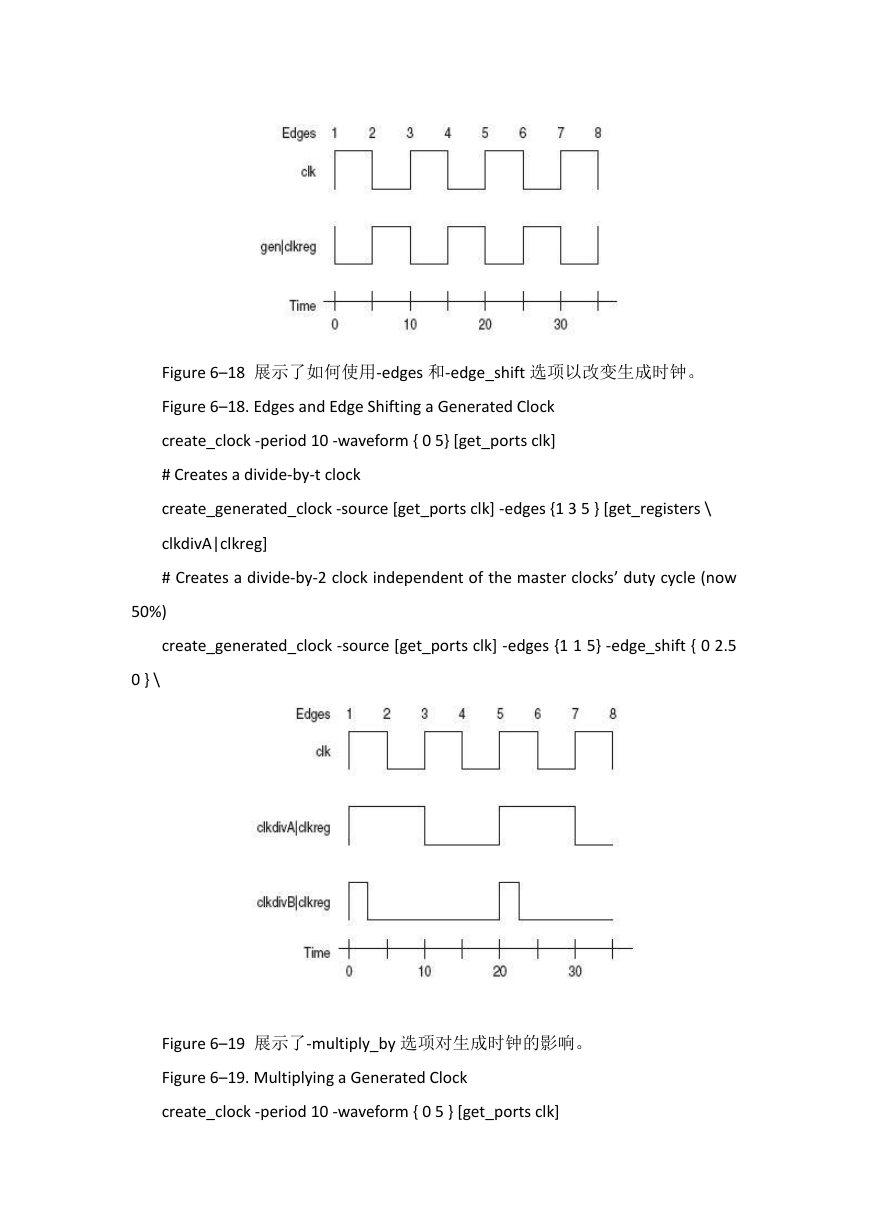

�Figure 6–18 展示了如何使用-edges 和-edge_shift 选项以改变生成时钟。

Figure 6–18. Edges and Edge Shifting a Generated Clock

create_clock -period 10 -waveform { 0 5} [get_ports clk]

# Creates a divide-by-t clock

create_generated_clock -source [get_ports clk] -edges {1 3 5 } [get_registers \

clkdivA|clkreg]

# Creates a divide-by-2 clock independent of the master clocks’ duty cycle (now

50%)

create_generated_clock -source [get_ports clk] -edges {1 1 5} -edge_shift { 0 2.5

0 } \

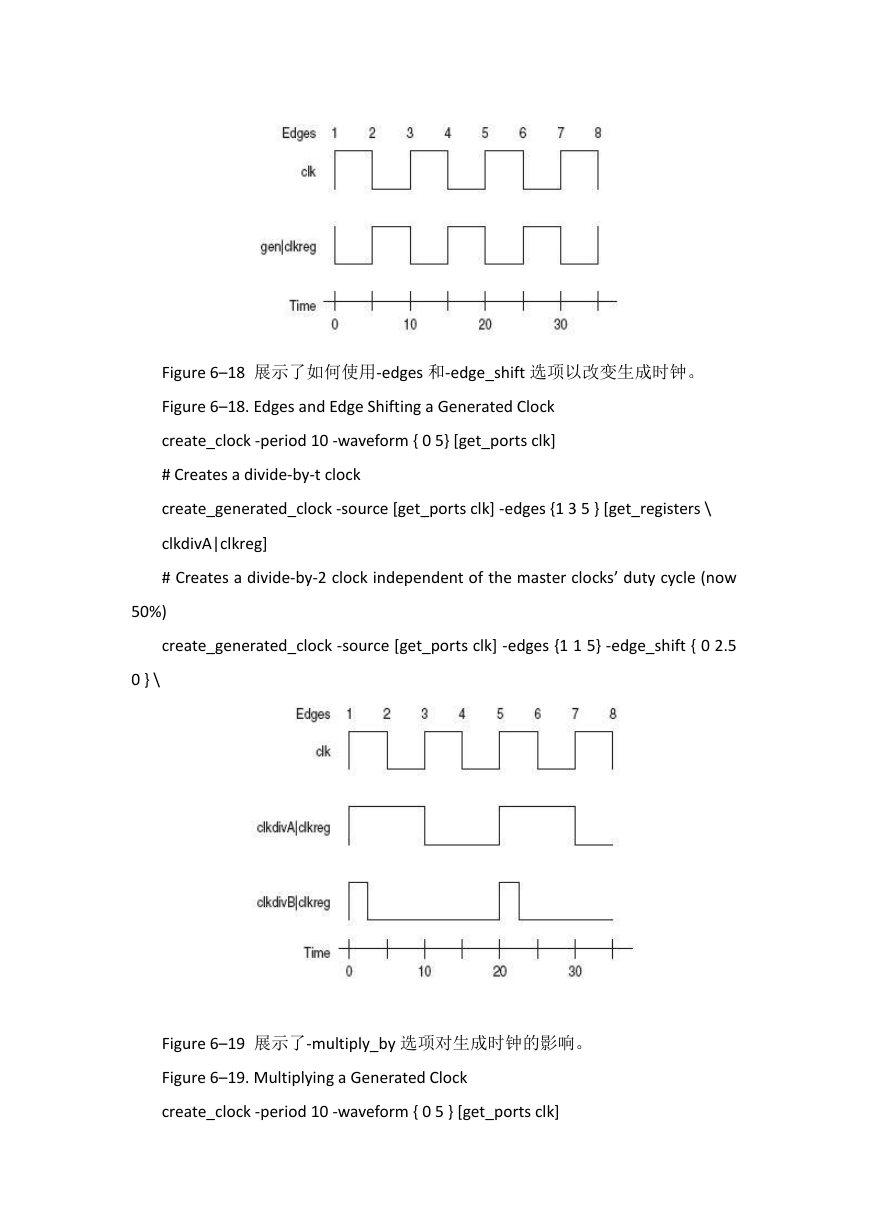

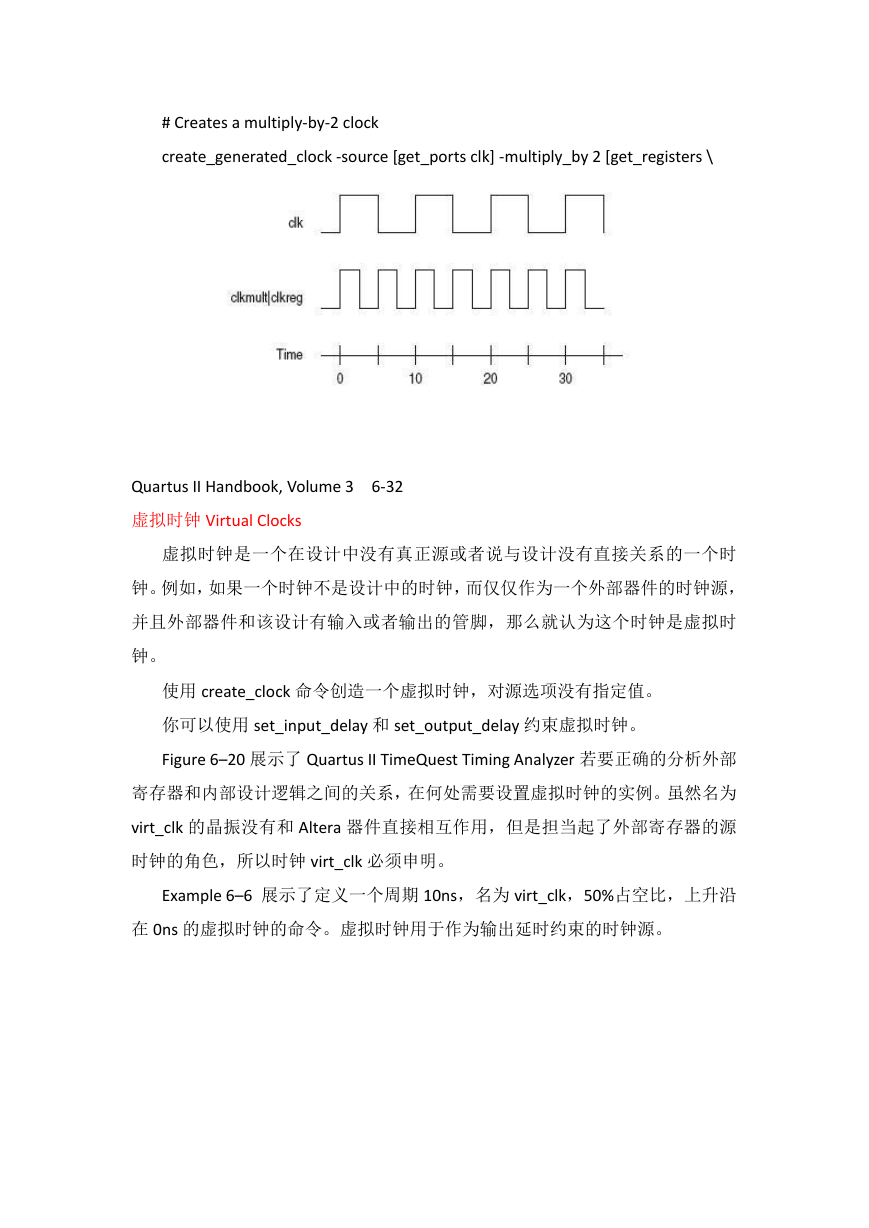

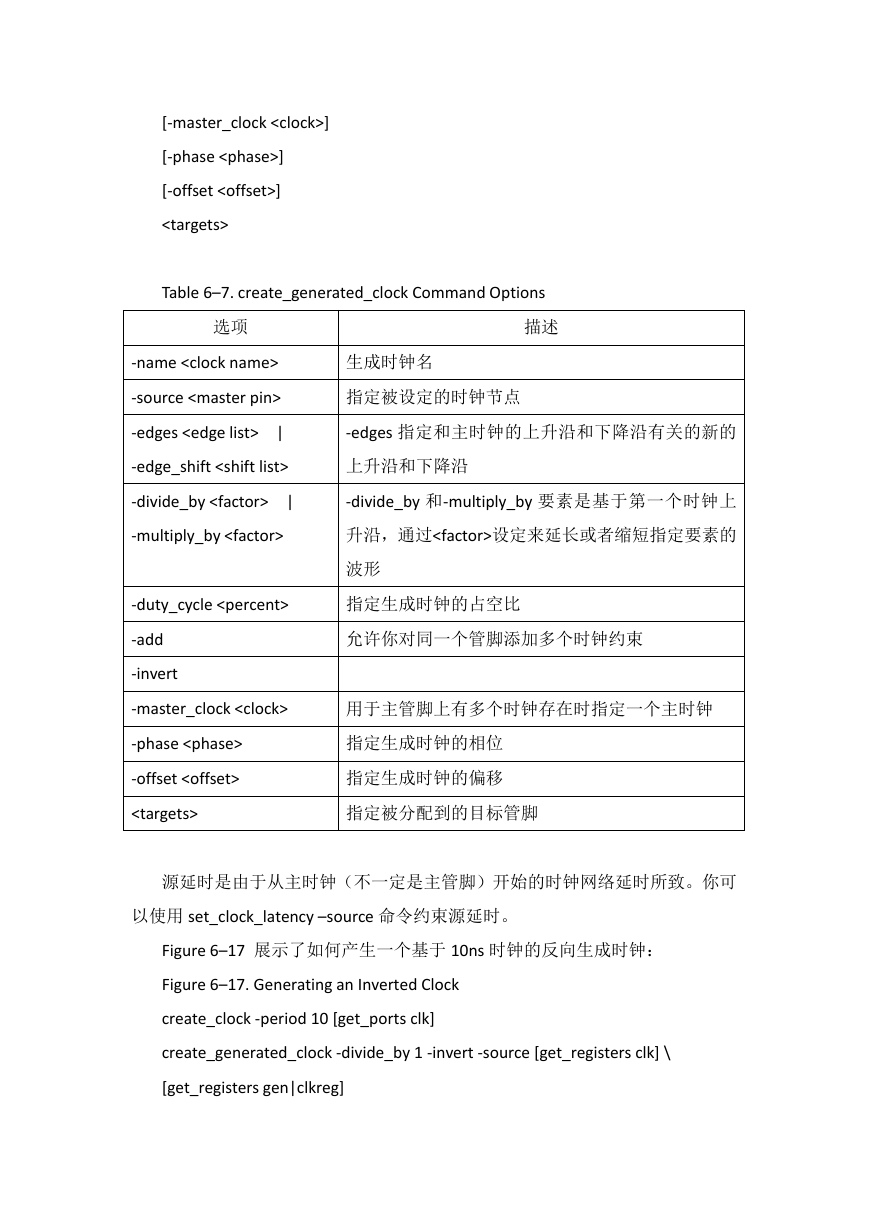

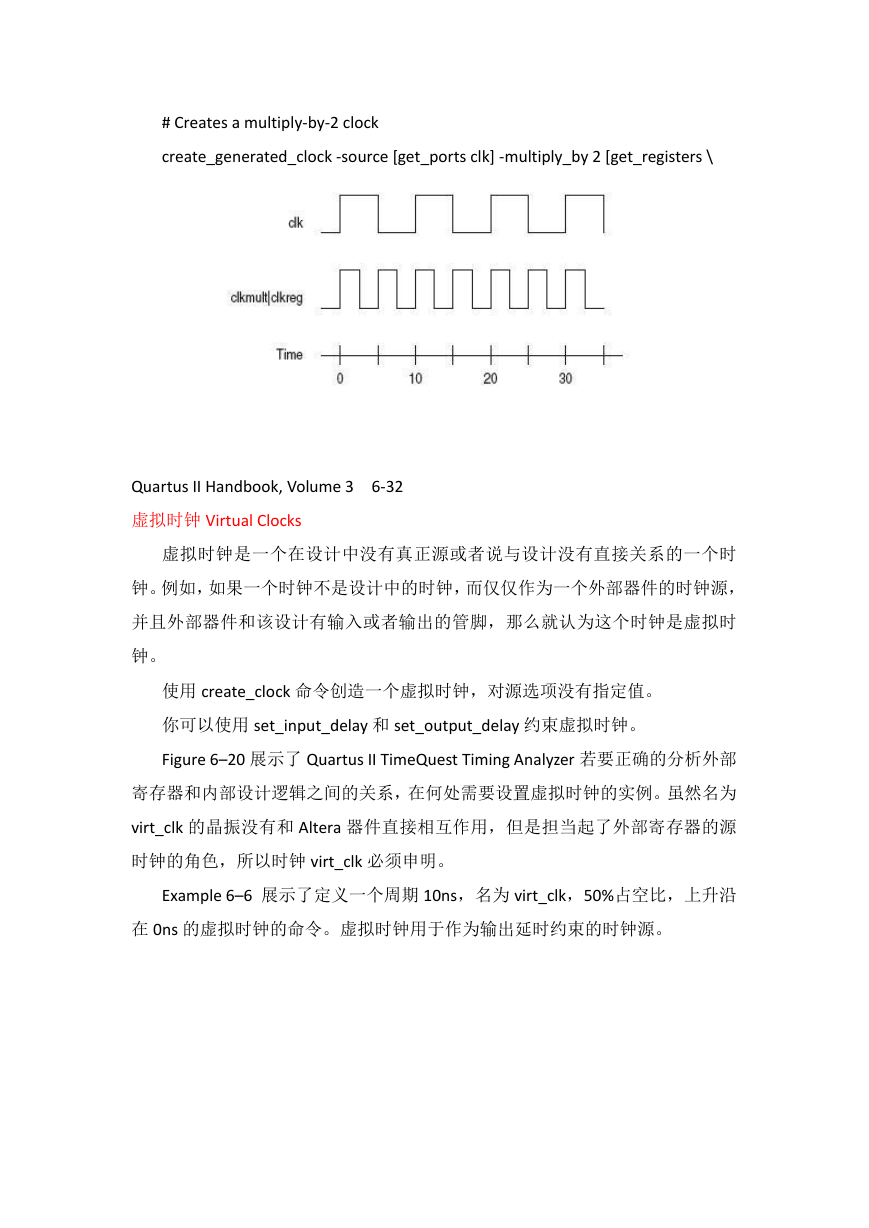

Figure 6–19 展示了-multiply_by 选项对生成时钟的影响。

Figure 6–19. Multiplying a Generated Clock

create_clock -period 10 -waveform { 0 5 } [get_ports clk]

�

# Creates a multiply-by-2 clock

create_generated_clock -source [get_ports clk] -multiply_by 2 [get_registers \

Quartus II Handbook, Volume 3 6-32

虚拟时钟 Virtual Clocks

虚拟时钟是一个在设计中没有真正源或者说与设计没有直接关系的一个时

钟。例如,如果一个时钟不是设计中的时钟,而仅仅作为一个外部器件的时钟源,

并且外部器件和该设计有输入或者输出的管脚,那么就认为这个时钟是虚拟时

钟。

使用 create_clock 命令创造一个虚拟时钟,对源选项没有指定值。

你可以使用 set_input_delay 和 set_output_delay 约束虚拟时钟。

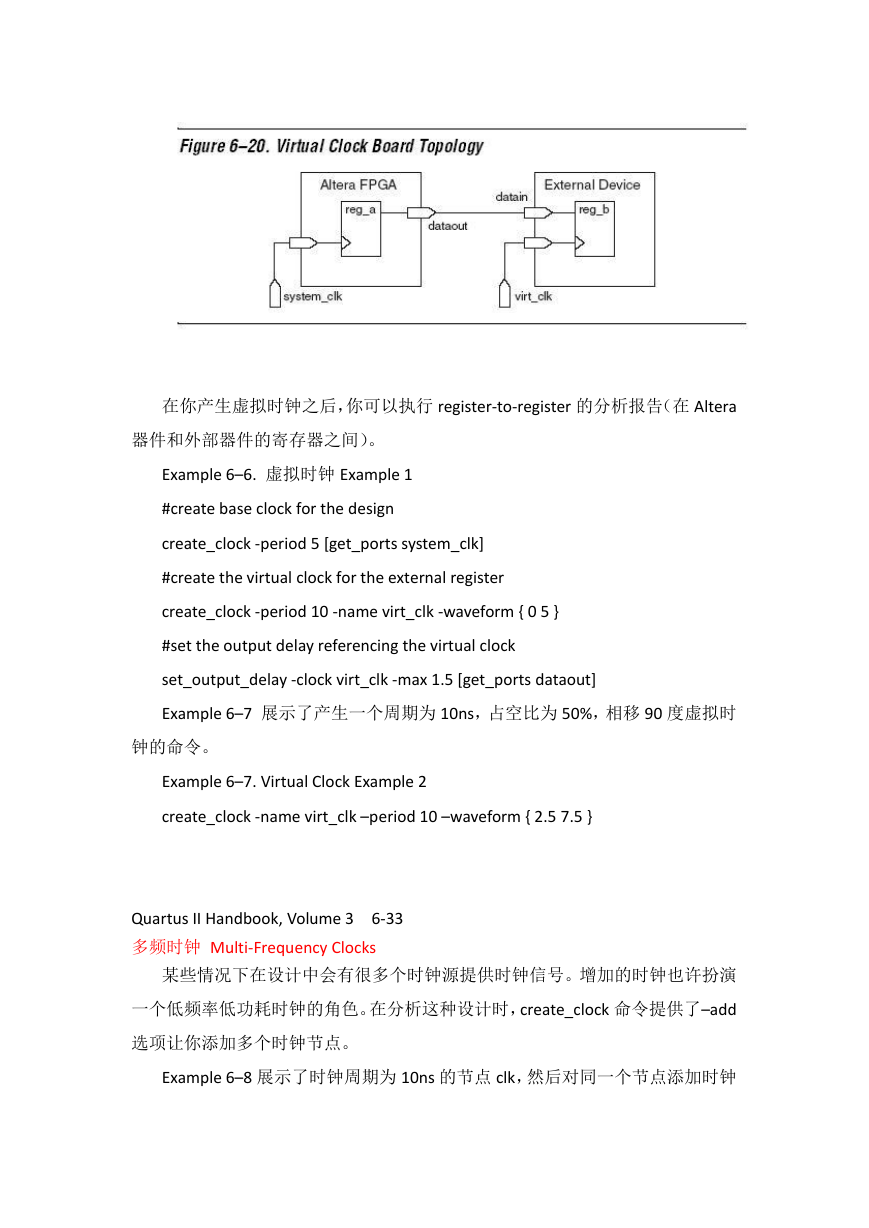

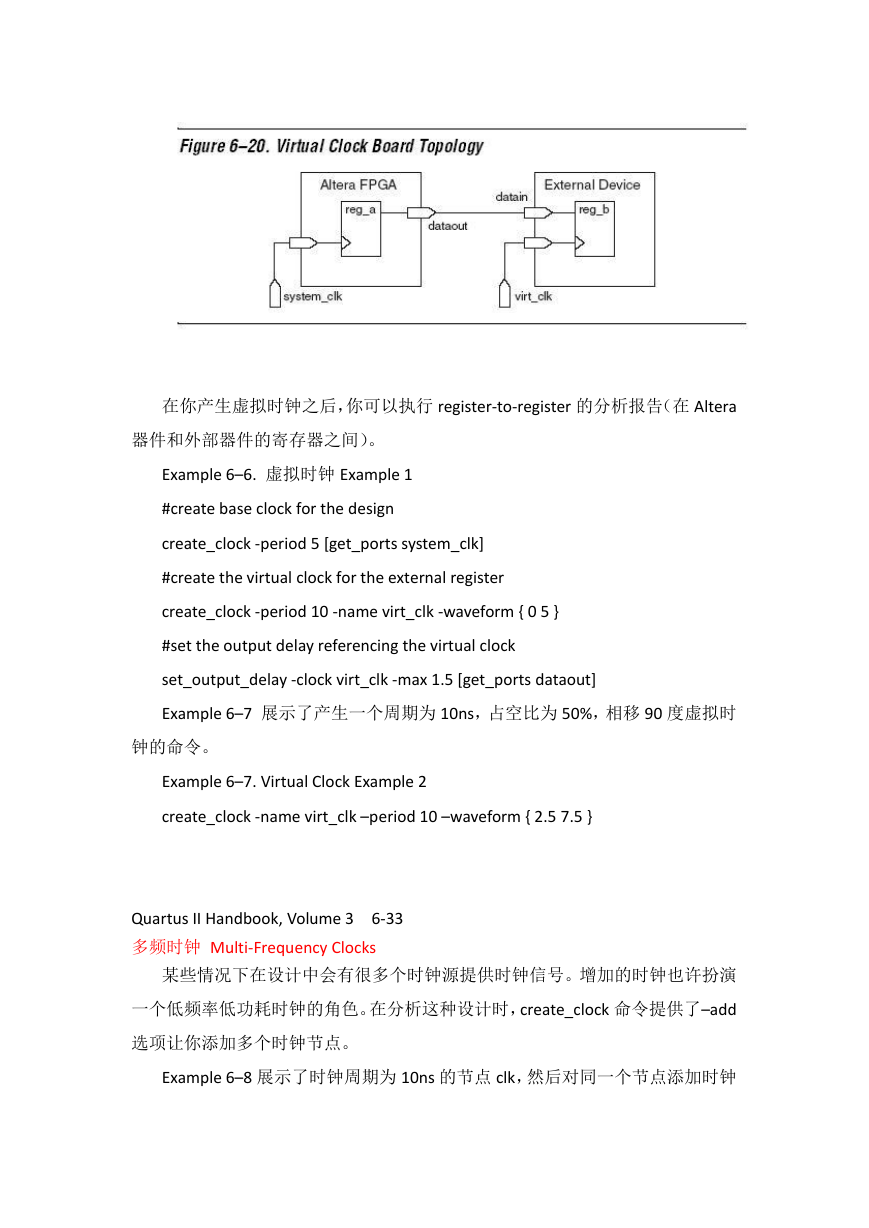

Figure 6–20 展示了 Quartus II TimeQuest Timing Analyzer 若要正确的分析外部

寄存器和内部设计逻辑之间的关系,在何处需要设置虚拟时钟的实例。虽然名为

virt_clk 的晶振没有和 Altera 器件直接相互作用,但是担当起了外部寄存器的源

时钟的角色,所以时钟 virt_clk 必须申明。

Example 6–6 展示了定义一个周期 10ns,名为 virt_clk,50%占空比,上升沿

在 0ns 的虚拟时钟的命令。虚拟时钟用于作为输出延时约束的时钟源。

�

在你产生虚拟时钟之后,你可以执行 register-to-register 的分析报告(在 Altera

器件和外部器件的寄存器之间)。

Example 6–6. 虚拟时钟 Example 1

#create base clock for the design

create_clock -period 5 [get_ports system_clk]

#create the virtual clock for the external register

create_clock -period 10 -name virt_clk -waveform { 0 5 }

#set the output delay referencing the virtual clock

set_output_delay -clock virt_clk -max 1.5 [get_ports dataout]

Example 6–7 展示了产生一个周期为 10ns,占空比为 50%,相移 90 度虚拟时

钟的命令。

Example 6–7. Virtual Clock Example 2

create_clock -name virt_clk –period 10 –waveform { 2.5 7.5 }

Quartus II Handbook, Volume 3 6-33

多频时钟 Multi-Frequency Clocks

某些情况下在设计中会有很多个时钟源提供时钟信号。增加的时钟也许扮演

一个低频率低功耗时钟的角色。在分析这种设计时,create_clock 命令提供了–add

选项让你添加多个时钟节点。

Example 6–8 展示了时钟周期为 10ns 的节点 clk,然后对同一个节点添加时钟

�

周期为 15ns 的时钟。Quartus II TimeQuest Timing Analyzer 在执行时序分析时两个

时钟都用到了。

Example 6–8. Multi-Frequency Example

create_clock –period 10 –name clock_primary –waveform { 0 5 } [get_ports clk]

create_clock –period 15 –name clock_secondary –waveform { 0 7.5 } [get_ports

clk] -add

Quartus II Handbook, Volume 3 6-34

自动时钟检测 Automatic Clock Detection

想 要 为 你 的 设 计 中 所 有 的 时 钟 节 点 自 动 添 加 时 钟 约 束 , 那 么 就 使 用

derive_clocks 命令。这个命令从管脚或者寄存器生成时钟以确保设计中的每个寄

存器都有时钟。

Example 6–9 展示了 derive_clocks 命令选项。

Example 6–9. derive_clocks Command

derive_clocks

[-period

]

[-waveform ]

Table 6–8 describes the options for the derive_clocks command.

选项

描述

-period

指定时钟周期,你也可以指定时钟频率如下:

-waveform

-period MHz

指定沿变化时刻

derive_clocks 命令不能为 PLLs 输出时钟进行约束。

derive_clocks 命令相当于使用 create_clock 命令为每个寄存器或者管脚产生

时钟。

�Quartus II Handbook, Volume 3 6-35

锁相环时钟 Derive PLL Clocks

PLLs(锁相环)在 Altera 器件中被用于时钟管理和综合。你可以定制基于你

设计需要的PLL 输出时钟约束。因为所有的时钟节点应该有一个共同的时钟基准,

故所有的 PLL 输出应该有一个关联时钟。

你可以使用 create_generated_clock 命令手动添加一个作为 PLL 输出的基准时

钟,或者你也可以使用 derive_pll_clocks 命令自动搜寻时序网表并通过设置指定

PLL 输出来产生时钟。

使用 derive_pll_clocks 命令为 PLL 输出自动产生时钟的实例如下:

derive_pll_clocks

[-use_tan_name]

Table 6–9. derive_pll_clocks Command Options

选项

-use_tan_name

描述

缺省下,时钟名为输出时钟名字。这个选项使

用 的 网 络 名 字 类 似 于 在 Quartus II Classic Timing

Analyzer 中使用的。

derive_pll_clocks 命令调用 create_generated_clock 命令以产生 PLL 输出的生成

时钟。

create_generated_clock 命令的 source 是 PLL 的输入时钟。derive_pll_clocks

命令的前后已固定,你必须手动为 PLL 生成一个输入时钟节点。如果 PLL 的输入

时钟节点未被定义好,报告中不会出现 PLL 输出的时钟。取而代之的,当时序网

表更新后,Quartus II TimeQuest Timing Analyzer 发出一个类似于 Figure 6–10 的警

告信息。

Example 6–10. Warning Message

Warning: The master clock for this clock assignment could not be derived.

Clock: was not created.

你 可 以 把 derive_pll_clocks 命 令 添 加 到 你 的 SDC 文 件 中 , 以 使 得

derive_pll_clocks 命令可以自动检测 PLL 的任何变化。derive_pll_clocks 在你的 SDC

文件中,每次读取该文件,PLL 输出时钟脚的 create_generated_clock 命令就将生

成。如果在 derive_pll_clock 命令后使用 write_sdc 命令,新的 SDC 文件包含了独

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc