实验报告

2017 年 11 月 19 日

成绩:

姓名

姓名

专业

学号

学号

班级

班级

计算机科学与技术

课程名称

《数字电路课程设计》

任课老师

实验序号

指导老师

实验名称

7

实验时间 17.11.9 实验地点

机位号

加减法器

实验设备号

一、实验目的和实验要求

1. 实验目的:

(1) 学习二进制加/减法器运算器的原理和设计方法

(2) 掌握灵活运用 Verilog HDL 语言进行各种描述与建模的技巧和方法

2. 实验要求:

(1) 使用结构建模方法来实现加减法器.

(2) 课前任务:在 Xilink ISE 上完成创建工程、编辑程序源代码、编译、综合、仿真、验证,

确保逻辑正确性.

(3) 撰写实验报告:含程序源代码、激励代码及其仿真波形、综合得到的电路图、实验结果

分析以及对本实验的”思考与探索”部分所作的思考与探索.

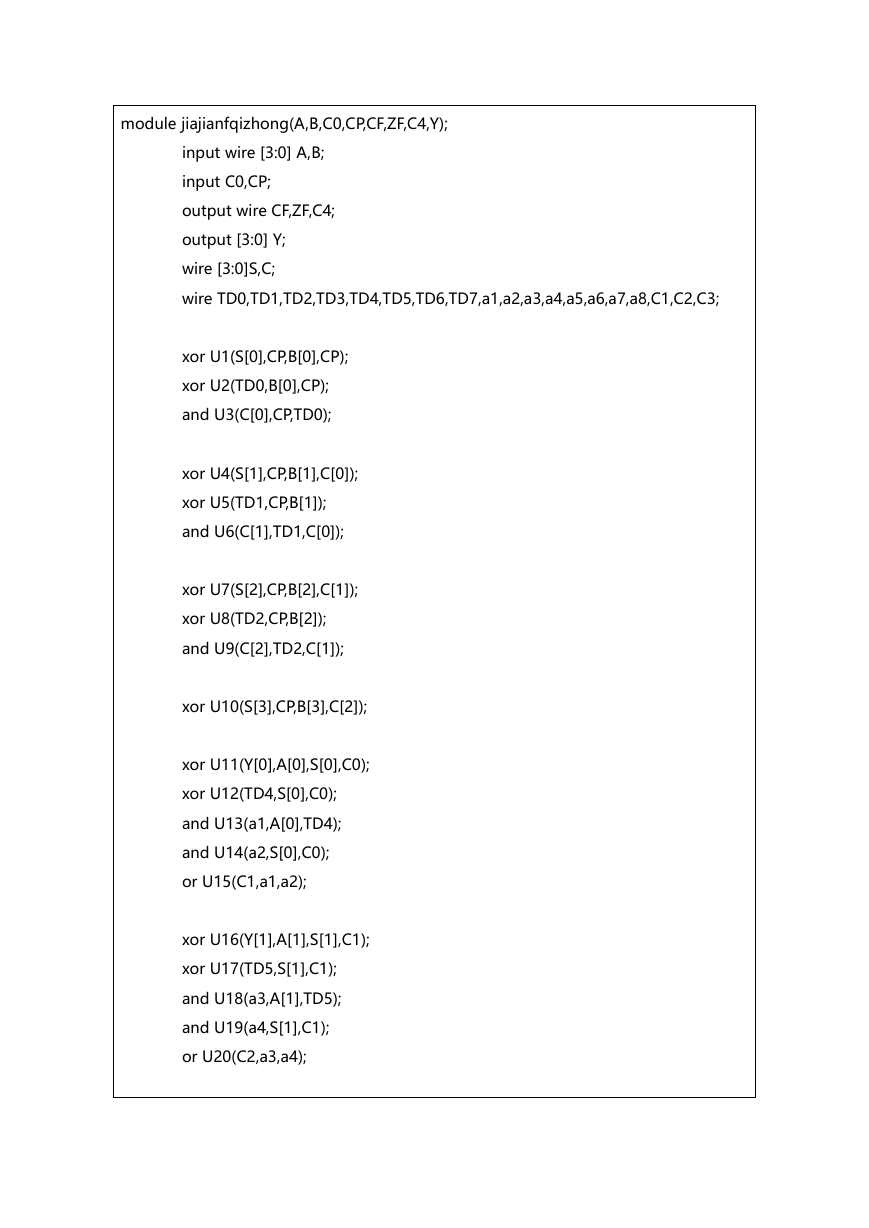

二、实验程序源代码

�

module jiajianfqizhong(A,B,C0,CP,CF,ZF,C4,Y);

input wire [3:0] A,B;

input C0,CP;

output wire CF,ZF,C4;

output [3:0] Y;

wire [3:0]S,C;

wire TD0,TD1,TD2,TD3,TD4,TD5,TD6,TD7,a1,a2,a3,a4,a5,a6,a7,a8,C1,C2,C3;

xor U1(S[0],CP,B[0],CP);

xor U2(TD0,B[0],CP);

and U3(C[0],CP,TD0);

xor U4(S[1],CP,B[1],C[0]);

xor U5(TD1,CP,B[1]);

and U6(C[1],TD1,C[0]);

xor U7(S[2],CP,B[2],C[1]);

xor U8(TD2,CP,B[2]);

and U9(C[2],TD2,C[1]);

xor U10(S[3],CP,B[3],C[2]);

xor U11(Y[0],A[0],S[0],C0);

xor U12(TD4,S[0],C0);

and U13(a1,A[0],TD4);

and U14(a2,S[0],C0);

or U15(C1,a1,a2);

xor U16(Y[1],A[1],S[1],C1);

xor U17(TD5,S[1],C1);

and U18(a3,A[1],TD5);

and U19(a4,S[1],C1);

or U20(C2,a3,a4);

�

xor U21(Y[2],A[2],S[2],C2);

xor U22(TD6,S[2],C2);

and U23(a5,A[2],TD6);

and U24(a6,S[2],C2);

or U25(C3,a5,a6);

xor U26(Y[3],A[3],S[3],C3);

xor U27(TD7,S[3],C3);

and U28(a7,A[3],TD7);

and U29(a8,S[3],C3);

or U30(C4,a7,a8);

nor U31(ZF,Y[3],Y[2],Y[1],Y[0]);

xor U32(CF,CP,C4);

endmodule

三、仿真文件和波形图(有就填,没有就不填)

仿真文件:

module jiajianfaqizuizhong_test;

// Inputs

reg [3:0] A;

reg [3:0] B;

reg C0;

reg CP;

// Outputs

wire CF;

wire ZF;

wire C4;

wire [3:0] Y;

�

// Instantiate the Unit Under Test (UUT)

jiajianfqizhong uut (

.A(A),

.B(B),

.C0(C0),

.CP(CP),

.CF(CF),

.ZF(ZF),

.C4(C4),

.Y(Y)

);

initial begin

// Initialize Inputs

A = 0;

B = 0;

C0 = 0;

CP = 0;

// Wait 100 ns for global reset to finish

#50;

// Add stimulus here

#50;

A = 4'b0000;B = 4'b0000;C0 = 0;CP = 1;

#50;

A = 4'b0001;B = 4'b0001;C0 = 0;CP = 1;

#50;

A = 4'b0011;B = 4'b1010;C0 = 0;CP = 1;

#50;

A = 4'b0100;B = 4'b0110;C0 = 0;CP = 1;

#50;

A = 4'b1000;B = 4'b0110;C0 = 0;CP = 1;

#50;

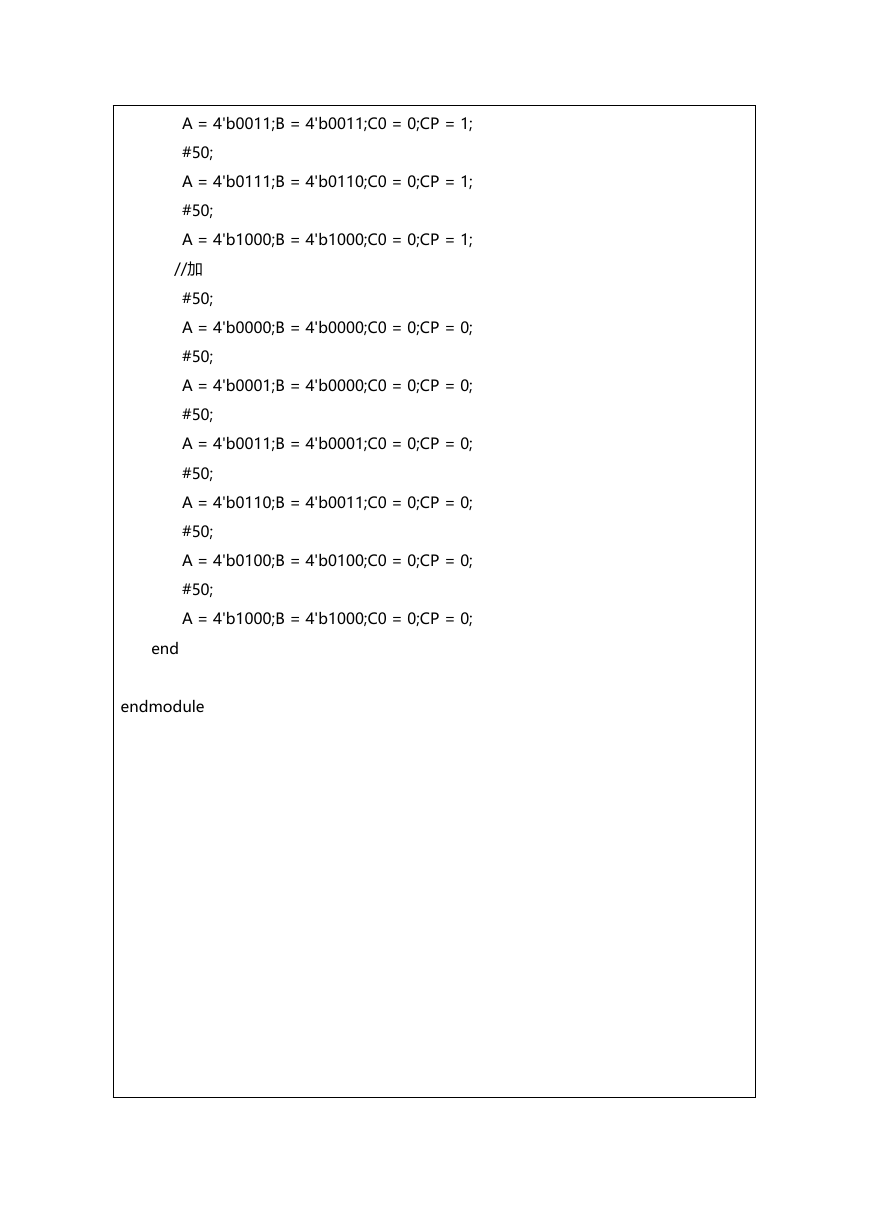

�

A = 4'b0011;B = 4'b0011;C0 = 0;CP = 1;

#50;

A = 4'b0111;B = 4'b0110;C0 = 0;CP = 1;

#50;

A = 4'b1000;B = 4'b1000;C0 = 0;CP = 1;

//加

#50;

A = 4'b0000;B = 4'b0000;C0 = 0;CP = 0;

#50;

A = 4'b0001;B = 4'b0000;C0 = 0;CP = 0;

#50;

A = 4'b0011;B = 4'b0001;C0 = 0;CP = 0;

#50;

A = 4'b0110;B = 4'b0011;C0 = 0;CP = 0;

#50;

A = 4'b0100;B = 4'b0100;C0 = 0;CP = 0;

#50;

A = 4'b1000;B = 4'b1000;C0 = 0;CP = 0;

end

endmodule

�

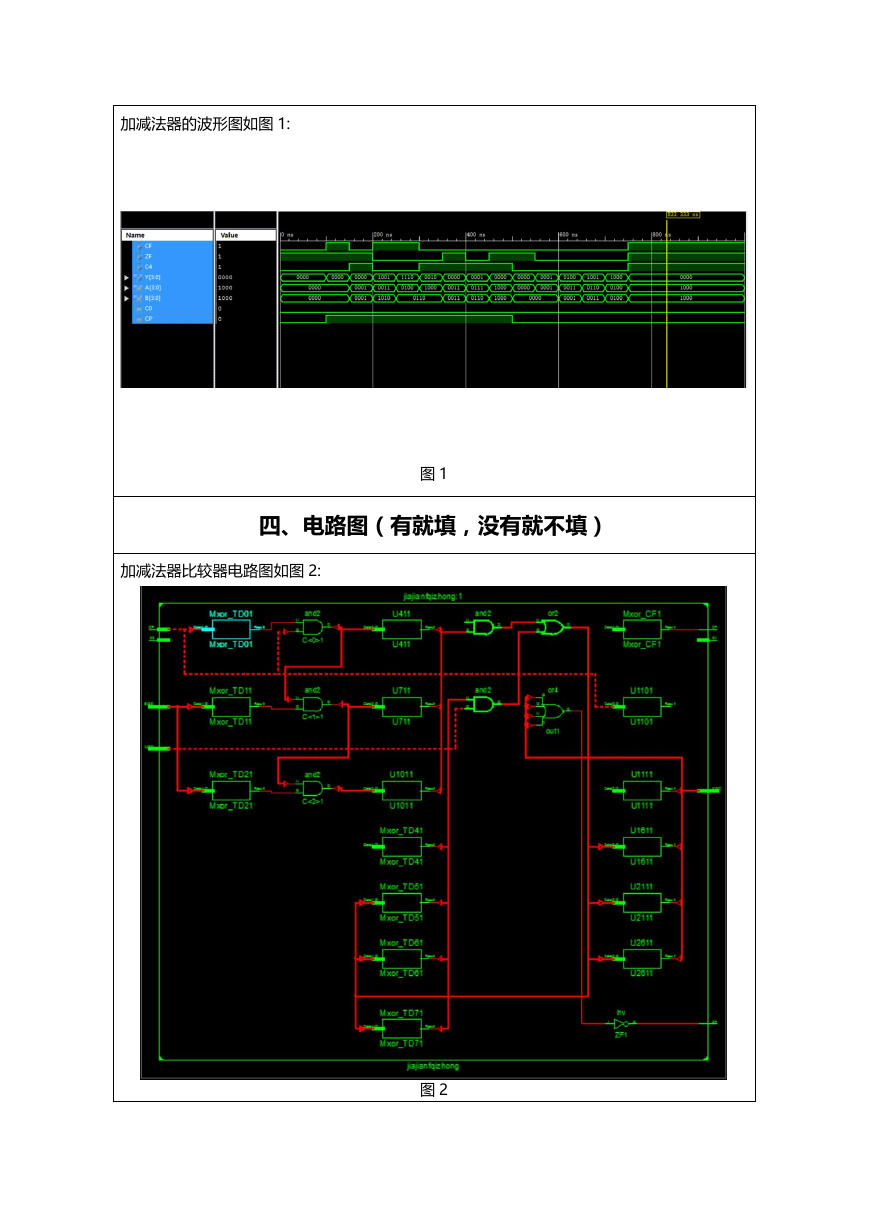

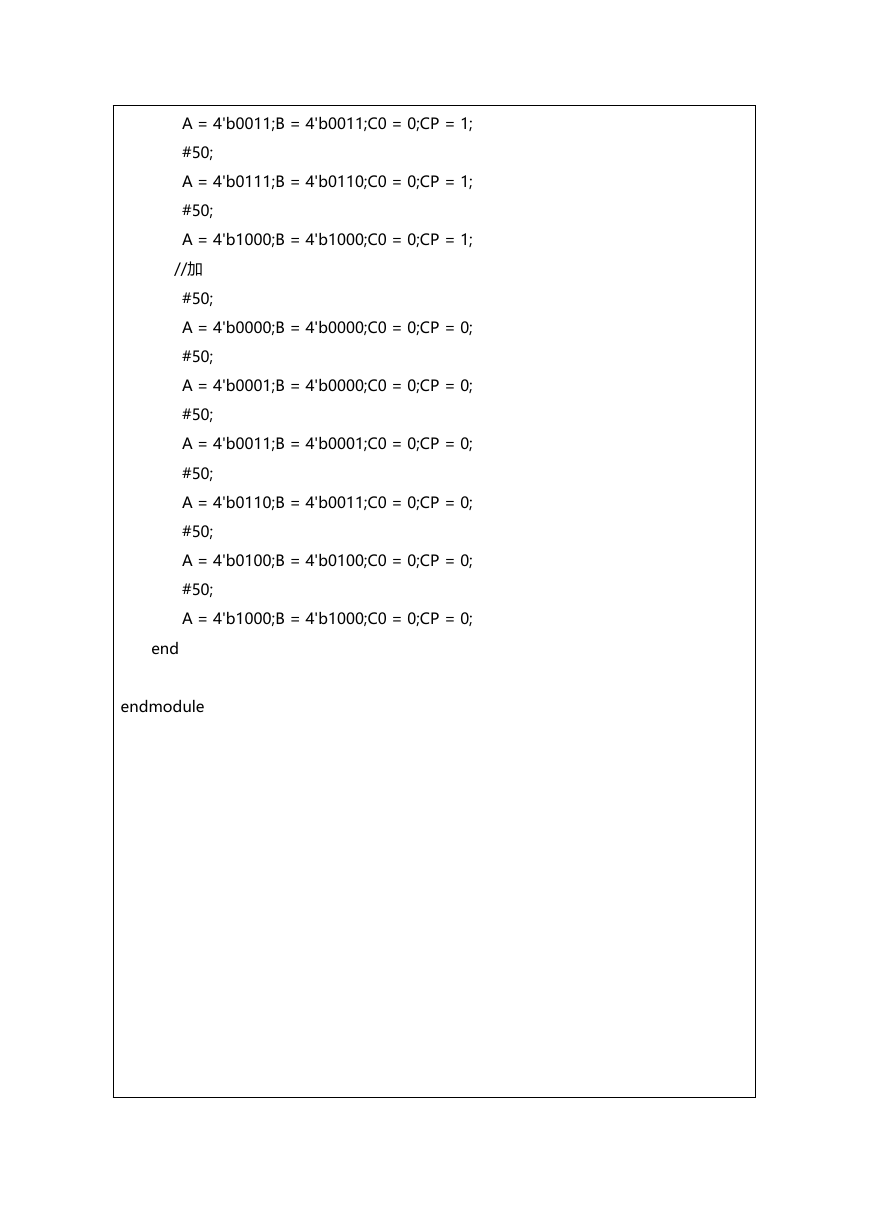

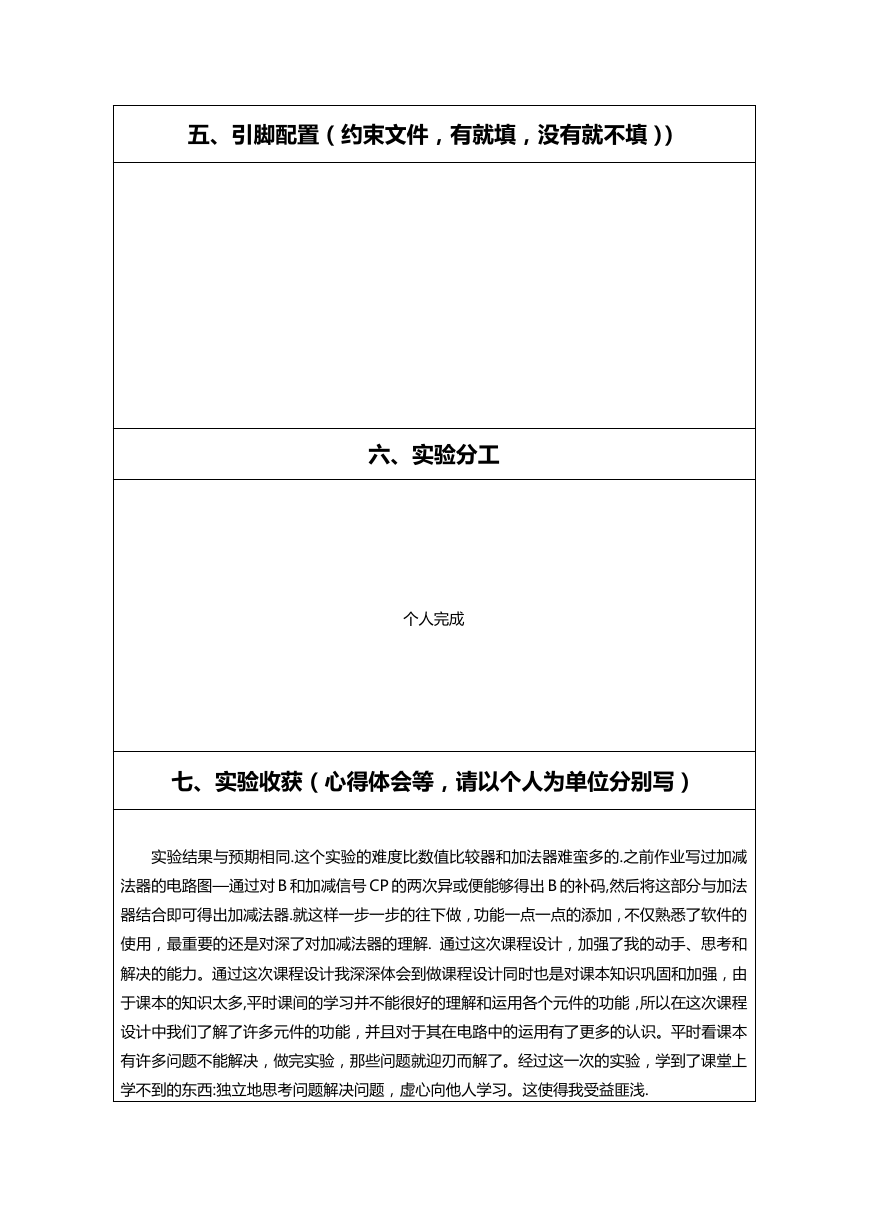

加减法器的波形图如图 1:

图 1

四、电路图(有就填,没有就不填)

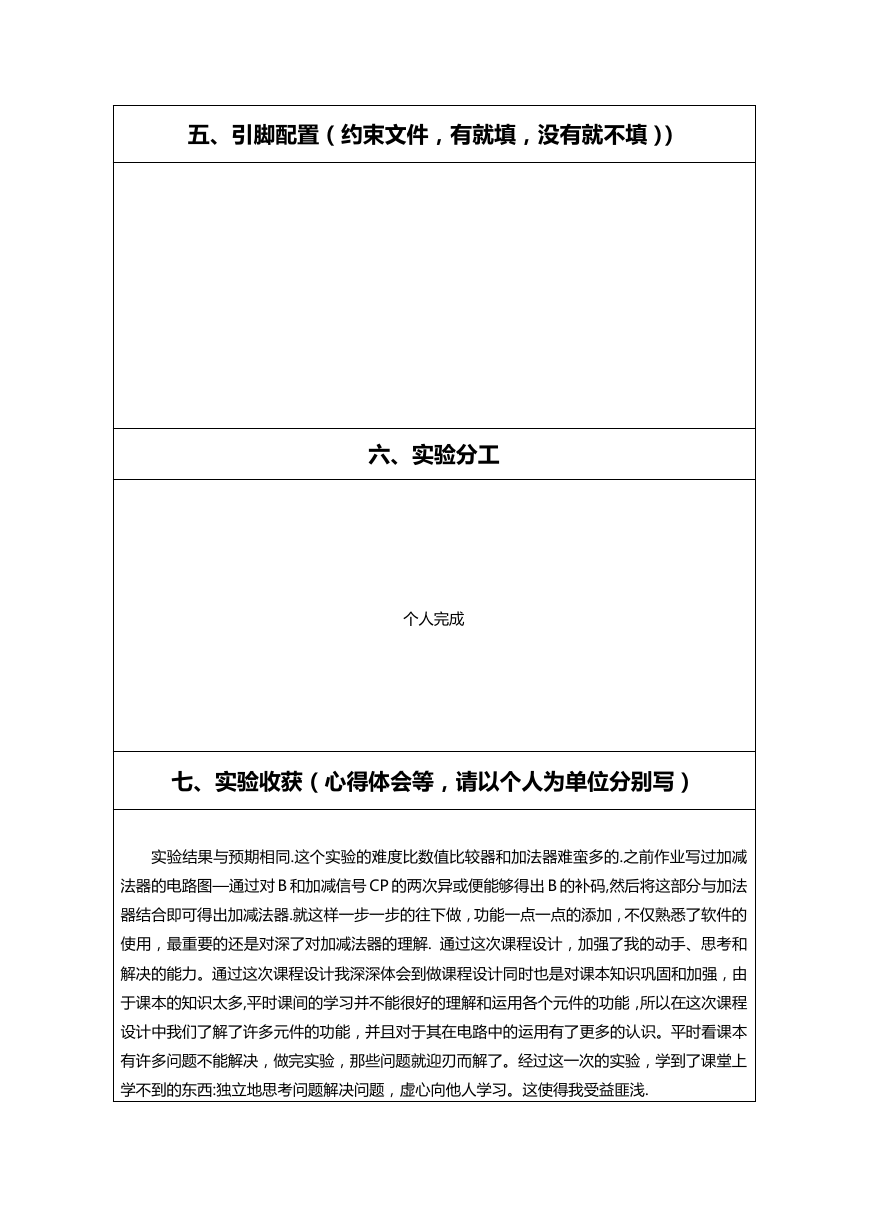

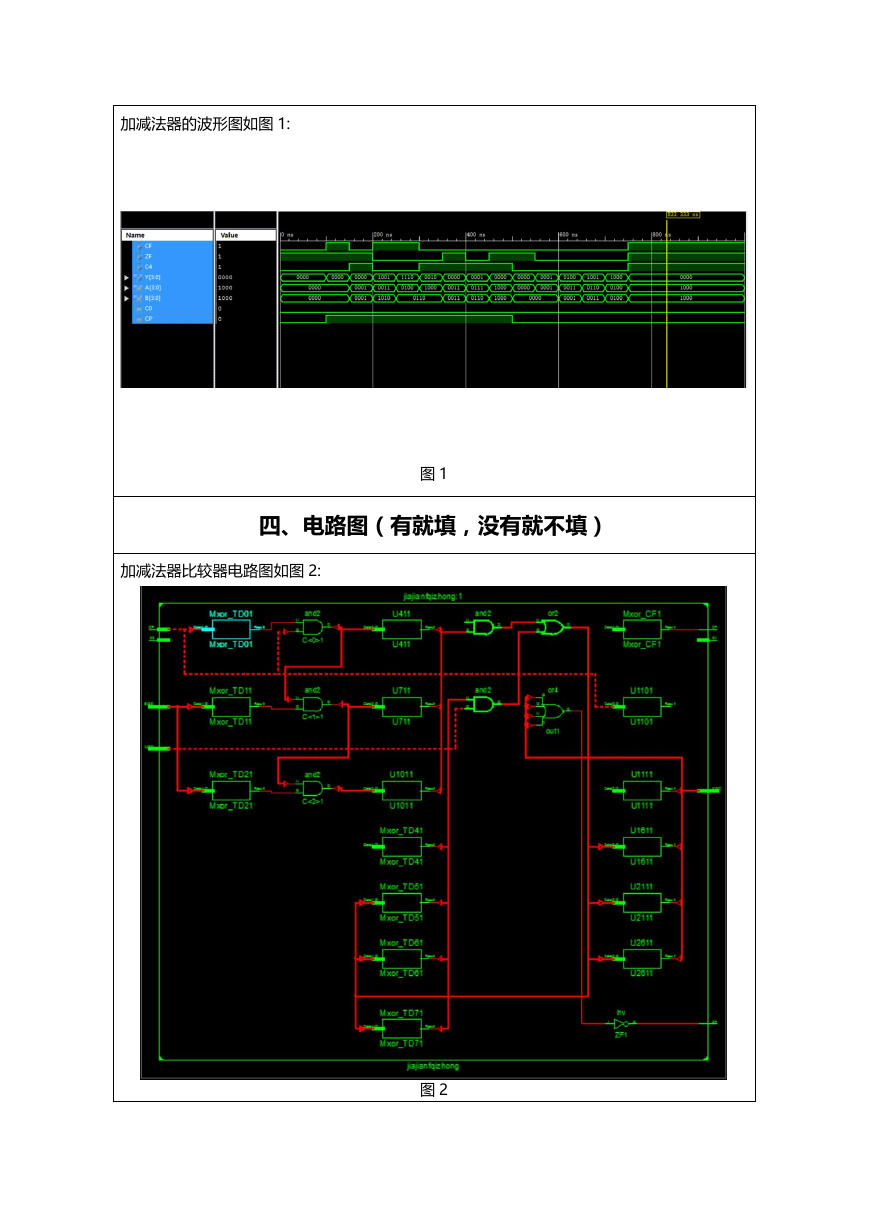

加减法器比较器电路图如图 2:

图 2

�

五、引脚配置(约束文件,有就填,没有就不填))

六、实验分工

个人完成

七、实验收获(心得体会等,请以个人为单位分别写)

实验结果与预期相同.这个实验的难度比数值比较器和加法器难蛮多的.之前作业写过加减

法器的电路图—通过对 B 和加减信号 CP 的两次异或便能够得出 B 的补码,然后将这部分与加法

器结合即可得出加减法器.就这样一步一步的往下做,功能一点一点的添加,不仅熟悉了软件的

使用,最重要的还是对深了对加减法器的理解. 通过这次课程设计,加强了我的动手、思考和

解决的能力。通过这次课程设计我深深体会到做课程设计同时也是对课本知识巩固和加强,由

于课本的知识太多,平时课间的学习并不能很好的理解和运用各个元件的功能,所以在这次课程

设计中我们了解了许多元件的功能,并且对于其在电路中的运用有了更多的认识。平时看课本

有许多问题不能解决,做完实验,那些问题就迎刃而解了。经过这一次的实验,学到了课堂上

学不到的东西:独立地思考问题解决问题,虚心向他人学习。这使得我受益匪浅.

�

八、思考、探索与建议

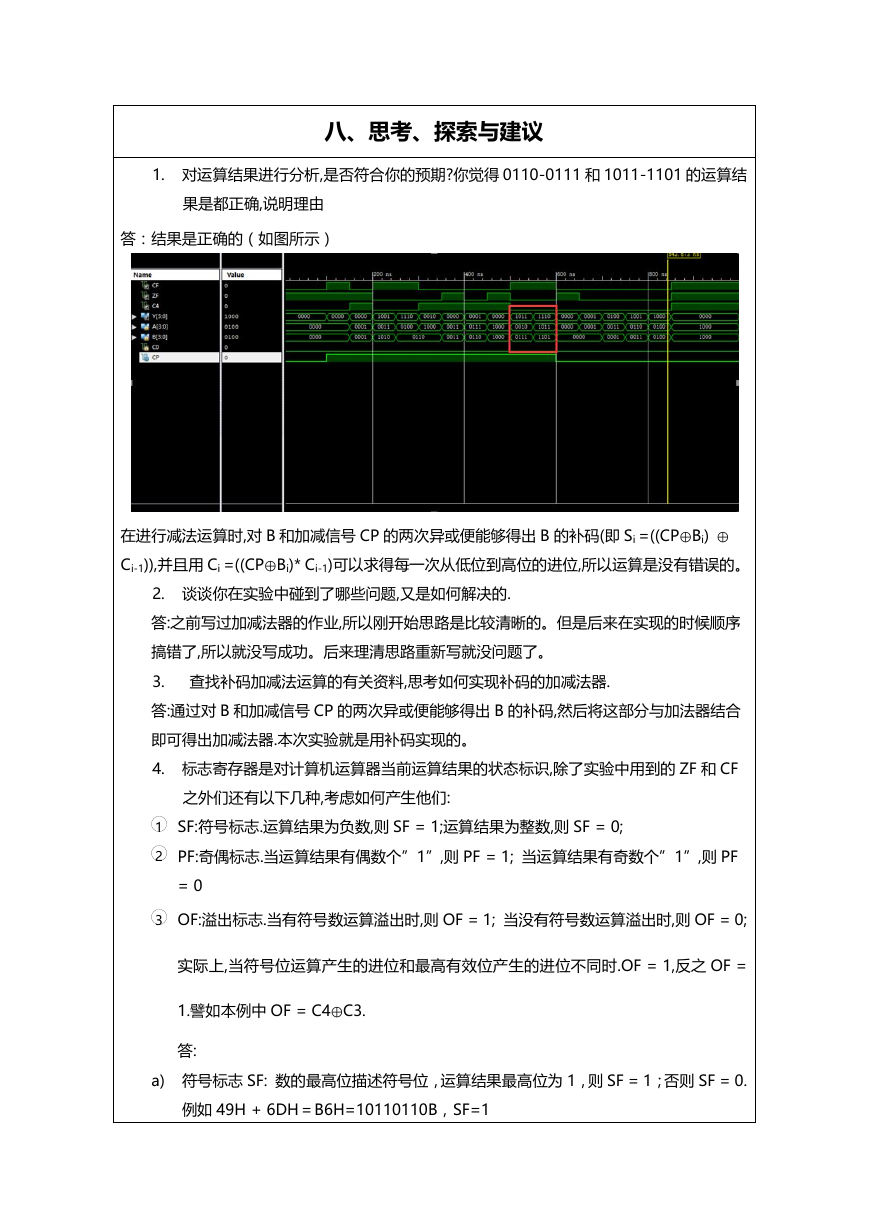

1. 对运算结果进行分析,是否符合你的预期?你觉得 0110-0111 和 1011-1101 的运算结

果是都正确,说明理由

答:结果是正确的(如图所示)

在进行减法运算时,对 B 和加减信号 CP 的两次异或便能够得出 B 的补码(即 Si =((CP⊕Bi) ⊕

Ci-1)),并且用 Ci =((CP⊕Bi)* Ci-1)可以求得每一次从低位到高位的进位,所以运算是没有错误的。

2. 谈谈你在实验中碰到了哪些问题,又是如何解决的.

答:之前写过加减法器的作业,所以刚开始思路是比较清晰的。但是后来在实现的时候顺序

搞错了,所以就没写成功。后来理清思路重新写就没问题了。

3. 查找补码加减法运算的有关资料,思考如何实现补码的加减法器.

答:通过对 B 和加减信号 CP 的两次异或便能够得出 B 的补码,然后将这部分与加法器结合

即可得出加减法器.本次实验就是用补码实现的。

4. 标志寄存器是对计算机运算器当前运算结果的状态标识,除了实验中用到的 ZF 和 CF

之外们还有以下几种,考虑如何产生他们:

1 SF:符号标志.运算结果为负数,则 SF = 1;运算结果为整数,则 SF = 0;

2 PF:奇偶标志.当运算结果有偶数个”1”,则 PF = 1; 当运算结果有奇数个”1”,则 PF

= 0

3 OF:溢出标志.当有符号数运算溢出时,则 OF = 1; 当没有符号数运算溢出时,则 OF = 0;

实际上,当符号位运算产生的进位和最高有效位产生的进位不同时.OF = 1,反之 OF =

1.譬如本例中 OF = C4⊕C3.

答:

a) 符号标志 SF: 数的最高位描述符号位,运算结果最高位为 1,则 SF = 1;否则 SF = 0.

例如 49H + 6DH=B6H=10110110B,SF=1

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc