2018 年广西桂林电子科技大学通信电子电路及 EDA 技术考

研真题 A 卷

一、选择题(每题 2 分,共 20 分)

1.

of 为并联谐振回路的谐振频率,当工作频率

f

f 时,回路呈(

o

)性。

A、纯电阻

B、电感

C、电容

D、不确定

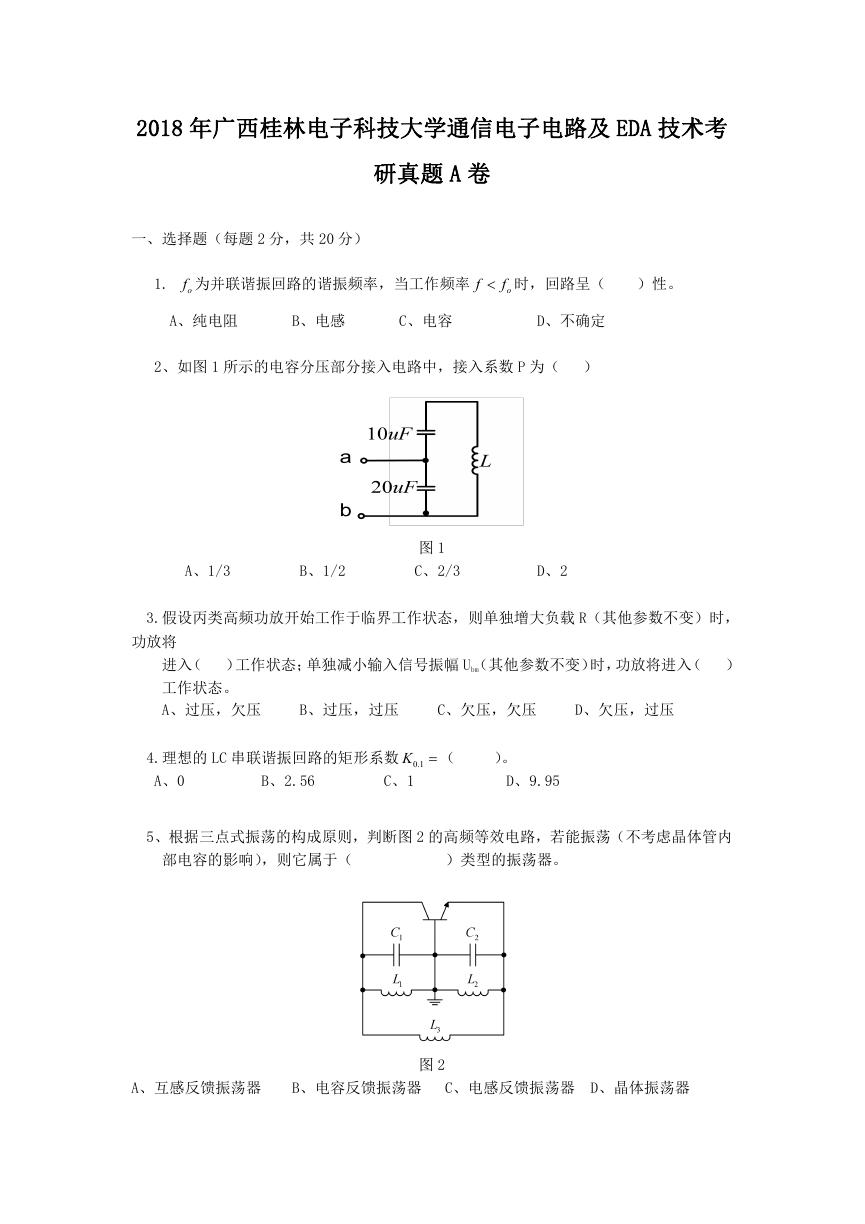

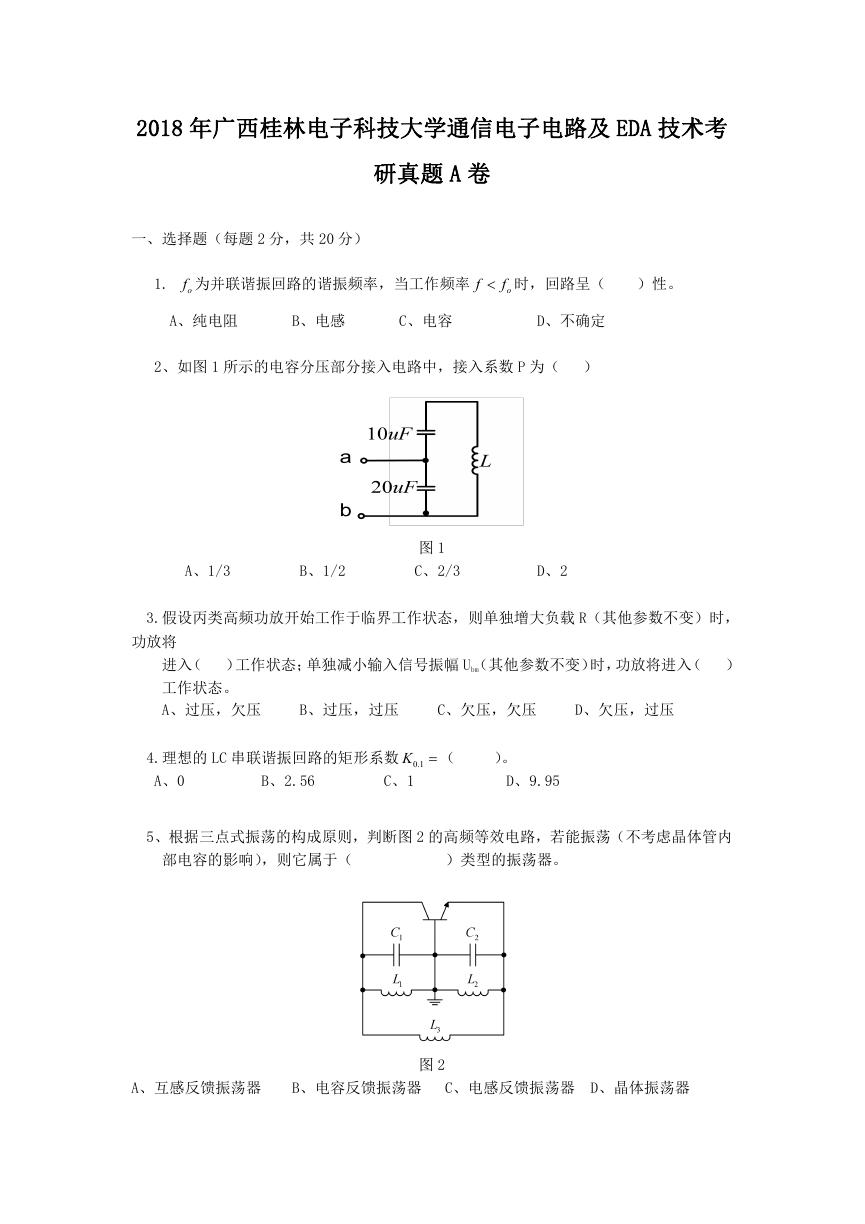

2、如图 1 所示的电容分压部分接入电路中,接入系数 P 为( )

A、1/3

B、1/2

图 1

C、2/3

D、2

3.假设丙类高频功放开始工作于临界工作状态,则单独增大负载 R(其他参数不变)时,

功放将

进入( )工作状态;单独减小输入信号振幅 Ubm(其他参数不变)时,功放将进入( )

工作状态。

A、过压,欠压

B、过压,过压

D、欠压,过压

C、欠压,欠压

4.理想的 LC 串联谐振回路的矩形系数 0.1K (

A、0

B、2.56

C、1

)。

D、9.95

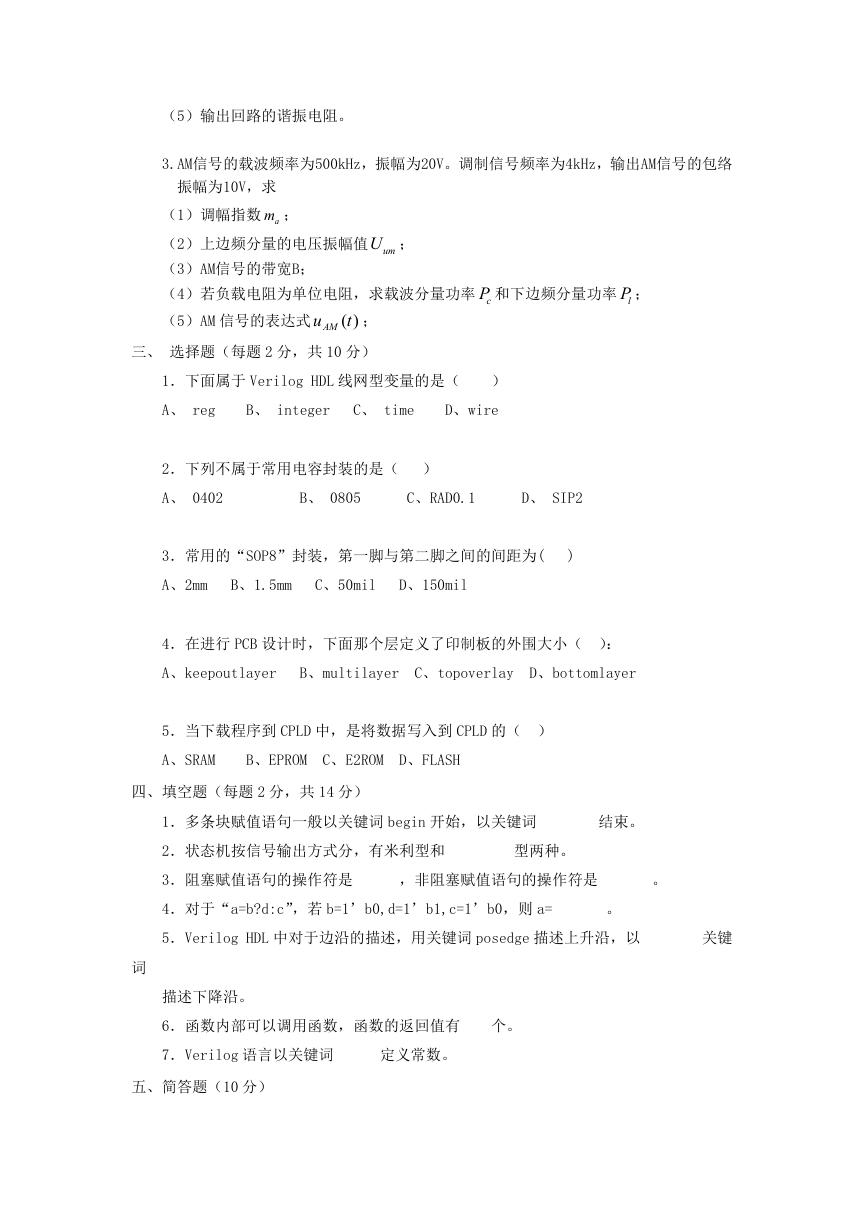

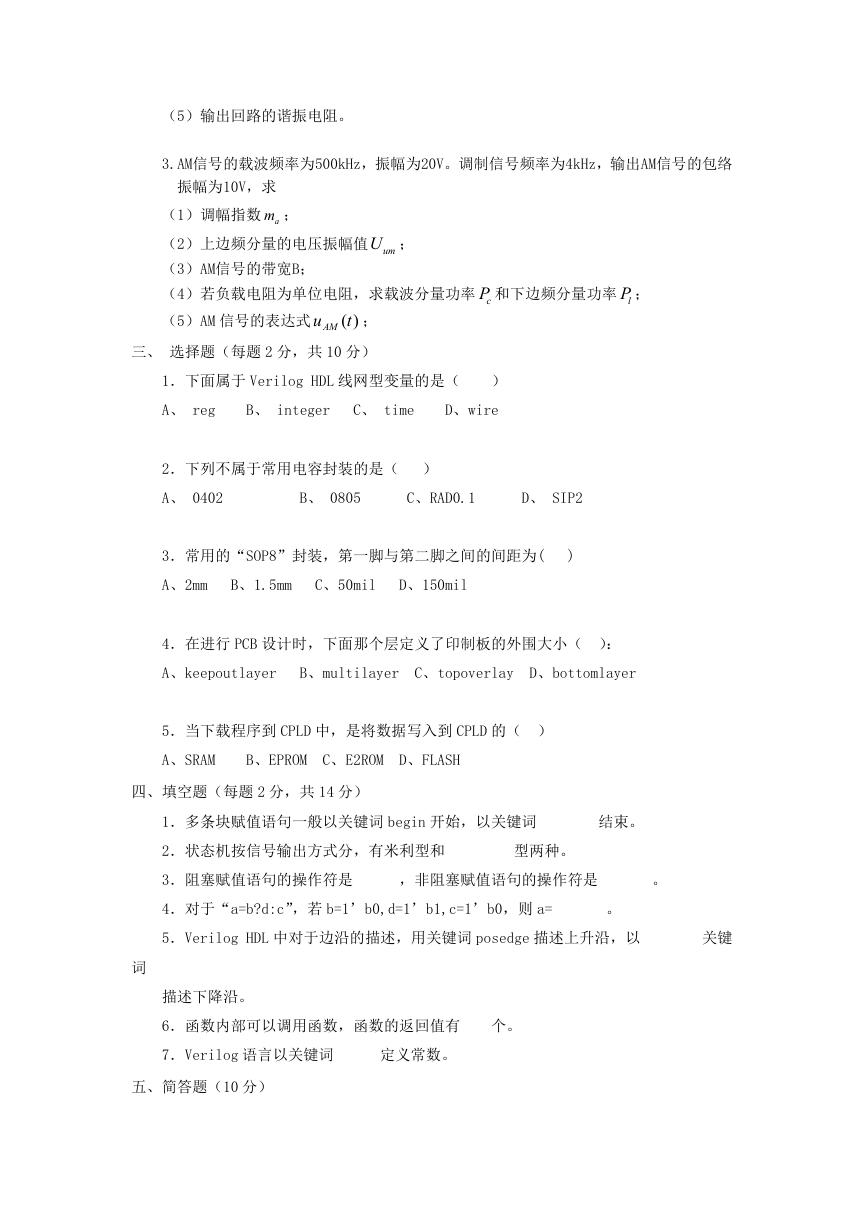

5、根据三点式振荡的构成原则,判断图 2 的高频等效电路,若能振荡(不考虑晶体管内

部电容的影响),则它属于(

)类型的振荡器。

A、互感反馈振荡器

B、电容反馈振荡器 C、电感反馈振荡器 D、晶体振荡器

图 2

�

6.AM 信号的载波频率为 600kHz,振幅为 8V;调制信号频率为 10kHz,振幅为 2V。则上、

下边频的频率值分别为(

A、610kHz,590kHz

)。

B、590kHz,610kHz

C、590kHz,580kHz

D、620kHz,610kHz

7.调角波

( ) 10cos(2

u t

10

6

t

5cos 4000 )

t

,最大相移 m 为(

)

A、2

B、5

C、10

D、0.2

8.下列电路中属于频谱非线性搬移的是(

)。

A、振幅调制

B、同步检波

C、 相位调制

D、混频

9.乘积型同步检波器包含的主要电路不包括(

)

A、相乘器

B、本地载波恢复电路

C、包络检波电路

D、低通滤波器

10.调幅(AM)信号的总功率(

)未调载波功率,调频(FM)信号的总功率(

)

未调载波功率。

A、大于、等于 B、大于、小于 C、等于、小于 D、等于、等于

二、计算题(每题 10 分,共 30 分)

1.如图 3 所示的谐振回路,设电感的损耗忽略不计,信号源接在电感线圈的中心抽头,

20kΩ

sR

。画等效后的电路,并计算:

信号源的幅度为 5mA,信号源内阻

LR

(1)谐振频率 0f ;

(3)有载品质因数;

(2)回路的总电导;

(4)回路的通频带 B 。

10kΩ

, 200pF

C

L

, 1

L

2

5μH

,负载电阻

图 3

2.某工作于临界状态的高频功率放大器电源电压

, 晶 体 管 输 出 特 性 饱 和 线 斜 率

)

通 角

80

0.472

c

1(80 )

(1)计算集电极输出电压幅度 1cmU ;

(2)集电极电流中直流电流 coI ;

(3)集电极电流中基波电流幅度 1cmI ;

(4)集电极输出交流功率 oP ;

cE

18V

crg

,电压利用系数 0.9 ,电流

0.2A/V

。( 0(80 )

0.286

;

�

(5)输出回路的谐振电阻。

3.AM信号的载波频率为500kHz,振幅为20V。调制信号频率为4kHz,输出AM信号的包络

振幅为10V,求

(1)调幅指数 am ;

(2)上边频分量的电压振幅值 umU ;

(3)AM信号的带宽B;

(4)若负载电阻为单位电阻,求载波分量功率 cP 和下边频分量功率 lP ;

(5)AM 信号的表达式 ( )

t ;

AMu

三、 选择题(每题 2 分,共 10 分)

1.下面属于 Verilog HDL 线网型变量的是(

)

A、 reg

B、 integer

C、 time

D、wire

2.下列不属于常用电容封装的是( )

A、 0402

B、 0805

C、RAD0.1

D、 SIP2

3.常用的“SOP8”封装,第一脚与第二脚之间的间距为(

)

A、2mm

B、1.5mm

C、50mil

D、150mil

4.在进行 PCB 设计时,下面那个层定义了印制板的外围大小( ):

A、keepoutlayer

B、multilayer

C、topoverlay

D、bottomlayer

5.当下载程序到 CPLD 中,是将数据写入到 CPLD 的( )

A、SRAM

B、EPROM

C、E2ROM

D、FLASH

四、填空题(每题 2 分,共 14 分)

1.多条块赋值语句一般以关键词 begin 开始,以关键词

结束。

2.状态机按信号输出方式分,有米利型和

型两种。

3.阻塞赋值语句的操作符是

,非阻塞赋值语句的操作符是

。

4.对于“a=b?d:c”,若 b=1’b0,d=1’b1,c=1’b0,则 a=

。

5.Verilog HDL 中对于边沿的描述,用关键词 posedge 描述上升沿,以

关键

词

描述下降沿。

6.函数内部可以调用函数,函数的返回值有

个。

7.Verilog 语言以关键词

定义常数。

五、简答题(10 分)

�

1.Verilog

HDL 语言进行电路设计方法有哪几种?

2、FPGA 芯片主流的生产厂家有哪 3 家?每个厂家列举 1 个型号芯片。

六、阅读以下程序并回答问题(每空 2 分共 16 分)

1、画出下面程序综合出来的电路图。(8 分)

always@(posedge

clk)

begin

q0<=~q2;

q1<= q0;

q2<= q1;

end

addr);

2. Verilog 代码如下:(8 分)

module INST2 (yout ,

output [7:0] yout;

input [2:0] addr;

assign yout[0] = ((~addr[2]) & (~addr[1]) & (~addr[0]));

assign yout[1] = ((~addr[2]) & (~addr[1]) & (addr[0]));

assign yout[2] = ((~addr[2]) & (addr[1]) & (~addr[0]));

assign yout[3] = ((~addr[2]) & (addr[1]) & (addr[0]));

assign yout[4] = ((addr[2]) & (~addr[1]) & (~addr[0]));

assign yout[5] = ((addr[2]) & (~addr[1]) & (addr[0]));

assign yout[6] = ((addr[2]) & (addr[1]) & (~addr[0]));

assign yout[7] = ((addr[2]) & (addr[1]) & (addr[0]));

endmodule

该元件的功能是:____________________(6 分)

Assign 语句属于_______________(2 分)

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc