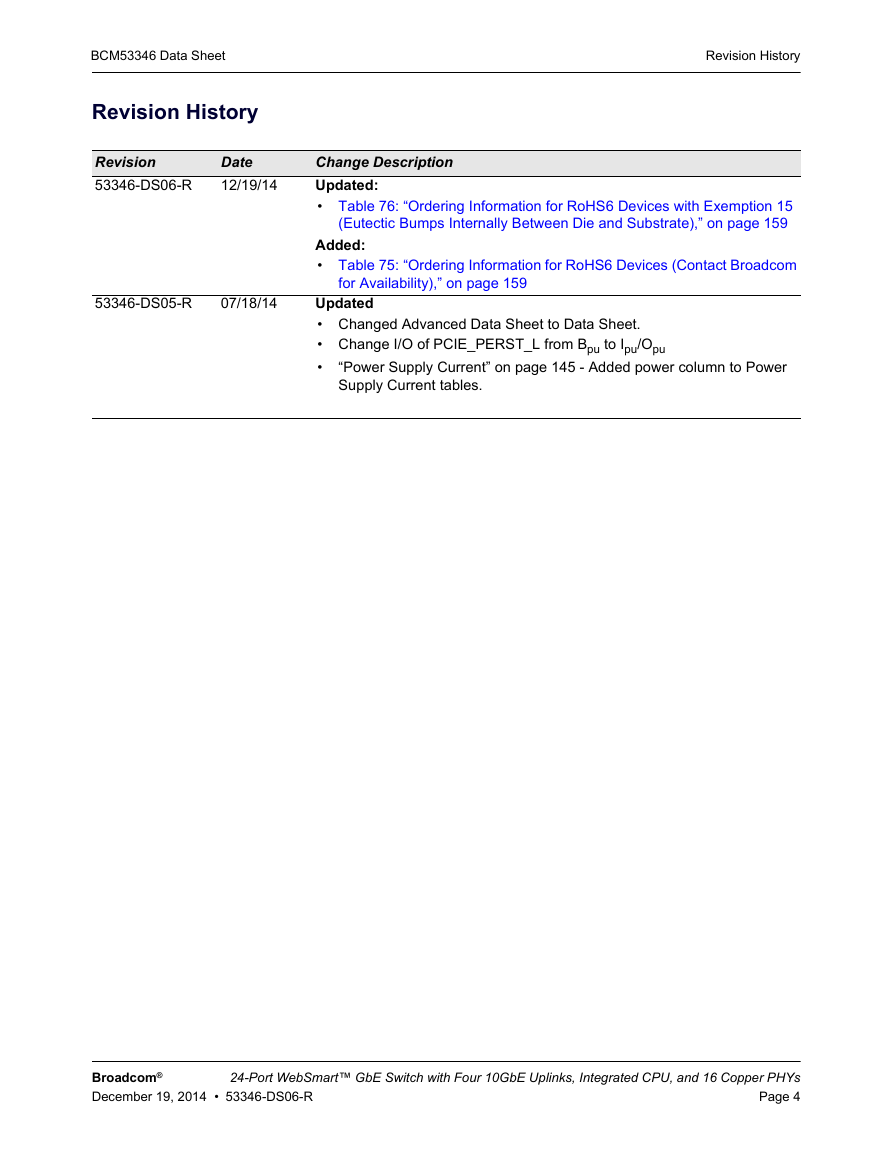

Revision History

Table of Contents

List of Figures

List of Tables

About This Document

Purpose and Audience

Acronyms and Abbreviations

Document Conventions

References

Technical Support

Section 1: Introduction

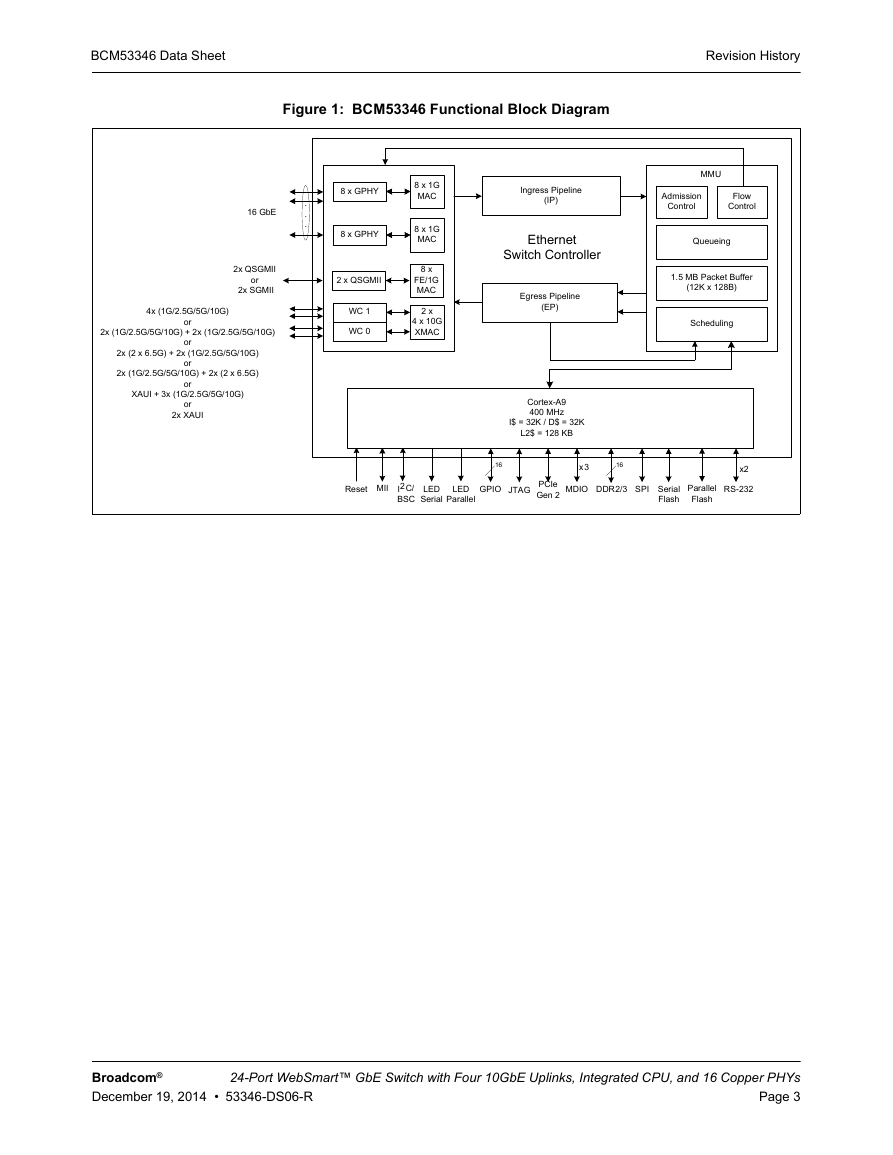

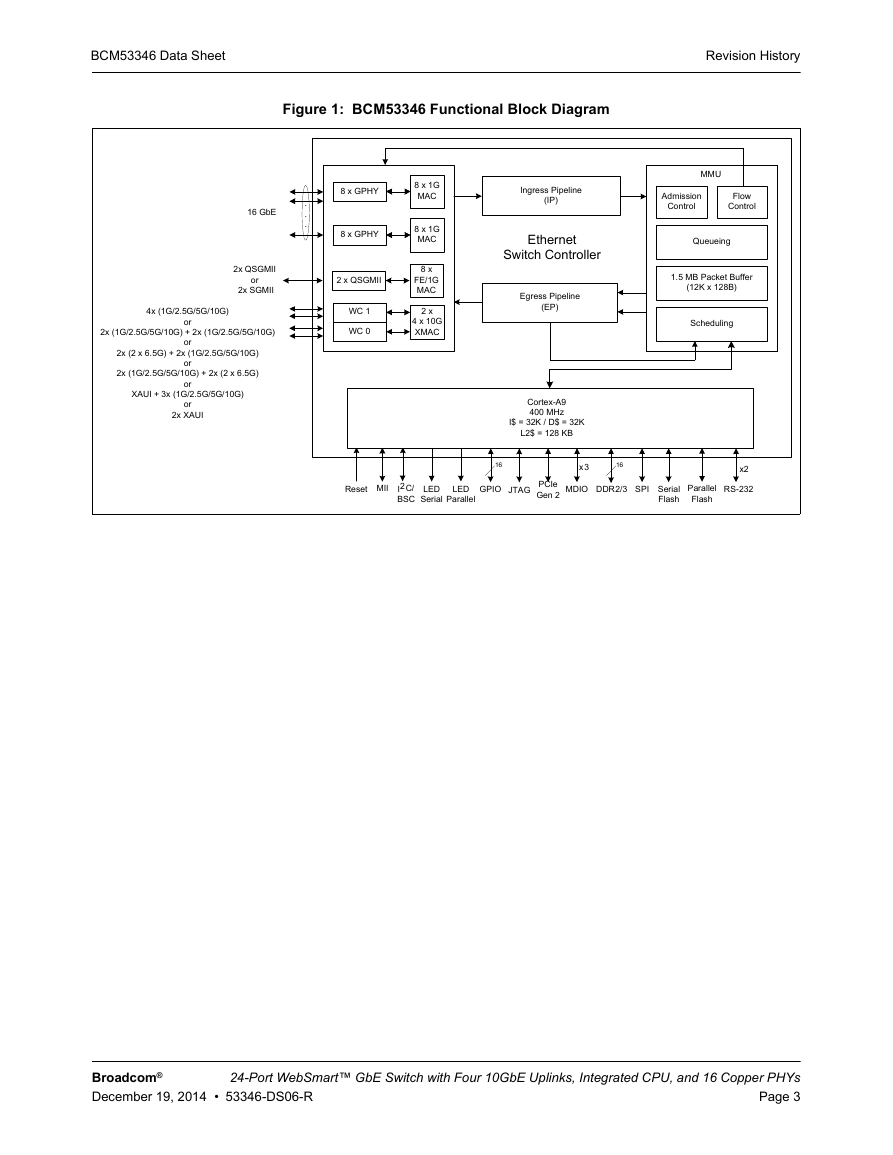

Overview

Ethernet Switch Controller

ARM Cortex-A9 Processor

Section 2: Common Interfaces

System Reset

Power Sequencing

JTAG

Section 3: Ethernet Switch Controller Features Description

Architecture

Feature Overview

Memory

Address Management

Class of Service

Strict Priority-Based Scheduling

Weighted Round Robin Scheduling

Deficit Round Robin Scheduling

Simple Random Early Detection

Backpressure Handling

Per Port Packet Rate (Storm) Control

Mirroring

Spanning Tree Support

IEEE 802.1D Support

Port Filtering Mode A

Port Filtering Mode B

Port Filtering Mode C

IEEE 802.1Q Support

Link Aggregation

Double-Tagging

Forwarding Control Block Mask

ContentAware Processing

Ingress Filter Processor (IFP)

Network Management Support

CPU/Management Interface

External CPU with PCIe Bus

Energy Efficient Ethernet

Section 4: Ethernet Switch Controller System Interfaces

Overview

SerDes Warpcore

TSC Ports

10GbE (XAUI)

HIGIG+/HIGIG2 Interface

HiGig_Lite Frame Structure

HiGig-Duo[13] Interface

1G/2.5G/5G Interface

1GbE (QSGMII/SGMII)

MII Management

Broadcom Serial Interface (BSC)

LED Interfaces

Serial LED Mode

PHY-driven Parallel LED Mode

Serial to Parallel LED Mode

Ethernet Time Synchronization (Synchronous Ethernet)

IEEE 1588

Section 5: Gigabit Ethernet Transceiver

Copper Interface

Encoder

Decoder

Link Monitor

Digital Adaptive Equalizer

Echo Canceler

Crosstalk Canceler

Analog-to-Digital Converter

Clock Recovery/Generator

Baseline Wander Correction

Multimode TX Digital-to-Analog Converter

Stream Cipher

Wire Map and Pair Skew Correction

Automatic MDI Crossover

1000BASE-T Operation

10/100BASE-TX Operation (Auto-Negotiation Enabled)

10/100BASE-TX Operation (Forced Mode)

Full-Duplex Mode

Master/Slave Configuration

Next Page Exchange

Auto-Negotiation

Ethernet@Wirespeed

Ethernet@Wirespeed Example

Enabling/Disabling Ethernet@Wirespeed

Removing Ethernet@Wirespeed Downgrade

Changing the Number of Failed Link Attempts

Monitoring Ethernet@Wirespeed

Super Isolate Mode

Software Enable/Disable

Standby Power-Down Mode

Auto Power-Down (APD) Mode

ADP Mode Enable (Auto-Negotiation Enabled)

Sleep Cycle Settings

Wake Cycle Settings

Section 6: ARM Cortex-A9 Processor Subsystem Functional Description

Cortex-A9

DDR SDRAM Interface

PCI Express Gen-2 Interface

Transaction Layer Interface

Data Link Layer

Physical Layer

Electrical Subblock

Configuration Space

NOR Serial Flash Interface

NOR Parallel Flash Interface

NAND Flash Interface

MIIM/UART/GPIO Interfaces

SPI interface

MII Interface

Section 7: Pin List Description

Signal Name Descriptions

Pin List by Pin Name

Pin List by Signal Name

Section 8: Electrical Specifications

Absolute Maximum Ratings

DC Characteristics

Operating Conditions

Power-Up and Power-Down Specifications

Power Supply Current

Standard 3.3V Signals

PCIe DC Characteristics

BSC Signals

SGMII/SerDes Signals

2.5GbE SerDes Signals

QSGMII SerDes Signals

Warpcore Technology Quad SerDes Signals

MIIM (MDIO) Signals

AC Characteristics

MII Interface Timing

MII Input Timing

MII Output Timing

AC Timing for Reset

BSC AC Characteristics

SPI AC Characteristics

MDIO AC Characteristics

JTAG AC Specifications

NAND Flash Interface Timing

NOR Flash Interface Timing

Synchronous Ethernet Interface Timing

L1_RCVRD_CLK and L1_RCVRD_CLK_BKUP Output Timing

L1_RCVRD_CLK_VALID and L1_RCVRD_CLK Output Timing

QSPI Flash Interface Timing

DDR3 Interface AC Specifications

DDR3 Address and Control Timing

DDR3 Write Timing

DDR3 Read Timing

PCIe Interface Timing

PCIE_REFCLK Timing

PCIe_RX Timing

PCIe_TX Timing

LED Controller Interface

XTAL Clock Requirements

XG_PLL2_REFCLK Clock Requirements

LC_PLL1_REFCLK Clock Requirements

LC_PLL0_REFCLK Clock Requirements

EXT_QS2_CLKP/N Clock Specifications

QSGMII AC Specifications

Transmitter

Receiver

SGMII AC Specifications

SGMII/SerDes Interface Output Timing

SGMII/SerDes Interface Input Timing

2.5GbE SerDes AC Specifications

2.5GbE/SerDes Interface Output Timing

2.5GbE/SerDes Interface Input Timing

Warpcore Technology Serial Interface AC Specification

WCx_TDy Transmit Preemphasis Setting

10GBASE-KR Electrical Characteristics

Transmitter

Receiver

AC-JTAG

Section 9: Thermal Characteristics

Section 10: Mechanical Information

Section 11: Ordering Information

Appendix A: Acronyms and Abbreviations

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc