MEDIATEK CONFIDENTIAL

MT7621

PROGRAMMING

GUIDE

loginid=fan.yang@z-linkelec.com,time=2014-12-01 17:05:26,ip=183.37.105.173,doctitle=MT7621_ProgrammingGuide_Preliminary_Platform.pdf,company=Z-Link Limited 香港瑞聯電子_RLT

�

MT7621 PROGRAMMING GUIDE

MT7621 Overview

includes a high performance 880 MHz MIPS1004Kc CPU core and high speed

The MT7621 SoC

USB3.0/PCIe/SDXC interfaces, which is designed to enable a multitude of high performance, cost-effective IEEE

802.11n/ac applications with a MediaTek (Ralink) WiFi client card.

S

U

B

P

INTC

Timer

SPI

NFI

UARTLx3

GPIO

I2C

I2S

PCM x4

SPDIF

To CPU

interrupts

SPI

NAND

UART

GPIO

/LED

I2C

I2S

PCM

SPDIF

EJTAG

OCP_IF

PHY

Host

SD

PCIe x 3

RBUS

PBUS

Crypto

Engine

Switch

(5GE)

SDXC

USB 3.0/2.0

OCP Bridge

Arbiter

Functional Block Diagram

MIPS 1004Kc

32/32 KB I/D-

Cache per Core

(880 MHz)

PCIe 1.1

PHY

DRAM

Controller

16-Bit DDR2/DDR3

MEDIATEK CONFIDENTIAL

Figure 1-1 MT7621 Block Diagram

RJ45 x5

TMII/MII x1

GDMA/

HSDMA

5-Port EPHY

RGMII

There are several masters (MIPS 1004KEc, USB, PCI Express, SDXC, FE) in the MT7621 SoC on a high

performance, low latency Rbus, (Ralink Bus). In addition, the MT7621 SoC supports lower speed peripherals

such as UART Lite, GPIO, NFI and SPI via a low speed peripheral bus (Pbus). The DDR2/DDR3 controller is the

only bus slave on the Rbus. It includes an Advanced Memory Scheduler to arbitrate the requests from bus

masters, enhancing the performance of memory access intensive tasks.

PGMT7621_V.1.0_130607

loginid=fan.yang@z-linkelec.com,time=2014-12-01 17:05:26,ip=183.37.105.173,doctitle=MT7621_ProgrammingGuide_Preliminary_Platform.pdf,company=Z-Link Limited 香港瑞聯電子_RLT

Page 2 of 349

�

MT7621 PROGRAMMING GUIDE

Table of Contents

MT7621 OVERVIEW

2. REGISTERS

2.1 NOMENCLATURE

2.2 SYSTEM CONTROL

FUNCTIONAL BLOCK DIAGRAM

TABLE OF CONTENTS

1. MIPS 1004KC PROCESSOR

2.2.1 FEATURES

2.2.2 BLOCK DIAGRAM

2.2.3 REGISTERS

2.3.1 FEATURES

2.3.2 BLOCK DIAGRAM

2.3.3 REGISTERS

1.1 FEATURES

1.2 MEMORY MAP SUMMARY

1.3 INTERUPT TABLE SUMMARY

MEDIATEK CONFIDENTIAL

2.6.1 FEATURES

2.6.2 BLOCK DIAGRAM

2.6.3 GPIO PIN MAPPING

2.6.4 REGISTERS

2.7 I2C CONTROLLER

2.7.1 FEATURES

2.7.2 LIST OF REGISTERS

2.8 NAND FLASH INTERFACE

2.8.1 FEATURES

2.8.2 REGISTERS

2.8.3 PROGRAMMING GUIDE

2.9.1 FEATURES

2.9.2 REGISTERS

2.9.3 PROGRAMMING GUIDE

2.4 SYSTEM TICK COUNTER

2.4.1 REGISTERS

2.5 UART LITE

2.5.1 FEATURES

2.5.2 REGISTERS

2.6 PROGRAMMABLE I/O

2.9 NFI ECC CONTROLLER

2.3 TIMER

2.10 PCM CONTROLLER

2.10.1 FEATURES

2.10.2 BLOCK DIAGRAM

2.10.3 LIST OF REGISTERS

2.10.4 PCM CONFIGURATION

2.11 GENERIC DMA CONTROLLER

PGMT7621_V.1.0_130607

loginid=fan.yang@z-linkelec.com,time=2014-12-01 17:05:26,ip=183.37.105.173,doctitle=MT7621_ProgrammingGuide_Preliminary_Platform.pdf,company=Z-Link Limited 香港瑞聯電子_RLT

2

2

3

5

5

7

9

11

11

12

12

12

13

41

41

42

43

48

48

50

50

51

65

65

65

65

67

79

79

80

87

87

88

106

115

115

116

130

134

134

134

136

152

154

Page 3 of 349

�

MT7621 PROGRAMMING GUIDE

154

154

155

156

202

202

202

203

213

213

213

215

220

221

235

235

236

319

319

319

320

325

329

330

333

334

346

349

2.15.1 FEATURES

2.15.2 REGISTERS

2.14 SPDIF TX

2.14.1 REGISTERS

2.15 MEMORY CONTROLLER

2.13.1 FEATURES

2.13.2 BLOCK DIAGRAM

2.13.3 REGISTERS

2.12.1 FEATURES

2.12.2 BLOCK DIAGRAM

2.12.3 REGISTERS

2.13 I2S CONTROLLER

2.16.1 FEATURES

2.16.2 BLOCK DIAGRAM

2.16.3 REGISTERS OF QOS CONTROL

2.16.4 REGISTERS OF RBUS MATRIX

2.11.1 FEATURES

2.11.2 BLOCK DIAGRAM

2.11.3 PERIPHERAL CHANNEL CONNECTION

2.11.4 REGISTERS

2.12 SPI CONTROLLER

MEDIATEK CONFIDENTIAL

2.17 EXTERNAL MC ARBITER

2.17.1 REGISTERS

2.18 ANALOG MACRO CONTROL

2.16 RBUS MATRIX AND QOS ARBITER

2.18.1 REGISTERS

3. LIST

4. REVISION HISTORY

PGMT7621_V.1.0_130607

loginid=fan.yang@z-linkelec.com,time=2014-12-01 17:05:26,ip=183.37.105.173,doctitle=MT7621_ProgrammingGuide_Preliminary_Platform.pdf,company=Z-Link Limited 香港瑞聯電子_RLT

Page 4 of 349

�

MT7621 PROGRAMMING GUIDE

1. MIPS 1004Kc Processor

1.1 Features

Programmable L1 Cache Sizes

MIPS MT Application Specific Extension (ASE)

Support for 2 Virtual Processing Elements (VPEs) per CORE

One Thread Context (TC) per VPE

8-9-stage pipeline

32-bit Address Paths

64-bit Data Paths to Caches

MIPS32 Enhanced Architecture (Release 2) Features

16 bit encodings of 32-bit instructions to improve code density

Special PC-relative instructions for efficient loading of addresses and constants

Data type conversion instructions (ZEB, SEB, ZEH, SEH)

Compact jumps (JRC, JALRC)

Stack frame set-up and tear down “macro” instructions (SAVE and RESTORE)

Standardized Instruction Set Architecture

Vectored interrupts and support for an external interrupt controller

Programmable exception vector base

Atomic interrupt enable/disable

Bit field manipulation instructions

MIPS16e Application Specific Extension

MEDIATEK CONFIDENTIAL

32 dual-entry MIPS32-style JTLB per VPE with variable page sizes

JTLBs are sharable under software control

4-5 entry instruction TLB

8-entry data TLB

– Maximum issue rate of one 32x32 multiply per clock

–

Early-in divide control. Minimum 11, maximum 34 clock latency on divide

Standard Memory Management Unit

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

Individually configurable instruction and data caches

32KB I/D cache

4-way set associative

Up to 9 non-blocking loads

Data cache supports coherent and non-coherent Write-back with write-allocation

32-byte cache line size, doubleword sectored - suitable for standard single-port SRAM

Cache line locking support

Non-blocking prefetches

Duplicate tag array in D-cache allows coherence requests to access the cache in parallel with normal

load/store traffic

OCP Bus Interface Unit (BIU)

32b address and 64b data

Supports bursts of 4x64b

8 entry write buffer - handles eviction data, intervention response, uncached, and uncached

accelerated store data

Simple Byte enable mode allows easier bridging to other bus standards

Extensions for management of front side L2 cache

Intervention port supports memory coherency for use in a 1004K Coherent Processing System

Multiply-Divide Unit

Power Control

–

–

–

No minimum frequency

Support for software-controlled clock divider

Support for extensive use of fine-grain clock gating

PGMT7621_V.1.0_130607

loginid=fan.yang@z-linkelec.com,time=2014-12-01 17:05:26,ip=183.37.105.173,doctitle=MT7621_ProgrammingGuide_Preliminary_Platform.pdf,company=Z-Link Limited 香港瑞聯電子_RLT

Page 5 of 349

�

–

–

–

–

–

–

–

–

Start, stop, and single stepping control

Software breakpoints via the SDBBP instruction

Optional hardware breakpoints on virtual addresses; 0, 2, or 4 instruction and 0,1, or 2 data

breakpoints per VPE

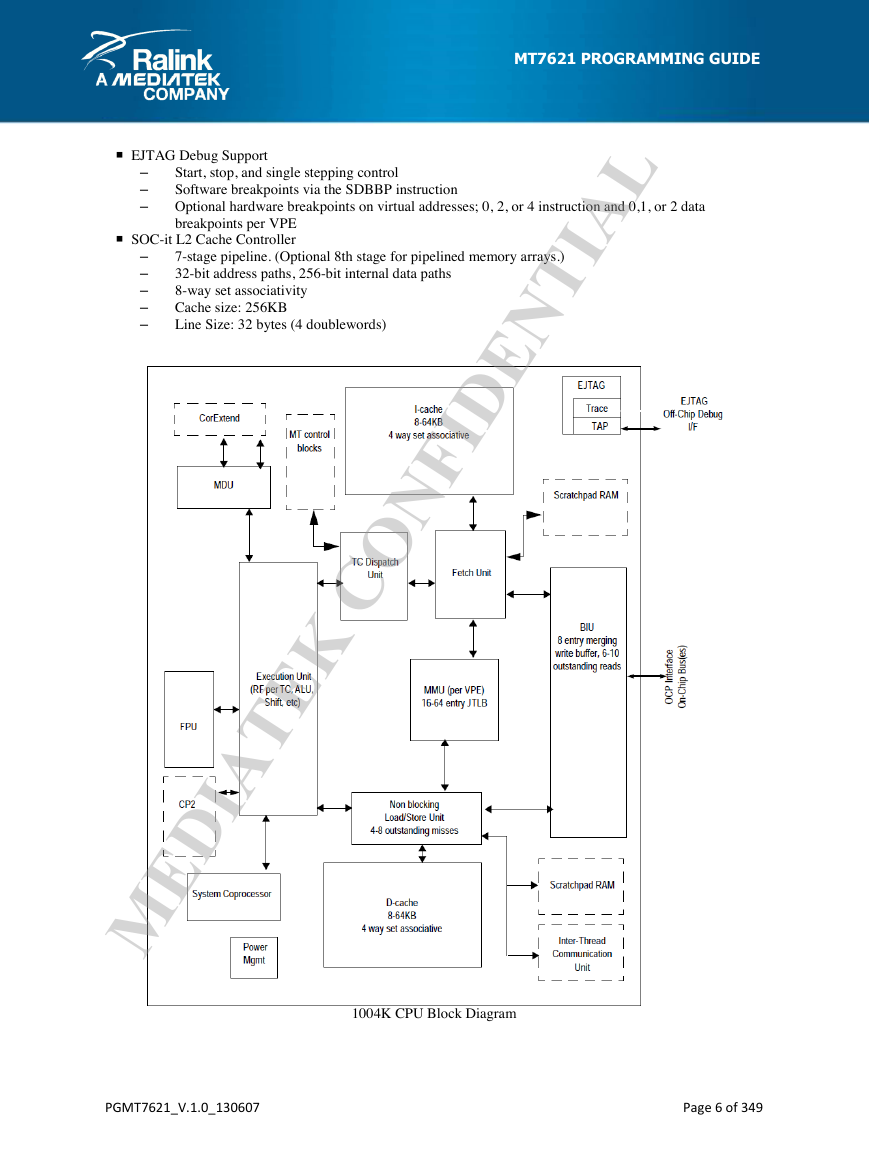

SOC-it L2 Cache Controller

EJTAG Debug Support

7-stage pipeline. (Optional 8th stage for pipelined memory arrays.)

32-bit address paths, 256-bit internal data paths

8-way set associativity

Cache size: 256KB

Line Size: 32 bytes (4 doublewords)

MEDIATEK CONFIDENTIAL

MT7621 PROGRAMMING GUIDE

1004K CPU Block Diagram

PGMT7621_V.1.0_130607

loginid=fan.yang@z-linkelec.com,time=2014-12-01 17:05:26,ip=183.37.105.173,doctitle=MT7621_ProgrammingGuide_Preliminary_Platform.pdf,company=Z-Link Limited 香港瑞聯電子_RLT

Page 6 of 349

�

MT7621 PROGRAMMING GUIDE

MEDIATEK CONFIDENTIAL

Description

DRAM Direct Map

<>

SYSCTL

TIMER

INTCTL

Flash Controller (NOR/SRAM/SDRAM)

Rbus Matrix CTRL

MIPS CNT

GPIO

S/PDIF

DMA_CFG_ARB

I2C

I2S

SPI CSR

UARTLITE 1

UARTLITE 2

UARTLITE 3

ANACTL

<>

<>

PCM (up to 16 channel)

Generic DMA (up to 64 channel)

NAND Controller *(actually 1K in Module)

NAND_ECC Controller *(actually 3K in module)

Crypto Engine

MEM_CTRL (DDRII/DDRIII)

EXT_MC_ARB

HS DMA

<>

<>

Frame Engine (FE SRAM: 0x1E108000~0x1E10DFFF)

PCIe SRAM

Ethernet GMAC

ROM

<>

SDXC

<>

PCI Express

<>

USB Host (U2+U3)

<>

<>

Size

448M

32M

256

256

256

256

256

256

256

256

256

256

256

256

256

256

256

256

2K

2K

2K

2K

2K

2K

4K

4K

4K

4K

32K

960K

56K

8K

32K

32K

64K

32K

32K

256K

256K

256K

256K

64K

1.2 Memory Map Summary

Start

0

1C000000

1E000000

1E000100

1E000200

1E000300

1E000400

1E000500

1E000600

1E000700

1E000800

1E000900

1E000A00

1E000B00

1E000C00

1E000D00

1E000E00

1E000F00

1E001000

1E001800

1E002000

1E002800

1E003000

1E003800

1E004000

1E005000

1E006000

1E007000

1E008000

1E010000

1E100000

1E10E000

1E110000

1E118000

1E120000

1E130000

1E138000

1E140000

1E180000

1E1C0000

1E200000

1E240000

End

1BFFFFFF

1DFFFFFF

1E0000FF

1E0001FF

1E0002FF

1E0003FF

1E0004FF

1E0005FF

1E0006FF

1E0007FF

1E0008FF

1E0009FF

1E000AFF

1E000BFF

1E000CFF

1E000DFF

1E000EFF

1E000FFF

1E0017FF

1E001FFF

1E0027FF

1E002FFF

1E0037FF

1E003FFF

1E004FFF

1E005FFF

1E006FFF

1E007FFF

1E00FFFF

1E0FFFFF

1E10DFFF

1E10FFFF

1E117FFF

1E11FFFF

1E12FFFF

1E137FFF

1E13FFFF

1E17FFFF

1E1BFFFF

1E1FFFFF

1E23FFFF

1E24FFFF

PGMT7621_V.1.0_130607

loginid=fan.yang@z-linkelec.com,time=2014-12-01 17:05:26,ip=183.37.105.173,doctitle=MT7621_ProgrammingGuide_Preliminary_Platform.pdf,company=Z-Link Limited 香港瑞聯電子_RLT

Page 7 of 349

�

MT7621 PROGRAMMING GUIDE

1E250000

1E800000

1EC00000

1FBC0000

1FBE0000

1FBF0000

1FBF8000

1FC00000

20000000

24000000

60000000

70000000

1E7FFFFF

1EBFFFFF

1FBBFFFF

1FBDFFFF

1FBEFFFF

1FBF7FFF

1FBFFFFF

1FFFFFFF

23FFFFFF

5FFFFFFF

6FFFFFFF

7FFFFFFF

5824K

4M

16128K

128

64K

32K

32K

4M

64M

960M

256M

256M

<>

PCIE Direct Access for iNIC

<>

CM_GIC

<>

CM_CPC

CM_GCR

ROM/SPI FLASH Direct Access

DRAM Re-Map

<>

PCIE Direct Access

<>

MEDIATEK CONFIDENTIAL

PGMT7621_V.1.0_130607

loginid=fan.yang@z-linkelec.com,time=2014-12-01 17:05:26,ip=183.37.105.173,doctitle=MT7621_ProgrammingGuide_Preliminary_Platform.pdf,company=Z-Link Limited 香港瑞聯電子_RLT

Page 8 of 349

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc