基于基于FPGA的单边带调制解调系统

的单边带调制解调系统

单边带通信是目前应用比较广泛并具有占用较窄频带特点的一种通信方法。本文着重介绍单边带调制解调技

术,采用DSP Builder设计流程,结合Modelsim对Signal Compiler生成的test bench文件进行仿真,在QuartusII

环境下编译生成VHDL语言,组建工程,下载至硬件,利用Signal Tap II Logic Analyzer观察硬件输出波形。

摘摘 要:要:

关键词:

关键词: 单边带;调制解调;DSP Builder

1 单边带调制解调的算法

单边带调制解调的算法

单边带(SSB)调制属于幅度调制中的一种。其利用一个边带进行通信,提高了信道的利用率,也避免了不必要的功率发

射。SSB调制既可以用模拟方法实现,也可以转换成数字方法实现。其方法有3种:经典滤波器(Filter)方法、Weaver算法和

Hartley算法。这里着重介绍滤波法。

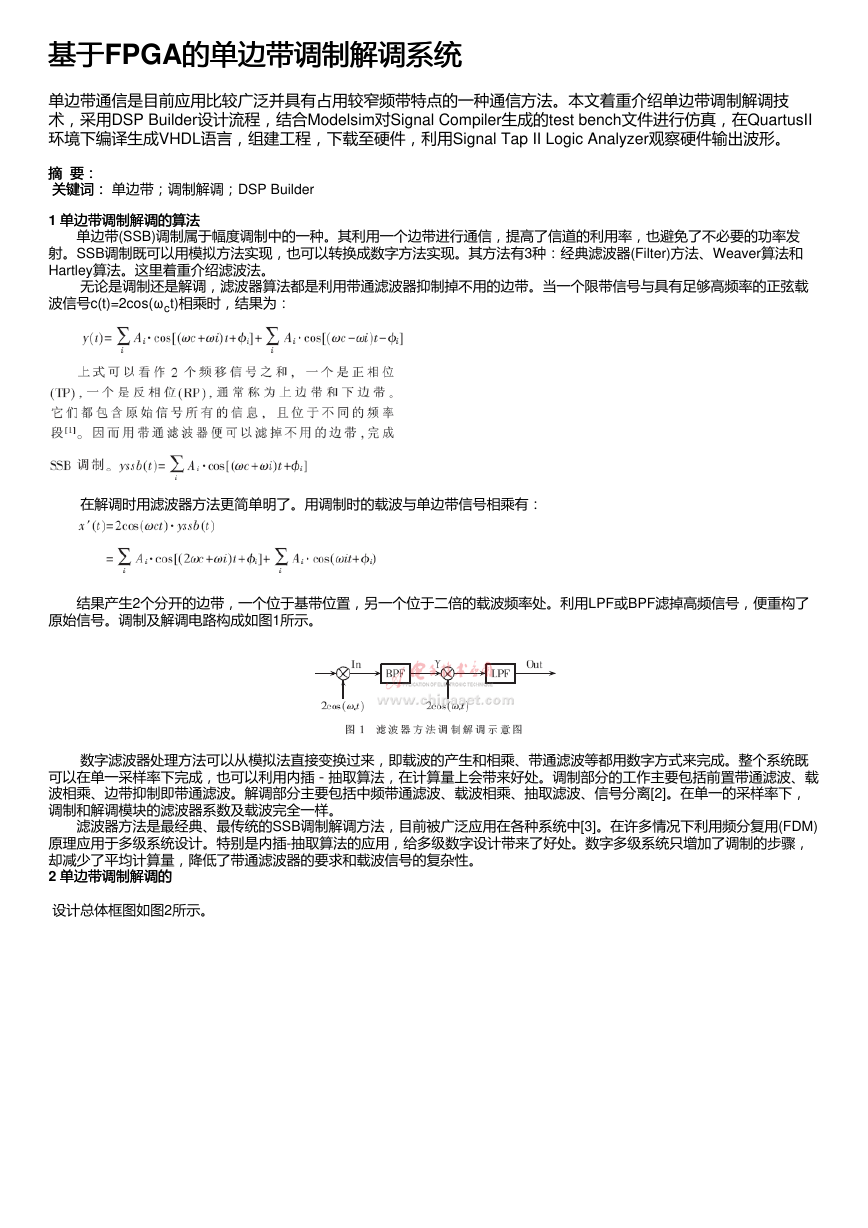

无论是调制还是解调,滤波器算法都是利用带通滤波器抑制掉不用的边带。当一个限带信号与具有足够高频率的正弦载

波信号c(t)=2cos(ωct)相乘时,结果为:

在解调时用滤波器方法更简单明了。用调制时的载波与单边带信号相乘有:

结果产生2个分开的边带,一个位于基带位置,另一个位于二倍的载波频率处。利用LPF或BPF滤掉高频信号,便重构了

原始信号。调制及解调电路构成如图1所示。

数字滤波器处理方法可以从模拟法直接变换过来,即载波的产生和相乘、带通滤波等都用数字方式来完成。整个系统既

可以在单一采样率下完成,也可以利用内插-抽取算法,在计算量上会带来好处。调制部分的工作主要包括前置带通滤波、载

波相乘、边带抑制即带通滤波。解调部分主要包括中频带通滤波、载波相乘、抽取滤波、信号分离[2]。在单一的采样率下,

调制和解调模块的滤波器系数及载波完全一样。

滤波器方法是最经典、最传统的SSB调制解调方法,目前被广泛应用在各种系统中[3]。在许多情况下利用频分复用(FDM)

原理应用于多级系统设计。特别是内插-抽取算法的应用,给多级数字设计带来了好处。数字多级系统只增加了调制的步骤,

却减少了平均计算量,降低了带通滤波器的要求和载波信号的复杂性。

2 单边带调制解调的

单边带调制解调的

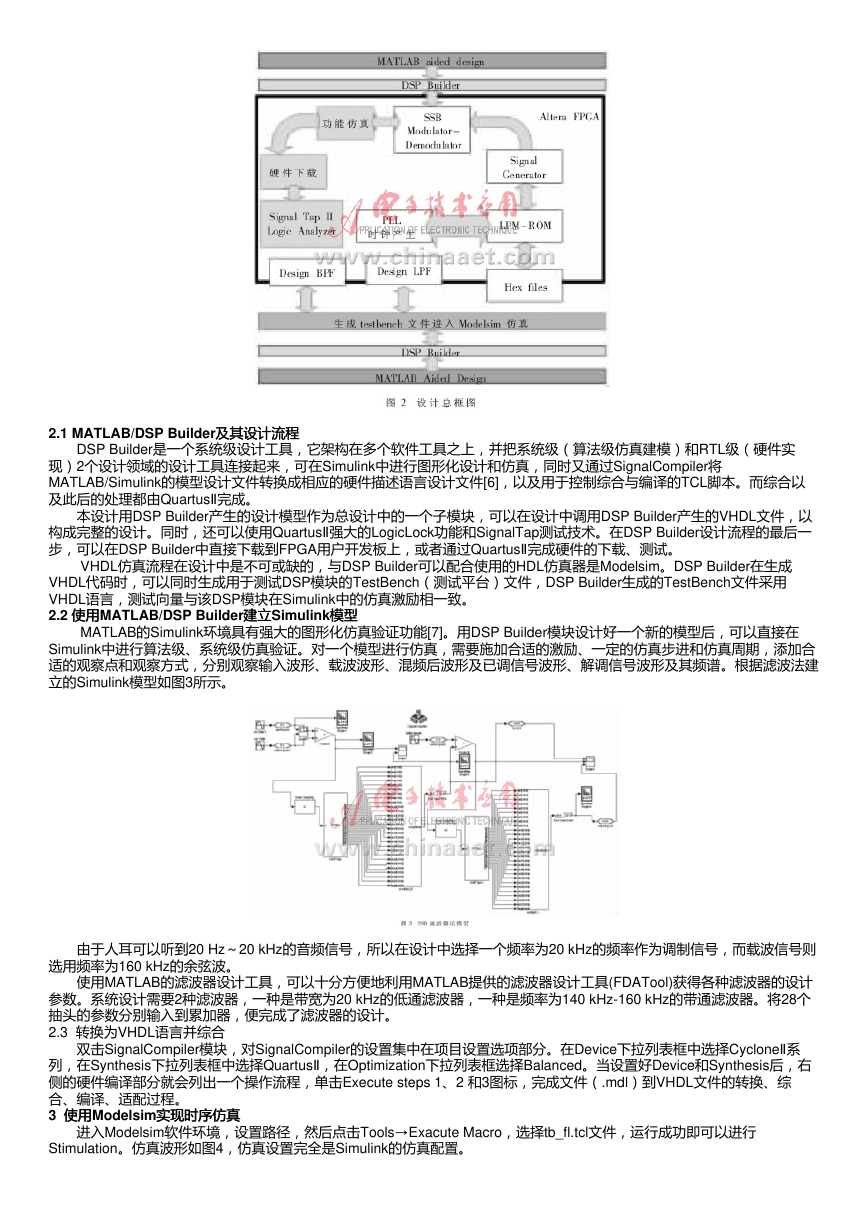

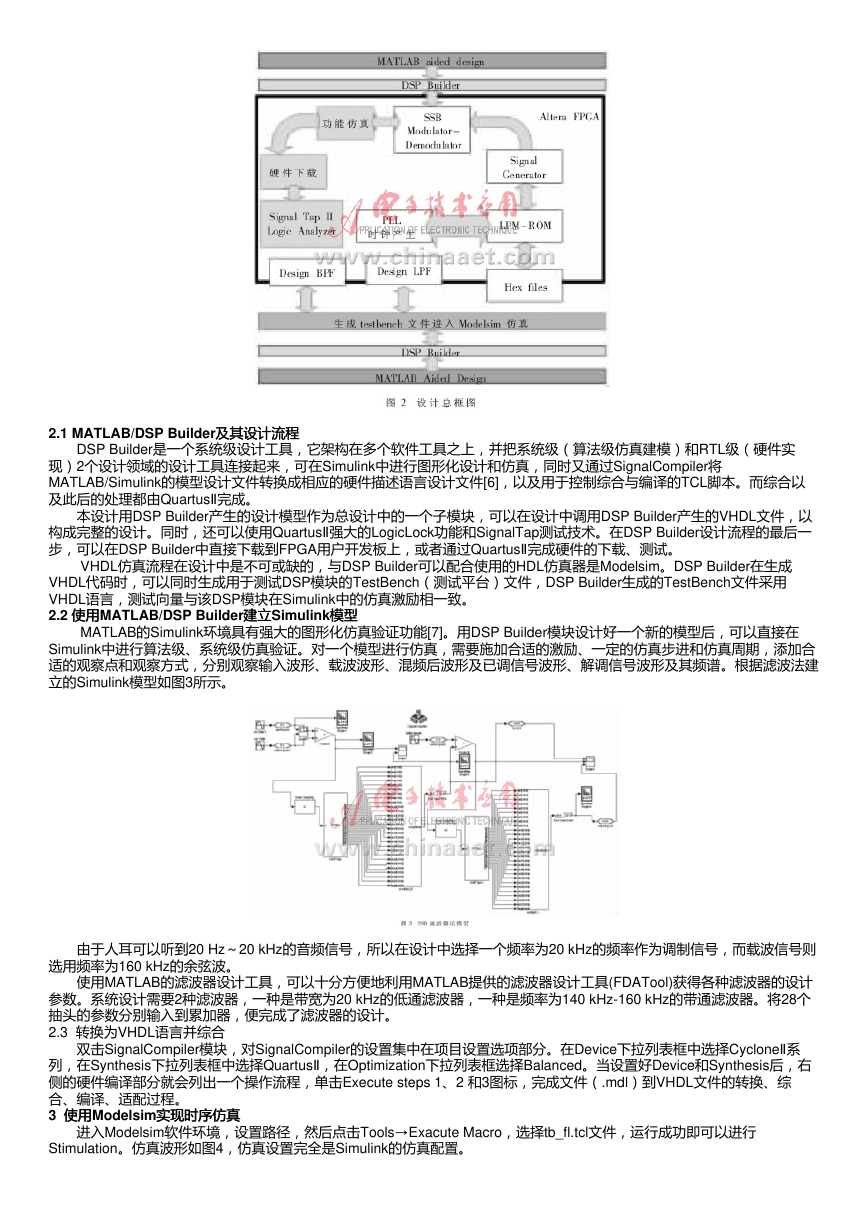

设计总体框图如图2所示。

�

2.1 MATLAB/DSP Builder及其设计流程

及其设计流程

DSP Builder是一个系统级设计工具,它架构在多个软件工具之上,并把系统级(算法级仿真建模)和RTL级(硬件实

现)2个设计领域的设计工具连接起来,可在Simulink中进行图形化设计和仿真,同时又通过SignalCompiler将

MATLAB/Simulink的模型设计文件转换成相应的硬件描述语言设计文件[6],以及用于控制综合与编译的TCL脚本。而综合以

及此后的处理都由QuartusⅡ完成。

本设计用DSP Builder产生的设计模型作为总设计中的一个子模块,可以在设计中调用DSP Builder产生的VHDL文件,以

构成完整的设计。同时,还可以使用QuartusⅡ强大的LogicLock功能和SignalTap测试技术。在DSP Builder设计流程的最后一

步,可以在DSP Builder中直接下载到FPGA用户开发板上,或者通过QuartusⅡ完成硬件的下载、测试。

VHDL仿真流程在设计中是不可或缺的,与DSP Builder可以配合使用的HDL仿真器是Modelsim。DSP Builder在生成

VHDL代码时,可以同时生成用于测试DSP模块的TestBench(测试平台)文件,DSP Builder生成的TestBench文件采用

VHDL语言,测试向量与该DSP模块在Simulink中的仿真激励相一致。

2.2 使用使用MATLAB/DSP Builder建立建立Simulink模型模型

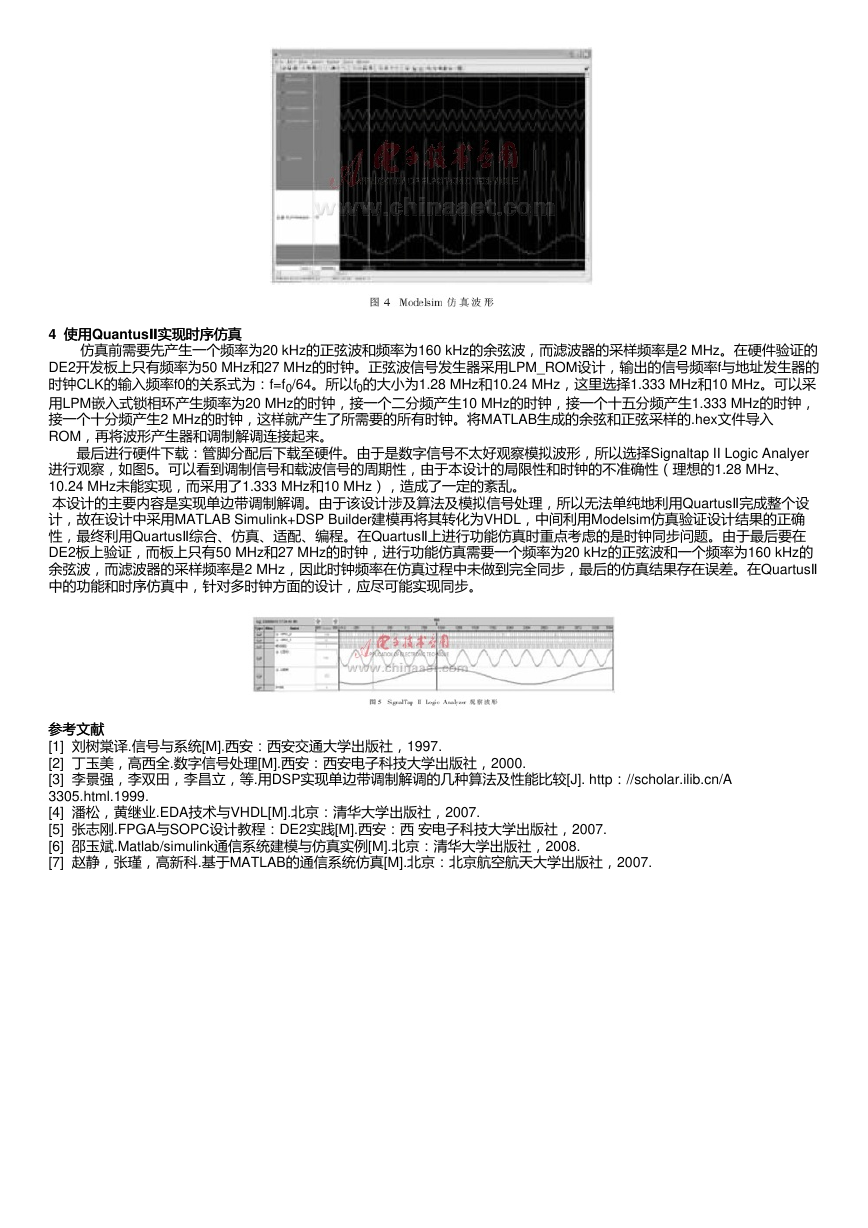

MATLAB的Simulink环境具有强大的图形化仿真验证功能[7]。用DSP Builder模块设计好一个新的模型后,可以直接在

Simulink中进行算法级、系统级仿真验证。对一个模型进行仿真,需要施加合适的激励、一定的仿真步进和仿真周期,添加合

适的观察点和观察方式,分别观察输入波形、载波波形、混频后波形及已调信号波形、解调信号波形及其频谱。根据滤波法建

立的Simulink模型如图3所示。

由于人耳可以听到20 Hz~20 kHz的音频信号,所以在设计中选择一个频率为20 kHz的频率作为调制信号,而载波信号则

选用频率为160 kHz的余弦波。

使用MATLAB的滤波器设计工具,可以十分方便地利用MATLAB提供的滤波器设计工具(FDATool)获得各种滤波器的设计

参数。系统设计需要2种滤波器,一种是带宽为20 kHz的低通滤波器,一种是频率为140 kHz-160 kHz的带通滤波器。将28个

抽头的参数分别输入到累加器,便完成了滤波器的设计。

2.3 转换为VHDL语言并综合

双击SignalCompiler模块,对SignalCompiler的设置集中在项目设置选项部分。在Device下拉列表框中选择CycloneⅡ系

列,在Synthesis下拉列表框中选择QuartusⅡ,在Optimization下拉列表框选择Balanced。当设置好Device和Synthesis后,右

侧的硬件编译部分就会列出一个操作流程,单击Execute steps 1、2 和3图标,完成文件(.mdl)到VHDL文件的转换、综

合、编译、适配过程。

3 使用使用Modelsim实现时序仿真

实现时序仿真

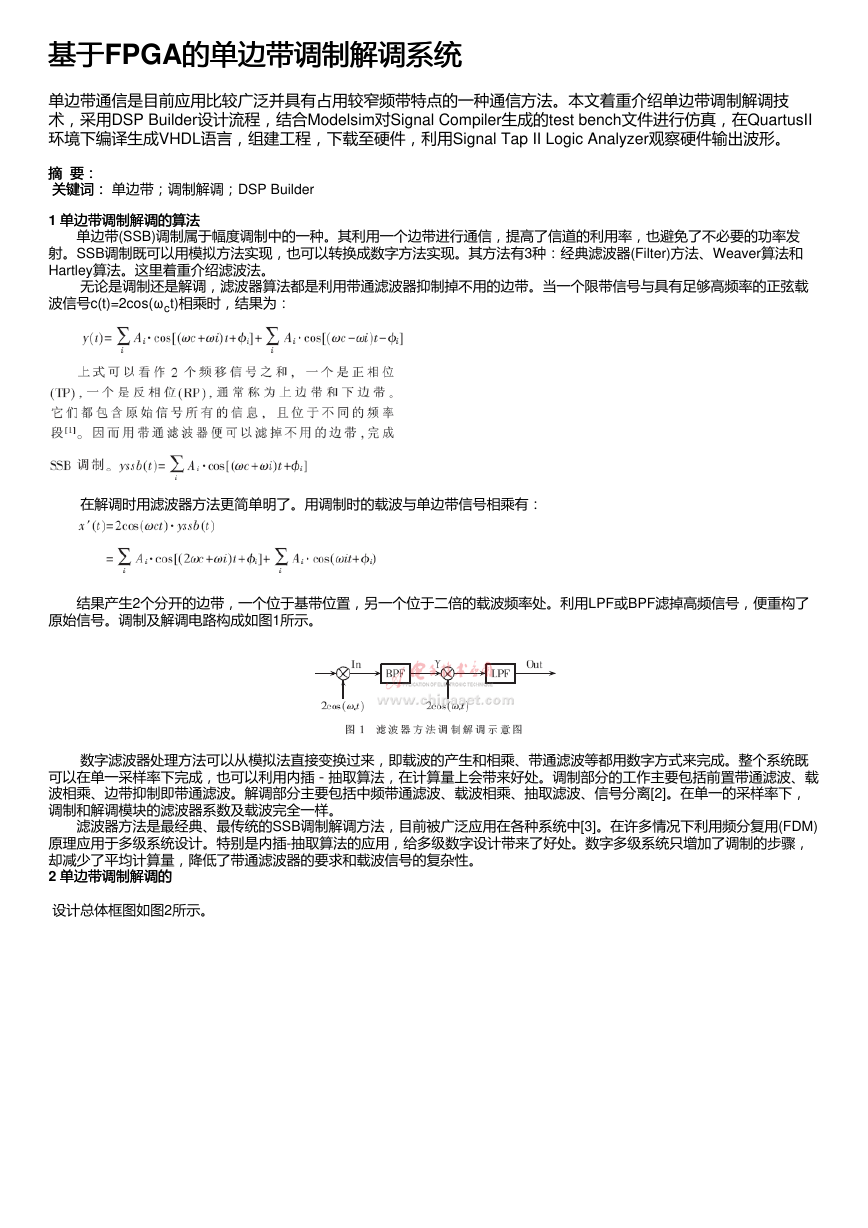

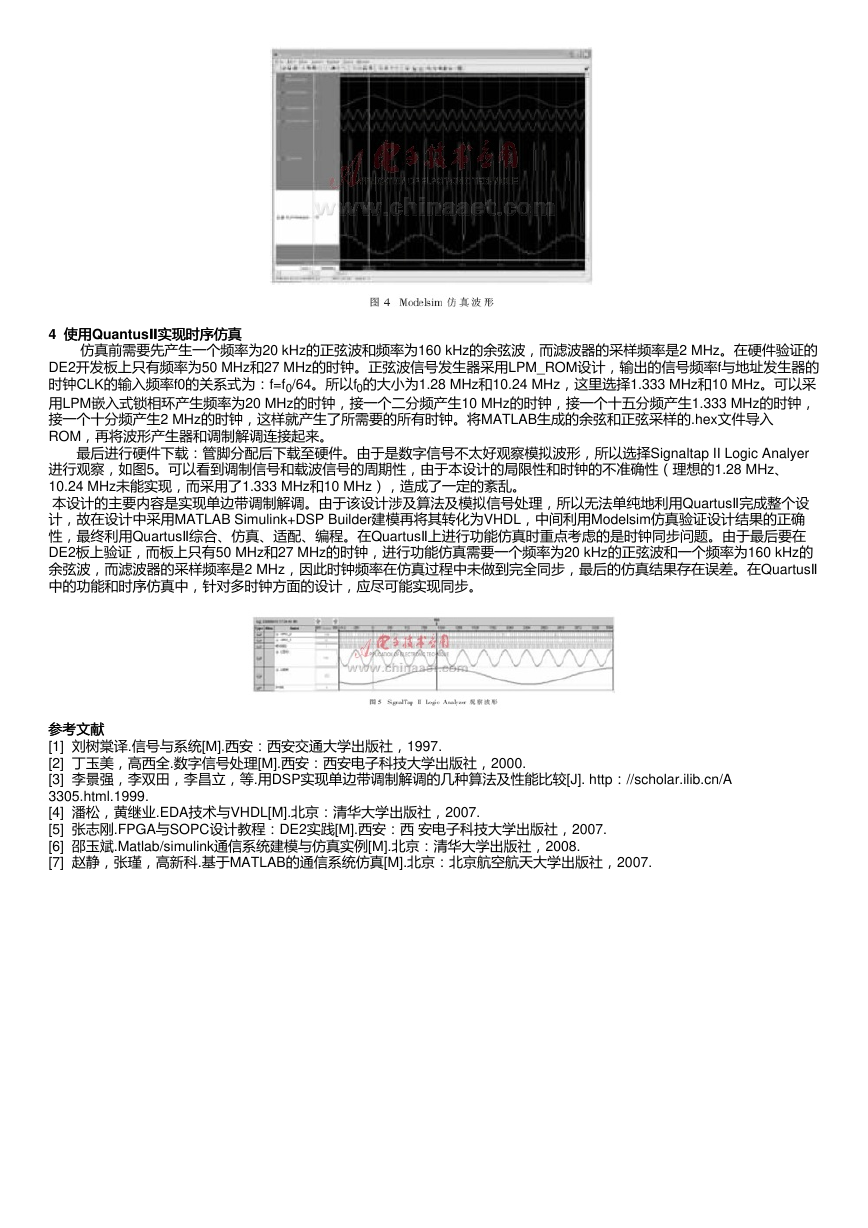

进入Modelsim软件环境,设置路径,然后点击Tools→Exacute Macro,选择tb_fl.tcl文件,运行成功即可以进行

Stimulation。仿真波形如图4,仿真设置完全是Simulink的仿真配置。

�

4 使用使用QuantusⅡ实现时序仿真

实现时序仿真

仿真前需要先产生一个频率为20 kHz的正弦波和频率为160 kHz的余弦波,而滤波器的采样频率是2 MHz。在硬件验证的

DE2开发板上只有频率为50 MHz和27 MHz的时钟。正弦波信号发生器采用LPM_ROM设计,输出的信号频率f与地址发生器的

时钟CLK的输入频率f0的关系式为:f=f0/64。所以f0的大小为1.28 MHz和10.24 MHz,这里选择1.333 MHz和10 MHz。可以采

用LPM嵌入式锁相环产生频率为20 MHz的时钟,接一个二分频产生10 MHz的时钟,接一个十五分频产生1.333 MHz的时钟,

接一个十分频产生2 MHz的时钟,这样就产生了所需要的所有时钟。将MATLAB生成的余弦和正弦采样的.hex文件导入

ROM,再将波形产生器和调制解调连接起来。

最后进行硬件下载:管脚分配后下载至硬件。由于是数字信号不太好观察模拟波形,所以选择Signaltap II Logic Analyer

进行观察,如图5。可以看到调制信号和载波信号的周期性,由于本设计的局限性和时钟的不准确性(理想的1.28 MHz、

10.24 MHz未能实现,而采用了1.333 MHz和10 MHz),造成了一定的紊乱。

本设计的主要内容是实现单边带调制解调。由于该设计涉及算法及模拟信号处理,所以无法单纯地利用QuartusⅡ完成整个设

计,故在设计中采用MATLAB Simulink+DSP Builder建模再将其转化为VHDL,中间利用Modelsim仿真验证设计结果的正确

性,最终利用QuartusⅡ综合、仿真、适配、编程。在QuartusⅡ上进行功能仿真时重点考虑的是时钟同步问题。由于最后要在

DE2板上验证,而板上只有50 MHz和27 MHz的时钟,进行功能仿真需要一个频率为20 kHz的正弦波和一个频率为160 kHz的

余弦波,而滤波器的采样频率是2 MHz,因此时钟频率在仿真过程中未做到完全同步,最后的仿真结果存在误差。在QuartusⅡ

中的功能和时序仿真中,针对多时钟方面的设计,应尽可能实现同步。

参考文献

参考文献

[1] 刘树棠译.信号与系统[M].西安:西安交通大学出版社,1997.

[2] 丁玉美,高西全.数字信号处理[M].西安:西安电子科技大学出版社,2000.

[3] 李景强,李双田,李昌立,等.用DSP实现单边带调制解调的几种算法及性能比较[J]. http://scholar.ilib.cn/A

3305.html.1999.

[4] 潘松,黄继业.EDA技术与VHDL[M].北京:清华大学出版社,2007.

[5] 张志刚.FPGA与SOPC设计教程:DE2实践[M].西安:西 安电子科技大学出版社,2007.

[6] 邵玉斌.Matlab/simulink通信系统建模与仿真实例[M].北京:清华大学出版社,2008.

[7] 赵静,张瑾,高新科.基于MATLAB的通信系统仿真[M].北京:北京航空航天大学出版社,2007.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc