慧净电子好评资料包,赠送给各位好人,好人一生平安,一生辛福

慧净电子 HJ-C52 开发板---最新配套 58 课 51 单片机视频教程

小学生 4 年级水平的同学都能看教程学会单片机技术

目 录

慧净电子 -做人人都买得起的单片机开发板 单片机资料下载网址:WWW.HJMCU.COM

�

第 1 节 引言 ……………………………………………………………2

1.1 数字频率计概述…………………………………………………………………………2

1.2 频率测量仪的设计思路与频率的计算…………………………………………………2

1.3 基本设计原理……………………………………………………………………………3

第 2 节 数字频率计(低频)的硬件结构设计…………………………4

2.1 系统硬件的构成…………………………………………………………………………4

2.2 系统工作原理图…………………………………………………………………………4

2.3AT89C51 单片机及其引脚说明 …………………………………………………………5

2.4 信号调理及放大整形模块………………………………………………………………7

2.5 时基信号产生电路………………………………………………………………………7

2.6 显示模块…………………………………………………………………………………8

第 3 节 软件设计………………………………………………………12

3.1 定时计数 ………………………………………………………………………………12

3.2 量程转换 ………………………………………………………………………………12

3.3 BCD 转换…………………………………………………………………………………12

3.4 LCD 显示…………………………………………………………………………………12

第 4 节 结束语 ……………………………………………………… 13

参考文献 ………………………………………………………………14

附录 汇编源程序代码…………………………………………………15

基于 51 单片机的数字频率计

1

�

第 1 节 引言

本应用系统设计的目的是通过在“单片机原理及应用”课堂上学习的知识,

以及查阅资料,培养一种自学的能力。并且引导一种创新的思维,把学到的知识

应用到日常生活当中。在设计的过程中,不断的学习,思考和同学间的相互讨论,

运用科学的分析问题的方法解决遇到的困难,掌握单片机系统一般的开发流程,

学会对常见问题的处理方法,积累设计系统的经验,充分发挥教学与实践的结合。

全能提高个人系统开发的综合能力,开拓了思维,为今后能在相应工作岗位上的

工作打下了坚实的基础。

1.1 数字频率计概述

数字频率计是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量

仪器。它是一种用十进制数字显示被测信号频率的数字测量仪器。它的基本功能

是测量正弦信号,方波信号及其他各种单位时间内变化的物理量。在进行模拟、

数字电路的设计、安装、调试过程中,由于其使用十进制数显示,测量迅速,精

确度高,显示直观,经常要用到频率计。

本数字频率计将采用定时、计数的方法测量频率,采用一个 1602A LCD 显示

器动态显示 6 位数。测量范围从 1Hz—10kHz 的正弦波、方波、三角波,时基宽

度为 1us,10us,100us,1ms。用单片机实现自动测量功能。

基本设计原理是直接用十进制数字显示被测信号频率的一种测量装置。它以

测量周期的方法对正弦波、方波、三角波的频率进行自动的测量。

1.2 频率测量仪的设计思路与频率的计算

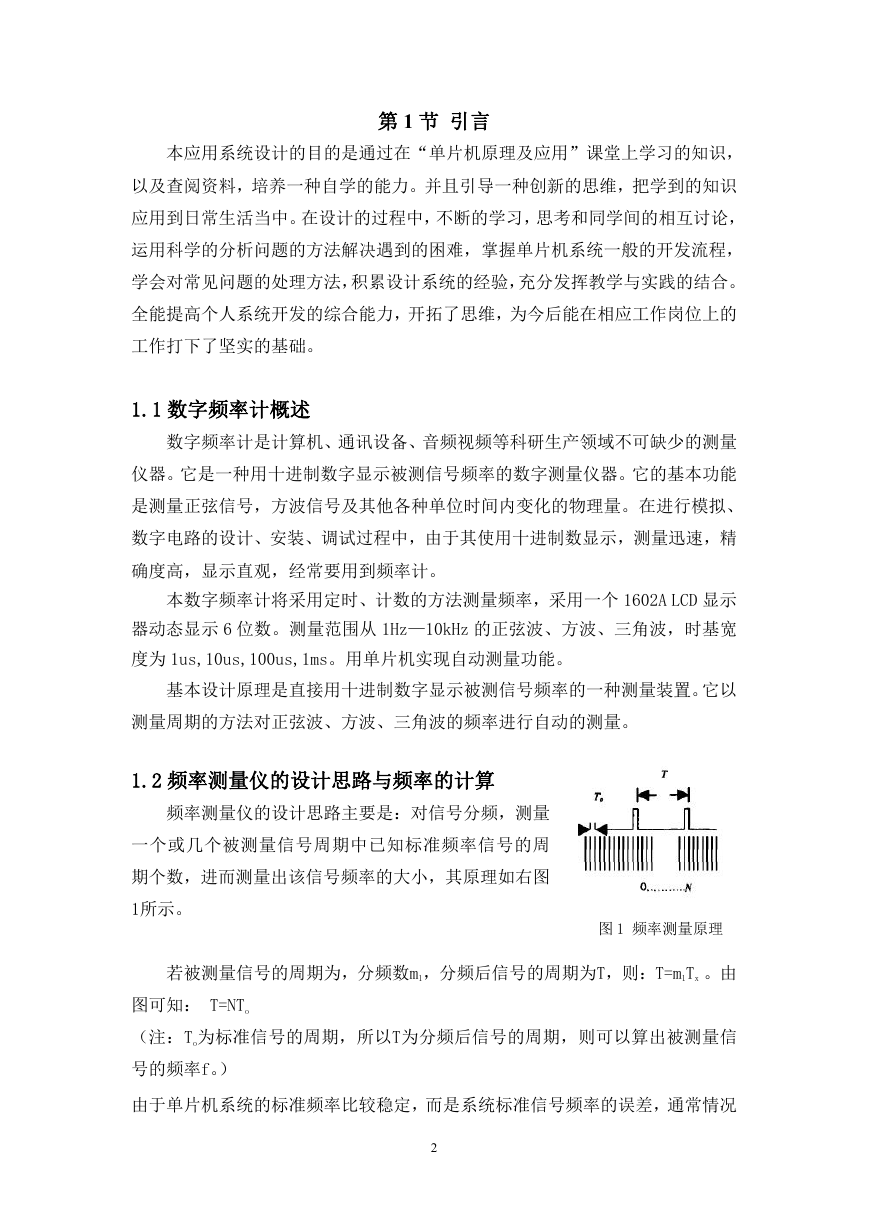

频率测量仪的设计思路主要是:对信号分频,测量

一个或几个被测量信号周期中已知标准频率信号的周

期个数,进而测量出该信号频率的大小,其原理如右图

1所示。

图 1 频率测量原理

若被测量信号的周期为,分频数m1,分频后信号的周期为T,则:T=m1Tx 。由

图可知: T=NTo

(注:To为标准信号的周期,所以T为分频后信号的周期,则可以算出被测量信

号的频率f。)

由于单片机系统的标准频率比较稳定,而是系统标准信号频率的误差,通常情况

2

�

下很小;而系统的量化误差小于 1,所以由式 T=NTo 可知,频率测量的误差主要

取决于 N 值的大小,N 值越大,误差越小,测量的精度越高。

1.3 基本设计原理

基本设计原理是直接用十进制数字显示被测信号频率的一种测量装置。它以

测量周期的方法对正弦波、方波、三角波的频率进行自动的测量。

所谓“频率”,就是周期性信号在单位时间(1s)内变化的次数。若在一定

时间间隔 T 内测得这个周期性信号的重复变化次数 N,则其频率可表示为 f=N/T。

其中脉冲形成电路的作用是将被测信号变成脉冲信号,其重复频率等于被测频率

fx。时间基准信号发生器提供标准的时间脉冲信号,若其周期为 1s,则门控电路

的输出信号持续时间亦准确地等于 1s。闸门电路由标准秒信号进行控制,当秒信

号来到时,闸门开通,被测脉冲信号通过闸门送到计数译码显示电路。秒信号结

束时闸门关闭,计数器停止计数。由于计数器计得的脉冲数 N 是在 1 秒时间内

的累计数,所以被测频率 fx=NHz。

3

�

第2节 数字频率计(低频)的硬件结构设计

2.1 系统硬件的构成

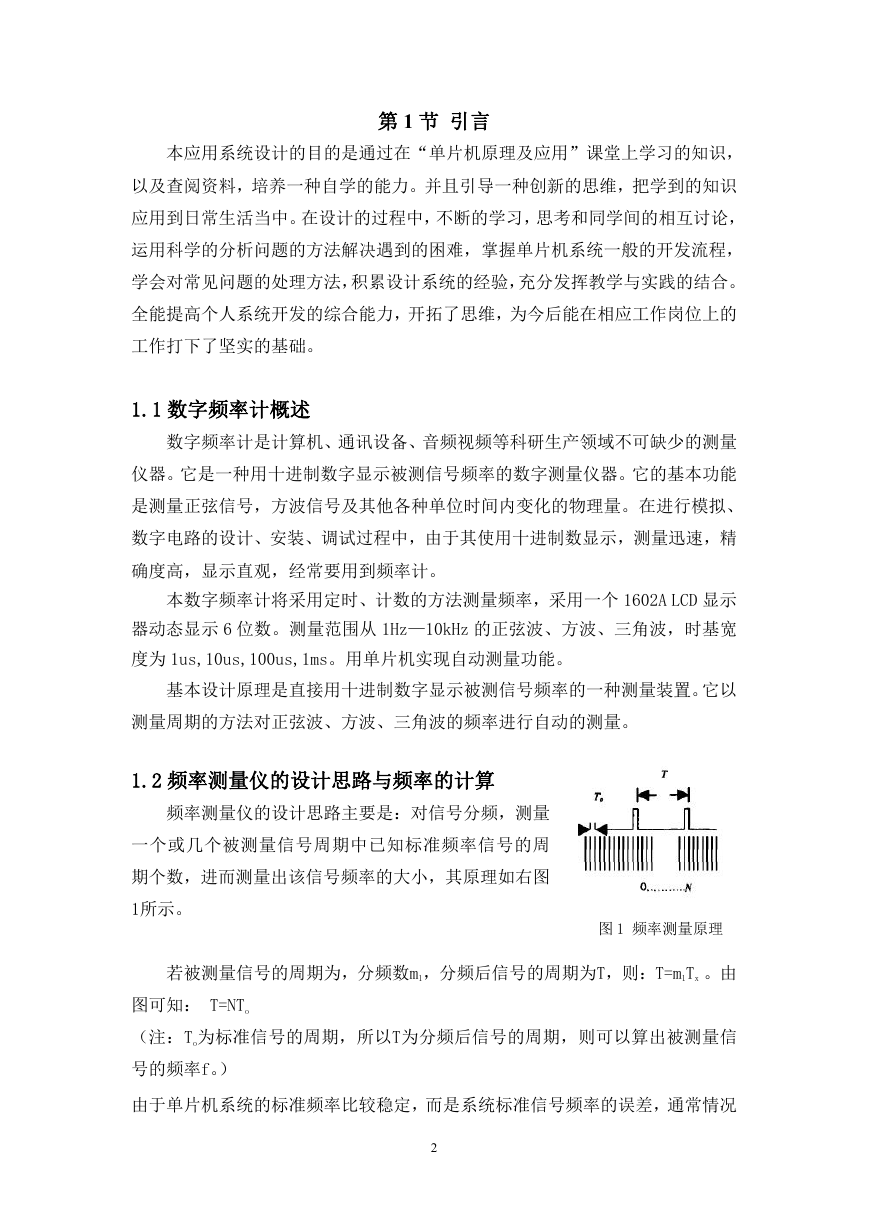

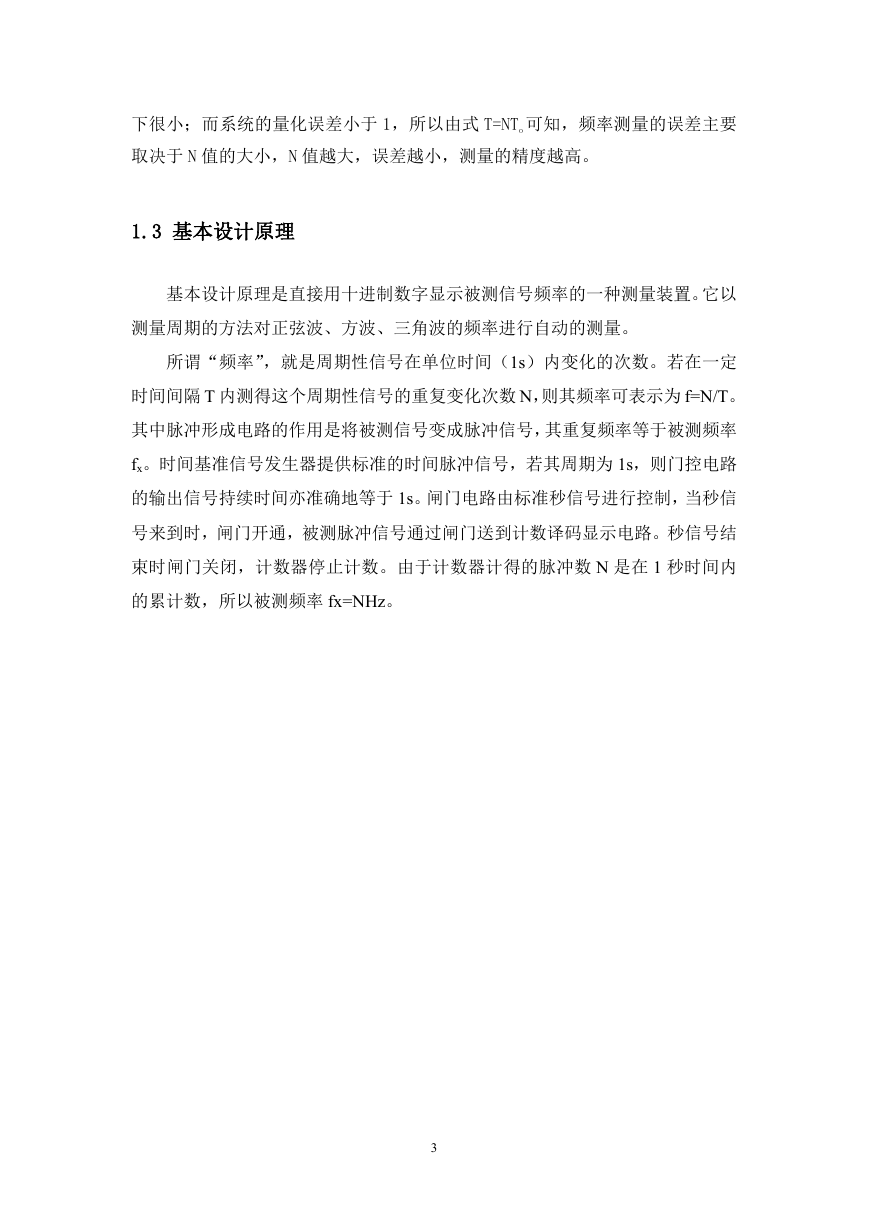

本频率计的数据采集系统主要元器件是单片机 AT89C51,由它完成对待测信

号频率的计数和结果显示等功能,外部还要有分频器、显示器等器件。可分为以

下几个模块:放大整形模块、秒脉冲产生模块、换档模拟转换模块、单片机系统、

LCD 显示模块。各模块关系图如图 2 所示:

显 示

单

片

机

倍 频 锁 相

放 大 整 形

被 测 信 号

时 基 电 路

图 2 数字频率计功能模块

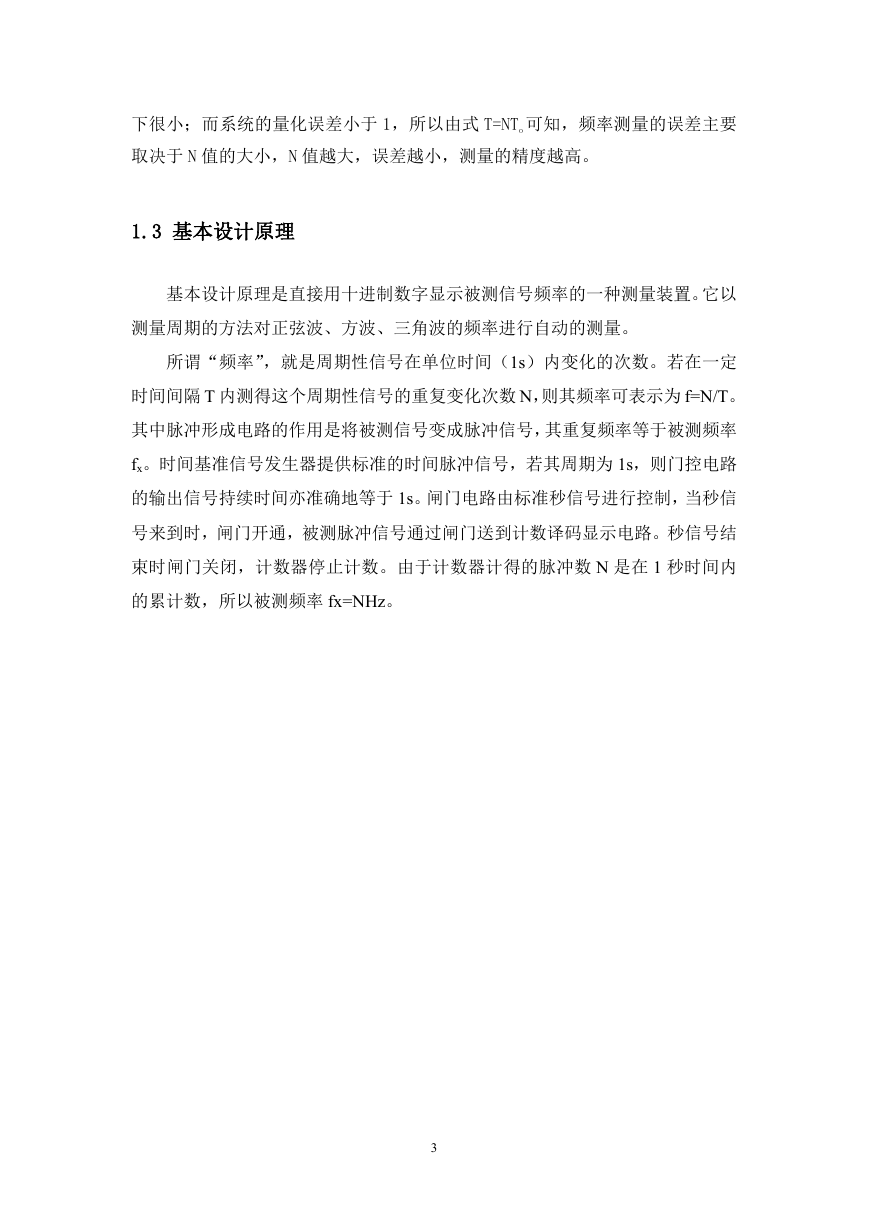

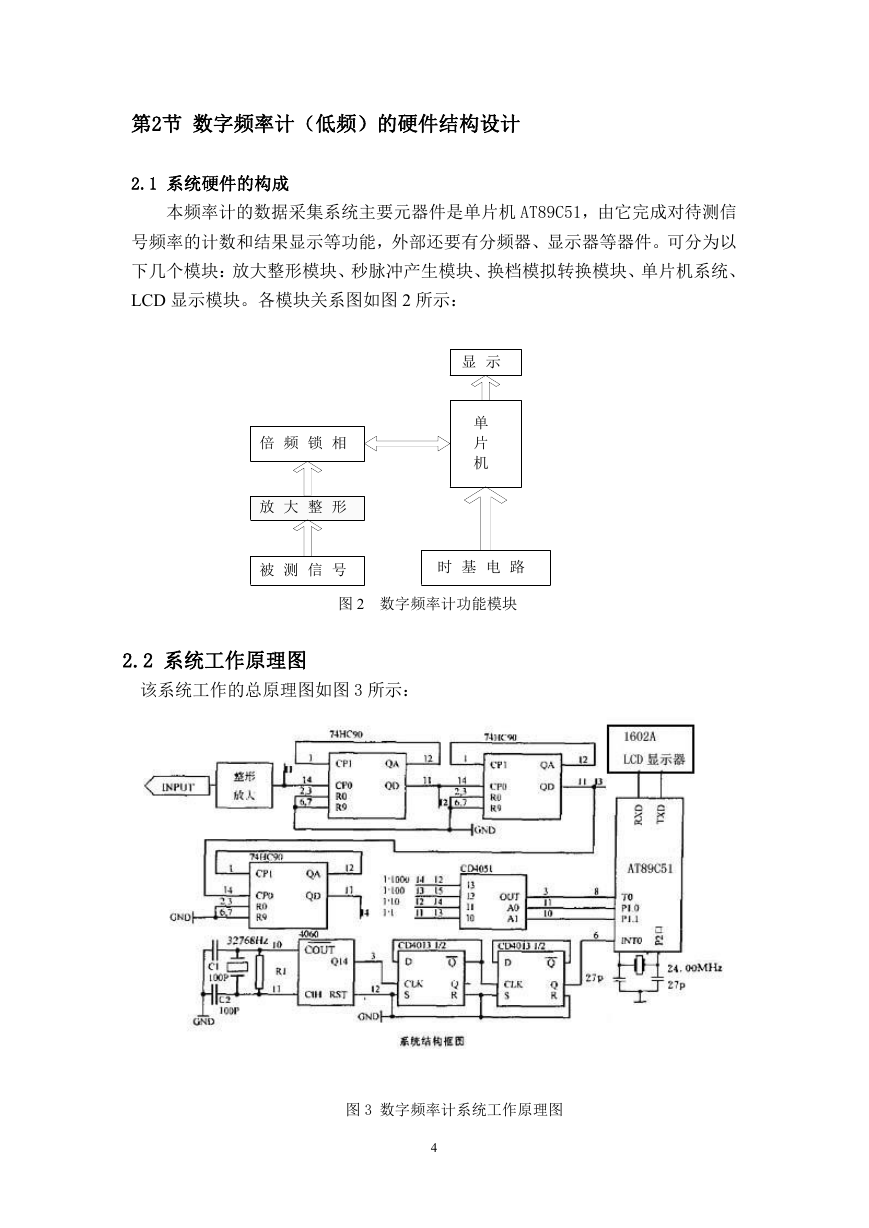

2.2 系统工作原理图

该系统工作的总原理图如图 3 所示:

图 3 数字频率计系统工作原理图

4

�

2.3 AT89C51 单片机及其引脚说明

89C51 是一种高性能低功耗的采用 CMOS 工艺制造的 8 位微控制器,它提

供下列标准特征:4K 字节的程序存储器,128 字节的 RAM,32 条 I/O 线,2 个

16 位定时器/计数器, 一个 5 中断源两个优先级的中断结构,一个双工的串行口,

片上震荡器和时钟电路。

引脚说明:

·VCC:电源电压

·GND:地

·P0 口:P0 口是一组 8 位漏极开路型双向 I/O 口,作为输出口用时,每个

引脚能驱动 8 个 TTL 逻辑门电路。当对 0 端口写入 1 时,可以作为高阻抗输入端

使用。

当 P0 口访问外部程序存储器或数据存储器时,它还可设定成地址数据总线

复用的形式。在这种模式下,P0 口具有内部上拉电阻。

在 EPROM 编程时,P0 口接收指令字节,同时输出指令字节在程序校验时。

程序校验时需要外接上拉电阻。

·P1 口:P1 口是一带有内部上拉电阻的 8 位双向 I/O 口。P1 口的输出缓冲

能接受或输出 4 个 TTL 逻辑门电路。当对 P1 口写 1 时,它们被内部的上拉电阻

拉升为高电平,此时可以作为输入端使用。当作为输入端使用时,P1 口因为内

部存在上拉电阻,所以当外部被拉低时会输出一个低电流(IIL)。

·P2 口:P2 是一带有内部上拉电阻的 8 位双向的 I/O 端口。P2 口的输出缓

冲能驱动 4 个 TTL 逻辑门电路。当向 P2 口写 1 时,通过内部上拉电阻把端口拉

到高电平,此时可以用作输入口。作为输入口,因为内部存在上拉电阻,某个引

脚被外部信号拉低时会输出电流(IIL)。

P2 口在访问外部程序存储器或 16 位地址的外部数据存储器(例如 MOVX @

DPTR)时,P2 口送出高 8 位地址数据。在这种情况下,P2 口使用强大的内部上

拉电阻功能当输出 1 时。当利用 8 位地址线访问外部数据存储器时(例 MOVX @

R1),P2 口输出特殊功能寄存器的内容。

当 EPROM 编程或校验时,P2 口同时接收高 8 位地址和一些控制信号。

·P3 口:P3 是一带有内部上拉电阻的 8 位双向的 I/O 端口。P3 口的输出缓

冲能驱动 4 个 TTL 逻辑门电路。当向 P3 口写 1 时,通过内部上拉电阻把端口拉

到高电平,此时可以用作输入口。作为输入口,因为内部存在上拉电阻,某个引

5

�

脚被外部信号拉低时会输出电流(IIL)。

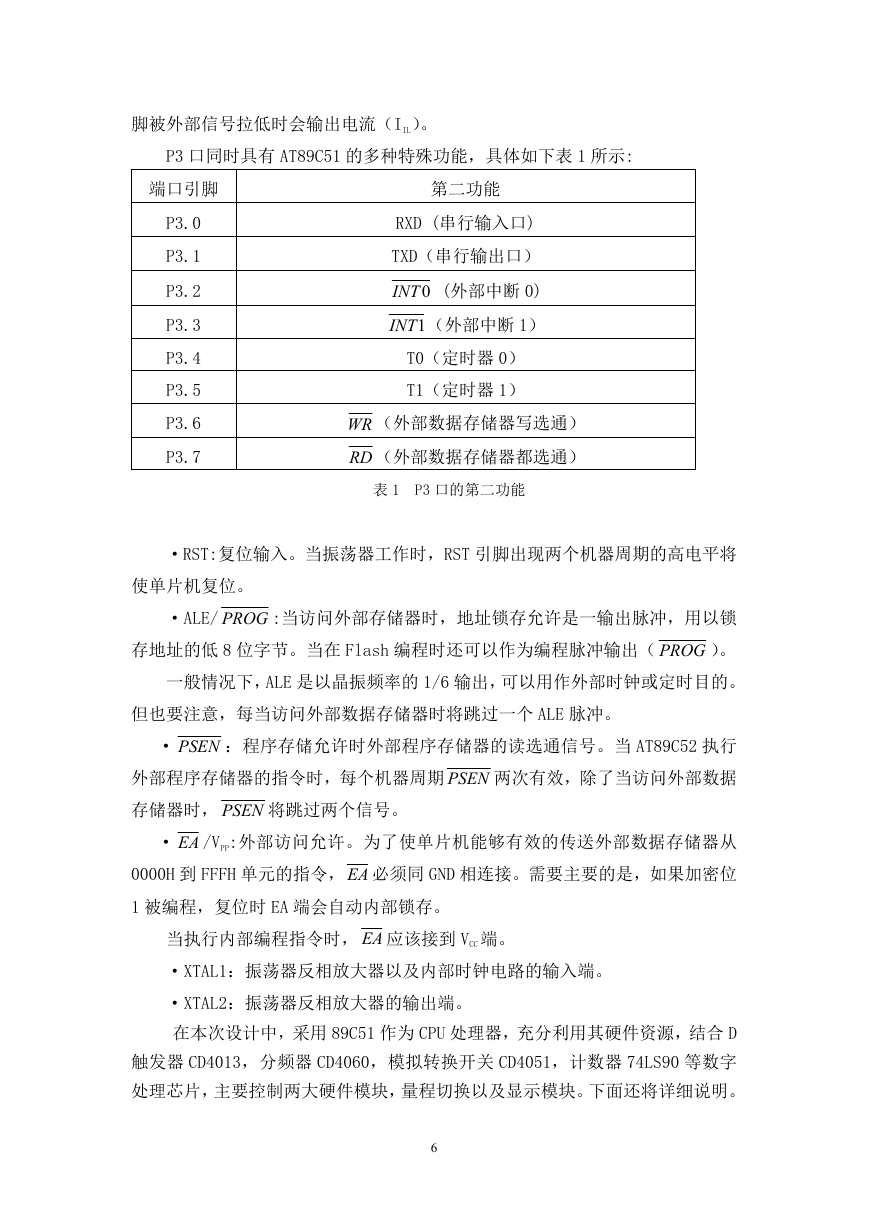

P3 口同时具有 AT89C51 的多种特殊功能,具体如下表 1 所示:

端口引脚

第二功能

P3.0

P3.1

P3.2

P3.3

P3.4

P3.5

P3.6

P3.7

RXD (串行输入口)

TXD(串行输出口)

(外部中断 0)

0

INT

1

INT (外部中断 1)

T0(定时器 0)

T1(定时器 1)

WR (外部数据存储器写选通)

RD (外部数据存储器都选通)

表 1

P3 口的第二功能

·RST:复位输入。当振荡器工作时,RST 引脚出现两个机器周期的高电平将

使单片机复位。

·ALE/ PROG :当访问外部存储器时,地址锁存允许是一输出脉冲,用以锁

存地址的低 8 位字节。当在 Flash 编程时还可以作为编程脉冲输出( PROG )。

一般情况下,ALE 是以晶振频率的 1/6 输出,可以用作外部时钟或定时目的。

但也要注意,每当访问外部数据存储器时将跳过一个 ALE 脉冲。

· PSEN :程序存储允许时外部程序存储器的读选通信号。当 AT89C52 执行

外部程序存储器的指令时,每个机器周期 PSEN 两次有效,除了当访问外部数据

存储器时, PSEN 将跳过两个信号。

· EA /VPP:外部访问允许。为了使单片机能够有效的传送外部数据存储器从

0000H 到 FFFH 单元的指令,EA 必须同 GND 相连接。需要主要的是,如果加密位

1 被编程,复位时 EA 端会自动内部锁存。

当执行内部编程指令时, EA 应该接到 VCC 端。

·XTAL1:振荡器反相放大器以及内部时钟电路的输入端。

·XTAL2:振荡器反相放大器的输出端。

在本次设计中,采用 89C51 作为 CPU 处理器,充分利用其硬件资源,结合 D

触发器 CD4013,分频器 CD4060,模拟转换开关 CD4051,计数器 74LS90 等数字

处理芯片,主要控制两大硬件模块,量程切换以及显示模块。下面还将详细说明。

6

�

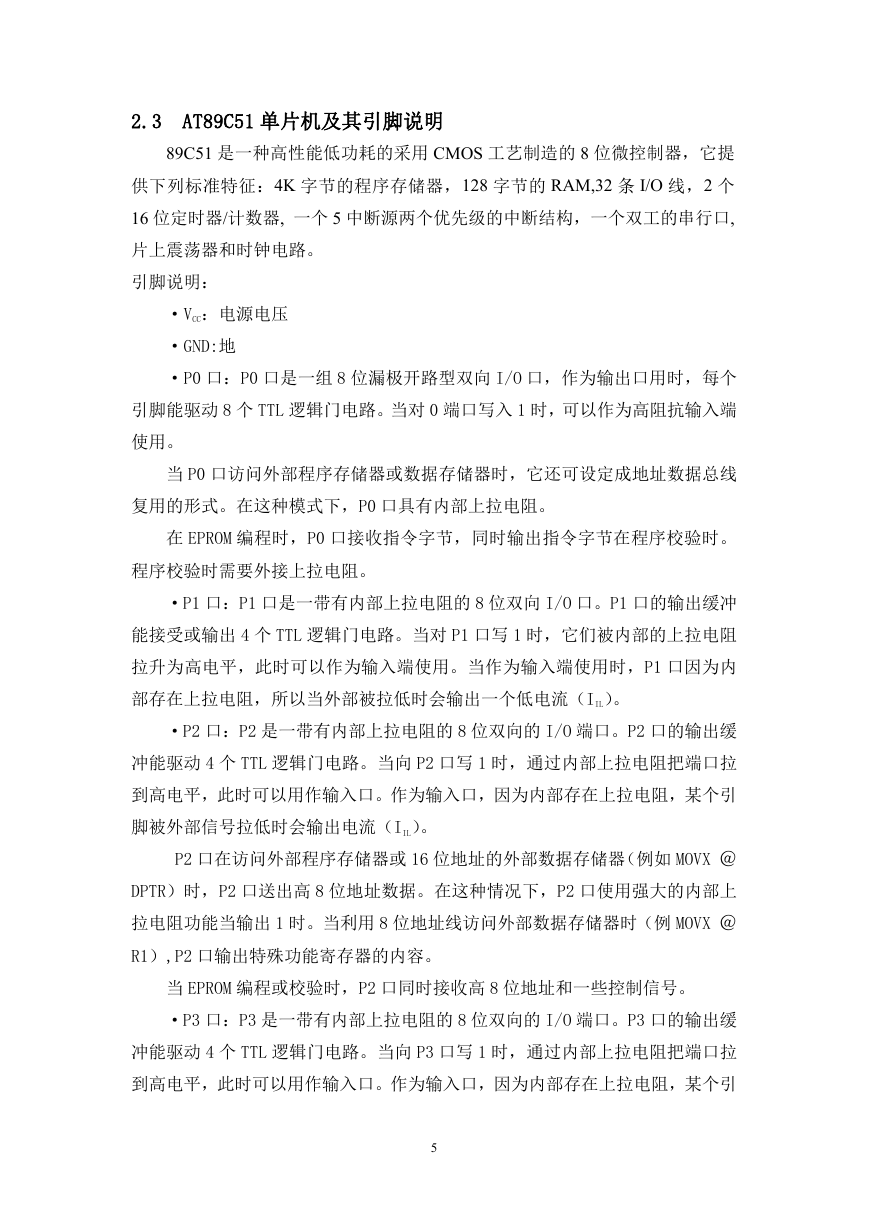

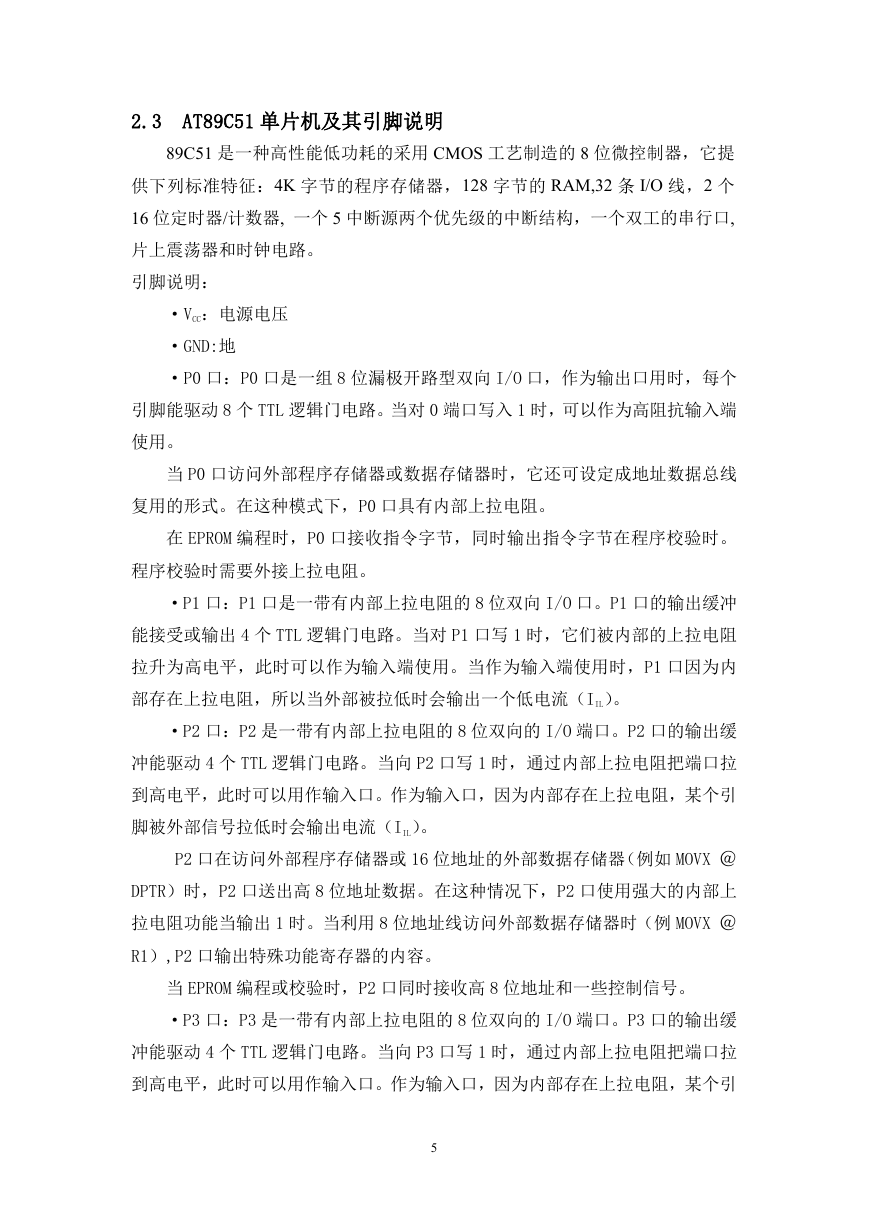

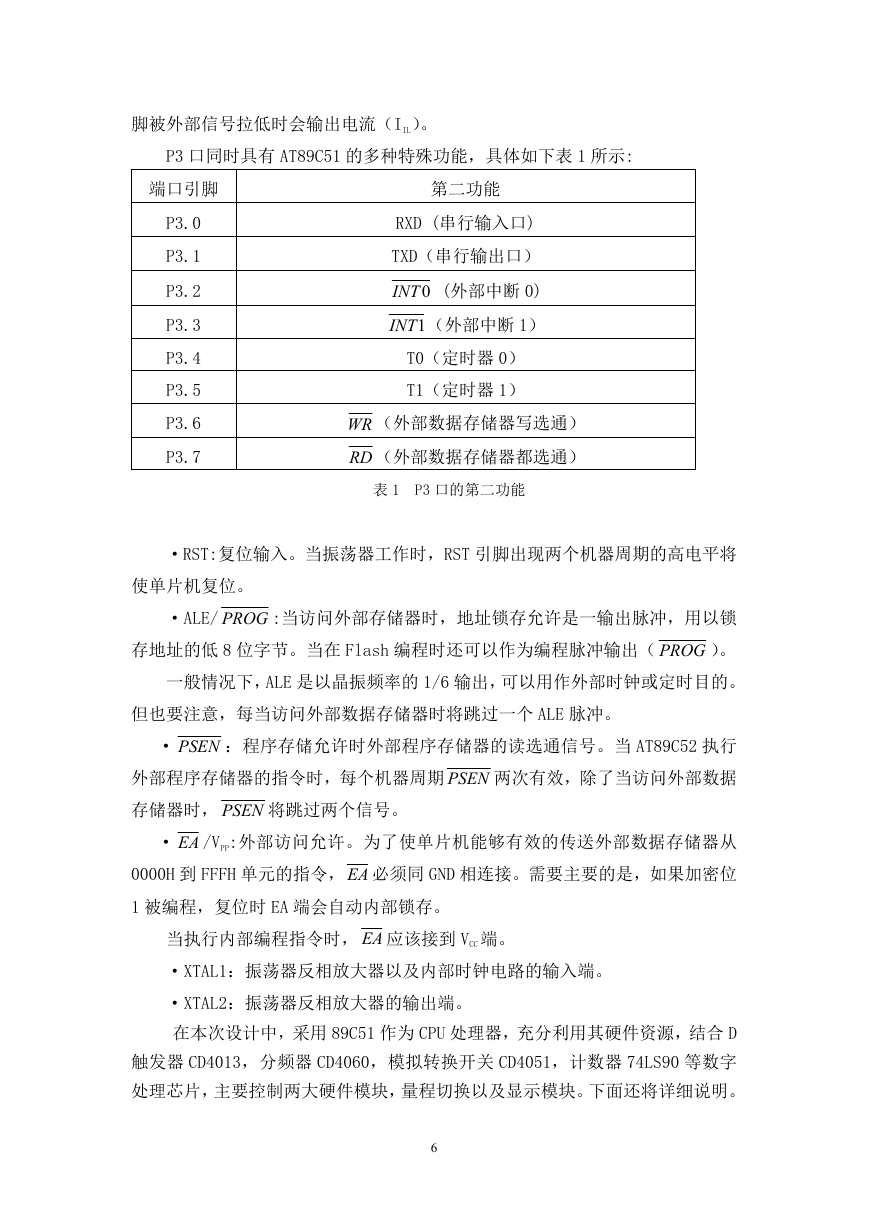

2.4 信号调理及放大整形模块

放大整形系统包括衰减器、跟随器、放大器、施密特触发器。它将正弦输入

信号 Vx 整形成同频率方波 Vo,幅值过大的被测信号经过分压器分压送入后级放

大器,以避免波形失真。由运算放大器构成的射级跟随器起阻抗变换作用,使输

入阻抗提高。同相输入的运算放大器的放大倍数为(R1+R2)/R1,改变 R1 的大

小可以改变放大倍数。系统的整形电路由施密特触发器组成,整形后的方波送到

闸门以便计数。

由于输入的信号幅度是不确定、可能很大也有可能很小,这样对于输入信

号的测量就不方便了,过大可能会把器件烧毁,过小可能器件检测不到,所以在

设计中采用了这个信号调理电路对输入的波形进行阻抗变换、放大限幅和整形,

信号调理部分电路具体实现电路原理图和参数如下图 4 所示:

C1

105

J1

2

1

CON2

U1A

1

LF353

VCC15V

8

4

-VCC15V

R4

RES1

3

2

R3

RES1

R2

RES1

GND

D1

DIODE

D2

DIODE

D3

DIODE

D5

ZENER1

D4

DIODE

R1

RES1

GND

6

5

U1B

LF353

7

图 4

VCC15V

5V

R6

RES1

R5

RES1

2

3

GND

8

6 5

U3

7

LM311

4

1

GND

-VCC15V

2

12

1

13

3

11

4

10

IC1

D1

D2

CLR1

CLR2

CLK1

CLK2

SET1

SET2

74LS14

+5V

Q1

Q2

Q1

Q2

GND

14

VCC

6

8

5

9

7

GND

J2

1

2

CON2

GND

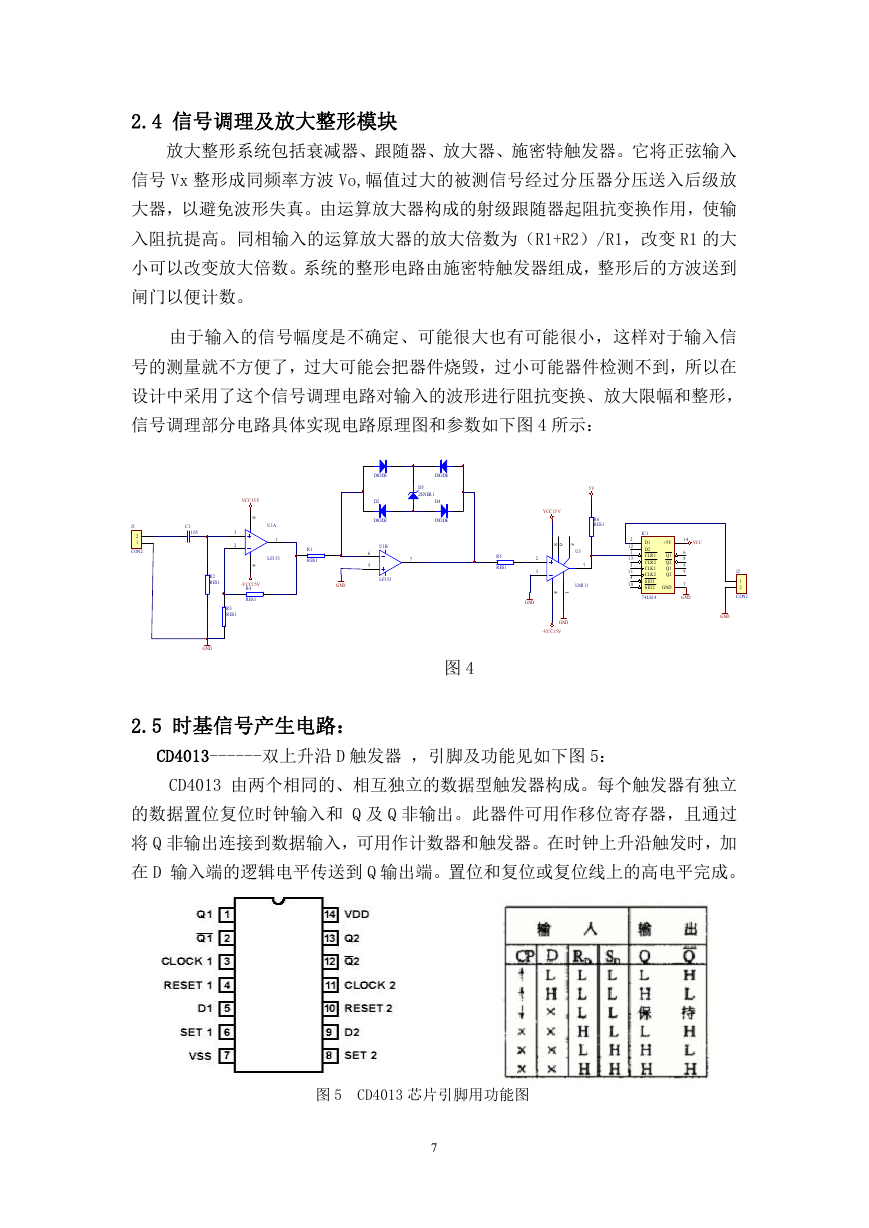

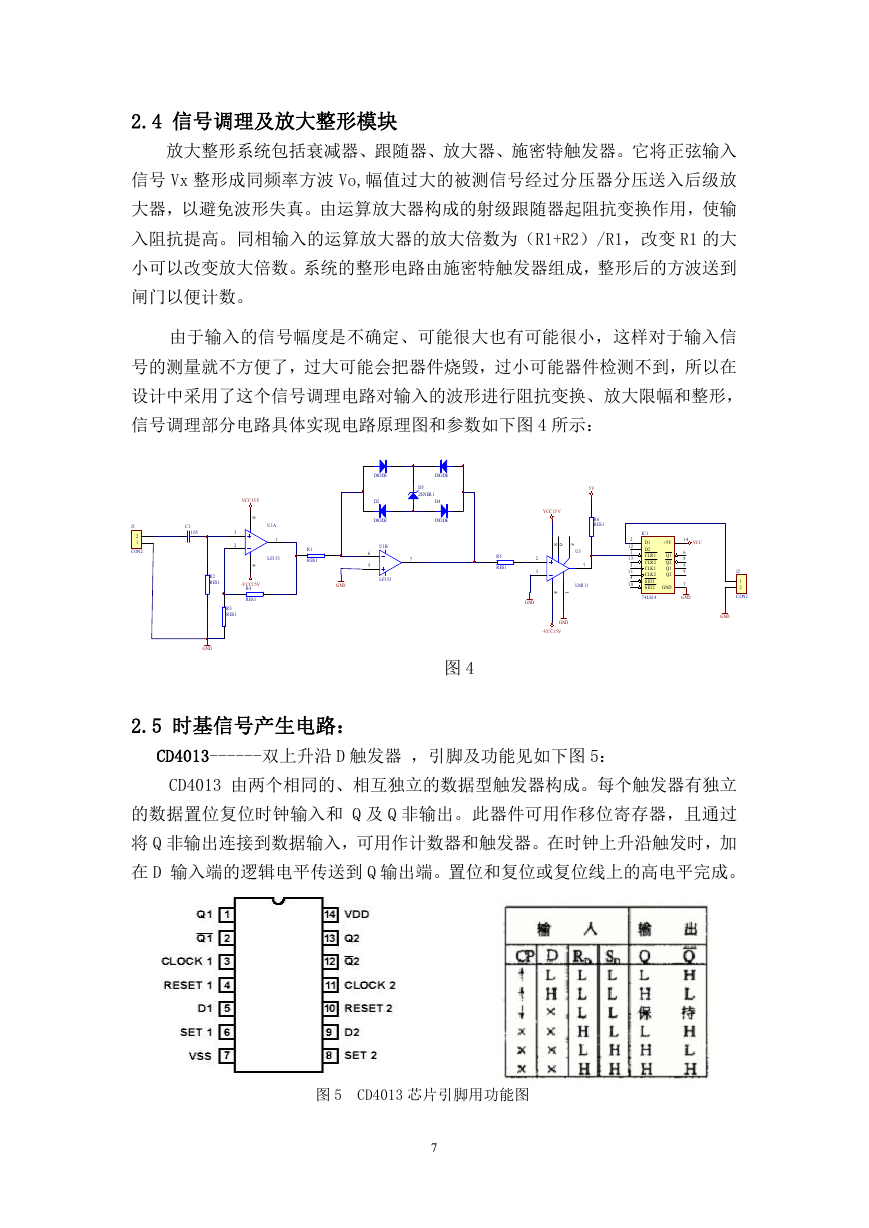

2.5 时基信号产生电路:

CD4013------双上升沿 D 触发器 ,引脚及功能见如下图 5:

CD4013 由两个相同的、相互独立的数据型触发器构成。每个触发器有独立

的数据置位复位时钟输入和 Q 及 Q 非输出。此器件可用作移位寄存器,且通过

将 Q 非输出连接到数据输入,可用作计数器和触发器。在时钟上升沿触发时,加

在 D 输入端的逻辑电平传送到 Q 输出端。置位和复位或复位线上的高电平完成。

图 5

CD4013 芯片引脚用功能图

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc