第1章 关于本文档

1.1 概述

1.1.1 目的

1.1.2 适用读者

1.2 约定

1.2.1 数字系统

1.2.2 印刷记号

1.2.3 特殊术语

表4-3 PPB内存映射

图5-1时钟框图

第2章 引言

2.1 概述

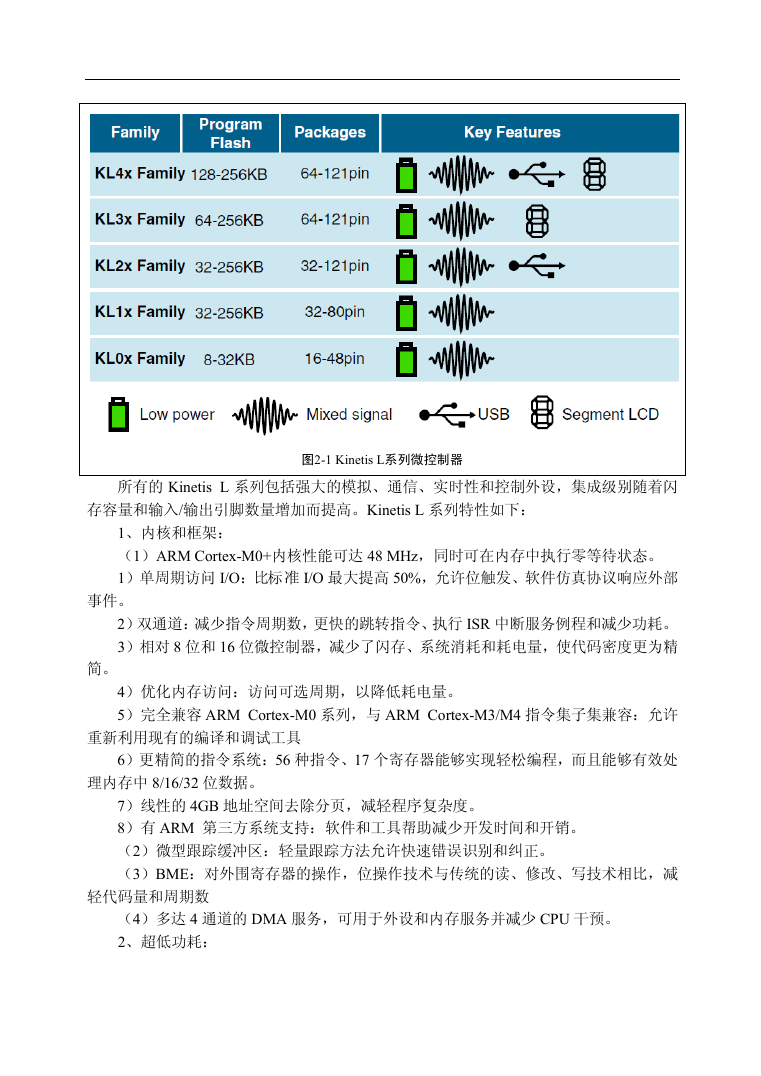

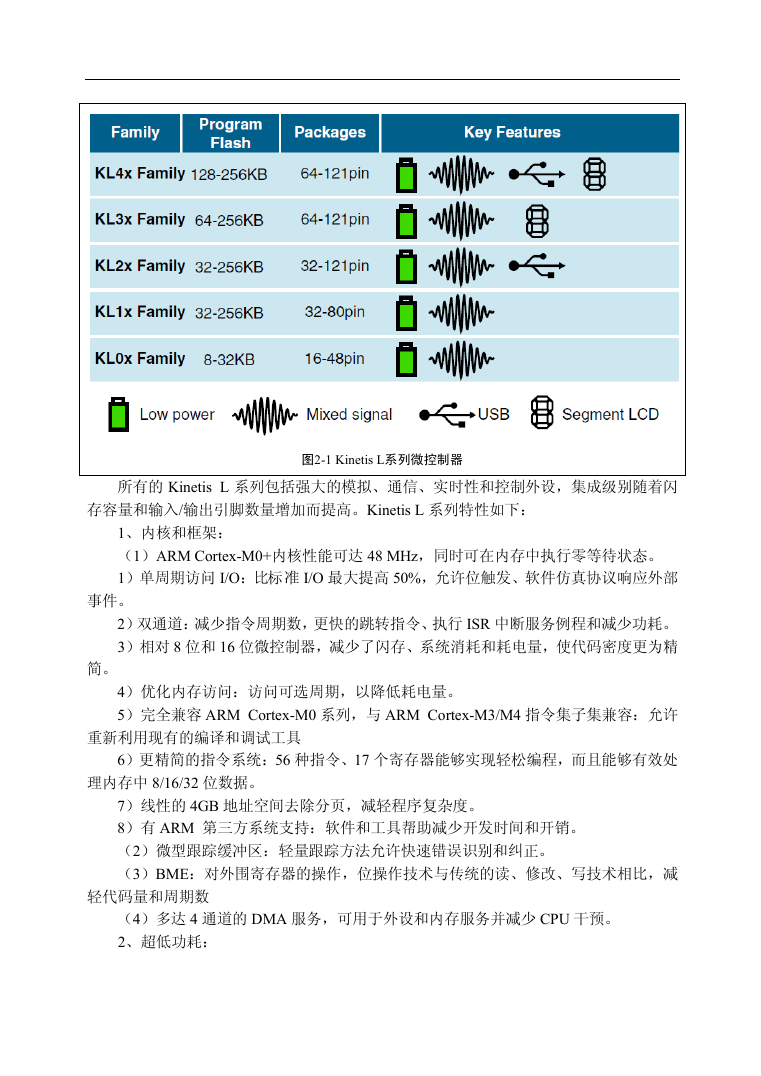

2.2 Kinetis L系列

2.3 KL25 子系列简介

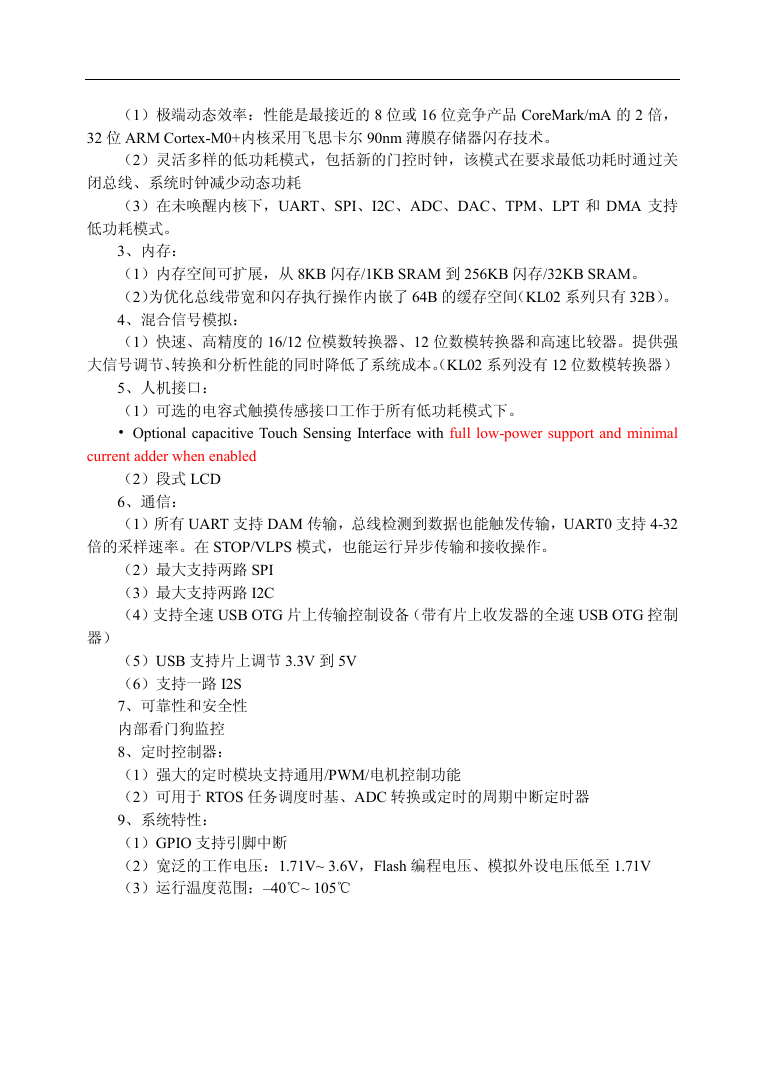

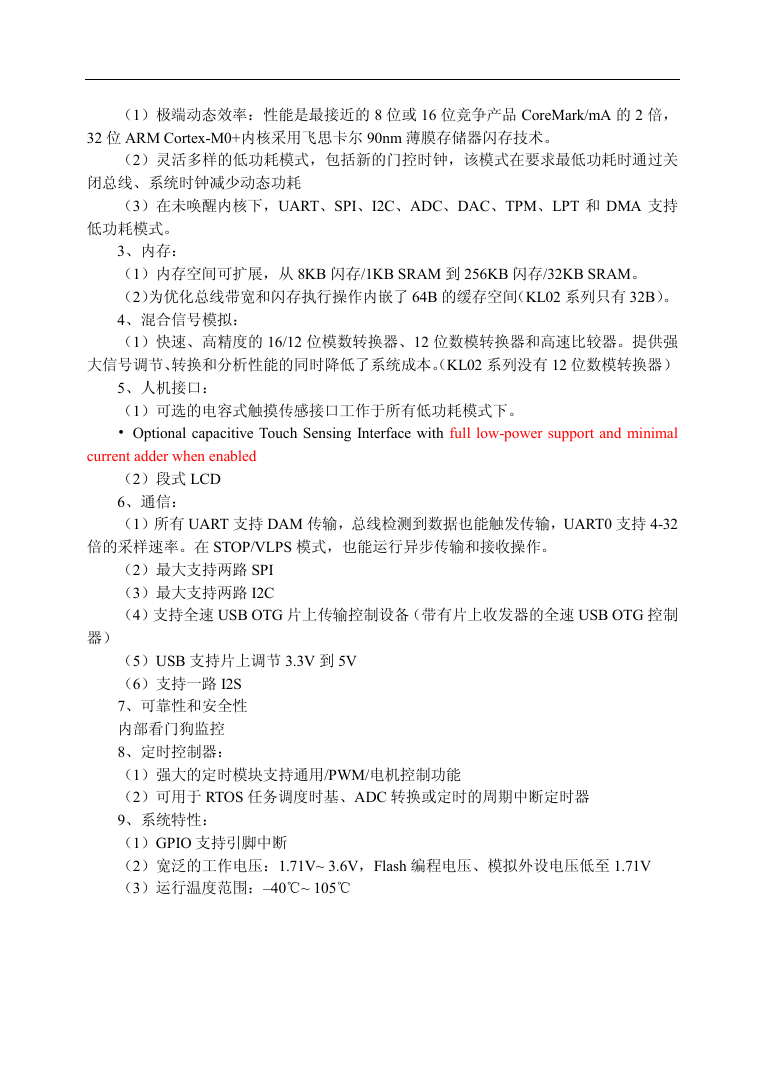

2.4 模块功能分类

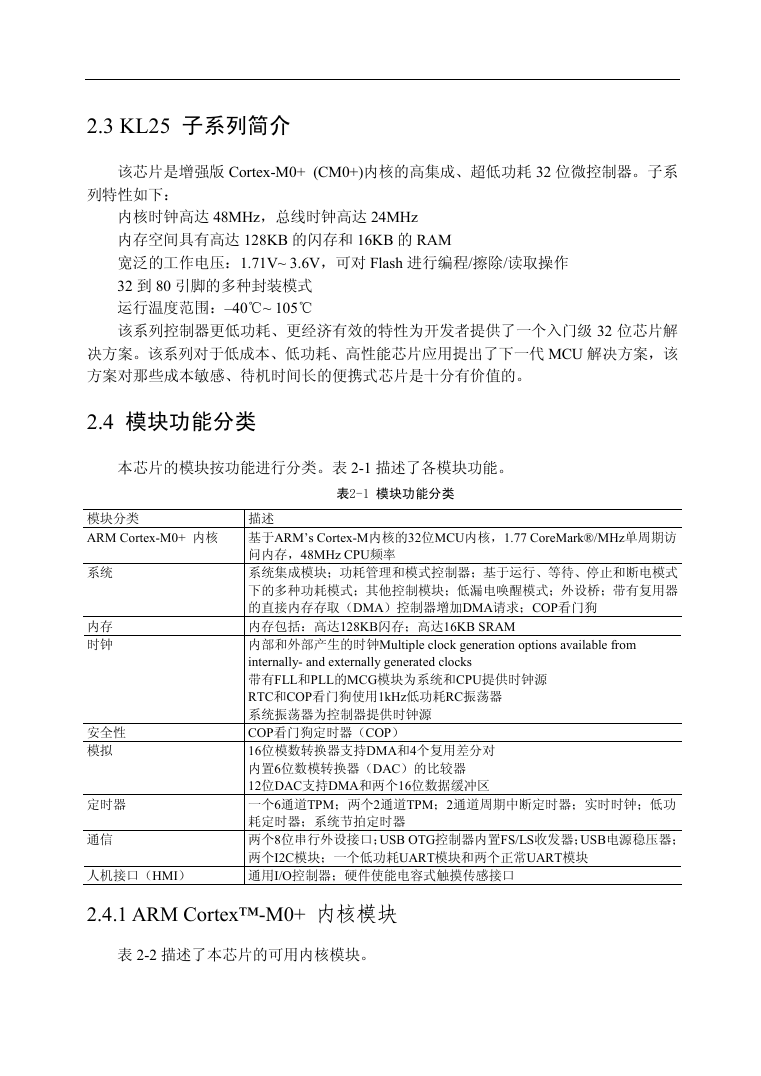

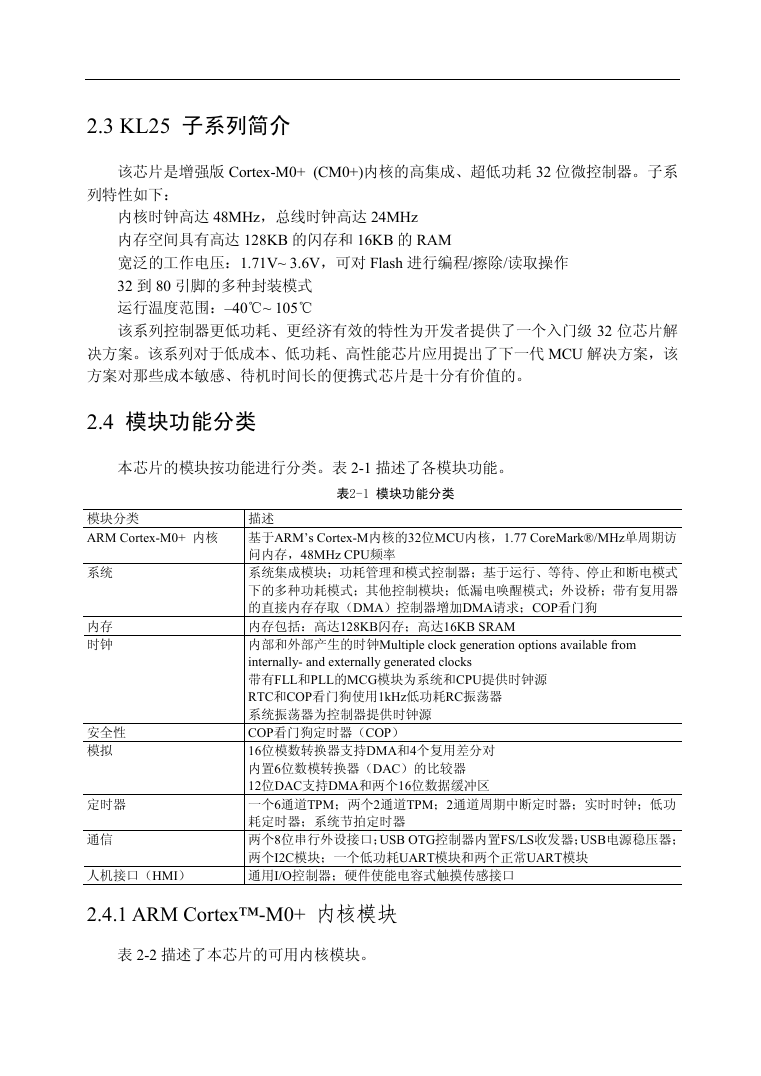

2.4.1 ARM Cortex™-M0+ 内核模块

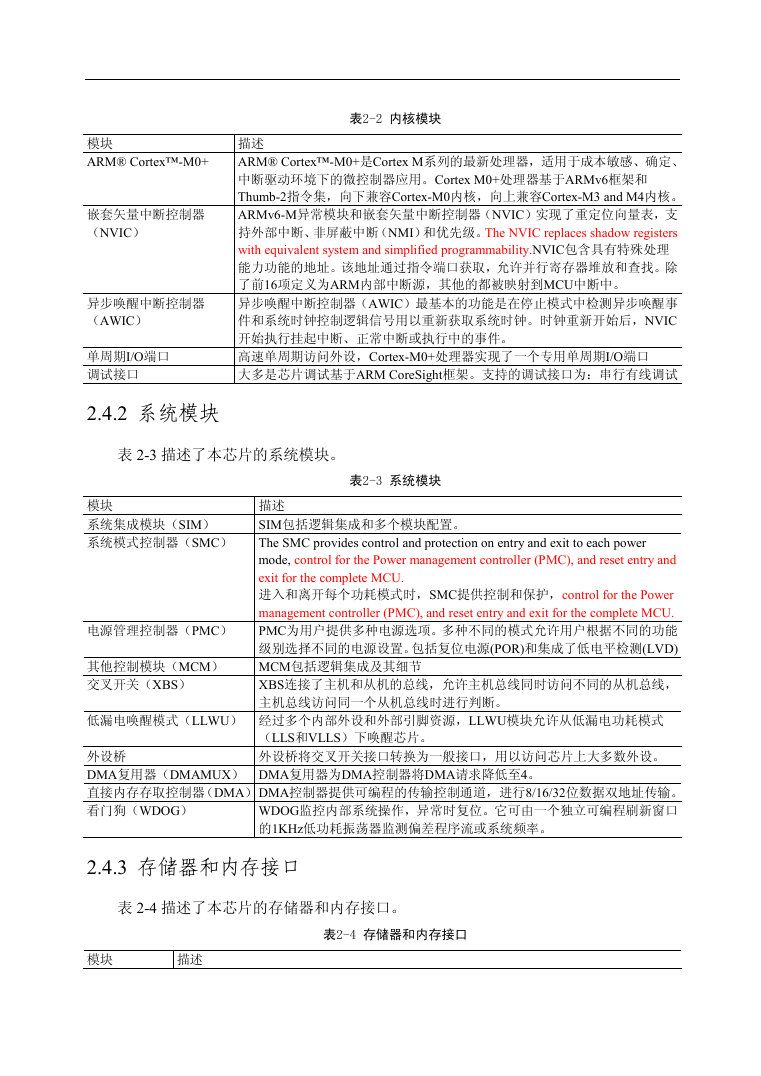

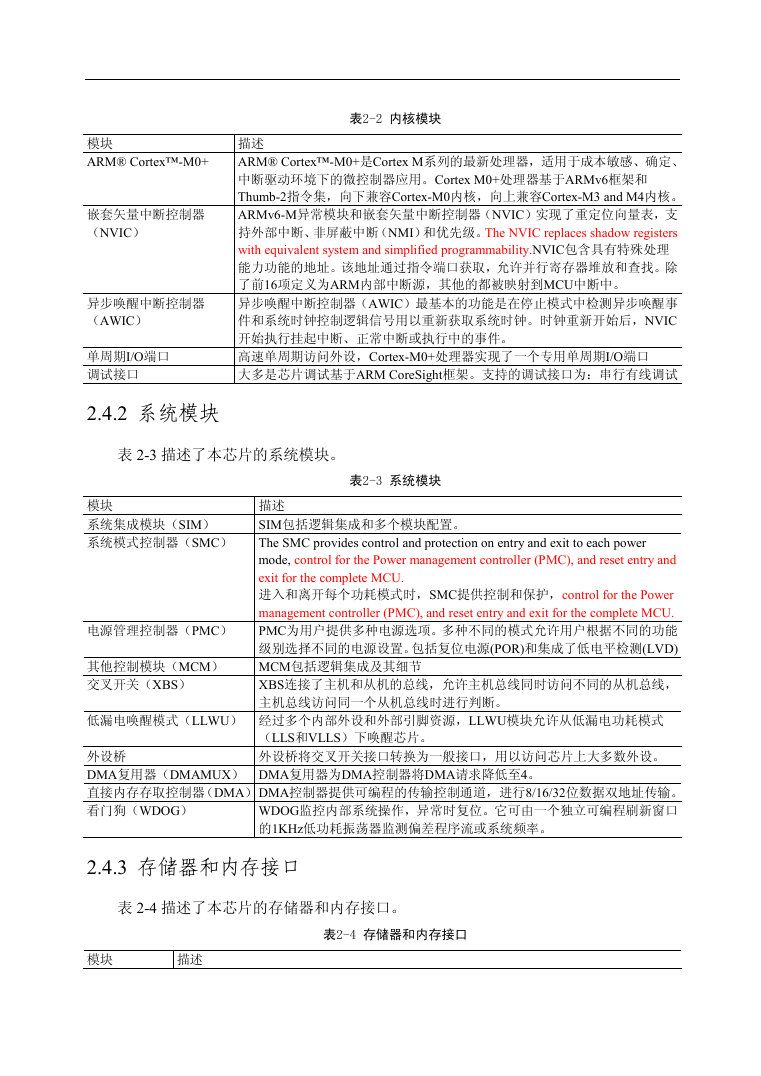

2.4.2 系统模块

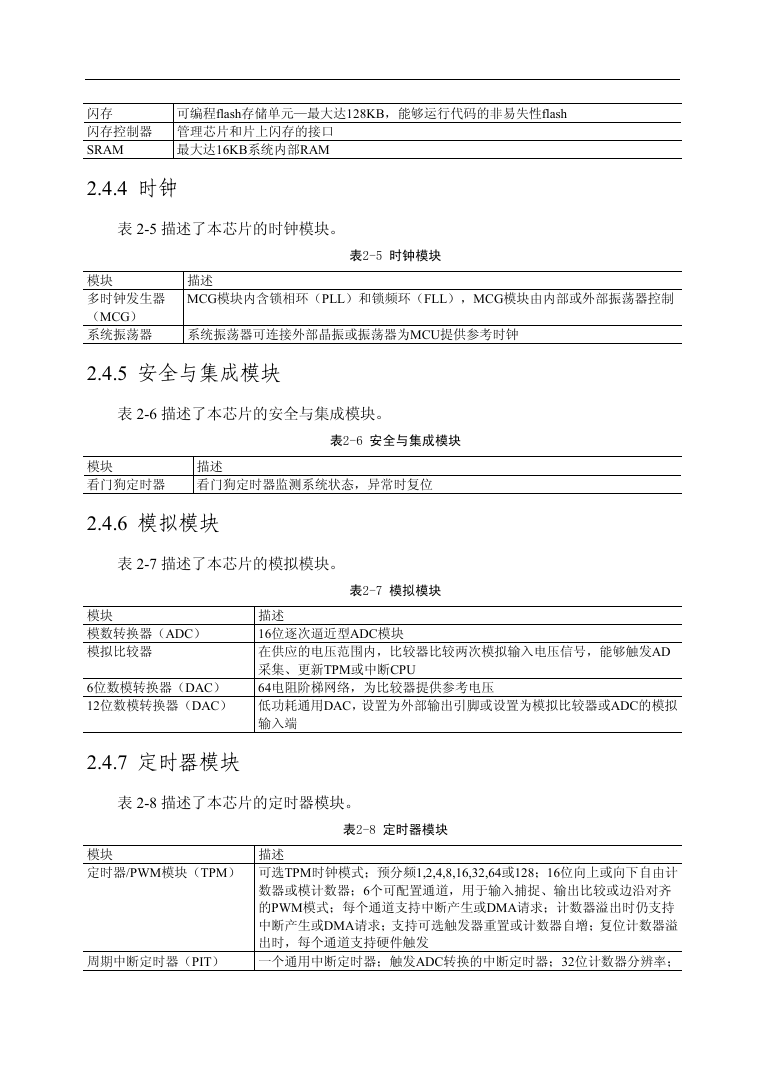

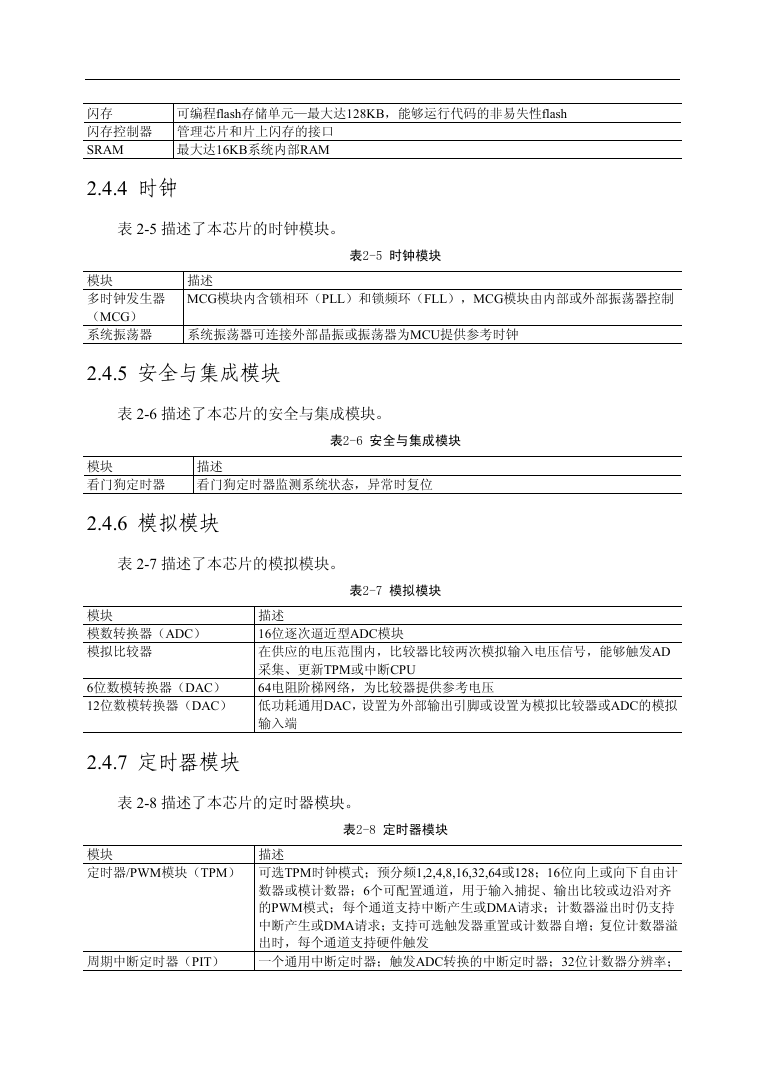

2.4.3 存储器和内存接口

2.4.4 时钟

2.4.5 安全与集成模块

2.4.6 模拟模块

2.4.7 定时器模块

2.4.8 通信接口

2.4.9 人机接口

2.5 型号标识

图2-1 Kinetis L系列微控制器

表2-1 模块功能分类

表2-2 内核模块

表2-3 系统模块

表2-4 存储器和内存接口

表2-5 时钟模块

表2-6 安全与集成模块

表2-7 模拟模块

表2-8 定时器模块

表2-9 通信模块

表2-10 HMI模块

表2-11 型号标识总结

第3章 芯片配置

3.1 引言

3.2 模块到模块的交互

3.2.1 模块之间的相互关系

3.2.2 模拟参考选项

3.3 内核模块

3.3.1 ARM Cortex-M0+内核结构

3.3.1.1 ARM Cortex M0+ 内核

3.3.1.2 总线、内部连接线和接口

3.3.1.3 系统时钟

3.3.1.4 调试工具

3.3.1.5内核权限级别

3.3.2 嵌套中断向量控制器结构

3.3.2.2不可屏蔽中断

3.3.2.3 中断通道评估表

3.3.2.3.1配置一个特别的中断确定位域和寄存器位置

3.3.3 异步唤醒中断控制器(AWIC)结构

3.3.3.1 唤醒源

3.4 系统模块

3.4.1 SIM结构

3.4.2 系统模式控制器结构

3.4.2.1 VLLS2不支持

3.4.3 PMC结构

3.4.4 低功耗唤醒单元(LLWU)结构

3.4.4.1 LLWU中断

3.4.4.2 唤醒源

3.4.5 MCM结构

3.4.6 闩开关结构

3.4.6.1 闩开关主机配置表

3.4.6.2 闩开关从机表

3.4.7 外设桥结构

3.4.7.1 外设桥数量

3.4.7.2 存储映射

3.4.8 多DMA请求结构

3.4.8.1 DMA MUX请求源

3.4.8.2 PIT触发DMA

3.4.9 DMA控制器结构

3.4.10 看门狗结构

3.4.10.1 COP时钟

3.4.10.2 COP看门狗操作

3.4.10.3 时钟门

3.5 时钟模块

3.5.1 MCG结构

3.5.1.1 MCG FLL 模式

3.5.2 OSC结构

3.5.2.1 MCG和RTC中的OSC的操作模式

3.6 存储和存储接口

3.6.1 Flash存储器结构

3.6.1.1 Flash存储器的大小

3.6.1.3 Flash安全性

3.6.1.4 Flash 模式

3.6.1.5 擦除所有的flash内容

3.6.1.6 FTFA_FOPT寄存器

3.6.2 Flash存储器的控制器结构

3.6.3 SRAM结构

3.6.3.1 SRAM大小

3.6.3.2 SRAM范围

3.6.3.3 低功耗模式下SRAM记忆

3.7 模拟

3.7.1 16位的SAR ADC结构

3.7.1.1 ADC实例化信息

3.7.1.2 ADC上的DMA支持

3.7.1.3 ADC0连接/通道分配

3.7.1.3.1 ADC0通道分配

3.7.1.4 ADC 模拟提供和参考连接

3.7.1.5 ADC 参考选项

3.7.2 CMP (比较器)结构

3.7.2.1 CMP 实例化信息

3.7.2.2 CMP输入连接

3.7.2.3 CMP 外部参考

3.7.2.4 CMP 触发模式

3.7.3 12位DAC结构

3.7.3.1 12位DAC实例化信息

3.7.3.2 12位DAC输出

3.7.3.3 12位DAC模拟提供和参考连接

3.7.3.4 12位DAC参考

3.8 定时器

3.8.1 定时器/PWM模块结构

3.8.1.1 TPM实例化信息

3.8.1.2 时钟选项

3.8.1.3 触发选项

3.8.1.4 全局时基

3.8.1.5 TPM中断

3.8.2 PIT结构

3.8.2.1 PIT/DMA周期触发列表

3.8.2.2 PIT/ADC触发

3.8.2.3 PIT/TPM触发

3.8.2.4 PIT/DAC触发

3.8.3 低功耗定时器结构

3.8.3.1 LPTMR实例化信息

3.8.3.2 LPTMR 脉冲计数输入选项

3.8.3.3 LPTMR预分频器/滤波器时钟选项

3.8.4 RTC结构

3.8.4.1 RTC 实例化信息

3.8.4.2 RTC_CLKOUT选项

3.9 通信接口

3.9.1 通用串行总线(USB)子系统

3.9.1.1 USB唤醒

3.9.1.2 USB电源分配

3.9.1.2.1 AA/AAA电池电源支持

3.9.1.2.2 Li-lon电池电源支持

3.9.1.2.3 USB总线电源支持

3.9.1.3 USB电源管理

3.9.1.4 USB控制结构

3.9.1.5 USB电压调节器结构

3.9.2 SPI结构

3.9.2.1 SPI实例化信息

3.9.3 I2C结构

3.9.3.1 I2C实例化信息

3.9.4 串口结构

3.9.4.1 UART0 概述

3.9.4.2 UART1 和 UART2 概述

3.10 人机交互接口(HMI)

3.10.1 GPIO结构

3.10.1.1 GPIO实例化

3.10.1.1.1 牵引芯片和方向

3.10.1.1.2 转换率

3.10.1.2 GPIO 在存储映像的可访问性

3.10.2 TSI结构

3.10.2.1 TSI实例化

3.10.2.2 TSI中断

表3-1 模块间关系参考表

表3-5 ARM Cortex M0+的两种权限级别

第4章 存储映射

4.1概要

4.2系统存储映射

4.3 Flash 存储映射

4.3.1 可选的非易失性的IRC(内部参考时钟) 用户裁剪

4.4 SRAM存储映射

4.5 位处理引擎(BME)

4.6 外设桥(AIPS-Lite)存储映射

4.6.2 外设桥0(AIPS-Lite0)存储映射

4.6.3 用户模式下模块访问限制

4.7 私有外设总线(PPB)存储映射

表4-1 系统存储映射

图4-1 flash存储映射

第5章 时钟分配

5.1概要

5.2 编程模型

5.3 高等级设备时钟框图

5.4 时钟定义

5.4.1 设备时钟概述

5.5 内部时钟要求

5.5.1 复位后的时钟分频值

5.5.2 VLPR模式时钟

5.6 时钟门

5.7 模块时钟

5.7.1 PMC 1-KHz LPO时钟

5.7.2 COP时钟(看门狗)

5.7.3 RTC 时钟

5.7.4 LPTMR时钟

5.7.5 TPM时钟

5.7.6 USB FS OTG控制时钟

5.7.7 UART时钟

表5-1 时钟综述

表5-2 模块时钟

图5-2 COP时钟发生器

图5-3 RTC时钟发生器

图5-4 LPTMRx 预分频/滤波时钟发生器

图5.6 USB 48MHz时钟源

图5.7 UART0时钟发生器

第6章 复位和启动

6.1 简介

6.2 复位

6.2.1 上电复位(POR)

6.2.2 系统复位源

6.2.2.1 外部引脚复位( )

6.2.2.1.1复位引脚过滤

6.2.2.2 低电平检测(LVD)

6.2.2.3 COP看门狗复位

6.2.2.4 低漏唤醒(LLWU)复位

6.2.2.5 多功能时钟发生器时钟丢失(LOC)复位

6.2.2.6 MCG –丢失锁定LOL复位

6.2.2.7 停止模式的应答错误(SACKERR)

6.2.2.8 软件复位(SW)

6.2.2.9 锁定复位(LOCKUP)

6.2.2.10 MDM-AP系统复位请求

6.2.3 MCU复位

6.2.3.1 POR上电复位

6.2.3.2 芯片非VLLS上电复位

6.2.3.3 芯片上电复位

6.2.3.4 芯片非VLLS复位

6.2.3.5 早期芯片复位

6.2.3.6 芯片复位

6.2.5 调试复位

6.2.5.1 复位调试子系统

6.3启动

6.3.1 启动源

6.3.2 FOPT启动选项

6.3.3 启动顺序

表6-1 复位源

表6-2. Flash选项寄存器(FTFL_FOPT)位定义

第7章 电源管理模块

7.1 简介

7.2 时钟模块

7.2.1 局部停止

7.2.2 DMA唤醒

7.2.3 计算操作

7.2.4 外设休眠

7.2.5 时钟门

7.3 电源模块

7.4 进入及退出电源模式

7.5 低功耗下的模块操作

表7-1 芯片电源模式

表7-2 低功耗下的模块操作

第8章 安全性

8.1 介绍

8.2 Flash 安全性

8.3其他模块的安全性交互

8.3.1安全性和调试的交互

第9章 调试

9.1 介绍

9.2 调试端口引脚

9.3 SWD状态和控制寄存器

9.3.1 MDM-AP控制寄存器

9.3.2 MDM-AP 状态寄存器

9.4 调试复位

9.5 微型追踪缓冲区(MTB)

9.6 在低功耗模式下的调试

9.7 调试&安全

表9-1 SWD引脚描述

表9-2 MDM-AP寄存器概要

图9-1MDM-AP地址

表 9-3. MDM-AP 控制寄存器分配

表9-6 MDM-AP状态寄存器

图10-1信号复用集成

图10-2 KL25 80LQFP引脚图

图10-3 KL25 64LQFP引脚图

图10-4 KL25 48-pin QFN引脚图

图10-5 KL25 32-pin QFN引脚图

图13-1 电源模式状态框图

图13-2 低功耗系统部分和联系

图15-1 LLWU块表

图13-1 电源模式状态框图

图13-2 低功耗系统部分和联系

图15-1 LLWU块表

图17-1 通用Cortex-M0+内核平台结构图

图17-2 封装式存储:数据位插入操作时序图

图17-3 封装式存储地址:逻辑AND

图17-4 封装式存储地址:逻辑OR

图17-5 封装式存储地址:逻辑XOR

图17-6 封装式地址存储:数据位插入操作

图17-7 封装式载入:置位和清除操作时序图

图17-8 封装式载入:无符号位提取时序图

图17-10 封装式载入地址:载入-置位操作

图17-11 封装式载入地址:无符号数提取操作

图19-1 Cotex-M0+内核平台结构图

图19-2 MTB执行跟踪存储格式

图19-56 CoreSight组件寻找流程

图22-1 DMAMUX模块框图

图22-2 DMAMUX触发通道

图22-4 DMAMUX通道触发(忽视触发)

图23-1 通道的DMA框图

图23-2 双向地址传输

图24-1 多用途时钟生成器(MCG)框图

图24-2 MCG模式状态图

图24-3 使用4MHz晶振从FEI到PEE模式转换流程图

图24-4 使用4MHz晶振PEE到BLPI模式转换流程图

图 24-5 使用一个4MHz晶振从BLPI到FEE模式转换的流程图

图25-1 OSC模块框图

图25-2 晶振/陶瓷谐振器连接——连接1

图25-3 晶振/陶瓷谐振器连接——连接2

图25-4 晶振/陶瓷谐振器连接——连接3

图25-5 晶振/陶瓷谐振器连接——连接4

图25-6 外部时钟连接

图25-7 OSC模块状态图

图 27-1 FTFL框图

图27-2 程序Flash保护

图27-3 FTFL命令写次序框图

图27-4 擦除flash段操作的挂起及恢复

图28-1 ADC模块结构图

图28-2 初始化流程图

图29-1 比较器,数模转换,模拟复用器的结构图

图29-15 持续模式下的比较器操作

图29-16 采样无滤波模式(#3A):外部驱动采样点

图29-17 采样无滤波模式(#3B):内部驱动采样点

图29-18 采样滤波模式(#4A):外部采样点输入

图29-19 采样滤波模式(#4B):内部采样点输入

图29-20 运行下的窗口模式

图29-21 窗口模式

图29-22 运行下的窗口/重复采样模式

图29-23 窗口/滤波模式

图29-24 6位DAC模块结构图

图30-1 DAC结构图

图31-2 预分频计数器的示例

图31-3 TPM的上升计数示例

图31-4TPM的可逆计数示例

图31-5 输入捕获模式

图31-6 输出比较模式匹配当匹配通道输出切换时的例子

图31-7 输出比较模式当匹配清零通道输出时的例子

图31-8 输出比较模式当匹配置位通道输出

图31-9 EPWM周期和脉冲宽度与ELSnB:ELSnA = 1:0

图31-10 当ELSnB:ELSnA = 1:0时的EPWM信号

图31-11 EPWM信号当ELSnB:ELSnA = X:1时

图31-12 CPWM周期和脉冲宽度当ELSnB:ELSnA = 1:0时

图31-13 CPWM信号当ELSnB :ELSnA = 1:0时

图31-14 CPWM信号当ELSnB:ELSnA = X:1时

图32-1 PIT框图

图32-2 停止和启动定时器

图32-3 修改运行的定时器周期

图32-4 动态设置新载入值

图35-1 USB2.0系统

图35-2 USB OTG系统

图 35-3 缓冲区描述表

图35-4 USB令牌传输

图35-91 A设备双重角色流程图

图 35-92 B设备双重角色流程图

图 36-1 调节器处于与输入电压之间的理想关系图

图36-2 USB电压调节器框图

图37-1 SPI系统连接

图37-2 没有FIFO的SPI模块结构图

图37-3 通过DMA SPI传输的基本流程

图37-4 推荐启动DMA SPI传输

图37-5 SPI时钟格式(CPHA = 1)

图37-6 SPI时钟格式(CPHA = 0)

图37-7 SPI波特率发生器

图37-8 正常模式和双向模式

图37-9 SPI主设备的初始化流程实例

图38-1 I2C功能框图

图38-2 I2C总线传输信号

图38-3 I2C时钟同步

图38-4 超时测量间隔

图38-5 可编程输入干扰滤波器图

图38-6 典型的I2C中断服务程

图38-7 典型的I2C的SMBus中断服务程序

图39-1 UART发送器模块框图

图39-2 UART发送器模块框图

图40-1 UART发送器模块框图

图40-2 UART接收器模块框图

图40-3 UART波特率生成器

图42-1 TSI结构图

图42-2 TSI电极性晶振线路

图42-3 TSI电极晶振图

图42-4 噪声探测模式下的TSI电路

图42-5 噪声探测模式下波形

图42-6 噪声阈值自动管理模块

第10章 复用信号和信号描述

10.1 概要

10.2 内部集成信号复用

表10-1 相关的信息

10.2.1 端口控制和中断性能

10.2.2 时钟门

10.2.3 信号复用系统规定参数

10.3 引脚输出

10.3.1 KL25信号复用和引脚列表

10.3.2 KL25引脚输出

10.4 模块信号描述表

10.4.1 内核模块

10.4.2 系统模块

10.4.3 时钟模块

10.4.4 存储和存储器接口

10.4.5 模拟信号

10.4.6 时钟模块

10.4.7 通信接口

10.4.8 人机接口(Human-Machine Interfaces ,HMI)

第11章 端口控制与中断 (PORT)

11.1 简介

11.2 概述

11.2.1 特征

11.2.2 工作模式

11.2.2.1 运行模式

11.2.2.2 等待模式

11.2.2.3 停止模式

11.2.2.4 调试模式

11.3 外部引脚描述

11.4 引脚信号详细说明

11.5 内存映射与寄存器定义

11.5.1 引脚控制寄存器n (PORTx_PCRn)

11.5.2 全局引脚控制地位寄存器 (PORTx_GPCLR)

11.5.3 全局引脚控制高位寄存器 (PORTx_GPCHR)

11.5.4 中断状态标志寄存器 (PORTx_ISFR)

11.6 功能说明

11.6.1 引脚控制

11.6.2 全局引脚控制

11.6.3 外部中断

第12章 系统集成模块(SIM)

12.1 简介

12.1.1 特性

12.2 内存映像和寄存器定义

12.2.1 系统选项寄存器1(SIM_SOPT1)

12.2.2 SOPT1配置寄存器(SIM_SOPT1CFG)

12.2.3 系统选项寄存器(SIM_SOPT2)

12.2.4 系统选项寄存器4(SIM_SOPT4)

12.2.5 系统选项寄存器5(SIM_SOPT5)

12.2.6 系统选项寄存器7(SIM_SOPT7)

12.2.7 系统设备识别寄存器(SIM_SDID)

12.2.8 系统时钟门控制寄存器4(SIM_SCGC4)

12.2.9 系统时钟门控制寄存器5(SIM_SCGC5)

12.2.10 系统时钟门控制寄存器6(SIM_SCGC6)

12.2.11 系统时钟门控制寄存器7(SIM_SCGC7)

12.2.12 系统时钟分频寄存器1(SIM_CLKDIV1)

12.2.13 Flash配置寄存器1(SIM_FCFG1)

12.2.14 Flash配置寄存器2(SIM_FCFG2)

12.2.15 唯一识别寄存器Mid-High(SIM_UIDMH)

12.2.16 唯一识别寄存器Mid-Low(SIM_UIDML)

12.2.17 唯一识别寄存器 Low(SIM_UIDL)

12.2.18 COP控制寄存器(SIM_COPC)

12.2.19 服务COP寄存器(SIM_SRVCOP)

12.3 功能描述

第13章 系统模式控制器

13.1 简介

13.2 操作模式

13.3 内存映射和寄存器描述

13.3.1 电源模式保护寄存器(SMC_PMPROT)

12.3.2 电源模式控制寄存器(SMC_PMCTRL)

13.3.3 停止控制寄存器(SMC_STOPCTRL)

13.3.4 电源模式状态寄存器(SMC_PMSTAT)

13.4 功能描述

13.4.1 电源模式转换

13.4.2 电源模式进入/退出顺序

13.4.2.1 停止模式进入顺序

13.4.2.2 停止模式退出序列

13.4.2.3 终止停止模式进入

13.4.2.4 转换到等待模式

13.4.2.5 从停止模式到调试模式的转换

13.4.3 运行模式

13.4.3.1 运行模式

13.4.3.2 非常低功耗运行(VLPR)模式

13.4.4 等待模式

13.4.4.1 等待模式

13.4.4.2 非常低功耗等待(VLPW)模式

13.4.5 停止模式

13.4.5.1 停止模式

13.4.5.2 非常低电压停止(VLPS)模式

13.4.5.3 低漏停止(LLS)模块

13.4.5.4 非常低漏停止(VLLSx)模式

13.4.6 低功耗模式的调试

第14章 电源管理控制器

14.1 简介

14.2 特性

14.3 低电压检测(LVD)系统

14.3.1 LVD复位操作

14.3.2 LVD中断操作

14.3.3 低电压警告(LVW)中断操作

14.4 IO保存

14.5 内存映射和寄存器描述

14.5.1 低电压检测状态和控制1寄存器(PMC_LVDSC1)

14.5.2 低电压检测状态和控制2寄存器(PMC_LVDSC2)

14.5.3 调节状态和控制寄存器(PMC_REGSC)

第15章 低漏唤醒单元(LLWU)

15.1 简介

15.1.1 特性

15.1.2 操作模式

15.1.3 块表

15.2 LLWU信号描述

15.3 内存映射/寄存器定义

15.3.1 LLWU引脚使能1寄存器(LLWU_PE1)

15.3.2 LLWU引脚使能2寄存器(LLWU_PE2)

15.3.3 LLWU引脚使能3寄存器(LLWU_PE3)

15.3.4 LLWU引脚使能4寄存器(LLWU_PE4)

15.3.5 LLWU模块使能寄存器(LLWU_ME)

15.3.6 LLWU标志1寄存器(LLWU_F1)

15.3.7 LLWU标志2寄存器(LLWU_F2)

15.3.8 LLWU标志3寄存器(LLWU_F3)

15.3.9 LLWU引脚过滤器1寄存器(LLWU_FILT1)

15.3.10 LLWU引脚过滤器2寄存器(LLWU_FILT2)

15.4 功能描述

15.4.1 LLSM模块

15.4.2 VLLS模块

15.4.3 初始化

第12章 系统集成模块(SIM)

12.1 简介

12.1.1 特性

12.2 内存映像和寄存器定义

12.2.1 系统选项寄存器1(SIM_SOPT1)

12.2.2 SOPT1配置寄存器(SIM_SOPT1CFG)

12.2.3 系统选项寄存器2(SIM_SOPT2)

12.2.4 系统选项寄存器4(SIM_SOPT4)

12.2.5 系统选项寄存器5(SIM_SOPT5)

12.2.6 系统选项寄存器7(SIM_SOPT7)

12.2.7 系统设备识别寄存器(SIM_SDID)

12.2.8 系统时钟门控制寄存器4(SIM_SCGC4)

12.2.9 系统时钟门控制寄存器5(SIM_SCGC5)

12.2.10 系统时钟门控制寄存器6(SIM_SCGC6)

12.2.11 系统时钟门控制寄存器7(SIM_SCGC7)

12.2.12 系统时钟分频寄存器1(SIM_CLKDIV1)

12.2.13 Flash配置寄存器1(SIM_FCFG1)

12.2.14 Flash配置寄存器2(SIM_FCFG2)

12.2.15 唯一识别寄存器Mid-High(SIM_UIDMH)

12.2.16 唯一识别寄存器Mid-Low(SIM_UIDML)

12.2.17 唯一识别寄存器 Low(SIM_UIDL)

12.2.18 COP控制寄存器(SIM_COPC)

12.2.19 服务COP寄存器(SIM_SRVCOP)

12.3 功能描述

第13章 系统模式控制器

13.1 简介

13.2 操作模式

13.3 内存映射和寄存器描述

13.3.1 电源模式保护寄存器(SMC_PMPROT)

12.3.2 电源模式控制寄存器(SMC_PMCTRL)

13.3.3 停止控制寄存器(SMC_STOPCTRL)

13.3.4 电源模式状态寄存器(SMC_PMSTAT)

13.4 功能描述

13.4.1 电源模式转换

13.4.2 电源模式进入/退出顺序

13.4.2.1 停止模式进入顺序

13.4.2.2 停止模式退出序列

13.4.2.3 终止停止模式进入

13.4.2.4 转换到等待模式

13.4.2.5 从停止模式到调试模式的转换

13.4.3 运行模式

13.4.3.1 运行模式

13.4.3.2 非常低功耗运行(VLPR)模式

13.4.4 等待模式

13.4.4.1 等待模式

13.4.4.2 非常低功耗等待(VLPW)模式

13.4.5 停止模式

13.4.5.1 停止模式

13.4.5.2 非常低电压停止(VLPS)模式

13.4.5.3 低漏停止(LLS)模块

13.4.5.4 非常低漏停止(VLLSx)模式

13.4.6 低功耗模式的调试

第14章 电源管理控制器

14.1 简介

14.2 特性

14.3 低电压检测(LVD)系统

14.3.1 LVD复位操作

14.3.2 LVD中断操作

14.3.3 低电压警告(LVW)中断操作

14.4 IO保存

14.5 内存映射和寄存器描述

14.5.1 低电压检测状态和控制1寄存器(PMC_LVDSC1)

14.5.2 低电压检测状态和控制2寄存器(PMC_LVDSC2)

14.5.3 调节状态和控制寄存器(PMC_REGSC)

第15章 低漏唤醒单元(LLWU)

15.1 简介

15.1.1 特性

15.1.2 操作模式

15.1.3 块表

15.2 LLWU信号描述

15.3 内存映射/寄存器定义

15.3.1 LLWU引脚使能1寄存器(LLWU_PE1)

15.3.2 LLWU引脚使能2寄存器(LLWU_PE2)

15.3.3 LLWU引脚使能3寄存器(LLWU_PE3)

15.3.4 LLWU引脚使能4寄存器(LLWU_PE4)

15.3.5 LLWU模块使能寄存器(LLWU_ME)

15.3.6 LLWU标志1寄存器(LLWU_F1)

15.3.7 LLWU标志2寄存器(LLWU_F2)

15.3.8 LLWU标志3寄存器(LLWU_F3)

15.3.9 LLWU引脚过滤器1寄存器(LLWU_FILT1)

15.3.10 LLWU引脚过滤器2寄存器(LLWU_FILT2)

15.4 功能描述

15.4.1 LLSM模块

15.4.2 VLLS模块

第16章 复位控制模块

16.1 介绍

16.2 RCM的存储器映射与寄存器描述

16.2.1 系统复位状态寄存器0(RCM_SRS0)

16.2.2 系统复位状态寄存器1(RCM_SRS1)

16.2.3 复位引脚滤波控制寄存器(RCM_RPFC)

16.2.4 复位引脚滤波宽度寄存器(RCM_RPFW)

第17章 位操作引擎

17.1 介绍

17.1.1 概述

17.1.2 特征

17.1.3 操作模式

17.2 外部信号描述

17.3 存储映射和寄存器定义

17.4 功能描述

17.4.1 BME封装式存储

17.4.1.1 封装式存储逻辑运算AND

1. 封装式存储逻辑运算OR

2. 封装式存储逻辑运算XOR

17.4.1.4 封装式存储数据位插入操作(BFI)

17.4.2 BME 封装式载入

1. 封装式载入-清除操作(LAC1)

2. 封装式载入-置位操作(LAS1)

3. 封装式载入无符号位提取操作(UBFX)

17.5 应用信息

第18章 杂项控制模块(MCM)

18.1 介绍

18.1.1 特征

18.2 存储器映射与寄存器描述

18.2.1 交叉开关(ABXS)从机配置(MCM_PLASC)

18.2.2 交叉开关(AXBS)主机配置(MCM_PLAMC)

18.2.3 平台控制寄存器(MCM_PLACR)

18.2.4 计算操作控制寄存器(MCM_CPO)

第19章 微型跟踪缓冲区(MTB)

19.1 介绍

19.1.1 概述

19.1.2 特征

19.1.3 操作模式

19.2 外部信号描述

19.3 存储器映射和寄存器定义

19.3.1 MTB_RAM存储器映射

1. MTB定位寄存器(MTB_POSITION)

2. MTB主机寄存器(MTB_MASTER)

3. MTB流寄存器(MTB_FLOW)

4. MTB基址寄存器(MTB_BASE)

5. 集成模式控制寄存器(MTB_MODECTRL)

6. TAG置位寄存器(MTB_TAGSET)

7. 锁存访问寄存器(MTB_LOCKACCESS)

8. 锁存状态寄存器(MTB_LOCKSTAT)

9. 锁存状态寄存器(MTB_AUTHSTAT)

10.设备架构寄存器(MTB_DEVICEARCH)

11.设备配置寄存器(MTB_DEVICECFG)

12. 设备类型标识符寄存器(MTB_DEVICETYPID)

13. 外设ID寄存器(MTB_PERIPHIDn)

14. 组件ID寄存器(MTB_COMPIDn)

19.3.2 MTB_DWT 寄存器映射

1. MTB DWT 控制寄存器(MTBDWT_CTRL)

2. MTB_DWT 比较器寄存器(MTBDWT_COMPn)

3. MTB DWT Comparator Mask Register(MTBDWT_MASKn)

4. MTB_DWT 比较器功能寄存器0(MTBDWT_FCT0)

5. MTB_DWT 比较器功能寄存器1(MTBDWT_FCT1)

6. MTB_DWT 跟踪缓冲区控制寄存器(MTBDWT_TBCTRL)

7. 设备配置寄存器(MTBDWT_DEVICECFG)

8. 设备类型标识符寄存器(MTBDWT_DEVICETYPID)

9. 外设ID寄存器(MTBDWT_PERIPHIDn)

10. 组件ID寄存器(MTBDWT_COMPIDn)

19.3.3 系统ROM存储器映射

1. 入口(ROM_ENTRYn)

2. 表格标记结束寄存器(ROM_TABLEMARK)

3. 系统访问寄存器(ROM_SYSACCESS)

4. 外设ID寄存器(ROM_PERIPHIDn)

5. 组件ID寄存器(ROM_COMPIDn)

第20章 交叉开关(crossbar switch Lite)

20.1 引言

20.1.1 特性

20.2 存储器映像/寄存器定义

20.3 功能说明

20.3.1 一般操作

较高优先级的主机有:

2)当主机挂起一个从机端口时,较低优先级的主机可以对该端口的从机进行访问。

20.3.2 仲裁

20.3.2.1 未定义长度的突发访问期间的仲裁

20.3.2.2 固定优先级操作

20.3.2.3 循环优先级的操作

20.4 初始化/应用信息

第21章 外设桥

21.1 引言

21.1.1 特性

21.1.2 一般操作

21.2 功能说明

21.2.1 访问支持

第22章 DMA复用器(DMAMUX)

22.1 引言

22.1.1 概述

22.1.2 特性

22.1.3 工作模式

22.2 外部引脚描述

22.3 存储器映像/寄存器定义

22.3.1 通道配置寄存器(DMAMUXx_CHCFGn)

22.4 功能说明

22.4.1 DMA通道的定时触发功能

20.4.2 没有触发功能的DMA通道

22.4.3 在线DMA使能

22.5 初始化信息

22.5.1 复位

22.5.2 使能和配置DMA源

第23章 DMA控制器模块(DMA Controller Module)

23.1 引言

23.1.1 概述

23.1.2 特性

23.2 DMA传输概述

23.3 储存器映射/寄存器定义

23.3.1 源地址寄存器(DMA_SARn)

23.3.2 目的地址寄存器(DMA_DARn)

23.3.3 DMA状态/字节计数寄存器(DMA_DSR_BCRn)

23.3.4 DMA控制寄存器(DMA_DCRn)

23.4 功能说明

23.4.1传输请求(周期挪用和连续模式)

23.4.2 通道的初始化和启动

23.4.2.1 通道优先级

23.4.2.2 DMA控制寄存器的编程

23.4.3 双地址传输模式

23.4.4 提前数据传输控制:矩阵

23.4.5 终止

第24章 多用途时钟信号生成器(MCG)

24.1 介绍

24.1.1 特性

24.1.2 运行模式

24.2 外部信号描述

24.3 内存映射/寄存器定义

24.3.1 MCG 控制寄存器1(MCG_C1)

24.3.2 MCG 控制寄存器2(MCG_C2)

24.3.3 MCG 控制寄存器3(MCG_C3)

24.3.4 MCG 控制寄存器4(MCG_C4)

24.3.5 MCG 控制寄存器5(MCG_C5)

24.3.6 MCG 控制寄存器6(MCG_C6)

24.3.7 MCG 状态寄存器(MCG_S)

24.3.8 MCG状态控制寄存器(MCG_SC)

24.3.9 MCG自动校准比较值高位寄存器(MCG——ATCVH)

24.3.10 MCG自动校准比较值低位寄存器(MCG—ATCVL)

24.3.11 MCG 控制寄存器7(MCG_C7)

24.3.12 MCG 控制寄存器8(MCG_C8)

24.3.13 MCG 控制寄存器9(MCG_C9)

24.3.14 MCG 控制寄存器10(MCG_C10)

24.4 功能描述

24.4.1 MCG模式状态图

24.4.1.1 MCG操作模式

24.4.1.2 MCG模式转换

24.4.2 低功耗位用法

24.4.3 MCG内部参考时钟

24.4.3.1 MCG内部参考时钟

24.4.4 MCG外部参考时钟

24.4.5 MCG固定时钟频率

24.4.6 MCG PLL时钟

24.4.7 MCG自动调整(ATM)

24.5 初始化/实例信息

24.5.1 MCG模块初始化流程

24.5.1.1 MCG初始化

24.5.2 使用32.768kHz参考

24.5.3 MCG模式转换

24.5.3.1 示例1:从FEI转换到PEE模式:外部晶振= 4MHz,MCGOUT频率=48MHz。

24.5.3.2 示例2:从PEE到BLPI的转变:MCGOUT频率=32KHz。

24.5.3.3 示例3:从BLPI到FEEE模式的转变。

第25章 振荡器(Oscillator,OSC)

25.1 导言

25.2 功能与模式

25.3 结构图

25.4 OSC引脚说明

25.5 外部晶振/谐振器连接

25.6 外部时钟连接

25.7 存储器映射/寄存器定义

25.7.1 OSC存储器映射/寄存器定义

25.7.1.1 OSC控制寄存器 (OSC_CR)

25.8 功能说明

25.8.1 OSC模块状态

25.8.1.1 关闭

25.8.1.2 振荡器启动(Oscillator Start-Up)

25.8.1.3 振荡器稳定(Oscillator Stable)

25.8.1.4 外部时钟状态

25.8.2 OSC模块模式

25.8.2.1 低频率,高增益模式

25.8.2.2 低频率,低功耗模式

25.8.2.3 高频率,高增益模式

25.8.2.4 高频率,低功耗模式

25.8.3 计数器

25.8.4 对参考时钟引脚的需求

25.9 复位

25.10 低功耗操作

25.11 中断

第26章 FLASH内存控制器(FMC)

26.1 介绍

26.1.1 概述

26.1.2 特征

26.2 操作模式

26.3 外部信号描述

26.4 内存映射和寄存器描述

26.5 功能描述

第27章 Flash存储器模块(FTFA)

27.1 引言

27.1.1特征

27.1.1.1 程序Flash储存储器特点

27.1.1.2 Flash存储器模块其他特点

27.1.2 块图表

27.1.3 术语

27.2 外部信号描述

27.3 存储器映射和寄存器

27.3.1 Flash配置字段描述

27.3.2 Flash IFR映射

27.3.2.1 一次写入字段

27.3.3 寄存器描述

FTFL 内存映射

27.3.3.1 内存状态寄存器(FTFL_FSTAT)

27.3.3.2 Flash配置寄存器(FTFL_FCNFG)

27.3.3.3 Flash安全寄存器(FTFL_FSEC)

27.3.3.4 Flash选项寄存器(FTFL_FOPT)

27.3.3.5 Flash通用命令对象寄存器(FTFL_FCCOBn)

27.3.3.6 Flash保护寄存器(FTFL_FPROTn)

27.4 功能描述

27.4.1 Flash保护

27.4.2 中断

表27-1 Flash中断源

27.4.3 低功耗模式下的Flash操作

27.4.3.1 等待模式

27.4.3.2. 停止模式

27.4.4 操作模式的函数

27.4.5 Flash 读和写忽视

27.4.6 写时读(RWW)

27.4.7 Flash写入和擦写

FTFL命令操作

27.4.8.1 命令写次序

27.4.8.1.1 装载FCCOB寄存器

27.4.8.1.2 通过清除CCIF位运行命令

27.4.8.1.3 命令执行和错误报告

27.4.8.2FTFL命令

27.4.8.3按模块分类flash命令

27.4.9 空白读命令

27.4.10 FTFL命令描述

27.4.10.1读1s段命令

27.4.10.2 程序检查命令

27.4.10.3读资源命令

27.4.10.4 程序长字命令

27.4.10.5擦除flash段命令

27.4.10.5.1 挂起擦除flash段操作

27.4.10.5.2恢复挂起的擦除flash段操作

27.4.10.5.3中止挂起擦除flash段操作

27.4.10.6读1s所有块命令

28.4.12.7一次读命令

27.4.10.8 一次写入命令

27.4.10.9擦除所有块命令

27.4.10.9.1激活flash所有的外部擦除操作

27.4.10.10验证后门访问密钥机制命令

27.4.11 安全

27.4.11.1 通过安全模式进入FTFL

27.4.11.2改变安全状态

27.4.11.2.1 使用后门密阴访问机制来解密芯片

27.4.12 重设次序

第28章 模拟—数字转换器

28.1 概述

28.1.1 特性

28.1.2 模块示意图

28.2 ADC 引脚描述

28.2.1 模拟电源(VDDA)

28.2.2 模拟地

28.2.3 参考电压选择

28.2.4 模拟通道输入

28.2.5 差分模拟通道输入(DADx)

28.3 寄存器定义

28.3.1 ADC状态控制寄存器1(ADC0_SC1n)

28.3.2 ADC配置寄存器(ADC0_CFG1)

28.3.3 ADC配置寄存器2(ADC0_CFG2)

28.3.4 ADC数据结果寄存器(ADC0_Rn)

28.3.5 ADC比较值寄存器(ADC0_CVn)

28.3.6 ADC状态控制寄存器2(ADC0_SC2)

28.3.7 ADC状态控制寄存器3(ADC0_SC3)

28.3.8 ADC偏移量修正寄存器(ADC0_OFS)

28.3.9 ADC正向增益寄存器(ADC0_PG)

28.3.10 ADC负向增益寄存器(ADC0_MG)

28.3.11 ADC正向增益通用校验值寄存器(ADC0_CLPD)

28.3.12 ADC正向增益通用校验值寄存器(ADC0_CLPS)

28.3.13 ADC正向增益通用校验值寄存器(ADC0_CLP4)

28.3.14 ADC正向增益通用校验值寄存器(ADC0_CLP3)

28.3.15 ADC正向增益通用校验值寄存器(ADC0_CLP2)

28.3.16 ADC正向增益通用校验值寄存器(ADC0_CLP1)

28.3.17 ADC正向增益通用校验值寄存器(ADC0_CLP0)

28.3.18 ADC负向增益通用校验值寄存器(ADC0_CLMD)

28.3.19 ADC负向增益通用校验值寄存器(ADC0_CLMS)

28.3.20 ADC负向增益通用校验值寄存器(ADC0_CLM4)

28.3.21 ADC负向增益通用校验值寄存器(ADC0_CLM3)

28.3.22 ADC负向增益通用校验值寄存器(ADC0_CLM2)

28.3.23 ADC负向增益通用校验值寄存器(ADC0_CLM1)

28.3.24 ADC负向增益通用校验值寄存器(ADC0_CLM0)

28.4 功能描述

28.4.1 时钟选择和分频控制

28.4.2 参考电压选择

28.4.3 硬件触发和通道选择

28.4.4 转换控制

28.4.4.1 启动转换

28.4.4.2 完成转换

28.4.4.3 取消转换

28.4.4.4 电源控制

28.4.4.5 长时间采样和总转换时间

28.4.4.6 转换时间实例

28.4.4.6.1 典型的转换时间配置

28.4.4.6.2 短时间采样配置

28.4.4.7 硬件计算均值功能

28.4.5 自动比较功能

28.4.6 校验功能

28.4.7 用户自定义的偏移功能

28.4.8 温度传感器

28.4.9 MCU等待模式

28.4.10 正常停止模式

28.4.10.1 ADACK禁止的正常停止模式

28.4.10.2 ADACK使能的正常停止模式

28.4.11 MCU低功耗停止模式

28.5 初始化信息

28.5.1 ADC模块初始化样例

28.5.5.1 初始化顺序

28.5.1.2 伪代码示例

28.6 应用信息

28.6.1 外部采集引脚

28.6.1.1 模拟量采集引脚

28.6.1.2 模拟电压参考引脚

28.6.1.3 模拟输入引脚

28.6.2 错误源

28.6.2.1 采样错误

28.6.2.2 引脚泄漏错误

28.6.2.3 噪声引起的错误

28.6.2.4 编码宽度和量化误差错误

28.6.2.5 线性误差

28.6.2.6 编码抖动,非单调性和失码

第29章 比较器

29.1 引言

29.2 比较器特点

6位DAC主要特性

29.4 ANMUX主要特性

29.5 比较器,数模转换和模拟复用器的结构图

29.6 CMP结构图

29.7 存储器映射/寄存器定义

29.7.1 CMP控制寄存器0(CMPx_CR0)

29.7.2 CMP控制寄存器1(CMPx_CR1)

29.7.3 CMP滤波周期南寄存器(CMPx_FPR)

29.7.4 CMP状态控制寄存器(CMPx_SCR)

29.7.5 DAC控制寄存器(CMPx_DACCR)

29.7.6 MCU控制寄存器(CMPx_MUXCR)

29.8 功能描述

29.8.1 CMP功能模式

29.8.1.1 禁止模式

29.8.1.2 连续模式(#s2A&2B)

29.8.1.3 采样,无滤波模式(#s3A&3B)

29.8.1.4 采样滤波模式(#s4A&4B)

29.8.1.5 窗口模式(#s5A&5B)

29.8.1.6 窗口/重复采样模式(#6)

29.8.1.7 窗口/滤波模式(#7)

29.8.2 电源模式

29.8.2.1 等待模式

29.8.2.2 停止模式

29.8.2.3 低漏电模式

29.8.2.4 后台调试模式

29.8.3 启动和运行

29.8.4 低通滤波器

29.8.4.1 滤波器模式使能

28.8.4.2 延迟问题

29.9 CMP中断

29.10 CMP对DMA的支持

29.11 CMP支持异步DMA

29.12 数模转换

29.13 DAC功能描述

参考电压选择

29.14 DAC复位

29.15 DAC时钟

29.16 DAC中断

29.17 CMP触发模式

第30章 12位的模数转换器

30.1 概述

30.2 特性

30.3 结构图

30.4 寄存器映像/寄存器定义

30.4.1 DAC数据(低)寄存器(DACx_DATnL)

30.4.2 DAC数据(高)寄存器(DACx_DATnH)

30.4.3 DAC状态寄存器(DACx_SR)

30.4.4 DAC控制寄存器(DACx_C0)

30.4.5 DAC控制器1(DACx_C1)

30.4.6 DAC控制寄存器(DACx_C2)

30.5 功能描述

30.5.1 DAC数据缓冲操作

30.5.1.1 DAC数据缓冲中断

30.5.1.2 DAC数据缓冲操作模式

30.5.2 DMA操作

30.5.3 复位

30.5.4 低功耗模式操作

第31章 定时器/脉宽调制模块(TPM)

31.1 概述

31.1.1 TPM理念

31.1.2 功能

31.1.3 操作模式

31.1.4 框图

31.2 TPM信号描述

31.2.1 TPM_EXTCLK - TPM外部时钟

31.2.2 TPM_CHn – TPM通道(n)I/O引脚

31.3 内存映射和寄存器定义

31.3.1 状态和控制(TPMx_SC)

31.3.2 计数器(TPMx_CNT)

31.3.3 取模(TPMx_MOD)

31.3.4 通道(n)状态和控制(TPMx_CnSC)

31.3.5 通道(n)值(TPMx_CnV)

31.3.6 捕捉和比较状态(TPMx_STATUS)

31.3.7 配置(TPMx_CONF)

31.4 功能描述

31.4.1 时钟域

31.4.1.1 计数器时钟模式

31.4.2 预分频器

31.4.3 计数器

31.4.3.1 上升计数

31.4.3.2 可逆计数

31.4.3.3 计数器复位

31.4.4 输入捕捉模式

31.4.5 输出比较模式

31.4.6 边沿对齐PWM(EPWM)模式

31.4.7 中心对齐PWM(CPWM)模式

31.4.8 寄存器被写缓冲区更新

31.4.8.1 MOD 寄存器更新

31.4.8.2 CnV 寄存器更新

31.4.9 DMA

31.4.10 复位概述

31.4.11 TPM中断

31.4.11.1 定时器溢出中断

31.4.11.2 通道(n)中断

第32章 周期性中断定时器(PIT)

32.1 简介

32.1.1 框图

32.1.2 功能

32.2 信号描述

32.3 内存映射/寄存器描述

32.3.1 PIT模块控制寄存器(PIT_MCR)

32.3.2 PIT上层生命周期器寄存器(PIT_LTMR64H)

32.3.3 PIT下层生命周期定时器寄存器(PIT_LTMR64L)

32.3.4 定时器载入值寄存器(PIT_LDVALn)

32.3.5 当前定时器值寄存器(PIT_CVALn)

32.3.6 定时器控制寄存器(PIT_TCTRLn)

32.3.7 定时器标记寄存器(PIT_TFLGn)

32.4 功能描述

32.4.1 通用操作

32.4.1.1 定时器

32.4.1.2 调试模式

32.4.2 中断

32.4.3 链接定时器

32.5 初始化和应用信息。

32.6 示例配置链接定时器

32.7 示例配置为生命周期定时器

第33章 低功耗定时器(LPTMR)

33.1 简介

33.1.1 功能

33.1.2 操作模式

33.2 LPTMR信号描述

33.2.1 详细的信号描述

33.3 内存映射和寄存器的定义

33.3.1 低功率定时器控件状态寄存器(LPTMRx_CSR)

33.3.2 低功耗定时器预分频寄存器(LPTMRx_PSR)

33.3.3 低功耗定时器比较寄存器(LPTMRx_CMR)

33.3.4 低功耗定时器计数寄存器(LPTMRx_CNR)

33.4 功能描述

33.4.1 LPTMR功耗和复位

33.4.2 LPTMR时钟

33.4.3 LPTMR预分频器/故障过滤器

33.4.3.1 预分频器使能

33.4.3.2 预分频器旁路

33.4.3.3 故障过滤器

33.4.3.4 故障过滤器旁路

33.4.4 LPTMR比较

33.4.5 LPTMR计数器

33.4.6 LPTMR硬件触发

33.4.7 LPTMR中断

第34章 实时时钟(RTC)

34.1 简介

34.1.1 功能

34.1.2 操作模式

34.1.3 RTC信号描述

34.1.3.1 RTC时钟输出

34.2 寄存器定义

34.2.1 RTC定时秒寄存器(RTC_ TSR)

34.2.2 RTC定时预分频器寄存器(RTC_ TPR)

34.2.3 RTC时间报警寄存器(RTC_TAR)

34.2.4 RTC定时补偿寄存器(RTC_TCR)

34.2.5 RTC控制寄存器(RTC_CR)

34.2.6 RTC状态寄存器(RTC_SR)

34.2.7 RTC锁存器 (RTC_LR)

34.2.8 RTC中断使能寄存器(RTC_IER)

34.3 功能描述

34.3.1 电源、时钟和复位

34.3.1.1 振荡器控制

34.3.1.2 软件复位

34.3.1.3 监管访问

34.3.2 定时计数器

34.3.3 补偿

34.3.4 定时报警

34.3.5 更新模式

34.3.6 寄存器锁

34.3.7 中断

第35章 USB总线OTG控制器

35.1 简介

35.1.1 USB

35.1.2 USB OTG功能

35.1.3 USB-FS特点

35.2 功能描述

35.2.1 数据结构

35.3 编程接口

35.3.1 缓冲区描述符表

35.3.2 作为USB目标设备或者USB主机的数据收发

35.3.3 寻址缓冲区描述符表实体

35.3.4 缓冲区描述符格式

35.3.5 USB传输

35.4 内存映射/寄存器定义

35.4.1 外设ID寄存器(USBx_PERID)

35.4.2 外设ID补码寄存器(USBx_IDCOMP)

35.4.3 外设修订寄存器(USBx_REV)

35.4.4 外设附加信息寄存器(USBx_ADDINFO)

35.4.5 OTG中断状态寄存器(USBx_OTGISTAT)

35.4.6 OTG中断控制寄存器(USBx_OTGICR)

35.4.7 OTG状态寄存器(USBx_OTGSTAT)

35.4.8 OTG控制寄存器(USBX_OTGCTL)

35.4.9 中断状态寄存器(USBx_ISTAT)

35.4.10 中断使能寄存器(USBx_INTEN)

35.4.11 错误中断状态寄存器(USBx_ERRSTAT)

35.4.12 错误中断使能寄存器(USBx_ERREN)

35.4.13 状态寄存器(USBx_STAT)

35.4.14 控制寄存器(USBx_CTL)

35.4.15 地址寄存器(USBx_ADDR)

35.4.16 BDT页寄存器1(USBx_BDTPAGE1)

35.4.17 帧号低位寄存器(USBx_FRMNUML)

35.4.18 帧号高位寄存器(USBx_FRMNUMH)

35.4.19 令牌寄存器(USBx_TOKEN)

35.4.20 SOF阈值寄存器(USBx_SOFTHLD)

35.4.21 BDT页寄存器2(USBx_BDTPAGE2)

35.4.22 BDT页寄存器3(USBx_BDTPAGE3)

35.4.23 端点控制寄存器(USBx_ENDPTn)

35.4.24 USB控制寄存器(USBx_USBCTRL)

35.4.25 USB检测寄存器(USBx_OBSERVE)

35.4.26 USB OTG控制寄存器(USBx_CONTROL)

35.4.27 USB收发控制寄存器0(USBx_USBTRC0)

35.4.28 帧调整寄存器(USBx_USBFRMADJUST)

35.5 OTG和主机模式操作

35.6 主机操作模式的例子

35.7 OTG操作

35.7.1 A设备操作的OTG双重角色

35.7.2B设备操作的OTG双重角色

第36章USB电压调节器

36.1简介

36.1.1 概述

36.1.2 特征

36.1.3 操作模式

36.2 USB电压调节器模块信号描述

第37章 串行外设接口SPI

37.1 介绍

37.1.1 特性

37.1.2 操作模式

37.1.3 结构图

37.1.3.1 SPI系统结构图

37.1.3.2 SPI模块结构图

37.2 外部信号描述

37.2.1 SPSCK - SPI串行时钟

37.2.2 MOSI – 主机数据输出,从机数据输入

37.2.3 MISO-主机数据输入,从机数据输出

37.2.4 AA—从机选择

选择

37.3 地址映射和寄存器说明

37.3.1 SPI控制寄存器1(SPIx-C1)

37.3.2 SPI控制寄存器2(SPIx-C2)

37.3.3 SPI波特率寄存器(SPIx_BR)

37.3.4 SPI状态寄存器(SPIx_S)

37.3.5 SPI数据寄存器(SPIx_D)

37.3.6 SPI匹配寄存器(SPIx_M)

37.4 功能说明

37.4.1 一般

37.4.2 主模式

37.4.3 从模式

37.4.4 通过DMA的SPI传输

37.4.4.1 通过DMA发送

37.4.4.2 DMA接收

37.4.5 SPI时钟格式

37.4.6 SPI波特率发生器

37.4.7 特殊功能

37.4.7.1 输出

37.4.7.2 双向模式(MOMI或SISO)

37.4.8 错误条件

37.4.8.1 模式故障

37.4.9 低功率模式选项

37.4.9.1 运行模式SPI

37.4.9.2 等待模式SPI

37.4.9.3 SPI在停止模式

37.4.10 复位

37.4.11 中断

37.4.11.1 MODF

37.4.11.2 SPRF

37.4.11.3 SPTEF

37.4.11.4 SPMF

37.4.11.5 在低功耗模式下的异步中断

37.5 初始化/应用信息

37.5.1 初始化序列

37.5.2 伪代码示例

第38章 内部集成电路 (I2C)

38.1 介绍

38.1.1 特点

38.1.2 操作模式

38.1.3 框图

38.2 I2C信号说明

38.3 内存映射和寄存器描述

38.3.1 I2C地址寄存器1(I2Cx_A1)

38.3.2 I2C分频寄存器(I2Cx_F)

38.3.3 I2C控制寄存器1(I2Cx_C1)

38.3.4 I2C状态寄存器(I2Cx_S)

38.3.5 I2C数据I / O寄存器(I2Cx_D)

38.3.6 I2C控制寄存器2(I2Cx_C2)

38.3.7 I2C可编程输入电子脉冲滤波寄存器(I2Cx_FLT)

38.3.8 I2C范围地址寄存器(I2Cx_RA)

38.3.9 I2C SMBus控制和状态寄存器(I2Cx_SMB)

38.3.10 I2C地址寄存器2(I2Cx_A2)

38.3.11 I2C SCL低超时寄存器高(I2Cx_SLTH)

38.3.12 I2C SCL低电平超时寄存器低(I2Cx_SLTL)

38.4功能描述

38.4.1 I2C协议

38.4.1.1 START信号

38.4.1.2 从机地址传输

38.4.1.3 数据传输

38.4.1.4 STOP信号

38.4.1.5 重复开始信号

38.4.1.6 仲裁程序

38.4.1.7 时钟同步

38.4.1.8 握手

38.4.1.9 时钟延长

38.4.1.10 I2C分频器和保持值

38.4.2.1 主机访问从机接收器

38.4.2.2 主接收器访问从发送器

38.4.3 地址匹配

38.4.4 系统管理总线规范

38.4.4.1 超时

1. SCL低超时

2.SCL高超时

3. CSMBCLK TIMEOUT MEXT 和 CSMBCLK TIMEOUT SEXT

38.4.4.2 FAST ACK和NACK

38.4.5 复位

38.4.6 中断

38.4.6.1 字节传输中断

38.4.6.2 地址检测中断

38.4.6.3 停止检测中断

38.4.6.4 退出低功耗/停止模式

38.4.6.5 仲裁丢失中断

38.4.6.6 在SMBus上的超时中断

38.4.7 可编程输入电子脉冲滤波器

38.4.8 地址匹配唤醒

38.4.9 DMA支持

38.5 初始化/应用信息

第39章 通用异步接收器/发送器(UART0)

39.1 简介

39.1.1 特征

39.1.2 操作模式

39.1.2.1 停止模式

39.1.2.2 等待模式

39.1.2.3 调试模式

39.1.3 模块框图

39.2 寄存器定义

39.2.1 UART波特率寄存器高(UARTx_BDH)

39.2.2 UART波特率寄存器低(UARTx_BDL)

39.2.3 UART控制寄存器1(UARTx_C1)

39.2.4 UART控制寄存器2(UARTx_C2)

39.2.5 UART状态寄存器1(UARTx_S1)

39.2.6 UART状态寄存器2(UARTx_S2)

39.2.7 UART控制寄存器3(UARTx_C3)

39.2.8 UART数据寄存器(UARTx_D)

39.2.9 UART地址匹配寄存器1(UARTx_MA1)

39.2.10 UART地址匹配寄存器2(UARTx_MA2)

39.2.11 UART控制寄存器4(UARTx_C4)

39.2.12 UART控制寄存器5(UARTx_C5)

39.3 功能描述

39.3.1 波特率发生器

39.3.2 发送器功能描述

39.3.2.1 发送中止与等待空闲

39.3.3 接收器功能描述

39.3.3.1 数据采样技术

39.3.3.2 接收器唤醒操作

39.3.3.2.1 空闲线唤醒

39.3.3.2.2 地址标志唤醒

39.3.3.2.3 匹配地址操作

39.3.4 额外的UART功能

39.3.4.1 8位、9位和10位数据模式

39.3.4.2 循环模式

39.3.4.3 单线操作

39.3.5 中断和状态标志

第40章 通用异步接收器/发送器(UART1与UART2)

40.1 简介

40.1.1 特征

40.1.2 操作模式

40.1.3 模块框图

40.2 寄存器定义

40.2.1 UART波特率寄存器高(UARTx_BDH)

40.2.2 UART波特率寄存器低(UARTx_BDL)

40.2.3 UART控制寄存器1(UARTx_C1)

40.2.4 UART控制寄存器2(UARTx_C2)

40.2.5 UART状态寄存器1(UARTx_S1)

40.2.6 UART状态寄存器2(UARTx_S2)

40.2.7 UART状态寄存器3(UARTx_C3)

40.2.8 UART数据寄存器3(UARTx_D)

40.2.9 UART控制寄存器4(UARTx_C4)

40.3 功能描述

40.3.1 波特率发生器

40.3.2 发送器功能描述

40.3.2.1 发送中止与等待空闲

40.3.3 接收器功能描述

40.3.3.1 数据采样技术

40.3.3.2 接收器唤醒操作

40.3.3.2.1 空闲线唤醒

40.3.3.2.2 地址标志唤醒

40.3.4 中断和状态标志

40.3.5 DMA操作

40.3.6 额外的UART功能

40.3.6.1 8位、9位数据模式

40.3.6.2 停止模式操作

40.3.6.3 循环模式

40.3.6.4 单线操作

第41章 通用I/O接口(GPIO)

41.1 引言

41.1.1 特性

41.1.2 操作模式

41.1.3 GPIO引脚描述

41.1.3.1 引脚描述详情

41.2 内存映射与寄存器定义

41.3.1 端口数据输出寄存器(GPIOx_PDOR)

41.3.2 端口输出置1寄存器(GPIOx_PSOR)

41.3.3 端口输出清0寄存器(GPIOx_PCOR)

41.3.4 端口输出取反寄存器(GPIOx_PTOR)

41.3.5 端口数据输入寄存器(GPIOx_PDIR)

41.3.6 端口数据方向寄存器(GPIOx_PDDR)

41.4 功能描述

41.4.1 通用输入

41.4.2 通用输出

41.4.3 IOPORT

第42章 触摸感应输出(TSI)

42.1 引言

42.1.1 特点

42.1.2 运行模式

42.1.3 结构图

42.2 外部信号描述

42.2.1 TSI[15:0]

42.3 寄存器定义

42.3.1 通用控制和状态寄存器(TSIx_GENCS)

42.3.2 TSI_DATA寄存器(TSIx_DATA)

42.3.3 阈值寄存器(TSIx_TSHD)

42.4 功能描述

42.4.1 电容测量

42.4.1.1 TSI电极晶振

42.2.2.2 电极晶振和计数器控制

42.2.2.3 TSI参考晶振

42.4.2 TSI测量结果

42.4.3 使能TSI模块

42.4.4 软件和硬件触发模式

42.4.5 扫描次数

42.4.5 时钟设置

42.4.7 参考电压

42.4.8 电流源

42.4.9 扫描结束

42.4.10 超出范围中断

42.4.11 从低功耗模式中唤醒MCU

42.4.12 DMA功能支持

42.4.13 噪声检测模式

42.4.13.1 自动噪声模式

42.4.13.2 单阈值噪声模式

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc