D

C

B

A

5

5

4

3

2

1

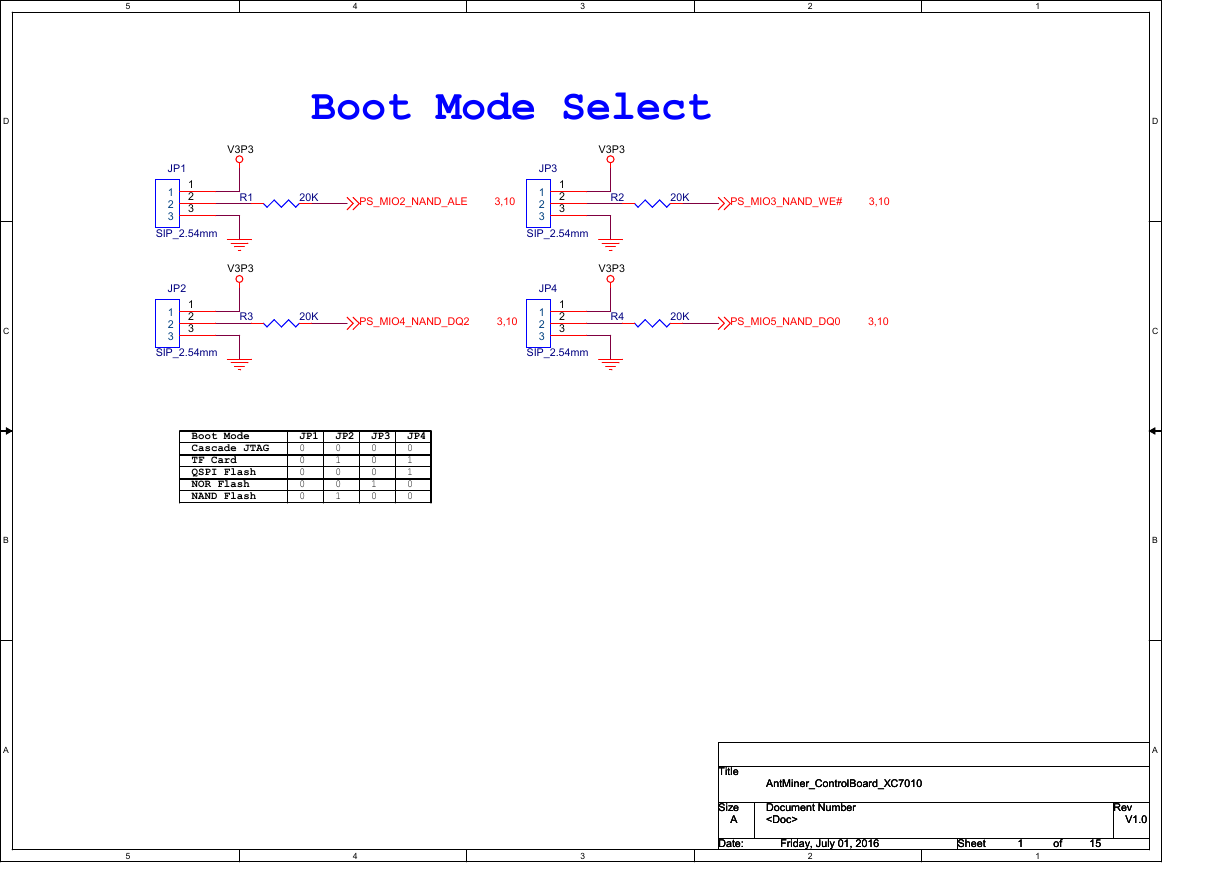

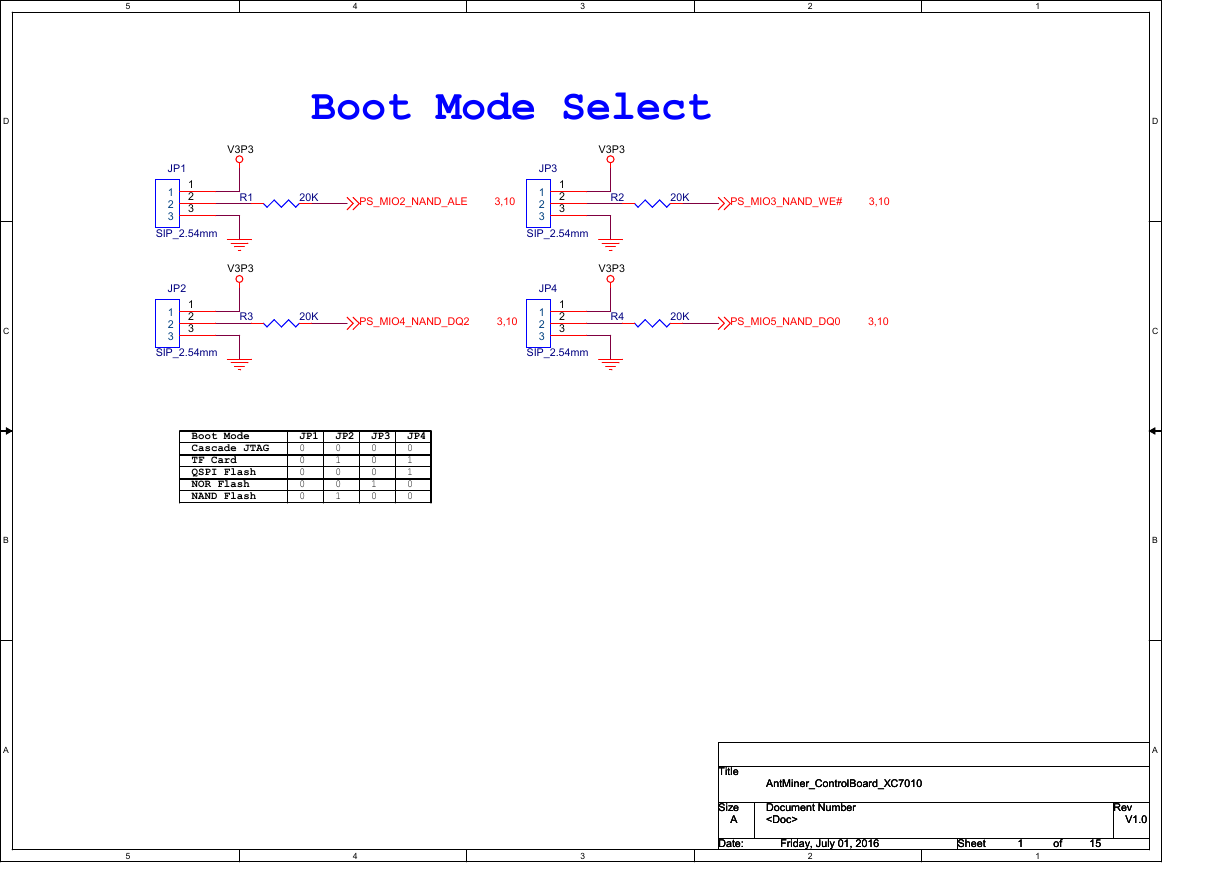

Boot Mode Select

V3P3

V3P3

R1

V3P3

R3

JP1

1

2

3

SIP_2.54mm

1

2

3

JP2

1

2

3

SIP_2.54mm

1

2

3

20K

20K

PS_MIO2_NAND_ALE

3,10

PS_MIO4_NAND_DQ2

3,10

JP3

1

2

3

SIP_2.54mm

1

2

3

JP4

1

2

3

SIP_2.54mm

1

2

3

R2

20K

PS_MIO3_NAND_WE#

3,10

V3P3

R4

20K

PS_MIO5_NAND_DQ0

3,10

D

C

B

A

Rev

Rev

Rev

V1.0

V1.0

V1.0

Sheet

Sheet

Sheet

1

1

1

1

of

of

of

15

15

15

Boot Mode

Cascade JTAG

TF Card

QSPI Flash

NOR Flash

NAND Flash

JP1

0

0

0

0

0

JP2

0

1

0

0

1

JP3

0

0

0

1

0

JP4

0

1

1

0

0

4

3

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

Document Number

Document Number

Document Number

Friday, July 01, 2016

Friday, July 01, 2016

Friday, July 01, 2016

2

�

D

C

B

A

5

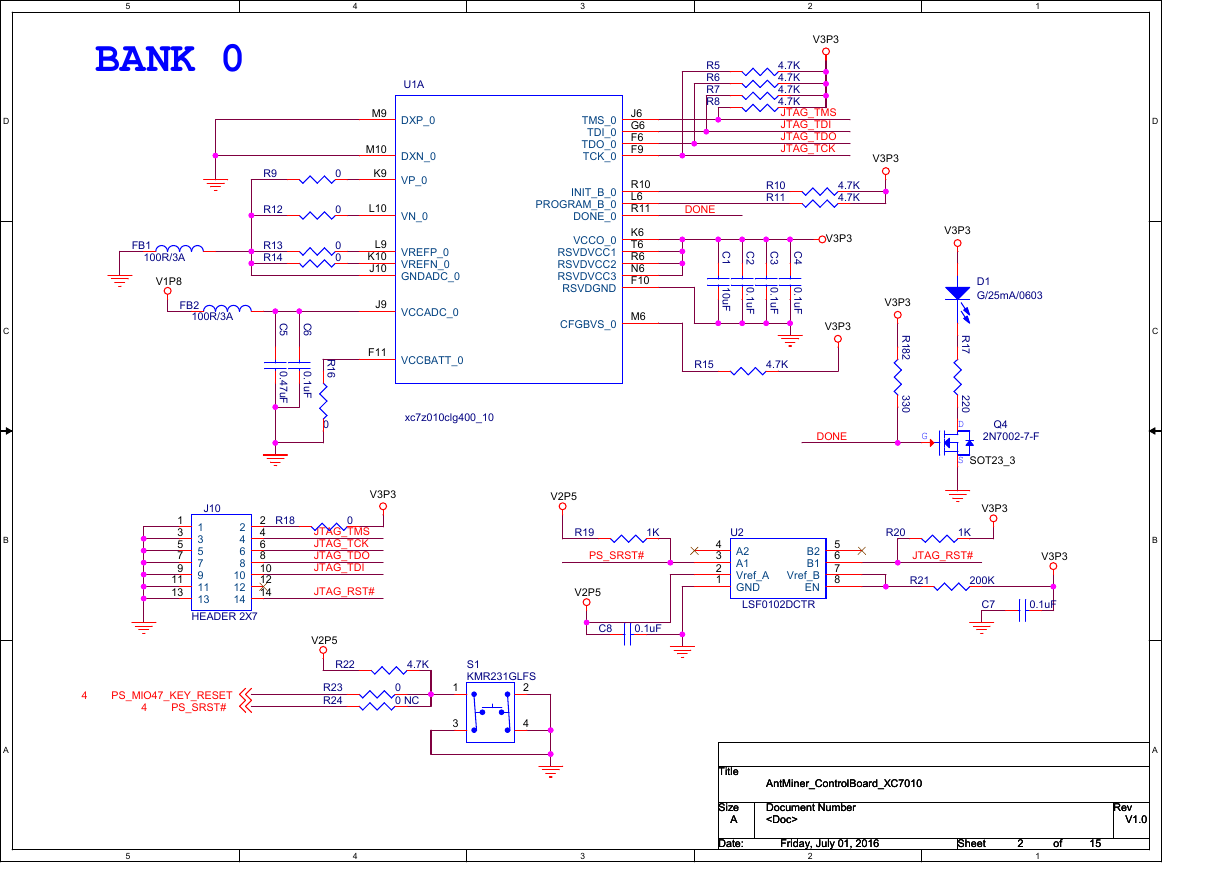

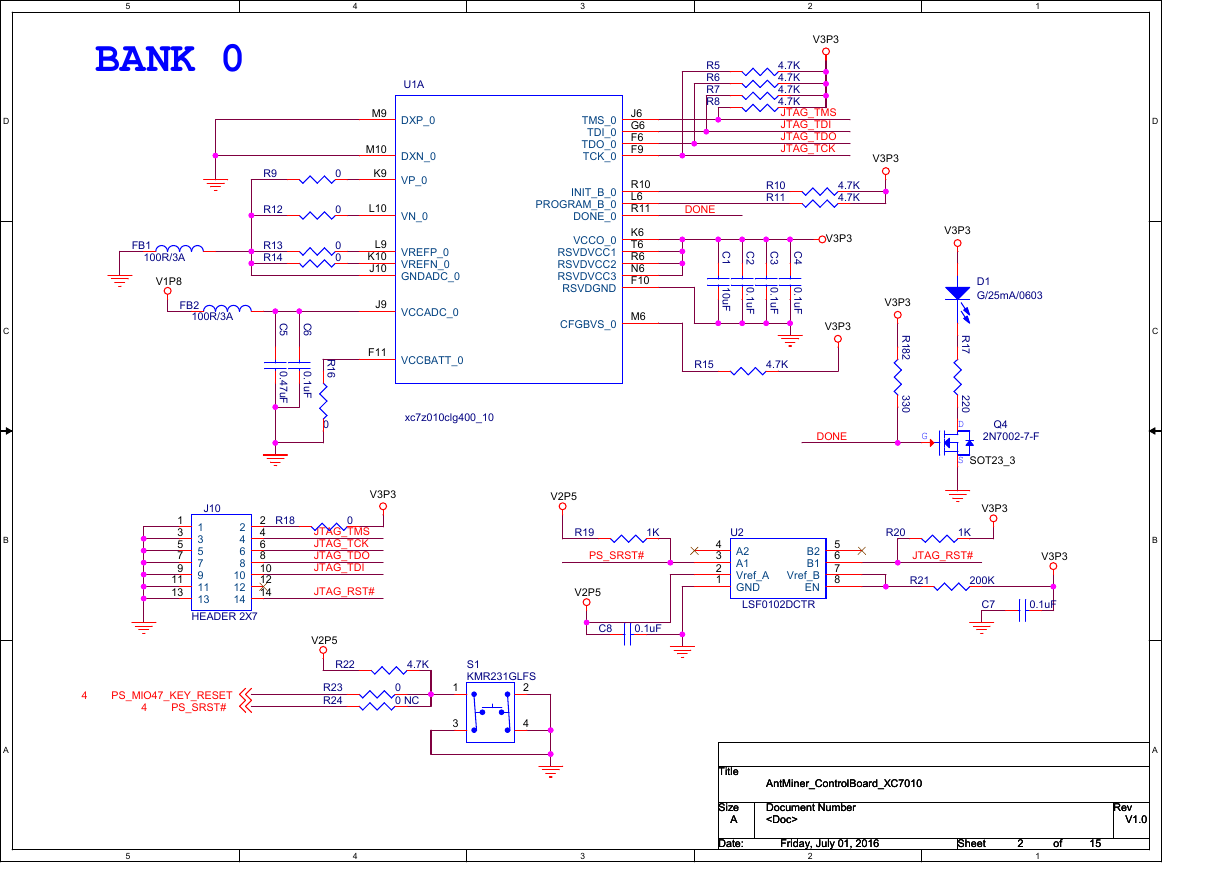

BANK 0

R9

R12

R13

R14

0

0

0

0

C

5

C

6

FB1100R/3A

V1P8

FB2100R/3A

4

3

U1A

DXP_0

DXN_0

VP_0

VN_0

VREFP_0

VREFN_0

GNDADC_0

VCCADC_0

VCCBATT_0

M9

M10

K9

L10

L9

K10

J10

J9

F11

J6

TMS_0

TDI_0 G6

F6

TDO_0

F9

TCK_0

INIT_B_0 R10

L6

PROGRAM_B_0

DONE_0 R11

K6

VCCO_0

T6

RSVDVCC1

RSVDVCC2 R6

RSVDVCC3 N6

RSVDGND F10

CFGBVS_0 M6

R5

R6

R7

R8

2

V3P3

4.7K

4.7K

4.7K

4.7K

JTAG_TMS

JTAG_TDI

JTAG_TDO

JTAG_TCK

R10

R11

DONE

C

1

C

2

C

3

C

4

1

0

u

F

0

0

0

.

.

.

1

u

F

1

u

F

1

u

F

R15

4.7K

4.7K

4.7K

V3P3

V3P3

DONE

1

V3P3

D1

G/25mA/0603

R

1

7

2

2

0

D

S

Q4

2N7002-7-F

SOT23_3

V3P3

V3P3

R

1

8

2

3

3

0

G

V2P5

R19

PS_SRST#

1K

V2P5

C8

0.1uF

R20

4

3

2

1

U2

5

B2

A2

6

B1

A1

7

Vref_B

Vref_A

EN 8

GND

LSF0102DCTR

V3P3

1K

JTAG_RST#

R21

200K

C7

V3P3

0.1uF

R

1

6

.

0

4

7

u

F

.

0

1

u

F

0

xc7z010clg400_10

V3P3

0

JTAG_TMS

JTAG_TCK

JTAG_TDO

JTAG_TDI

JTAG_RST#

V2P5

R22

R23

R24

4.7K

0

0 NC

S1KMR231GLFS

2

4

1

3

R18

1

3

5

7

9

11

13

J10

1

2

3

4

5

6

7

8

9

10

11

12

13

14

HEADER 2X7

2

4

6

8

10

12

14

4

PS_MIO47_KEY_RESET

PS_SRST#

4

5

4

3

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

Document Number

Document Number

Document Number

Friday, July 01, 2016

Friday, July 01, 2016

Friday, July 01, 2016

2

Rev

Rev

Rev

V1.0

V1.0

V1.0

Sheet

Sheet

Sheet

2

2

2

1

of

of

of

15

15

15

D

C

B

A

�

D

C

B

A

5

4

3

2

1

V3P3

C

9

.

0

1

u

F

4

2

R25

4.7K

1

3

Y1

VCC

ENA/DSI

GND

OUT

33..330MHz

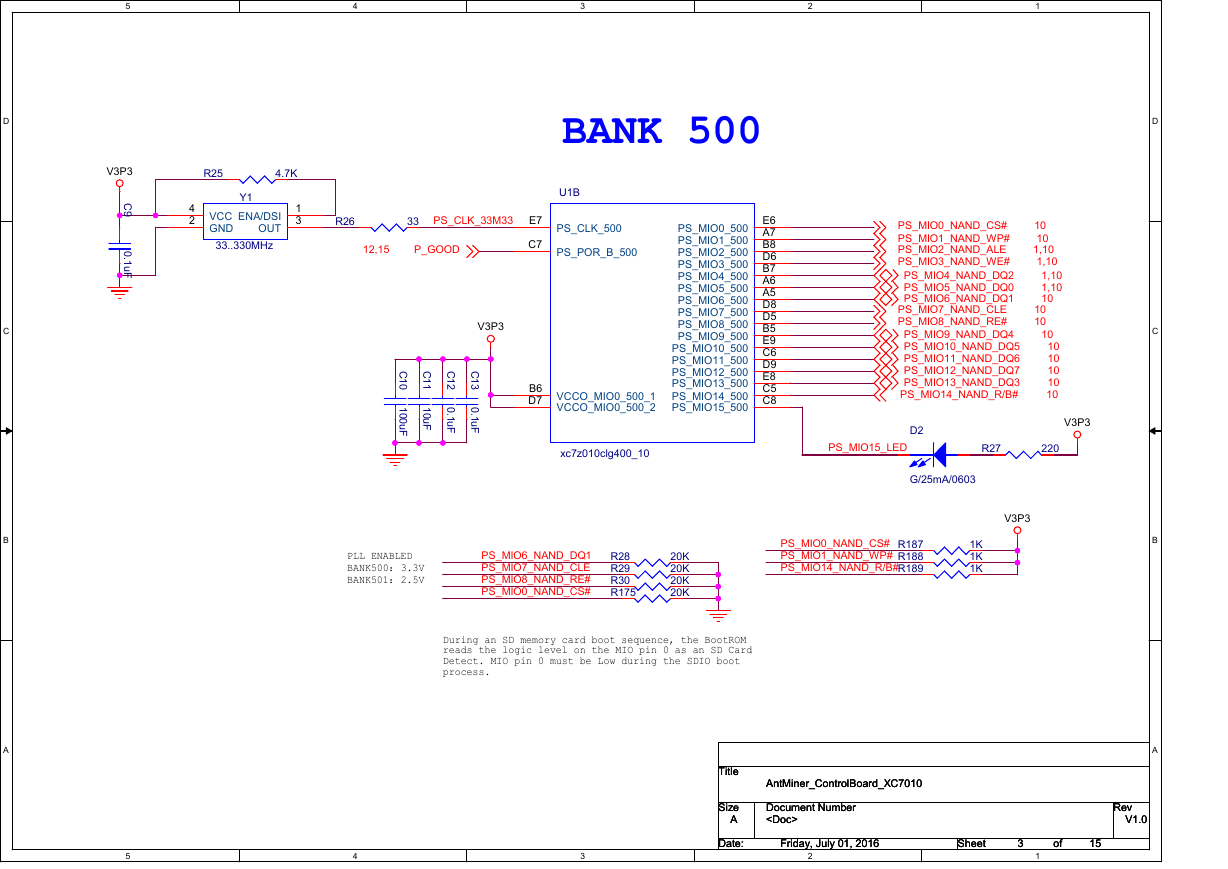

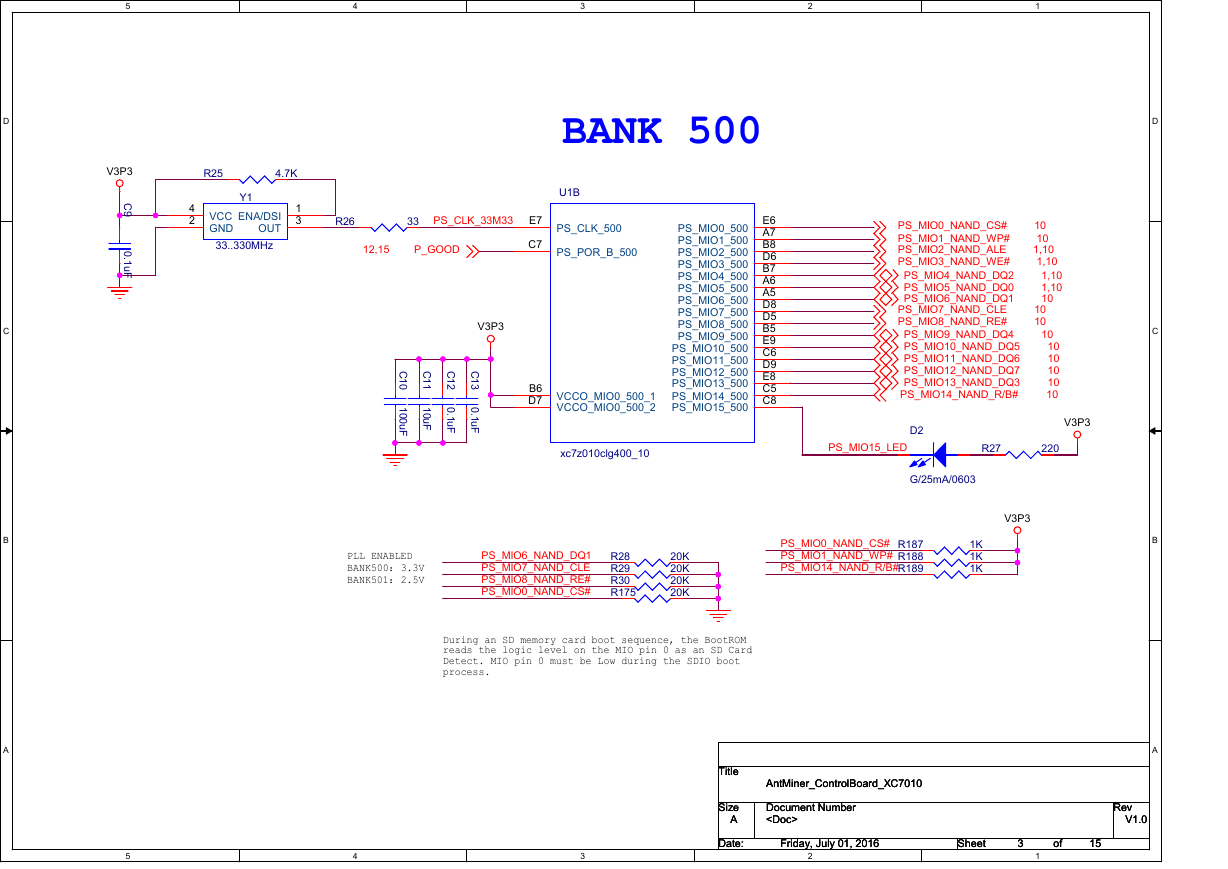

BANK 500

R26

PS_CLK_33M33

33

P_GOOD

E7

C7

12,15

U1B

PS_CLK_500

PS_POR_B_500

V3P3

C

1

0

C

1

1

C

1

2

C

1

3

1

0

0

u

F

1

0

u

F

0

0

.

.

1

u

F

1

u

F

B6

D7

VCCO_MIO0_500_1

VCCO_MIO0_500_2

xc7z010clg400_10

E6

PS_MIO0_500

A7

PS_MIO1_500

B8

PS_MIO2_500

PS_MIO3_500 D6

B7

PS_MIO4_500

A6

PS_MIO5_500

A5

PS_MIO6_500

PS_MIO7_500 D8

PS_MIO8_500 D5

B5

PS_MIO9_500

E9

PS_MIO10_500

PS_MIO11_500 C6

PS_MIO12_500 D9

E8

PS_MIO13_500

PS_MIO14_500 C5

PS_MIO15_500 C8

PS_MIO0_NAND_CS#

PS_MIO1_NAND_WP#

PS_MIO2_NAND_ALE

PS_MIO3_NAND_WE#

PS_MIO4_NAND_DQ2

PS_MIO5_NAND_DQ0

PS_MIO6_NAND_DQ1

PS_MIO7_NAND_CLE

PS_MIO8_NAND_RE#

PS_MIO9_NAND_DQ4

PS_MIO10_NAND_DQ5

PS_MIO11_NAND_DQ6

PS_MIO12_NAND_DQ7

PS_MIO13_NAND_DQ3

PS_MIO14_NAND_R/B#

D2

R27

PS_MIO15_LED

G/25mA/0603

V3P3

PS_MIO0_NAND_CS#

PS_MIO1_NAND_WP#

PS_MIO14_NAND_R/B#

R187

R188

R189

1K

1K

1K

PLL ENABLED

BANK500:3.3V

BANK501:2.5V

PS_MIO6_NAND_DQ1

PS_MIO7_NAND_CLE

PS_MIO8_NAND_RE#

PS_MIO0_NAND_CS#

R28

R29

R30

R175

20K

20K

20K

20K

During an SD memory card boot sequence, the BootROM

reads the logic level on the MIO pin 0 as an SD Card

Detect. MIO pin 0 must be Low during the SDIO boot

process.

10

10

1,10

1,10

1,10

1,10

10

10

10

10

10

10

10

10

10

220

V3P3

D

C

B

A

5

4

3

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

Document Number

Document Number

Document Number

Friday, July 01, 2016

Friday, July 01, 2016

Friday, July 01, 2016

2

Rev

Rev

Rev

V1.0

V1.0

V1.0

Sheet

Sheet

Sheet

3

3

3

1

of

of

of

15

15

15

�

D

C

B

A

5

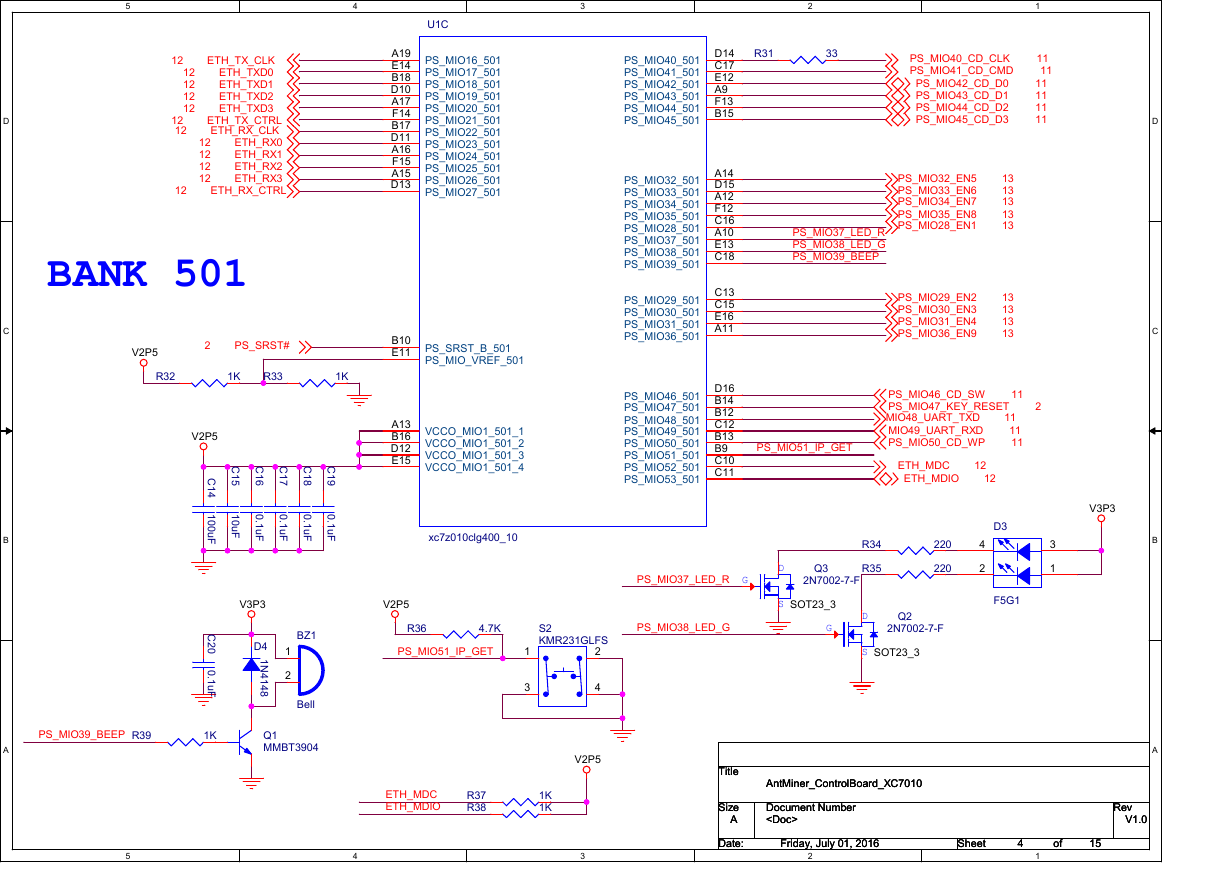

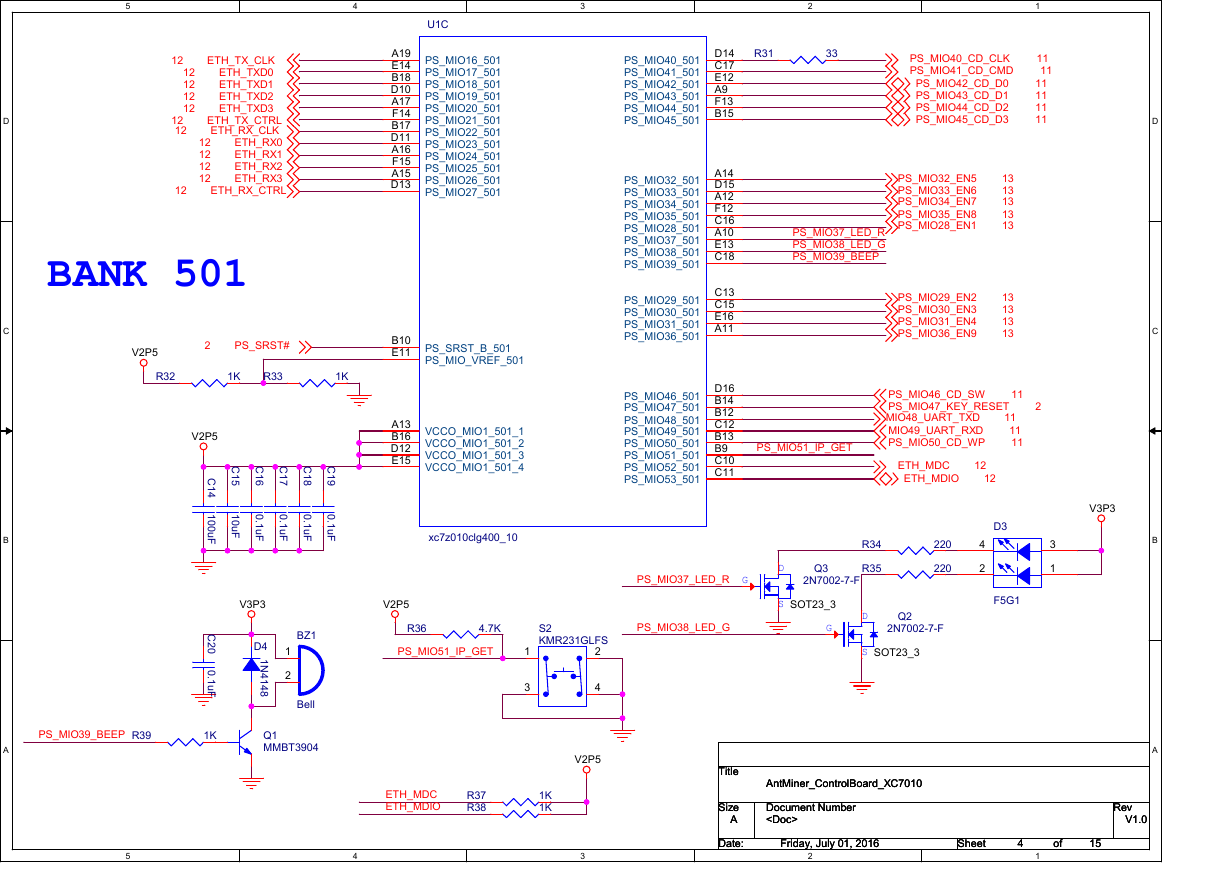

12

ETH_TX_CLK

ETH_TXD0

12

12

ETH_TXD1

12

ETH_TXD2

12 ETH_TX_CTRL

ETH_TXD3

12

ETH_RX_CLK

12

12

ETH_RX0

12

ETH_RX1

12

ETH_RX2

ETH_RX3

12ETH_RX_CTRL

12

BANK 501

V2P5

R32

2

PS_SRST#

R33

1K

1K

V2P5

C

1

5

C

1

6

C

1

7

C

1

8

C

1

9

C

1

4

1

0

0

u

F

1

0

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

V3P3

D4

BZ1

1

2

1

N

4

1

4

8

Bell

Q1MMBT3904

C

2

0

0

.

1

u

F

1K

PS_MIO39_BEEP

R39

5

4

4

A19

E14

B18

D10

A17

F14

B17

D11

A16

F15

A15

D13

B10

E11

A13

B16

D12

E15

U1C

PS_MIO16_501

PS_MIO17_501

PS_MIO18_501

PS_MIO19_501

PS_MIO20_501

PS_MIO21_501

PS_MIO22_501

PS_MIO23_501

PS_MIO24_501

PS_MIO25_501

PS_MIO26_501

PS_MIO27_501

PS_SRST_B_501

PS_MIO_VREF_501

VCCO_MIO1_501_1

VCCO_MIO1_501_2

VCCO_MIO1_501_3

VCCO_MIO1_501_4

xc7z010clg400_10

V2P5

R36

4.7K

PS_MIO51_IP_GET

S2KMR231GLFS

2

4

1

3

3

2

R31

33

PS_MIO37_LED_R

PS_MIO38_LED_G

PS_MIO39_BEEP

1

11

11

11

11

11

11

PS_MIO40_CD_CLK

PS_MIO41_CD_CMD

PS_MIO42_CD_D0

PS_MIO43_CD_D1

PS_MIO44_CD_D2

PS_MIO45_CD_D3

PS_MIO32_EN5

PS_MIO33_EN6

PS_MIO34_EN7

PS_MIO35_EN8

PS_MIO28_EN1

PS_MIO29_EN2

PS_MIO30_EN3

PS_MIO31_EN4

PS_MIO36_EN9

13

13

13

13

13

13

13

13

13

PS_MIO51_IP_GET

2

PS_MIO46_CD_SW

11

PS_MIO47_KEY_RESET

MIO48_UART_TXD

11

MIO49_UART_RXD

11

11

PS_MIO50_CD_WP

ETH_MDC

12

12

ETH_MDIO

PS_MIO40_501 D14

PS_MIO41_501 C17

E12

PS_MIO42_501

A9

PS_MIO43_501

F13

PS_MIO44_501

B15

PS_MIO45_501

A14

PS_MIO32_501

PS_MIO33_501 D15

A12

PS_MIO34_501

F12

PS_MIO35_501

PS_MIO28_501 C16

A10

PS_MIO37_501

E13

PS_MIO38_501

PS_MIO39_501 C18

PS_MIO29_501 C13

PS_MIO30_501 C15

E16

PS_MIO31_501

A11

PS_MIO36_501

PS_MIO46_501 D16

B14

PS_MIO47_501

B12

PS_MIO48_501

PS_MIO49_501 C12

B13

PS_MIO50_501

B9

PS_MIO51_501

PS_MIO52_501 C10

PS_MIO53_501 C11

PS_MIO37_LED_R

G

PS_MIO38_LED_G

D

S

Q3

2N7002-7-F

SOT23_3

G

R34

R35

220

220

D

S

Q2

2N7002-7-F

SOT23_3

V3P3

D3

4

2

F5G1

3

1

ETH_MDC

ETH_MDIO

R37

R38

1K

1K

V2P5

3

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

Document Number

Document Number

Document Number

Friday, July 01, 2016

Friday, July 01, 2016

Friday, July 01, 2016

2

Rev

Rev

Rev

V1.0

V1.0

V1.0

Sheet

Sheet

Sheet

4

4

4

1

of

of

of

15

15

15

D

C

B

A

�

D

C

B

A

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

5

9

9

9

9

9

9

9

9

DDR3_A0

DDR3_A1

DDR3_A2

DDR3_A3

DDR3_A4

DDR3_A5

DDR3_A6

DDR3_A7

DDR3_A8

DDR3_A9

DDR3_A10

DDR3_A11

DDR3_A12

DDR3_A13

DDR3_A14

DDR3_BA0

DDR3_BA1

DDR3_BA2

DDR3_CAS#

DDR3_RAS#

DDR3_WE#

DDR3_CS#

DDR3_CLK_P

DDR3_CLK_N

DDR3_CKE

DDR3_ODT

V1P5

V1P5

V1P5

4

R40

80.6

80.6

80.6

R41

R42

VREF_DDR3

C

2

1

C

2

2

0

0

.

.

1

u

F

1

u

F

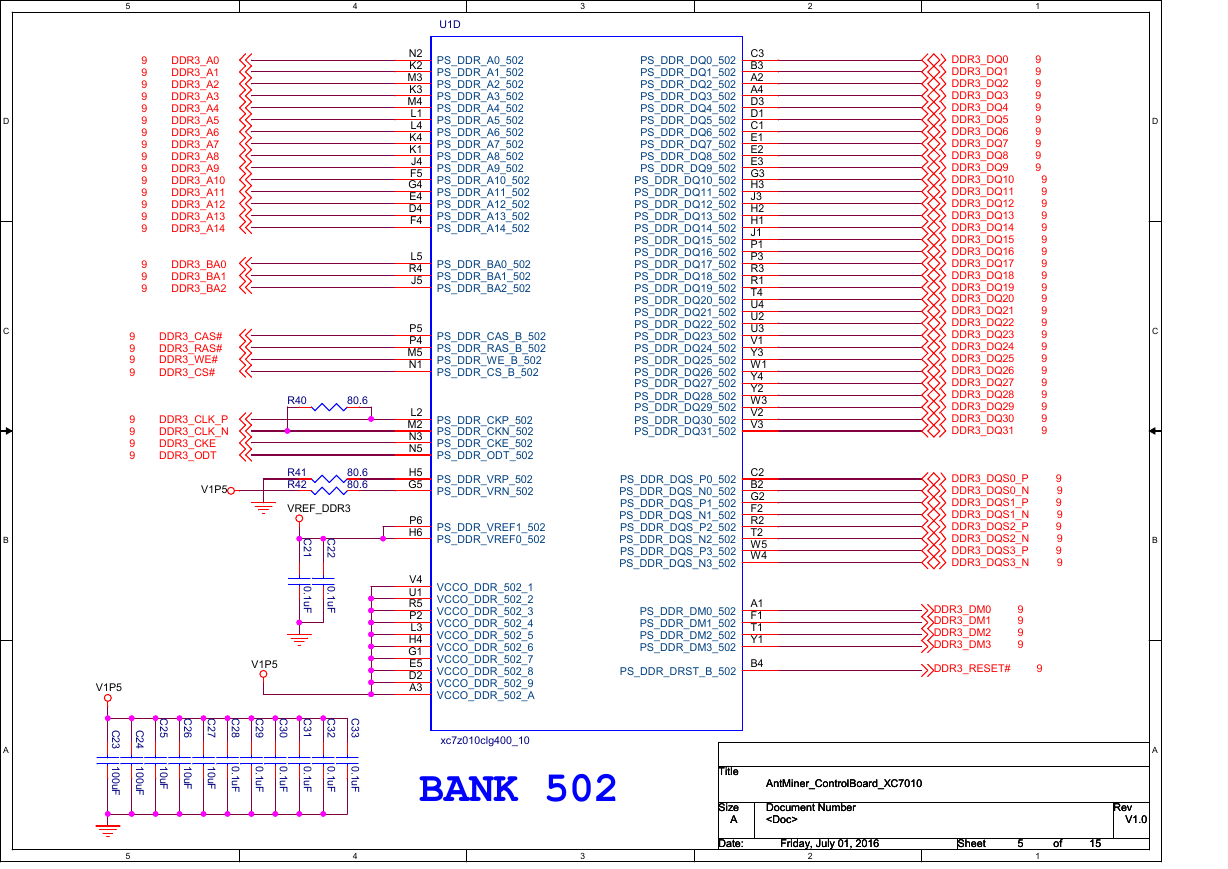

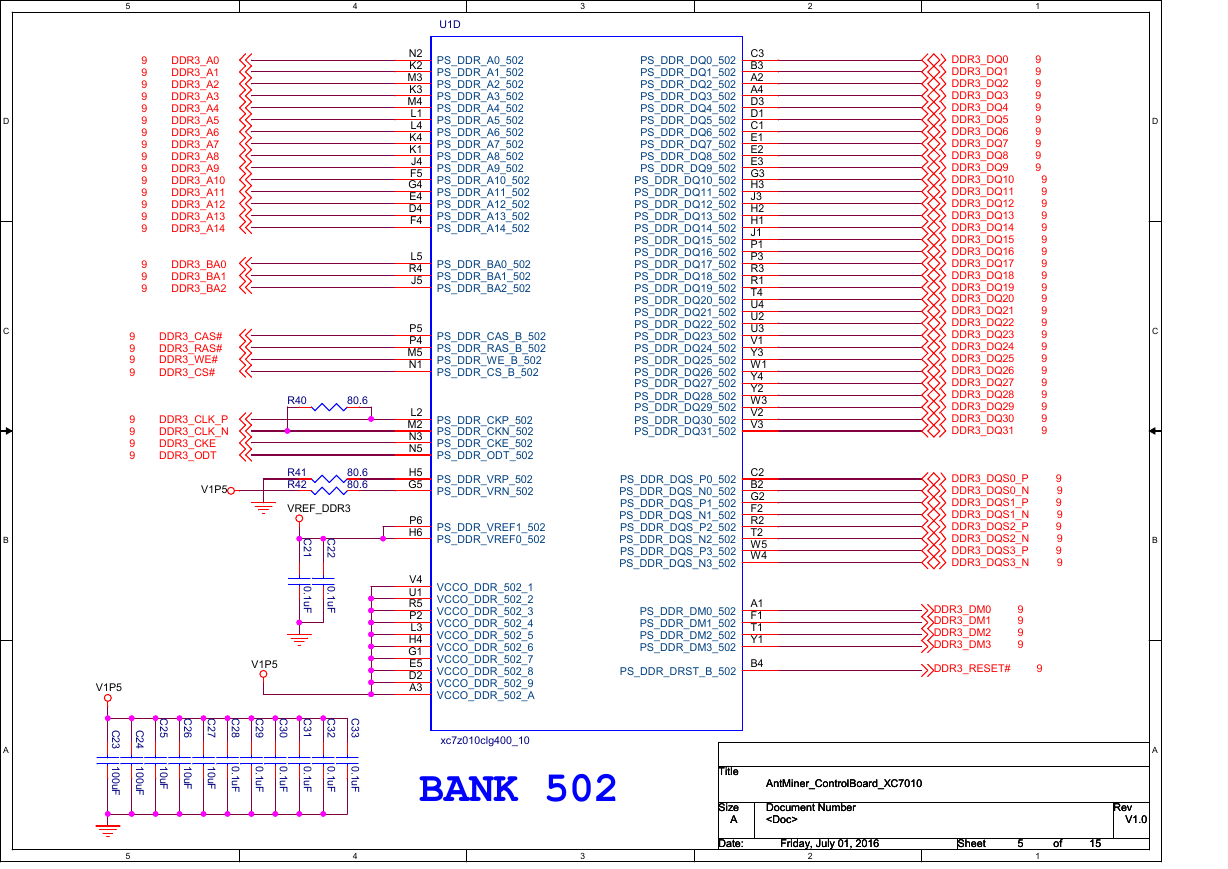

U1D

PS_DDR_A0_502

PS_DDR_A1_502

PS_DDR_A2_502

PS_DDR_A3_502

PS_DDR_A4_502

PS_DDR_A5_502

PS_DDR_A6_502

PS_DDR_A7_502

PS_DDR_A8_502

PS_DDR_A9_502

PS_DDR_A10_502

PS_DDR_A11_502

PS_DDR_A12_502

PS_DDR_A13_502

PS_DDR_A14_502

PS_DDR_BA0_502

PS_DDR_BA1_502

PS_DDR_BA2_502

PS_DDR_CAS_B_502

PS_DDR_RAS_B_502

PS_DDR_WE_B_502

PS_DDR_CS_B_502

PS_DDR_CKP_502

PS_DDR_CKN_502

PS_DDR_CKE_502

PS_DDR_ODT_502

PS_DDR_VRP_502

PS_DDR_VRN_502

PS_DDR_VREF1_502

PS_DDR_VREF0_502

VCCO_DDR_502_1

VCCO_DDR_502_2

VCCO_DDR_502_3

VCCO_DDR_502_4

VCCO_DDR_502_5

VCCO_DDR_502_6

VCCO_DDR_502_7

VCCO_DDR_502_8

VCCO_DDR_502_9

VCCO_DDR_502_A

N2

K2

M3

K3

M4

L1

L4

K4

K1

J4

F5

G4

E4

D4

F4

L5

R4

J5

P5

P4

M5

N1

L2

M2

N3

N5

H5

G5

P6

H6

V4

U1

R5

P2

L3

H4

G1

E5

D2

A3

3

2

PS_DDR_DQ0_502 C3

B3

PS_DDR_DQ1_502

A2

PS_DDR_DQ2_502

A4

PS_DDR_DQ3_502

PS_DDR_DQ4_502 D3

PS_DDR_DQ5_502 D1

PS_DDR_DQ6_502 C1

E1

PS_DDR_DQ7_502

E2

PS_DDR_DQ8_502

E3

PS_DDR_DQ9_502

PS_DDR_DQ10_502 G3

PS_DDR_DQ11_502 H3

J3

PS_DDR_DQ12_502

PS_DDR_DQ13_502 H2

PS_DDR_DQ14_502 H1

J1

PS_DDR_DQ15_502

P1

PS_DDR_DQ16_502

P3

PS_DDR_DQ17_502

PS_DDR_DQ18_502 R3

PS_DDR_DQ19_502 R1

T4

PS_DDR_DQ20_502

PS_DDR_DQ21_502 U4

PS_DDR_DQ22_502 U2

PS_DDR_DQ23_502 U3

V1

PS_DDR_DQ24_502

Y3

PS_DDR_DQ25_502

PS_DDR_DQ26_502 W1

Y4

PS_DDR_DQ27_502

Y2

PS_DDR_DQ28_502

PS_DDR_DQ29_502 W3

V2

PS_DDR_DQ30_502

V3

PS_DDR_DQ31_502

PS_DDR_DQS_P0_502 C2

B2

PS_DDR_DQS_N0_502

PS_DDR_DQS_P1_502 G2

F2

PS_DDR_DQS_N1_502

PS_DDR_DQS_P2_502 R2

T2

PS_DDR_DQS_N2_502

PS_DDR_DQS_P3_502 W5

PS_DDR_DQS_N3_502 W4

A1

F1

T1

Y1

B4

PS_DDR_DM0_502

PS_DDR_DM1_502

PS_DDR_DM2_502

PS_DDR_DM3_502

PS_DDR_DRST_B_502

C

2

5

C

2

6

C

2

7

C

2

8

C

2

9

C

3

0

C

3

1

C

3

2

C

3

3

C

2

3

C

2

4

1

0

0

u

F

1

0

0

u

F

1

0

u

F

1

0

u

F

1

0

u

F

0

0

0

0

0

0

.

.

.

1

u

F

1

u

F

1

u

F

1

u

F

1

u

F

1

u

F

.

.

.

xc7z010clg400_10

BANK 502

5

4

3

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

Document Number

Document Number

Document Number

Friday, July 01, 2016

Friday, July 01, 2016

Friday, July 01, 2016

2

1

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

DDR3_DQ0

DDR3_DQ1

DDR3_DQ2

DDR3_DQ3

DDR3_DQ4

DDR3_DQ5

DDR3_DQ6

DDR3_DQ7

DDR3_DQ8

DDR3_DQ9

DDR3_DQ10

DDR3_DQ11

DDR3_DQ12

DDR3_DQ13

DDR3_DQ14

DDR3_DQ15

DDR3_DQ16

DDR3_DQ17

DDR3_DQ18

DDR3_DQ19

DDR3_DQ20

DDR3_DQ21

DDR3_DQ22

DDR3_DQ23

DDR3_DQ24

DDR3_DQ25

DDR3_DQ26

DDR3_DQ27

DDR3_DQ28

DDR3_DQ29

DDR3_DQ30

DDR3_DQ31

DDR3_DQS0_P

DDR3_DQS0_N

DDR3_DQS1_P

DDR3_DQS1_N

DDR3_DQS2_P

DDR3_DQS2_N

DDR3_DQS3_P

DDR3_DQS3_N

9

9

9

9

9

9

9

9

DDR3_DM0

DDR3_DM1

DDR3_DM2

DDR3_DM3

DDR3_RESET#

9

9

9

9

9

D

C

B

A

Rev

Rev

Rev

V1.0

V1.0

V1.0

Sheet

Sheet

Sheet

5

5

5

1

of

of

of

15

15

15

�

5

4

2

1

3

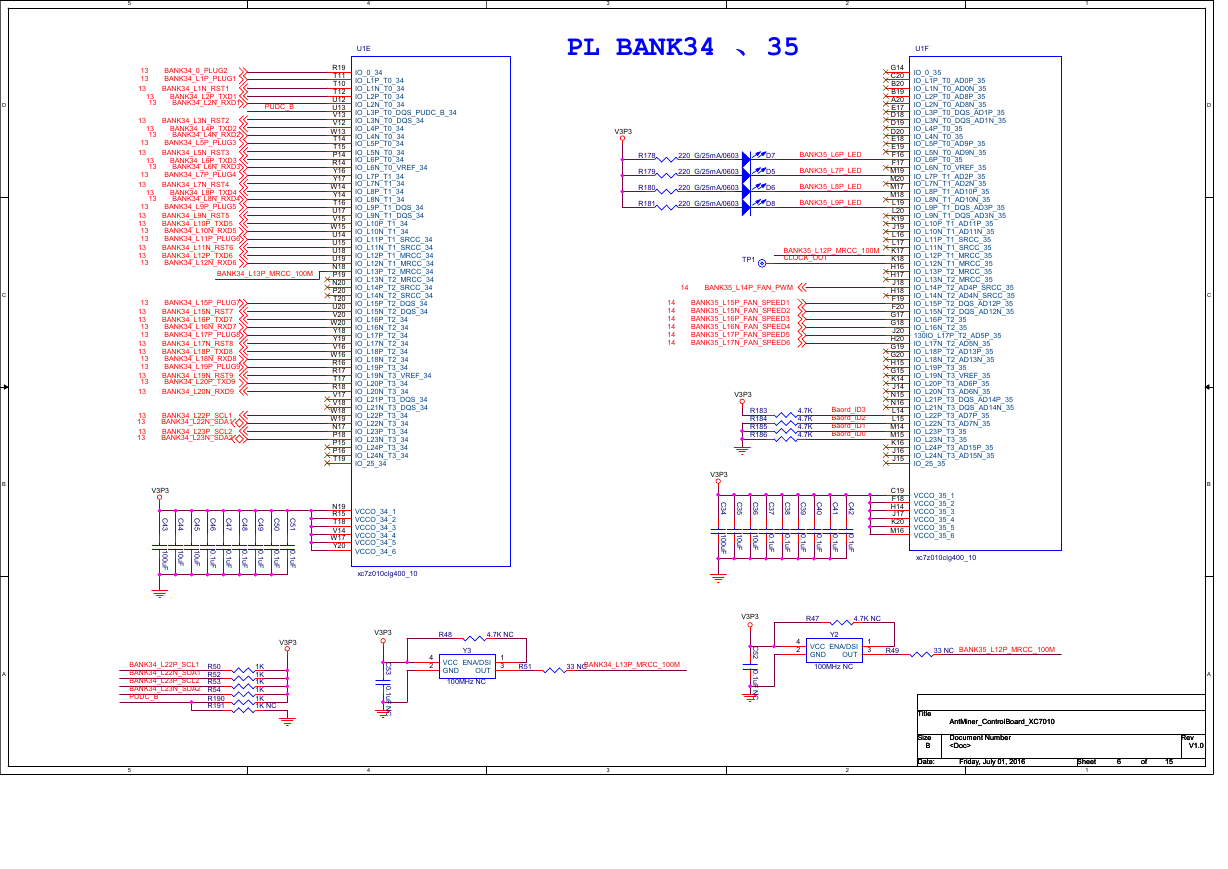

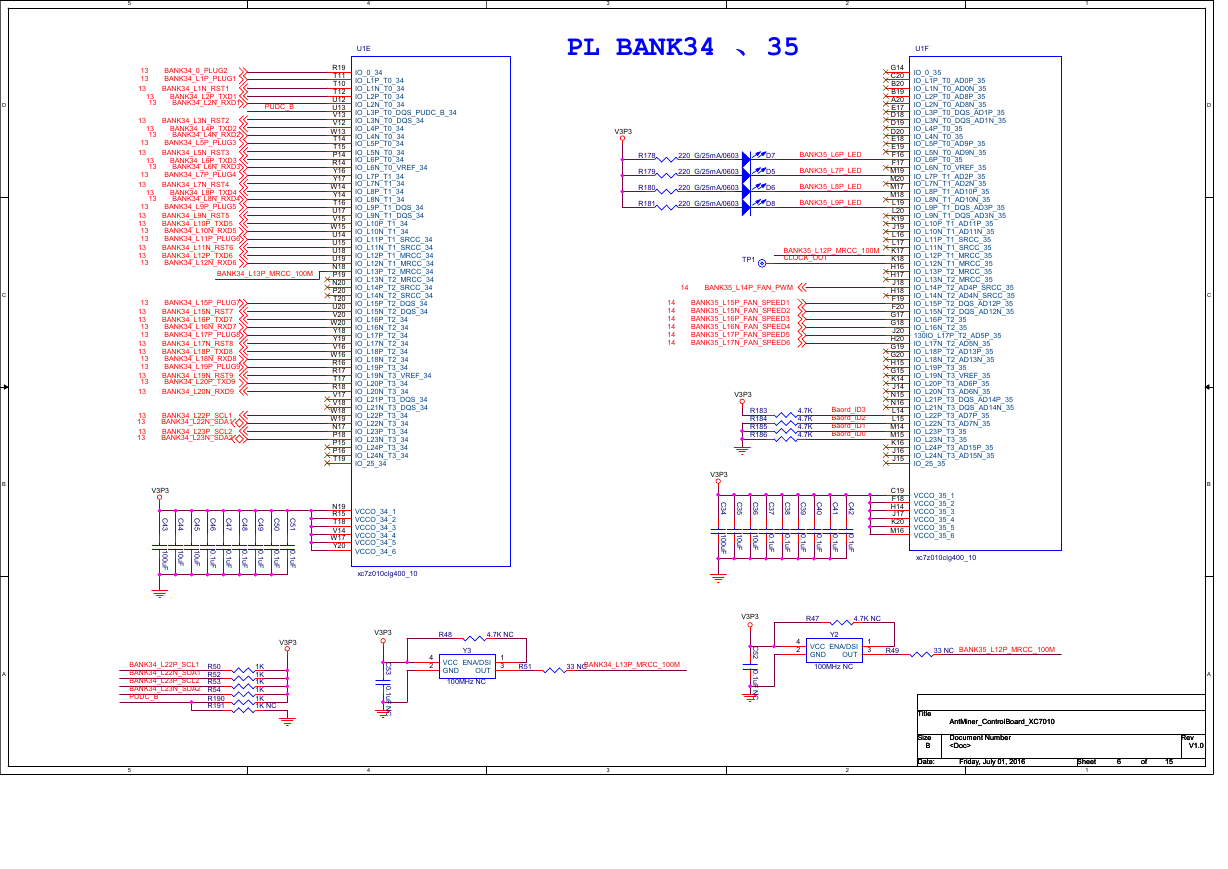

PL BANK34 、35

V3P3

R178

R179

R180

R181

220

220

220

220

G/25mA/0603

G/25mA/0603

G/25mA/0603

G/25mA/0603

D7

D5

D6

D8

BANK35_L6P_LED

BANK35_L7P_LED

BANK35_L8P_LED

BANK35_L9P_LED

TP1

BANK35_L12P_MRCC_100M

CLOCK_OUT

14

BANK35_L14P_FAN_PWM

BANK35_L15P_FAN_SPEED1

BANK35_L15N_FAN_SPEED2

BANK35_L16P_FAN_SPEED3

BANK35_L16N_FAN_SPEED4

BANK35_L17P_FAN_SPEED5

BANK35_L17N_FAN_SPEED6

14

14

14

14

14

14

V3P3

R183

R184

R185

R186

4.7K

4.7K

4.7K

4.7K

Baord_ID3

Baord_ID2

Baord_ID1

Baord_ID0

V3P3

C

3

4

C

3

5

C

3

6

C

3

7

C

3

8

C

3

9

C

4

0

C

4

1

C

4

2

1

0

0

u

F

1

0

u

F

1

0

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

G14

C20

B20

B19

A20

E17

D18

D19

D20

E18

E19

F16

F17

M19

M20

M17

M18

L19

L20

K19

J19

L16

L17

K17

K18

H16

H17

J18

H18

F19

F20

G17

G18

J20

H20

G19

G20

H15

G15

K14

J14

N15

N16

L14

L15

M14

M15

K16

J16

J15

C19

F18

H14

J17

K20

M16

U1F

IO_0_35

IO_L1P_T0_AD0P_35

IO_L1N_T0_AD0N_35

IO_L2P_T0_AD8P_35

IO_L2N_T0_AD8N_35

IO_L3P_T0_DQS_AD1P_35

IO_L3N_T0_DQS_AD1N_35

IO_L4P_T0_35

IO_L4N_T0_35

IO_L5P_T0_AD9P_35

IO_L5N_T0_AD9N_35

IO_L6P_T0_35

IO_L6N_T0_VREF_35

IO_L7P_T1_AD2P_35

IO_L7N_T1_AD2N_35

IO_L8P_T1_AD10P_35

IO_L8N_T1_AD10N_35

IO_L9P_T1_DQS_AD3P_35

IO_L9N_T1_DQS_AD3N_35

IO_L10P_T1_AD11P_35

IO_L10N_T1_AD11N_35

IO_L11P_T1_SRCC_35

IO_L11N_T1_SRCC_35

IO_L12P_T1_MRCC_35

IO_L12N_T1_MRCC_35

IO_L13P_T2_MRCC_35

IO_L13N_T2_MRCC_35

IO_L14P_T2_AD4P_SRCC_35

IO_L14N_T2_AD4N_SRCC_35

IO_L15P_T2_DQS_AD12P_35

IO_L15N_T2_DQS_AD12N_35

IO_L16P_T2_35

IO_L16N_T2_35

130IO_L17P_T2_AD5P_35

IO_L17N_T2_AD5N_35

IO_L18P_T2_AD13P_35

IO_L18N_T2_AD13N_35

IO_L19P_T3_35

IO_L19N_T3_VREF_35

IO_L20P_T3_AD6P_35

IO_L20N_T3_AD6N_35

IO_L21P_T3_DQS_AD14P_35

IO_L21N_T3_DQS_AD14N_35

IO_L22P_T3_AD7P_35

IO_L22N_T3_AD7N_35

IO_L23P_T3_35

IO_L23N_T3_35

IO_L24P_T3_AD15P_35

IO_L24N_T3_AD15N_35

IO_25_35

VCCO_35_1

VCCO_35_2

VCCO_35_3

VCCO_35_4

VCCO_35_5

VCCO_35_6

xc7z010clg400_10

D

C

B

A

R19

T11

T10

T12

U12

U13

V13

V12

W13

T14

T15

P14

R14

Y16

Y17

W14

Y14

T16

U17

V15

W15

U14

U15

U18

U19

N18

P19

N20

P20

T20

U20

V20

W20

Y18

Y19

V16

W16

R16

R17

T17

R18

V17

V18

W18

W19

N17

P18

P15

P16

T19

N19

R15

T18

V14

W17

Y20

PUDC_B

BANK34_L13P_MRCC_100M

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

BANK34_0_PLUG2

BANK34_L1P_PLUG1

BANK34_L1N_RST1

BANK34_L2P_TXD1

BANK34_L2N_RXD1

BANK34_L3N_RST2

BANK34_L4P_TXD2

BANK34_L4N_RXD2

BANK34_L5P_PLUG3

BANK34_L5N_RST3

BANK34_L6P_TXD3

BANK34_L6N_RXD3

BANK34_L7P_PLUG4

BANK34_L7N_RST4

BANK34_L8P_TXD4

BANK34_L8N_RXD4

BANK34_L9P_PLUG5

BANK34_L9N_RST5

BANK34_L10P_TXD5

BANK34_L10N_RXD5

BANK34_L11P_PLUG6

BANK34_L11N_RST6

BANK34_L12P_TXD6

BANK34_L12N_RXD6

BANK34_L15P_PLUG7

BANK34_L15N_RST7

BANK34_L16P_TXD7

BANK34_L16N_RXD7

BANK34_L17P_PLUG8

BANK34_L17N_RST8

BANK34_L18P_TXD8

BANK34_L18N_RXD8

BANK34_L19P_PLUG9

BANK34_L19N_RST9

BANK34_L20P_TXD9

BANK34_L20N_RXD9

BANK34_L22P_SCL1

BANK34_L22N_SDA1

BANK34_L23P_SCL2

BANK34_L23N_SDA2

V3P3

C

4

3

C

4

4

C

4

5

C

4

6

C

4

7

C

4

8

C

4

9

C

5

0

C

5

1

1

0

0

u

F

1

0

u

F

1

0

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

V3P3

BANK34_L22P_SCL1

BANK34_L22N_SDA1

BANK34_L23P_SCL2

BANK34_L23N_SDA2

PUDC_B

R50

R52

R53

R54

R190

R191

1K

1K

1K

1K

1K

1K NC

U1E

IO_0_34

IO_L1P_T0_34

IO_L1N_T0_34

IO_L2P_T0_34

IO_L2N_T0_34

IO_L3P_T0_DQS_PUDC_B_34

IO_L3N_T0_DQS_34

IO_L4P_T0_34

IO_L4N_T0_34

IO_L5P_T0_34

IO_L5N_T0_34

IO_L6P_T0_34

IO_L6N_T0_VREF_34

IO_L7P_T1_34

IO_L7N_T1_34

IO_L8P_T1_34

IO_L8N_T1_34

IO_L9P_T1_DQS_34

IO_L9N_T1_DQS_34

IO_L10P_T1_34

IO_L10N_T1_34

IO_L11P_T1_SRCC_34

IO_L11N_T1_SRCC_34

IO_L12P_T1_MRCC_34

IO_L12N_T1_MRCC_34

IO_L13P_T2_MRCC_34

IO_L13N_T2_MRCC_34

IO_L14P_T2_SRCC_34

IO_L14N_T2_SRCC_34

IO_L15P_T2_DQS_34

IO_L15N_T2_DQS_34

IO_L16P_T2_34

IO_L16N_T2_34

IO_L17P_T2_34

IO_L17N_T2_34

IO_L18P_T2_34

IO_L18N_T2_34

IO_L19P_T3_34

IO_L19N_T3_VREF_34

IO_L20P_T3_34

IO_L20N_T3_34

IO_L21P_T3_DQS_34

IO_L21N_T3_DQS_34

IO_L22P_T3_34

IO_L22N_T3_34

IO_L23P_T3_34

IO_L23N_T3_34

IO_L24P_T3_34

IO_L24N_T3_34

IO_25_34

VCCO_34_1

VCCO_34_2

VCCO_34_3

VCCO_34_4

VCCO_34_5

VCCO_34_6

xc7z010clg400_10

V3P3

C

5

3

4

2

.

0

1

u

F

N

C

R48

4.7K NC

Y3

ENA/DSI

VCC

GND

OUT

100MHz NC

1

3

R51

33 NC

BANK34_L13P_MRCC_100M

V3P3

C

5

2

4

2

.

0

1

u

F

N

C

R47

4.7K NC

Y2

ENA/DSI

VCC

GND

OUT

100MHz NC

1

3

R49

33 NC

BANK35_L12P_MRCC_100M

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

Document Number

Document Number

Document Number

Friday, July 01, 2016

Friday, July 01, 2016

Friday, July 01, 2016

Rev

Rev

Rev

V1.0

V1.0

V1.0

Sheet

Sheet

Sheet

1

6

6

6

of

of

of

15

15

15

5

4

3

2

D

C

B

A

�

D

C

B

A

5

5

3

2

1

4

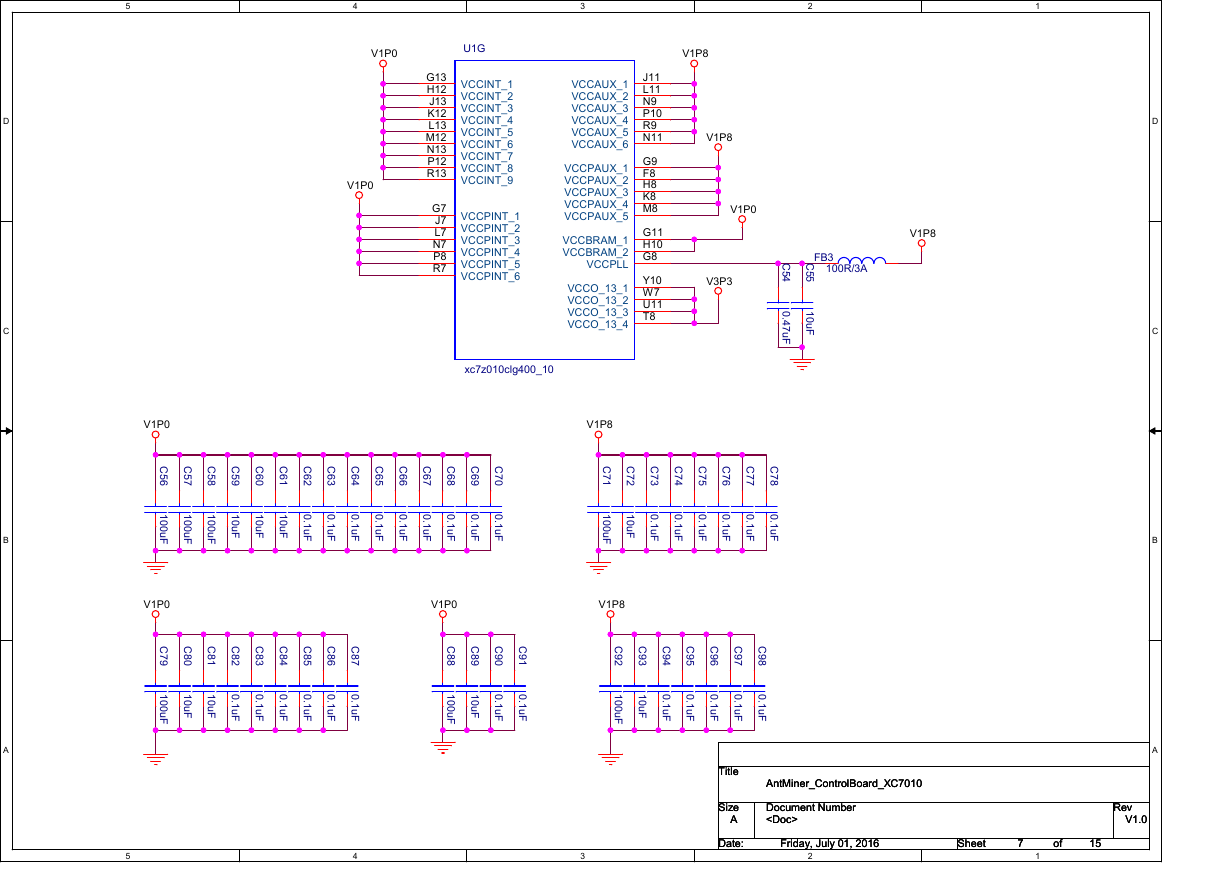

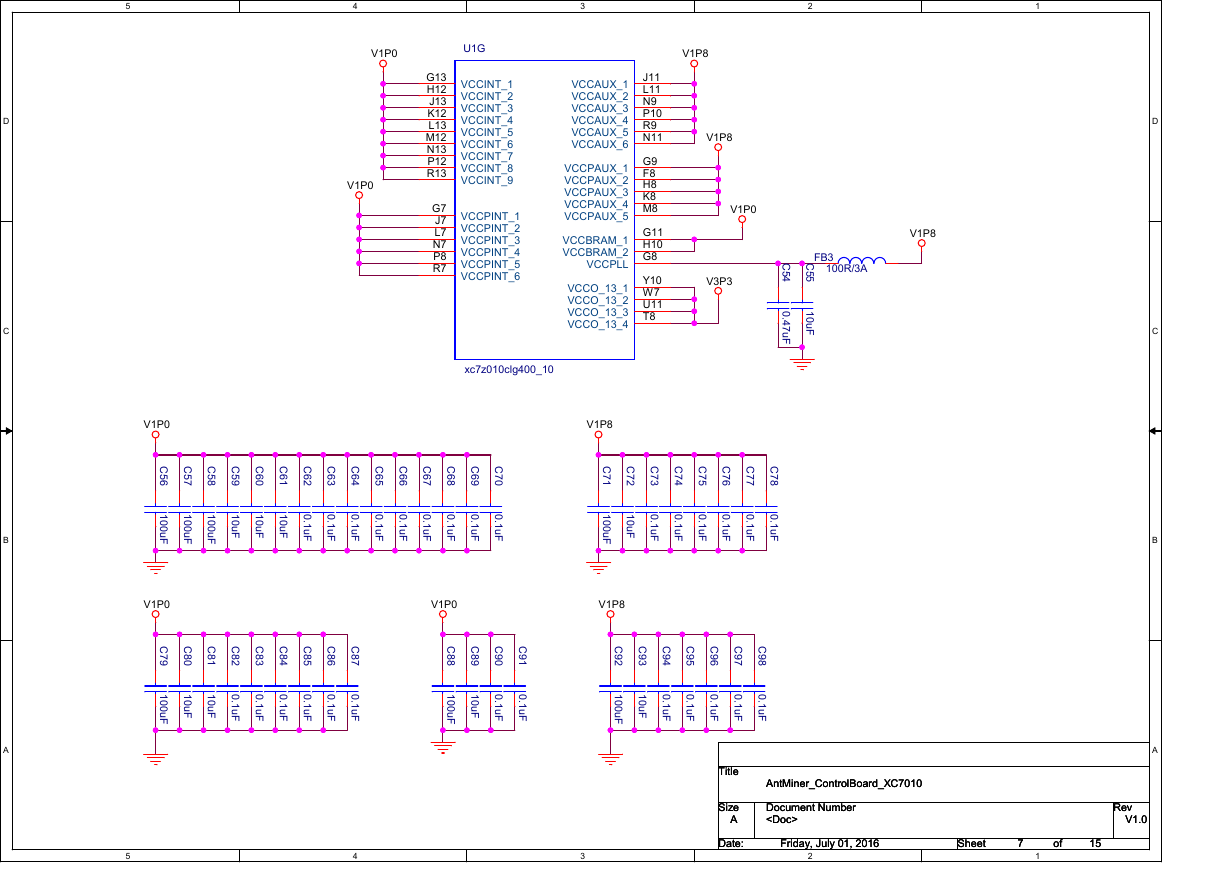

V1P0

V1P0

U1G

VCCINT_1

VCCINT_2

VCCINT_3

VCCINT_4

VCCINT_5

VCCINT_6

VCCINT_7

VCCINT_8

VCCINT_9

VCCPINT_1

VCCPINT_2

VCCPINT_3

VCCPINT_4

VCCPINT_5

VCCPINT_6

G13

H12

J13

K12

L13

M12

N13

P12

R13

G7

J7

L7

N7

P8

R7

V1P8

V1P8

V1P0

V3P3

J11

VCCAUX_1

L11

VCCAUX_2

VCCAUX_3 N9

P10

VCCAUX_4

VCCAUX_5 R9

VCCAUX_6 N11

VCCPAUX_1 G9

F8

VCCPAUX_2

VCCPAUX_3 H8

K8

VCCPAUX_4

VCCPAUX_5 M8

VCCBRAM_1 G11

VCCBRAM_2 H10

VCCPLL G8

Y10

VCCO_13_1

VCCO_13_2 W7

VCCO_13_3 U11

T8

VCCO_13_4

V1P8

FB3100R/3A

C

5

4

C

5

5

1

0

u

F

.

0

4

7

u

F

V1P0

xc7z010clg400_10

V1P8

C

5

6

C

5

7

C

5

8

C

5

9

C

6

0

C

6

1

C

6

2

C

6

3

C

6

4

C

6

5

C

6

6

C

6

7

C

6

8

C

6

9

C

7

0

C

7

1

C

7

2

C

7

3

C

7

4

C

7

5

C

7

6

C

7

7

C

7

8

1

0

0

u

F

1

0

0

u

F

1

0

0

u

F

1

0

u

F

1

0

u

F

1

0

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

1

0

0

u

F

1

0

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

V1P0

V1P0

V1P8

C

7

9

C

8

0

C

8

1

C

8

2

C

8

3

C

8

4

C

8

5

C

8

6

C

8

7

C

8

8

C

8

9

C

9

0

C

9

1

C

9

2

C

9

3

C

9

4

C

9

5

C

9

6

C

9

7

C

9

8

1

0

0

u

F

1

0

u

F

1

0

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

1

0

0

u

F

1

0

u

F

.

0

1

u

F

.

0

1

u

F

1

0

0

u

F

1

0

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

.

0

1

u

F

4

3

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

Document Number

Document Number

Document Number

Friday, July 01, 2016

Friday, July 01, 2016

Friday, July 01, 2016

2

D

C

B

A

Rev

Rev

Rev

V1.0

V1.0

V1.0

Sheet

Sheet

Sheet

7

7

7

1

of

of

of

15

15

15

�

D

C

B

A

5

5

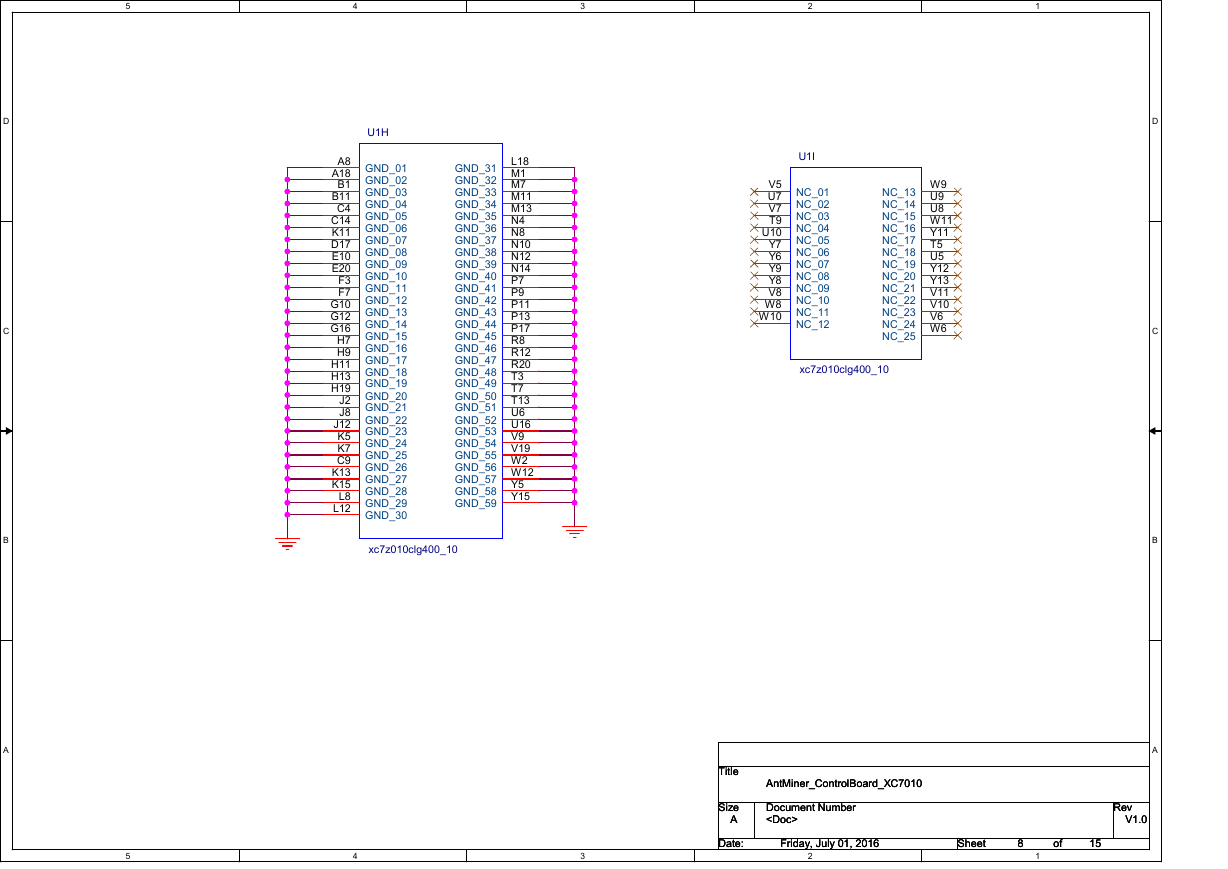

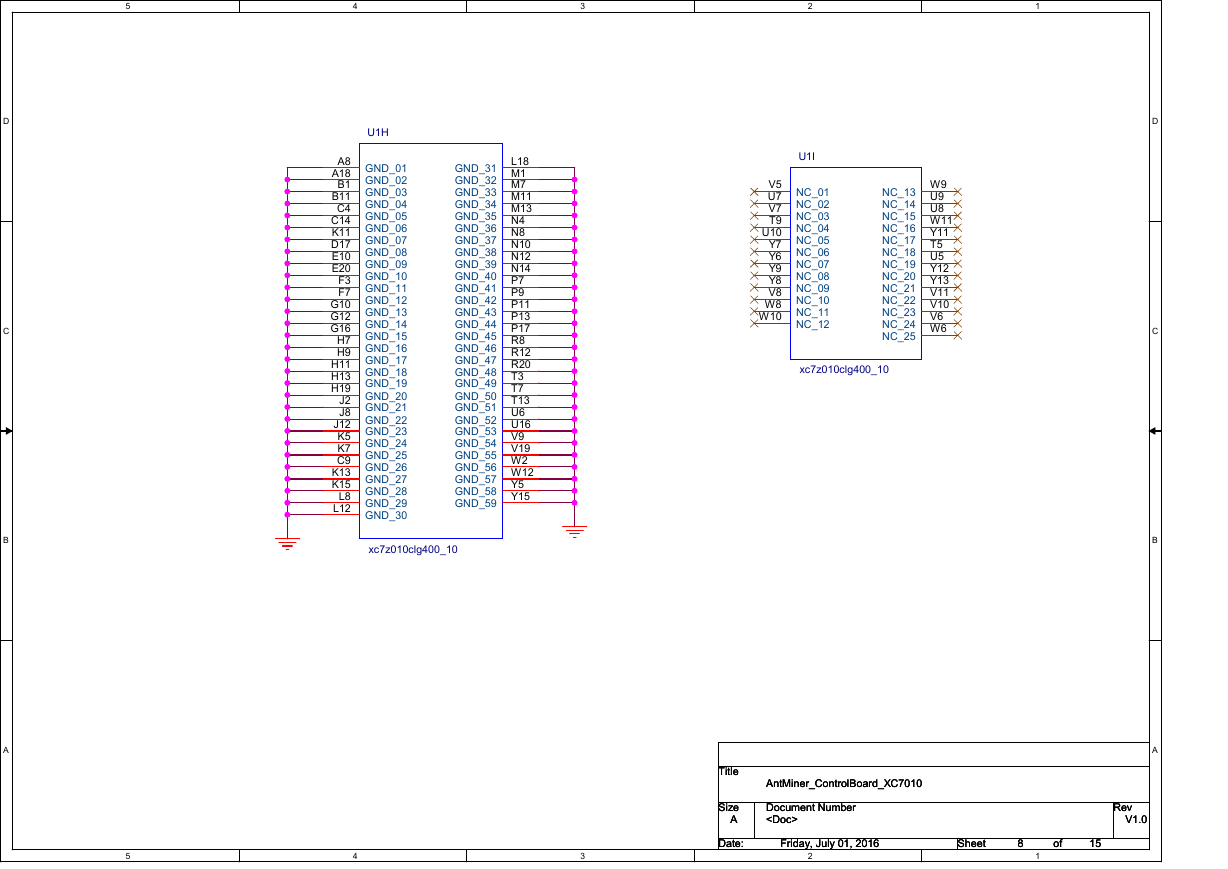

U1H

GND_01

GND_02

GND_03

GND_04

GND_05

GND_06

GND_07

GND_08

GND_09

GND_10

GND_11

GND_12

GND_13

GND_14

GND_15

GND_16

GND_17

GND_18

GND_19

GND_20

GND_21

GND_22

GND_23

GND_24

GND_25

GND_26

GND_27

GND_28

GND_29

GND_30

xc7z010clg400_10

L18

GND_31

GND_32 M1

GND_33 M7

GND_34 M11

GND_35 M13

GND_36 N4

GND_37 N8

GND_38 N10

GND_39 N12

GND_40 N14

P7

GND_41

P9

GND_42

P11

GND_43

P13

GND_44

P17

GND_45

GND_46 R8

GND_47 R12

GND_48 R20

T3

GND_49

T7

GND_50

T13

GND_51

GND_52 U6

GND_53 U16

V9

GND_54

V19

GND_55

GND_56 W2

GND_57 W12

Y5

GND_58

Y15

GND_59

A8

A18

B1

B11

C4

C14

K11

D17

E10

E20

F3

F7

G10

G12

G16

H7

H9

H11

H13

H19

J2

J8

J12

K5

K7

C9

K13

K15

L8

L12

4

4

3

3

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

2

1

U1I

NC_01

NC_02

NC_03

NC_04

NC_05

NC_06

NC_07

NC_08

NC_09

NC_10

NC_11

NC_12

V5

U7

V7

T9

U10

Y7

Y6

Y9

Y8

V8

W8

W10

NC_13 W9

NC_14 U9

NC_15 U8

NC_16 W11

Y11

NC_17

T5

NC_18

NC_19 U5

Y12

NC_20

Y13

NC_21

V11

NC_22

V10

NC_23

V6

NC_24

NC_25 W6

xc7z010clg400_10

D

C

B

A

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

AntMiner_ControlBoard_XC7010

Document Number

Document Number

Document Number

Friday, July 01, 2016

Friday, July 01, 2016

Friday, July 01, 2016

2

Rev

Rev

Rev

V1.0

V1.0

V1.0

Sheet

Sheet

Sheet

8

8

8

1

of

of

of

15

15

15

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc