摘要

ALDEC 公司的 HES-DVM 提供了一个通用的完

整的高效、全面的基于 FPGA 的硬件加速平台。

这对于大规模设计的高速仿真/模拟具有关键

HES-DVM 硬件加速培训

资料

基于 HES-DVM 2017.09. 6719 版本

性提升作用。

吴文显/Wenson Wu

wenson.wu@aldec.com.cn

�

目录

第 1 章 概述 ...................................................................................................................................................2

1.1. HES-DVM 简介 .............................................................................................................................2

HES-DVM——硬件加速仿真 .....................................................................................2

1.1.1.

1.1.2.

HES-DVM——混合 Co-Emulation、在线仿真(ICE)和虚拟平台 QEMU 软

硬件协同验证 .....................................................................................................................................4

1.1.3.

HES-DVM——原型验证(Prototyping)和多片 FPGA 分割(Multi-FPGA

Partitioning) .....................................................................................................................................6

1.2. HES-DVM 验证环境 ....................................................................................................................7

第 2 章 硬件加速仿真设计流程 ..............................................................................................................9

2.1. 硬件仿真加速概述 .......................................................................................................................9

2.2. 前期准备 ..........................................................................................................................................9

2.3. 设计工具流程 ............................................................................................................................. 10

Active-HDL/Riviera-PRO 工程准备 ....................................................................... 10

2.3.1.

2.3.2.

HES-DVM 硬件加速管理流程 ................................................................................. 10

2.3.3. 运行硬件加速仿真 ...................................................................................................... 18

第 3 章 设计分割(Partitioning)流程 ............................................................................................. 22

3.1. 设计分割(Partitioning)概述 ............................................................................................. 22

3.2. 设计分割流程和案例................................................................................................................ 23

3.2.1. 设计分割流程 ................................................................................................................ 23

3.2.2. 分割案例 ......................................................................................................................... 24

第 4 章 提问&回答 ................................................................................................................................... 39

第 5 章 附录 ................................................................................................................................................ 40

www.aldec.com

第1页

�

第1章 概述

1.1. HES-DVM 简介

1.1.1. HES-DVM——硬件加速仿真

HES™(Hardware Emulation Solution)是一套具有专利技术的事务级(transaction-

level)硬件验证平台,作为一种实用、灵活的硬件验证平台,能够为片上系统(SoC)的硬

件加速仿真,软硬件(HW/SW)协同验证,软件验证,电子系统级协同仿真和虚拟原型验证

提供了统一的验证平台。HES 结合了实用性,高速度和低功耗等优点,实现了设计的自动编

译,同时集成了标准测试接口以及业界领先的软硬件调试工具,将现有的 ASIC 原型验证通

过动态硬件仿真无缝实现。

仿真加速模式

HES 能将仿真速度提高十倍以上,并能装备到业界领导厂商(Aldec,Cadence,Mentor-

Graphics and synopsys)常用的 RTL 仿真软件上,实现功能仿真加速。加速模式结合了强

大的 HDL 仿真器调试能力和 FPGA 原型验证板的高速度,部分占用 CPU 资源较大的设计将被

下载到硬件电路板,同时由 HDL 仿真器 testbench 来控制整个仿真。HES 将从硬件电路板选

择好的测试点植入 HDL 仿真器的波形观察窗口,并能对任何一种仿真性能实现加速。

支持通过 SCE-MI 接口进行 UVM 架构的仿真加速效果更佳,最新的基于 Xilinx UltraScale

的加速板和背板扩展,其容量最大可以支持 6.33 亿个 ASIC gate。

Co-Emulation 模式

Co-Emulation 模式是目前速度最优的软硬件协同验证手段,通过 PC 中虚拟平台环境与

www.aldec.com

第2页

�

硬件 HES 平台进行整个系统验证,虚拟平台基于标准组织 OVP 或 imperas,可实现 ARM 处理

器、接口标准 IP 等事务级验证 IP,灵活配置并可对嵌入式软件进行调试,其中 In Circuit

Emulation(ICE)模式完美融合了硬件仿真和原型验证的有点,是目前业界速度最优的软硬

件协同验证手段。

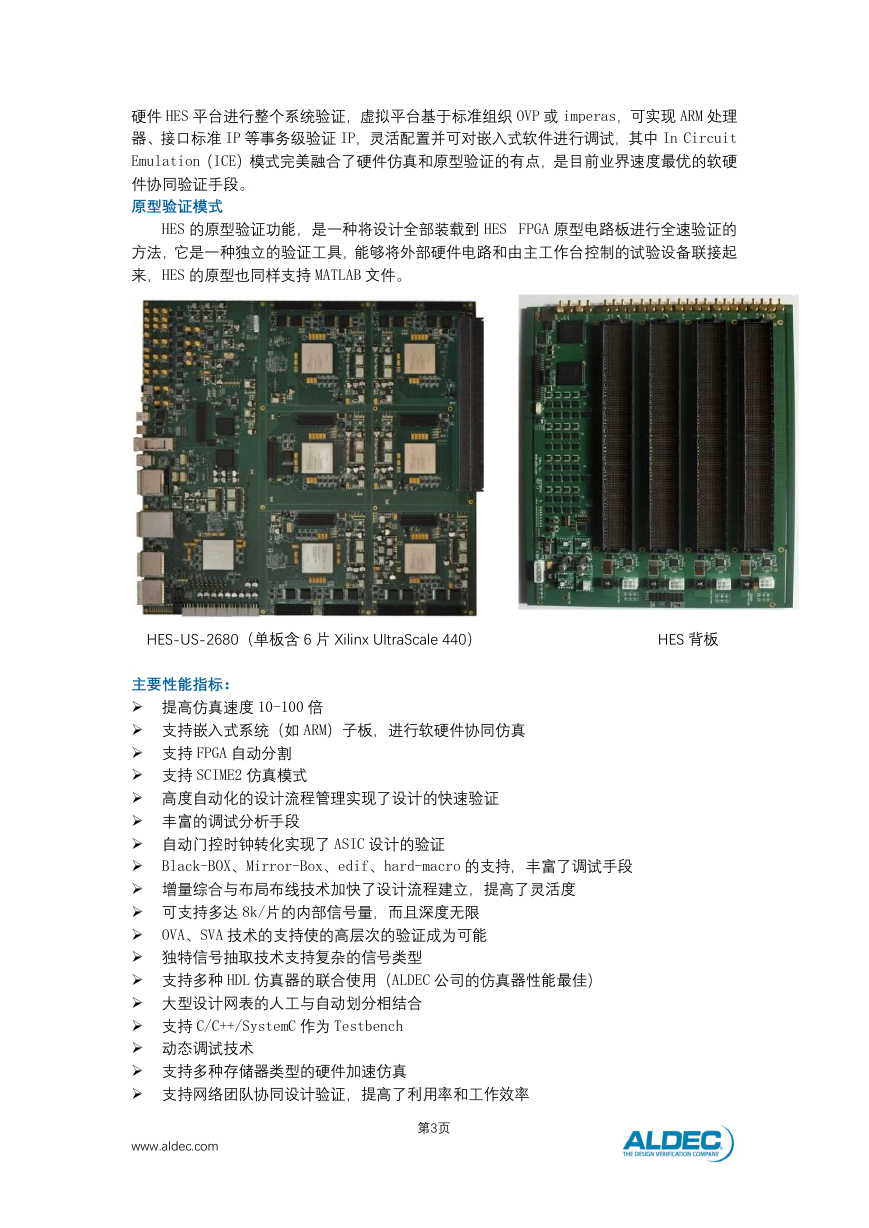

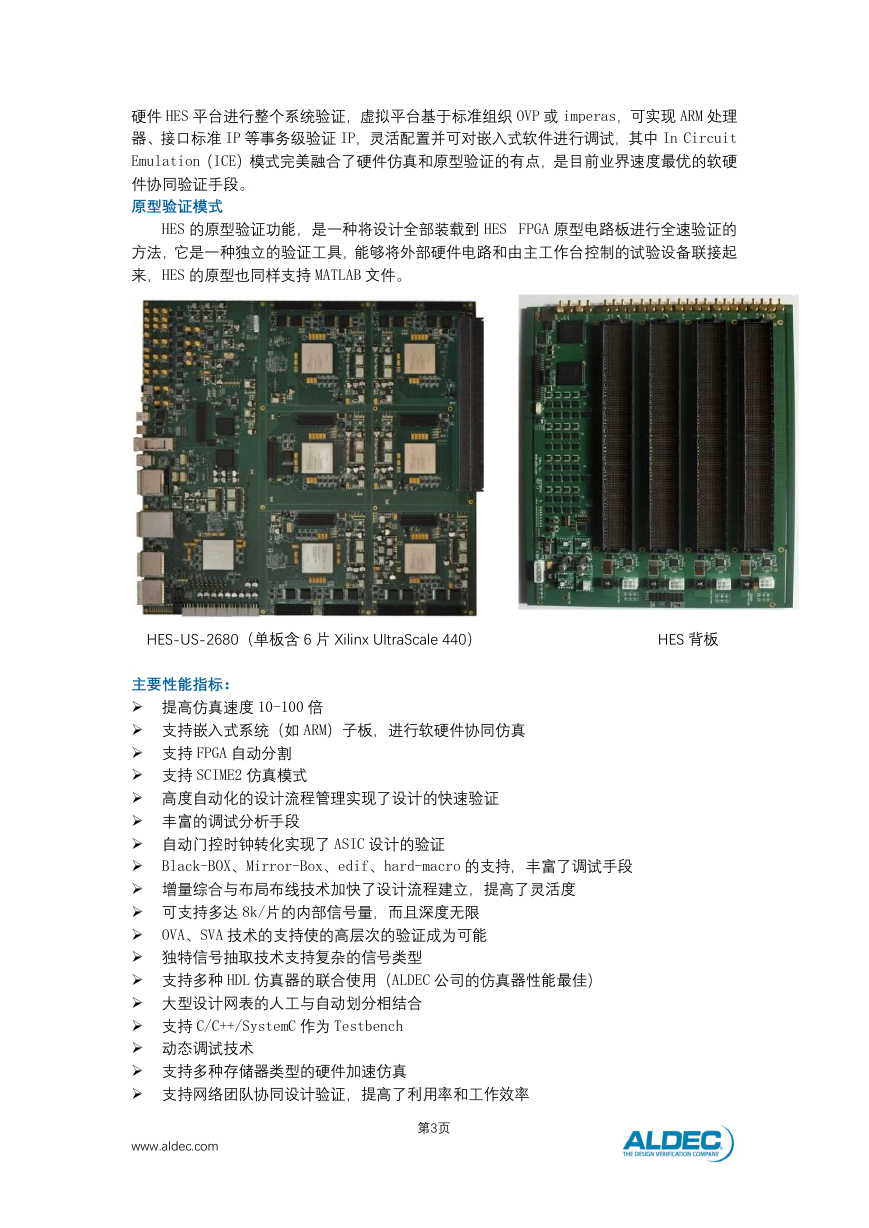

原型验证模式

HES 的原型验证功能,是一种将设计全部装载到 HES FPGA 原型电路板进行全速验证的

方法,它是一种独立的验证工具,能够将外部硬件电路和由主工作台控制的试验设备联接起

来,HES 的原型也同样支持 MATLAB 文件。

HES-US-2680(单板含 6 片 Xilinx UltraScale 440) HES 背板

主要性能指标:

➢ 提高仿真速度 10-100 倍

➢ 支持嵌入式系统(如 ARM)子板,进行软硬件协同仿真

➢ 支持 FPGA 自动分割

➢ 支持 SCIME2 仿真模式

➢ 高度自动化的设计流程管理实现了设计的快速验证

➢ 丰富的调试分析手段

➢ 自动门控时钟转化实现了 ASIC 设计的验证

➢ Black-BOX、Mirror-Box、edif、hard-macro 的支持,丰富了调试手段

➢ 增量综合与布局布线技术加快了设计流程建立,提高了灵活度

➢ 可支持多达 8k/片的内部信号量,而且深度无限

➢ OVA、SVA 技术的支持使的高层次的验证成为可能

➢ 独特信号抽取技术支持复杂的信号类型

➢ 支持多种 HDL 仿真器的联合使用(ALDEC 公司的仿真器性能最佳)

➢ 大型设计网表的人工与自动划分相结合

➢ 支持 C/C++/SystemC 作为 Testbench

➢ 动态调试技术

➢ 支持多种存储器类型的硬件加速仿真

➢ 支持网络团队协同设计验证,提高了利用率和工作效率

www.aldec.com

第3页

�

➢ 支持 Windows、Unix 以及 Linux 等操作平台

1.1.2. HES-DVM——混合 Co-Emulation、在线仿真(ICE)

和虚拟平台 QEMU 软硬件协同验证

随着工程的扩大,硬件模拟仿真变成了一种常见的集成在虚拟平台和标记为“混合 co-

emulation”的工具。该混合解决方案提供了一个唯一的验证平台给软件和硬件团队。该平台

允许了 SoC 级别中的验证性能,允许整个工程在最终设计代码在实际写入前进行验证,以及

允许了,例如,演示原型验证。

软硬件协同模拟仿真允许了工作环境的连接,该环境下,软件团队可以使用虚拟平台跟

硬件工程师使用模拟器进行连接。连接这两个领域允许了工程在 SoC 级别的测试,代替子系

统级别的测试,而这接着增加了测试的覆盖率,并使得问题的探测变得更加容易。

为了将软件和硬件验证行为组合起来,我们需要将一个虚拟平台和 RTL 仿真器连接起

来。一个广泛被使用和以软件团体而著名的例子是 QEMU,一个通用和开源的机器仿真器,

它支持多种的计算机硬件架构,包括 ARM Cortex 系列。QEMU 用于模拟仿真标准组件如 CPU

子系统和运行嵌入式软件测试。当它放在 RTL 仿真器上,则在行业内很罕见的,如 Aldec

Riviera-PRO。这个解决方案保证了彻底和全面的设计验证,同时在硬件和软件侧,而不需

要虚拟补丁或者器件驱动器的让步,否则或者用于一个非完整设计的固件代码。

验证流程

www.aldec.com

第4页

�

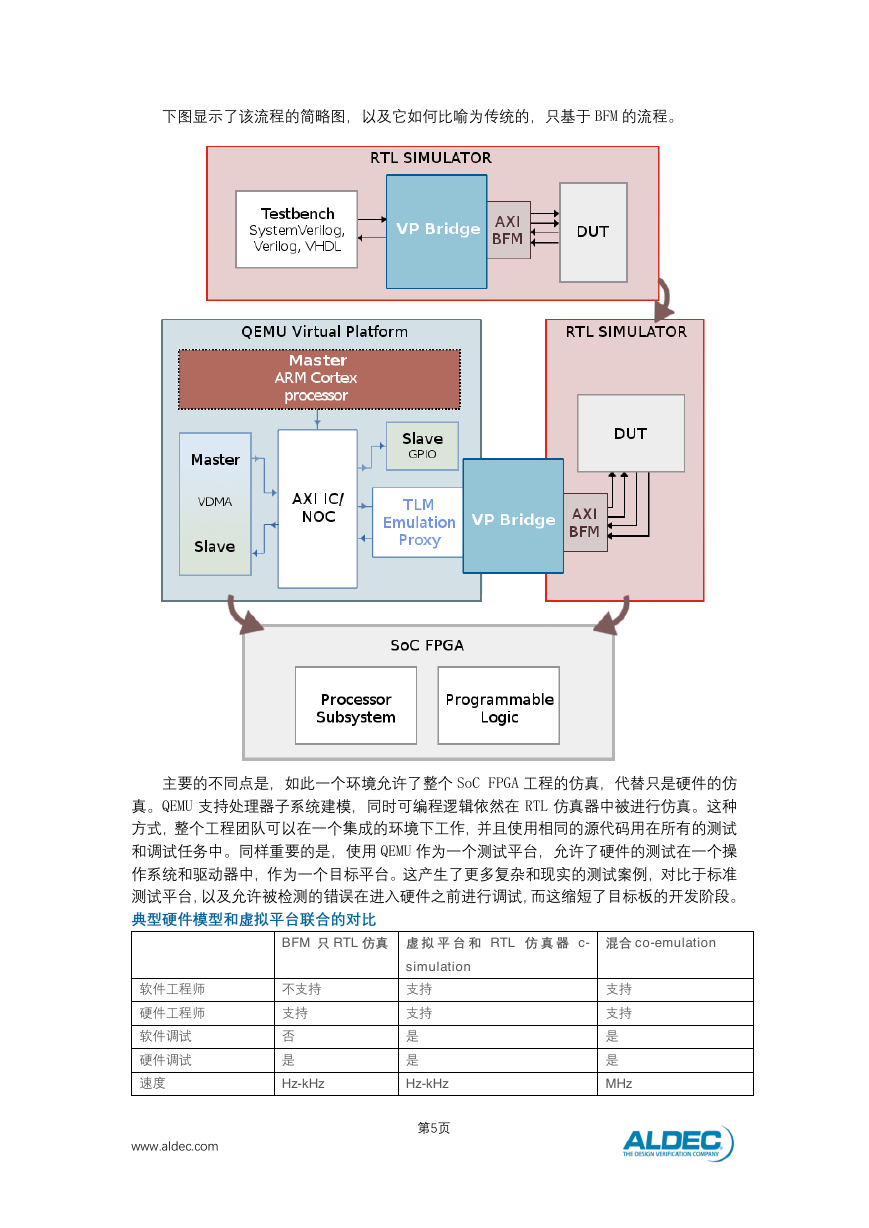

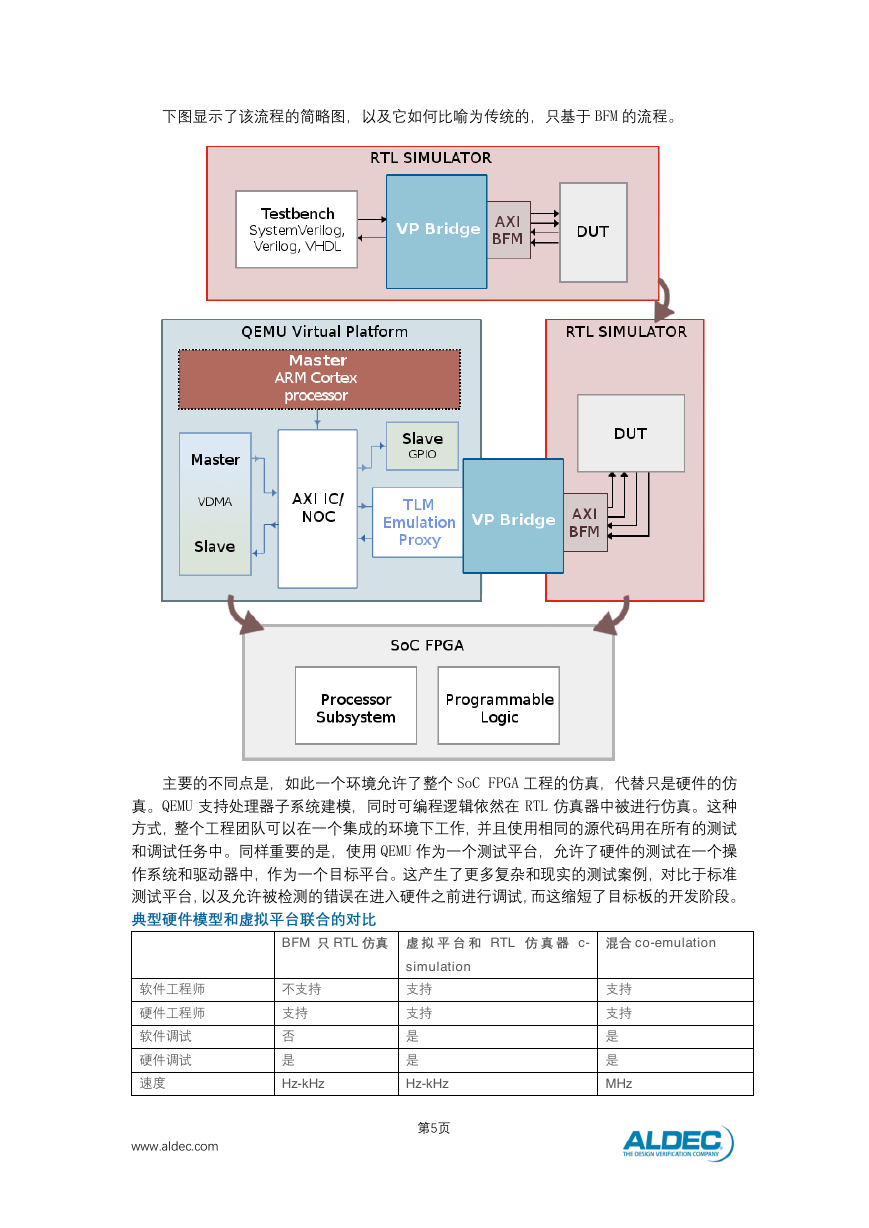

下图显示了该流程的简略图,以及它如何比喻为传统的,只基于 BFM 的流程。

主要的不同点是,如此一个环境允许了整个 SoC FPGA 工程的仿真,代替只是硬件的仿

真。QEMU 支持处理器子系统建模,同时可编程逻辑依然在 RTL 仿真器中被进行仿真。这种

方式,整个工程团队可以在一个集成的环境下工作,并且使用相同的源代码用在所有的测试

和调试任务中。同样重要的是,使用 QEMU 作为一个测试平台,允许了硬件的测试在一个操

作系统和驱动器中,作为一个目标平台。这产生了更多复杂和现实的测试案例,对比于标准

测试平台,以及允许被检测的错误在进入硬件之前进行调试,而这缩短了目标板的开发阶段。

典型硬件模型和虚拟平台联合的对比

BFM 只 RTL 仿真 虚 拟 平 台 和 RTL 仿 真 器 c-

混合 co-emulation

软件工程师

硬件工程师

软件调试

硬件调试

速度

www.aldec.com

不支持

支持

否

是

simulation

支持

支持

是

是

Hz-kHz

Hz-kHz

第5页

支持

支持

是

是

MHz

�

1.1.3. HES-DVM——原型验证(Prototyping)和多片 FPGA

分割(Multi-FPGA Partitioning)

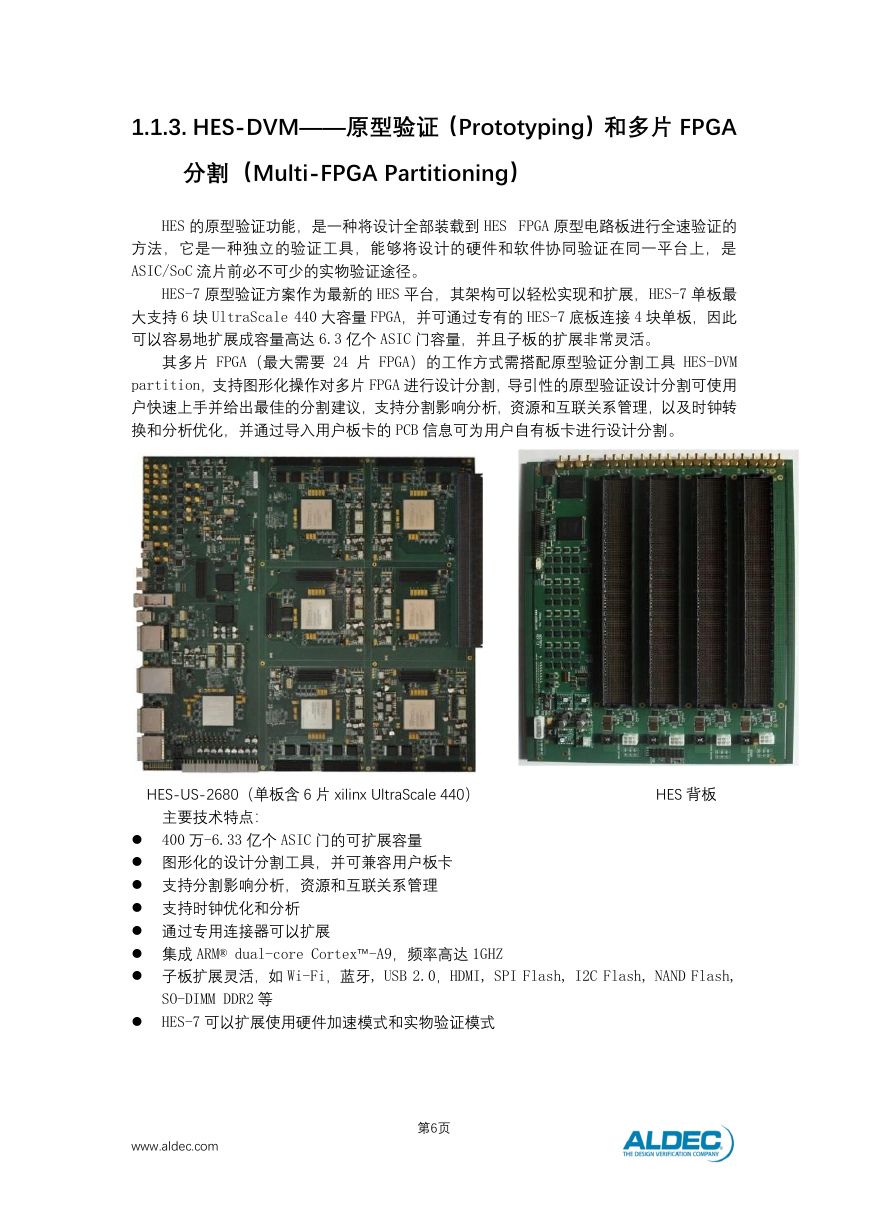

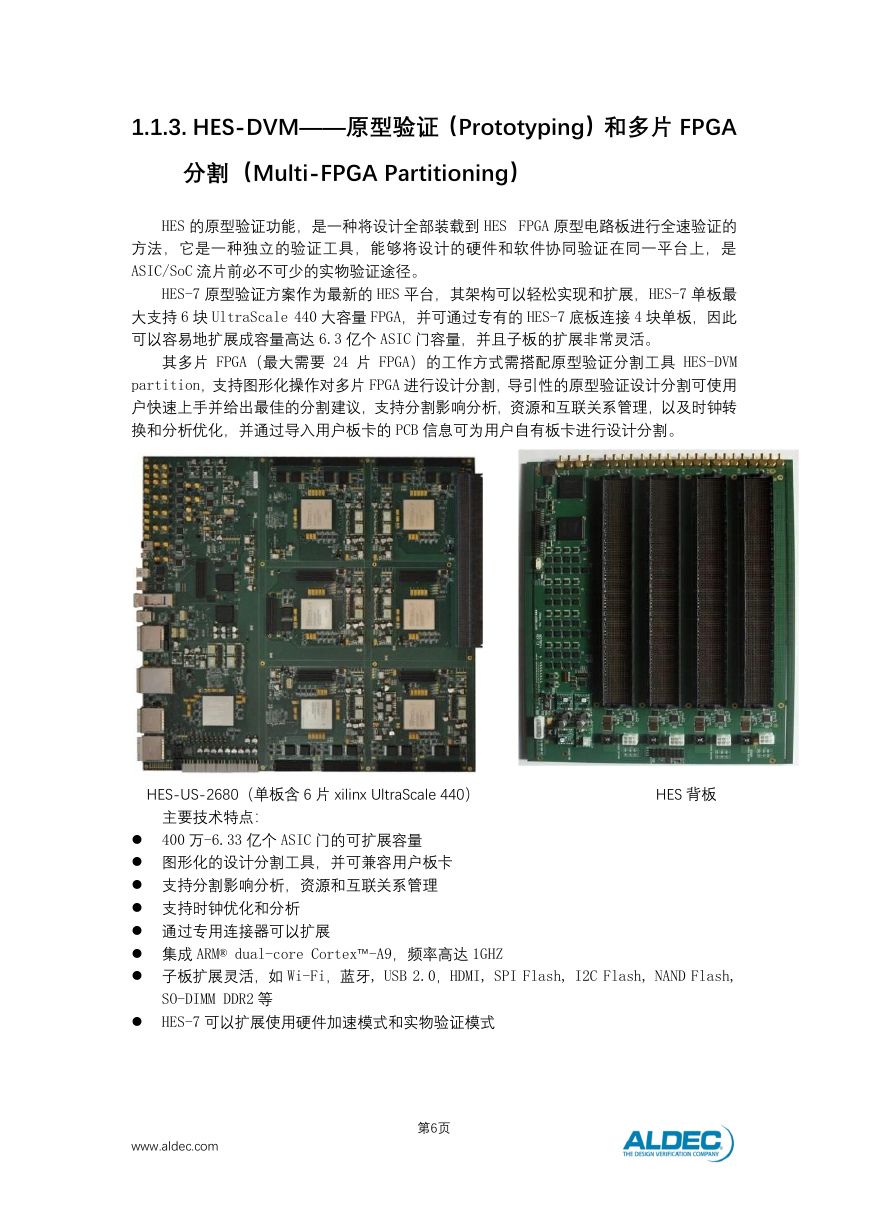

HES 的原型验证功能,是一种将设计全部装载到 HES FPGA 原型电路板进行全速验证的

方法,它是一种独立的验证工具,能够将设计的硬件和软件协同验证在同一平台上,是

ASIC/SoC 流片前必不可少的实物验证途径。

HES-7 原型验证方案作为最新的 HES 平台,其架构可以轻松实现和扩展,HES-7 单板最

大支持 6 块 UltraScale 440 大容量 FPGA,并可通过专有的 HES-7 底板连接 4 块单板,因此

可以容易地扩展成容量高达 6.3 亿个 ASIC 门容量,并且子板的扩展非常灵活。

其多片 FPGA(最大需要 24 片 FPGA)的工作方式需搭配原型验证分割工具 HES-DVM

partition,支持图形化操作对多片 FPGA 进行设计分割,导引性的原型验证设计分割可使用

户快速上手并给出最佳的分割建议,支持分割影响分析,资源和互联关系管理,以及时钟转

换和分析优化,并通过导入用户板卡的 PCB 信息可为用户自有板卡进行设计分割。

HES-US-2680(单板含 6 片 xilinx UltraScale 440) HES 背板

主要技术特点:

⚫ 400 万-6.33 亿个 ASIC 门的可扩展容量

⚫ 图形化的设计分割工具,并可兼容用户板卡

⚫ 支持分割影响分析,资源和互联关系管理

⚫ 支持时钟优化和分析

⚫ 通过专用连接器可以扩展

⚫ 集成 ARM® dual-core Cortex™-A9,频率高达 1GHZ

⚫ 子板扩展灵活,如 Wi-Fi,蓝牙, USB 2.0,HDMI, SPI Flash, I2C Flash, NAND Flash,

SO-DIMM DDR2 等

⚫ HES-7 可以扩展使用硬件加速模式和实物验证模式

www.aldec.com

第6页

�

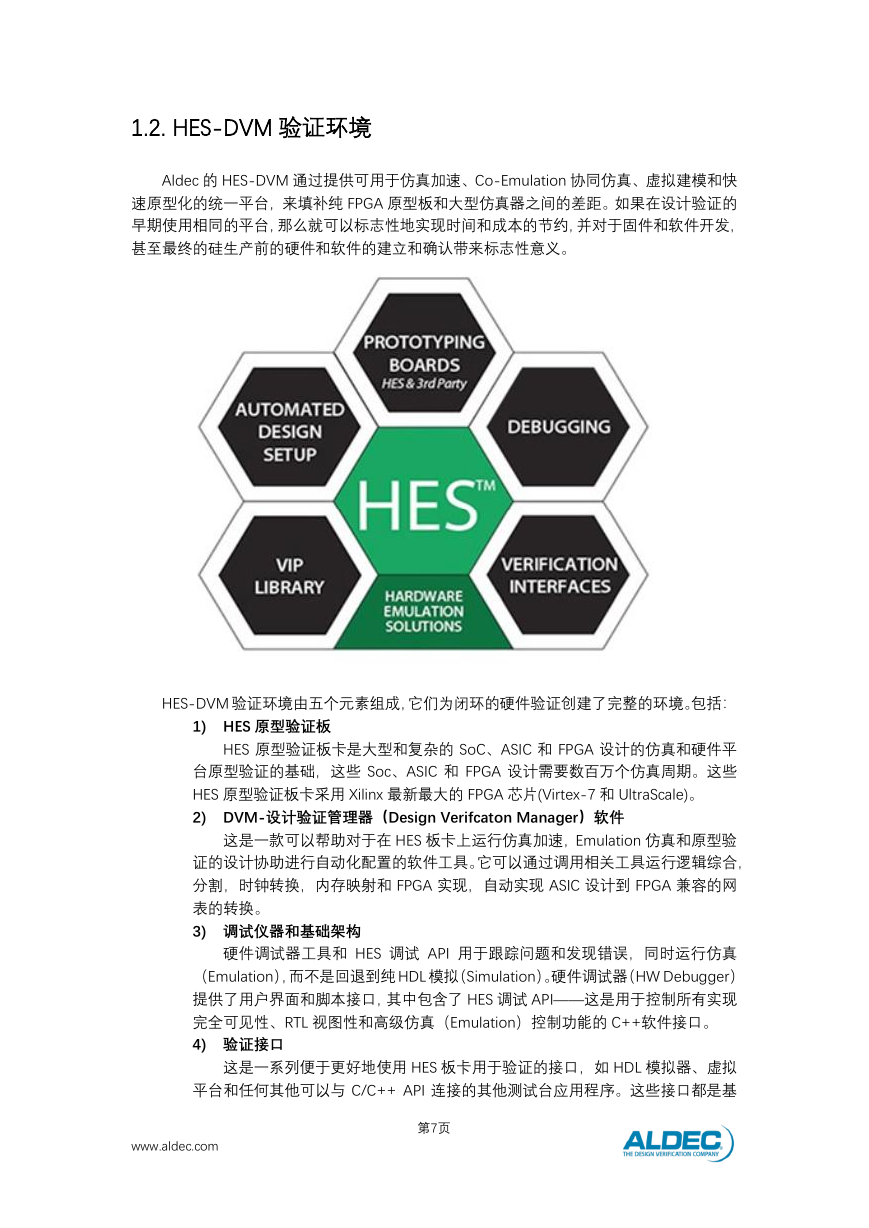

1.2. HES-DVM 验证环境

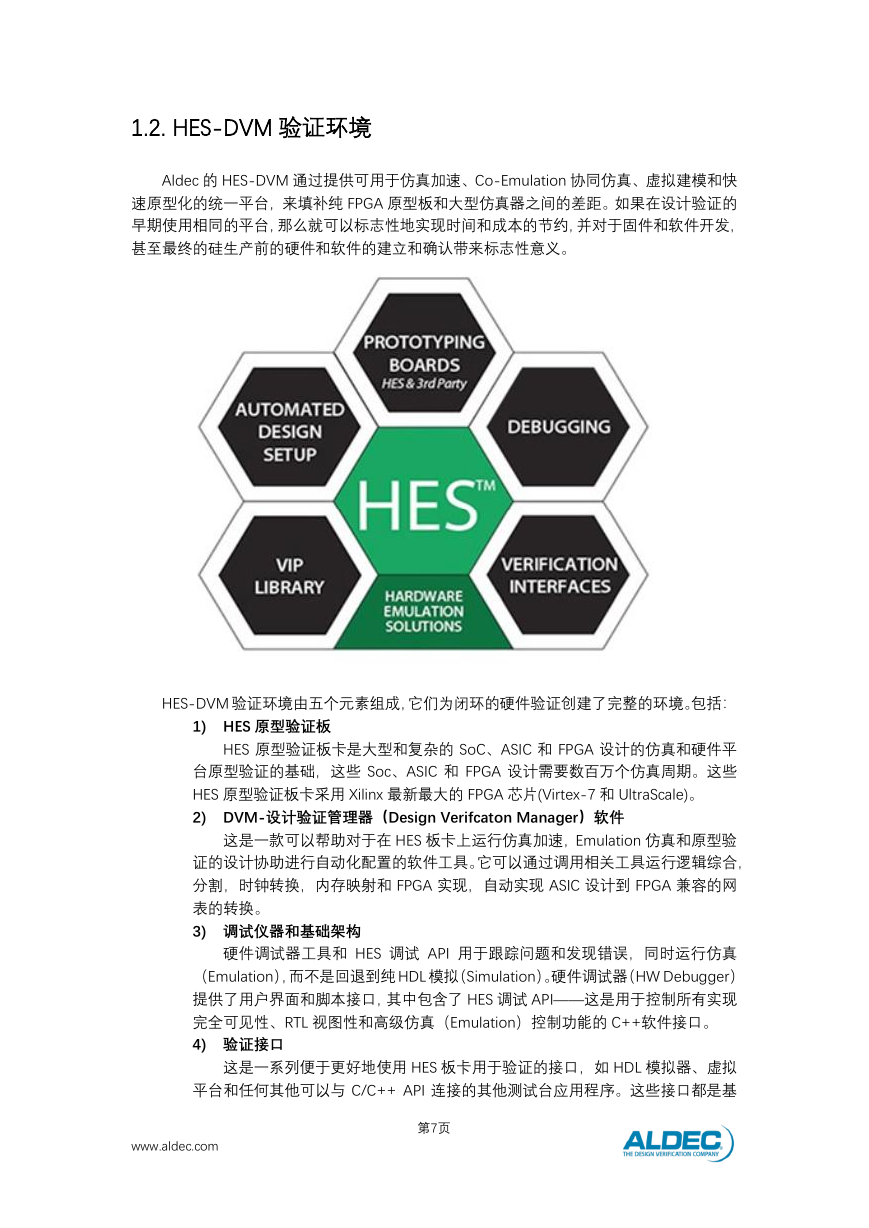

Aldec 的 HES-DVM 通过提供可用于仿真加速、Co-Emulation 协同仿真、虚拟建模和快

速原型化的统一平台,来填补纯 FPGA 原型板和大型仿真器之间的差距。如果在设计验证的

早期使用相同的平台,那么就可以标志性地实现时间和成本的节约,并对于固件和软件开发,

甚至最终的硅生产前的硬件和软件的建立和确认带来标志性意义。

HES-DVM 验证环境由五个元素组成,它们为闭环的硬件验证创建了完整的环境。包括:

1) HES 原型验证板

HES 原型验证板卡是大型和复杂的 SoC、ASIC 和 FPGA 设计的仿真和硬件平

台原型验证的基础,这些 Soc、ASIC 和 FPGA 设计需要数百万个仿真周期。这些

HES 原型验证板卡采用 Xilinx 最新最大的 FPGA 芯片(Virtex-7 和 UltraScale)。

2) DVM-设计验证管理器(Design Verifcaton Manager)软件

这是一款可以帮助对于在 HES 板卡上运行仿真加速,Emulation 仿真和原型验

证的设计协助进行自动化配置的软件工具。它可以通过调用相关工具运行逻辑综合,

分割,时钟转换,内存映射和 FPGA 实现,自动实现 ASIC 设计到 FPGA 兼容的网

表的转换。

3) 调试仪器和基础架构

硬件调试器工具和 HES 调试 API 用于跟踪问题和发现错误,同时运行仿真

(Emulation),而不是回退到纯 HDL 模拟(Simulation)。硬件调试器(HW Debugger)

提供了用户界面和脚本接口,其中包含了 HES 调试 API——这是用于控制所有实现

完全可见性、RTL 视图性和高级仿真(Emulation)控制功能的 C++软件接口。

4) 验证接口

这是一系列便于更好地使用 HES 板卡用于验证的接口,如 HDL 模拟器、虚拟

平台和任何其他可以与 C/C++ API 连接的其他测试台应用程序。这些接口都是基

www.aldec.com

第7页

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc