2

2

2

2

Modeling and Emulation of a Novel Pipeline ADC Based on MATLAB

L I M en g , Z H A N G R un

bi n , L A I Zon g

( I nstit ute of Microelect ronics Ci rcuit &S ystem , East Chi na N ormal Uni versit y , S han g hai 200062 , Chi na)

x i , C H E N L ei , S H E N J i a

mi n g , C H EN W en

s hen g

stage architect ure and lower p recision in 2 bit per

Abstract :A novel pipeline ADC st ruct ure based on MA TL AB/ Simulink toolbox is p ropo sed. In order to

balance higher power dissipation in 4 bit first

stage st ruc

stage t ype wit h 3 bit first stage is int roduced. Simulation result s indicate t hat t he maximum SN R

t ure ,a 8

( Signal to Noise Ratio) and SFDR (Sp urio us Free Dynamic Range) of t his ADC (Analog to Digital Conver

sion) are 60. 6 dB and 82. 177 dB respectively , wit h t he inp ut signal f requency of 10 M Hz and sampling

clock of 40 M Hz. The model of novel pipeline ADC can give helpf ul information on imp roving system error

performance and research on system static characteristic.

Key words :pipeline ADC ;3 bit architect ure ;gain error ;error in sub

EEACC :1290B

ADC ;error in sub

DAC

第 31 卷 第 3 期

2008 年 6 月

电 子 器 件

Chinese J ournal Of Elect ron Devices

Vol . 31 No. 3

J un. 2008

基于 MATLAB 的新型 Pipeline ADC 的建模和仿真

李 萌 ,张润曦 ,陈 磊 ,沈佳铭 ,陈文斌 ,赖宗声

(华东师范大学微电子电路与系统研究所 ,上海 200062)

摘 要 :在 MA TL AB/ Simulink 的平台上 ,设计并实现了一种新的 10 bit Pipeline ADC 的系统仿真模型 。针对 2 bit ,共 9 级

的结构的精度不足以及 4 bit 首级结构的功耗较大的特点 ,提出了一种首级 3 bit ,共 8 级的结构 。这种结构可以实现精度和功

耗的平衡 。经过系统仿真 ,在输入信号为 10 M Hz ,采样时钟频率为 40 M Hz 时 ,系统最大的 SNR = 60. 6 dB ,SFDR = 82. 177

dB 。创建的系统模型可为 ADC 系统中的误差和静态特性研究提供借鉴 。

关键词 :流水线结构的模数转换器 ;3 bit 结构 ;增益误差 ;子 ADC 误差 ;子 DAC(位数模转换器) 误差

中图分类号 :TN602

文献标识码 :A 文章编号 :1005

9490( 2008) 03

0834

04

模数转换器广泛应用于仪表 、通讯 、信号检测与

处理 、图像处理和多媒体等领域 ,它将现实社会的模

拟量转换为可以很方便地进行处理的数字量 ,几乎

所有的与模拟信号相关的电子产品中都能看到它的

身影 。不同领域对模数转换器的要求也不同 ,因此

模数转换器的结构也相应不同 。

流水线 结 构 由 两 步 结 构 演 化 而 来 , 由 m 级

flash ADC 构成 。每级包含采样保持 、子 ADC、子

DAC、减法器 、余量放大器等 ,从高位到低位依次算

出数字转换码 。由于每级都有采样保持电路 ,各级

可以同时工作 ,大大提高了转换速度 。采用 RSD

( Redundant Signed Digit ) 、平均技术 、校准技术等

可以获得较高的精度 。目前常用的结构有 9 级每级

2 bit 的结构[ 1 ] ,4 级每级 4bit 的结构[ 5 ] 等 。

然而 ,由于 9 级每级 2 bit 的结构的各级的精

度比较 低 , 受 级 间 转 换 误 差 ( 增 益 误 差 、子 ADC

误差 、子 DAC 误差) 的影响比较比较大 。如果采

用每级高精 度的 结构则 需要 较 大 的 功 耗 。例 如

每级 4 bit 的结构 ,每一级需要 15 个比较器 。本

文针对以上的矛盾设计了一种新的结构 ,在这种

结构中第一级采用了 3 bit 的结构 ,其它的 7 级则

采用每级 2 bit 的结构 。由于首级具有 3 bit 的精

16

03

收稿日期 :2007

基金项目 :上海市 AM 基金资助 (AM 0508) (AM 0513) ;上海市科委资助 (06SA14 )

作者简介 :李 萌 (1983

赖宗声 (1943

) ,男 ,硕士研究生 ,主要研究方向为数模混合集成电路设计 ,51051202029 @student . ecnu. edu. cn ;

) ,男 ,教授 ,博士生导师 ,华东师范大学微电子电路与系统研究所 ,研究方向为集成电路设计 。

�

第 3 期

李 萌 ,张润曦等 :基于 MA TL AB 的新型 Pipeline ADC 的建模和仿真

538

度 ,对级间误差可以达到较好的抑制 ,而相对于 9

级每级 2 bit 的结构只是多了 3 个比较器在功耗

上也相对较低 。

1 Pipeline ADC 模型的建立

1. 1 设计原理

ADC 的每一级都采用 2 bit 是一种常见的结

2 ] ,这种结构有两个主要的优点 : ①每一级的放

构[ 1

大器都具有很宽的带宽 ,大的反馈系数通常可以减

少建立时间 (较小的时间常数) ,这就意味着每一级

都可以有较快的速度[ 3 ] ; ②由于数字纠错系统可以

减小比较器所需的偏移量 ,这种结构在比较器中不

需要预放 (p reamplifier) ,因而这种结构具有较小的

功耗 。但是 ,这种结构的一个主要的缺点就是需要

较多的级数 ,这就使这种结构对级间的匹配要求比

较高[ 4 ] 。这种结构需要额外的校正电路 ,从而产生

了更多的死区 。

对于每级具有多位 (大于 2 bit) 的结构 ,系统

的整体精度 及级 间转换 误差 的抑 制能 力都有 所

提高 ,它具有以下几个优点 : ① 对放大器的增益

和建立时间没有十分严格地要求 ,增益误差对这

种结构的精度的影响相对较低 ,这就意味着可以

利用较 低 功 耗 结 构 的 放 大 器 来 实 现 此 结 构 [ 5 ] ;

② 由于 KT/ C 噪 声 较 低 , 电 容 匹 配 误 差 相 对 较

小 ,这种方法可以有效地减小电容的大小 ,也就

使功耗进一步降低 ; ③ 输入参考噪声将会减小 ,

这是由于从 下一 级反馈 的噪 声将 会被 高增益 的

放大器所隔 离 , 对 本级 的影 响会 大 大 减 少 [ 6 ] ; 尽

管如此 ,这种 方法 也有 明显的 不 足 。首 先 , 由 于

每级的位数 的增 加使每 级内 部的 放大 器的反 馈

系数减小 , 从 而具 有 较 大 的 时 间 常 数 [ 5 ] 。其 次 ,

当某一级的位数超过 4 bit ,在比较器中就需要加

上预放 ,而预 放的 加入 会使 整 个 ADC 的 功 耗 增

加 。最后 ,每级多位的结构将会增加比较器的数

量 。这会增加寄生的电容 ,放大器也必须去驱动

这些寄生电容负载 ,这就会增加了整体的功耗 。

1. 2 系统仿真模型的建立

基于以上的理论本文对提出的首级 3 bit 共 8

级的结 构 进 行 建 模 。利 用 的 工 具 是 MA TL AB/

Simulink 。Simulink 软件包的特色在于 : ①实现可

视化建模 。在 Windows 视窗下 ,用户通过简单的鼠

标抓取操作就可以建立直观的系统模型 ,并进行仿

真 。 ②实现了多工作环境间文件互用和数据交换 ,

具有方便 、直观和灵活的优点 ,因此 Simulink 软件

包是对 Pipeline ADC 进行建模的强有力工具 。

3 bit 单元的输入输出关系如式 (1) 所示 ,其中

vin为输入信号 , vout 为输出信号 , vref 为参考电平 (在

系统仿真中我们设参考电平的大小为 1) 。

4 ·vin - 3 ·vref

vin >

5

8

·vref

4 ·vin - 2 ·vref

4 ·vin - 1 ·vref

5

8

3

8

·vref > vin > 3

8

·vref > vin > 1

8

vref

vref

vout =

4 ·vin

1

8

·vref > vin > - 1

8

·vref

(1)

4 ·vin + 1 ·vref

4 ·vin - 2 ·vref

4 ·vin + 3 ·vref

-

- 1

8

3

8

- 5

8

·vref > vin > - 3

8

5

8

·vref > vin > -

vref

vref

·vref > vin

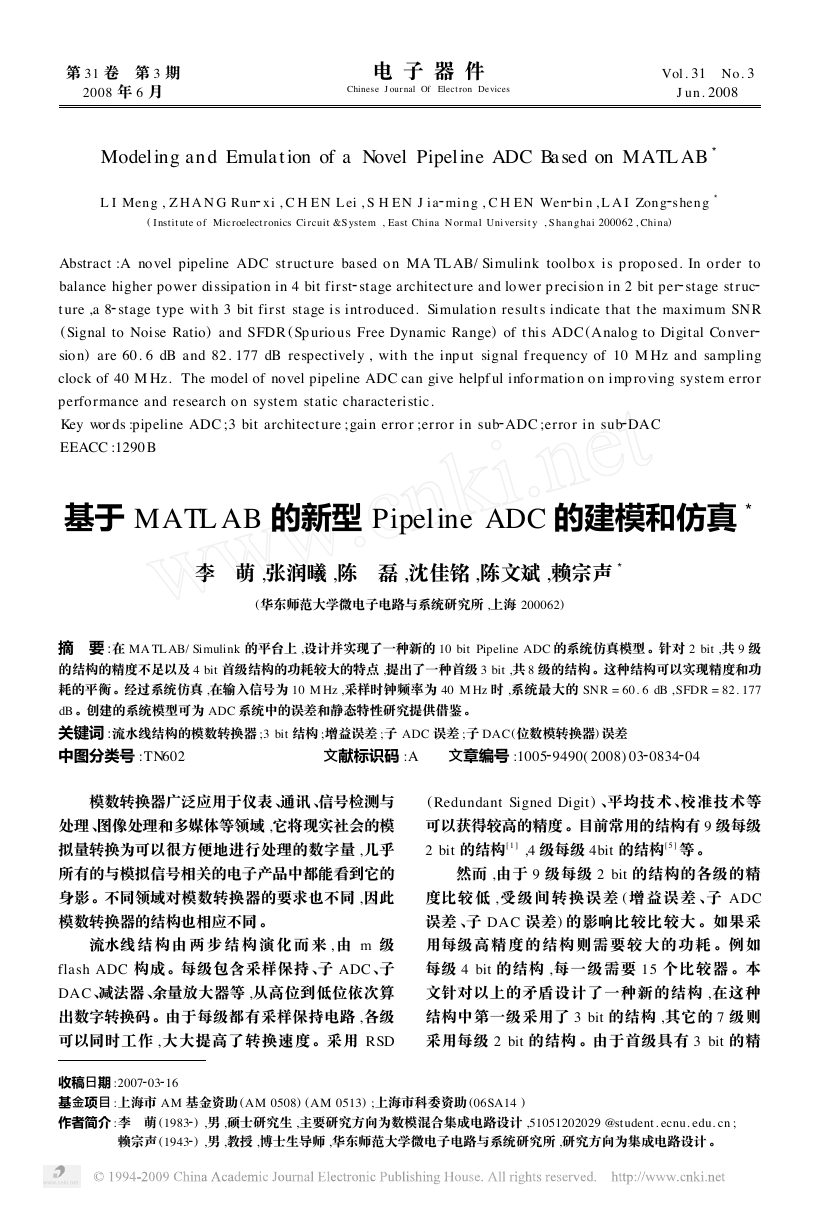

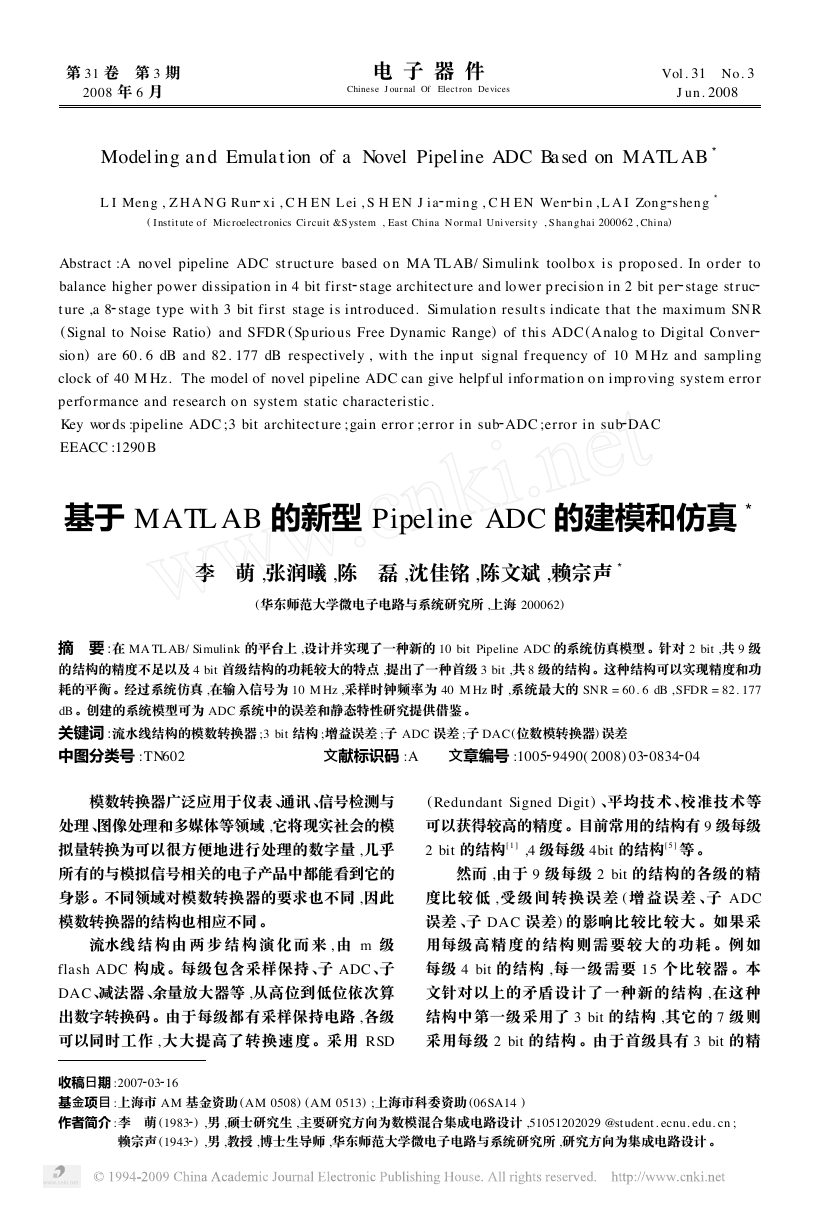

根据上式我们可以得到 3 bit 单元整体的结构

如图 1 所示 。整个结构包括一个零阶保持单元 ,一

图 1 3 bit 单元的结构图

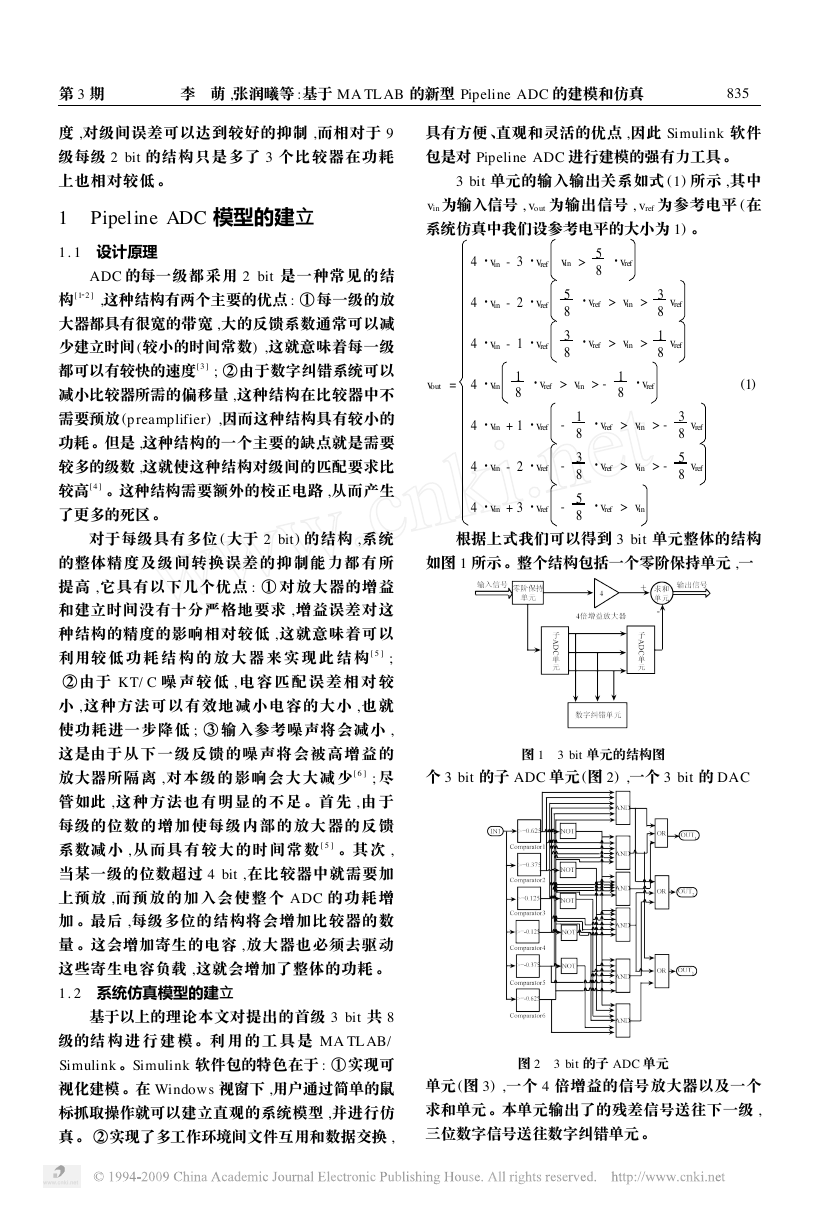

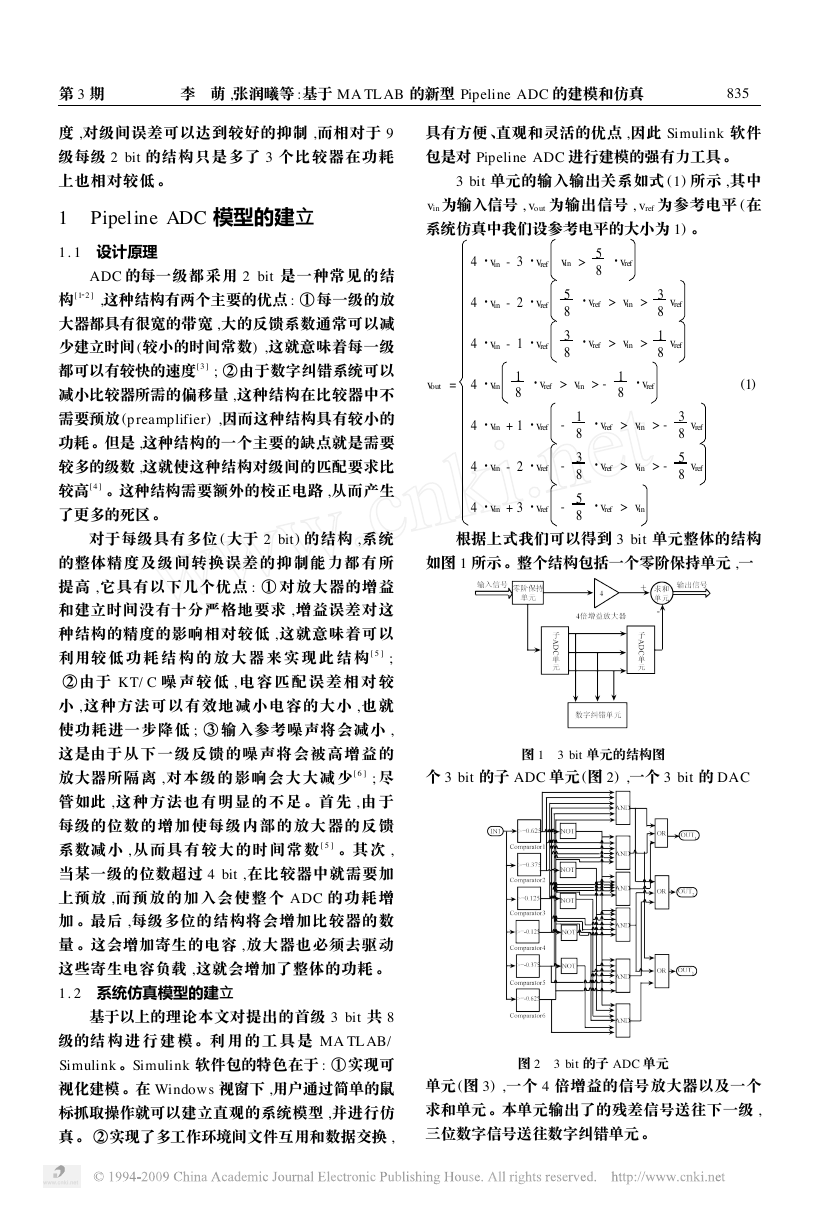

个 3 bit 的子 ADC 单元 (图 2) ,一个 3 bit 的 DAC

图 2 3 bit 的子 ADC 单元

单元 (图 3) ,一个 4 倍增益的信号放大器以及一个

求和单元 。本单元输出了的残差信号送往下一级 ,

三位数字信号送往数字纠错单元 。

�

638

电 子 器 件

第 31 卷

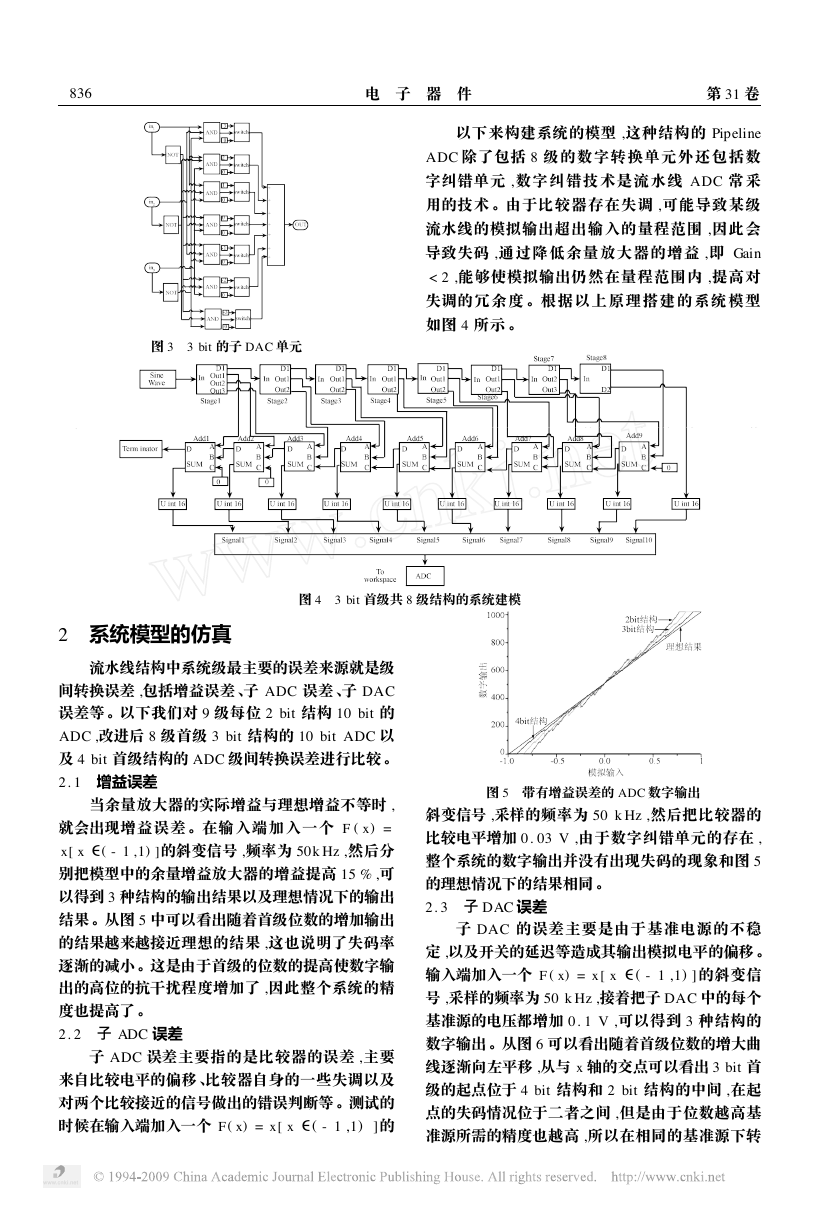

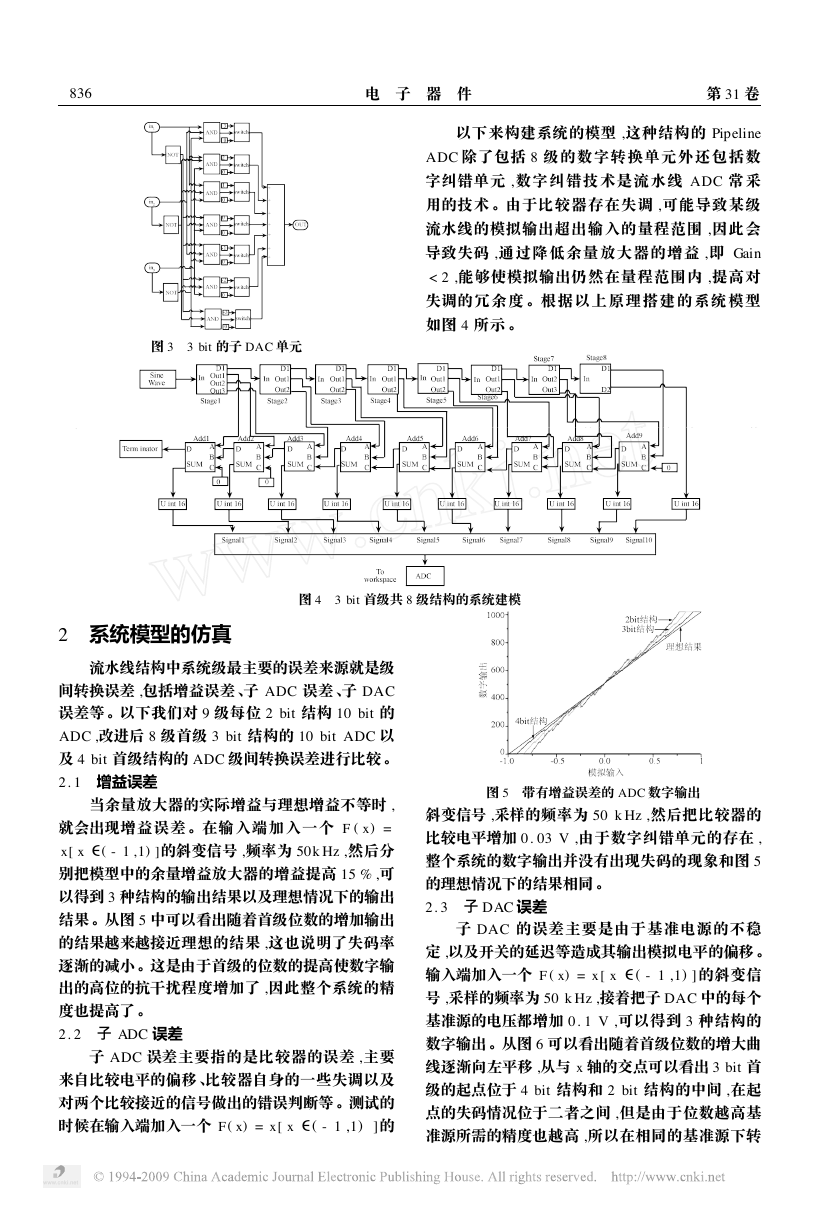

以下来构建系统的模型 ,这种结构的 Pipeline

ADC 除了包括 8 级的数字转换单元外还包括数

字纠错单元 ,数字纠错技术是流 水线 ADC 常采

用的技术 。由于比较器存在失调 ,可能导致某级

流水线的模拟输出超出输入的量程范围 ,因此会

导致失码 ,通过降低余量放大器的增益 ,即 Gain

< 2 ,能够使模拟输出仍然在量程范围内 ,提高对

失调的冗余 度 。根据 以上 原理 搭 建 的 系 统 模 型

如图 4 所示 。

图 3 3 bit 的子 DAC 单元

图 4 3 bit 首级共 8 级结构的系统建模

2 系统模型的仿真

流水线结构中系统级最主要的误差来源就是级

间转换误差 ,包括增益误差 、子 ADC 误差 、子 DAC

误差等 。以下我们对 9 级每位 2 bit 结构 10 bit 的

ADC ,改进后 8 级首级 3 bit 结构的 10 bit ADC 以

及 4 bit 首级结构的 ADC 级间转换误差进行比较 。

2. 1 增益误差

当余量放大器的实际增益与理想增益不等时 ,

就会出现增益误差 。在输入端加入一个 F ( x) =

x [ x ∈( - 1 ,1) ]的斜变信号 ,频率为 50k Hz ,然后分

别把模型中的余量增益放大器的增益提高 15 % ,可

以得到 3 种结构的输出结果以及理想情况下的输出

结果 。从图 5 中可以看出随着首级位数的增加输出

的结果越来越接近理想的结果 ,这也说明了失码率

逐渐的减小 。这是由于首级的位数的提高使数字输

出的高位的抗干扰程度增加了 ,因此整个系统的精

度也提高了 。

2. 2 子 ADC 误差

子 ADC 误差主要指的是比较器的误差 ,主要

来自比较电平的偏移 、比较器自身的一些失调以及

对两个比较接近的信号做出的错误判断等 。测试的

]的

时候在输入端加入一个 F( x) = x [ x ∈( - 1 ,1)

图 5 带有增益误差的 ADC 数字输出

斜变信号 ,采样的频率为 50 k Hz ,然后把比较器的

比较电平增加 0. 03 V ,由于数字纠错单元的存在 ,

整个系统的数字输出并没有出现失码的现象和图 5

的理想情况下的结果相同 。

2. 3 子 DAC 误差

子 DAC 的误差主要是由于基准电源的不稳

定 ,以及开关的延迟等造成其输出模拟电平的偏移 。

输入端加入一个 F ( x) = x [ x ∈( - 1 ,1) ]的斜变信

号 ,采样的频率为 50 k Hz ,接着把子 DAC 中的每个

基准源的电压都增加 0. 1 V ,可以得到 3 种结构的

数字输出 。从图 6 可以看出随着首级位数的增大曲

线逐渐向左平移 ,从与 x 轴的交点可以看出 3 bit 首

级的起点位于 4 bit 结构和 2 bit 结构的中间 ,在起

点的失码情况位于二者之间 ,但是由于位数越高基

准源所需的精度也越高 ,所以在相同的基准源下转

�

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

738

2

2

2

2

2

2

第 3 期

李 萌 ,张润曦等 :基于 MA TL AB 的新型 Pipeline ADC 的建模和仿真

换过程中 3 bit 会产生相对较多的失码 。在设计过

程中首级位数较多的结构需要要求严格的基准源 。

图 6 带有子 DAC 误差的数字输出

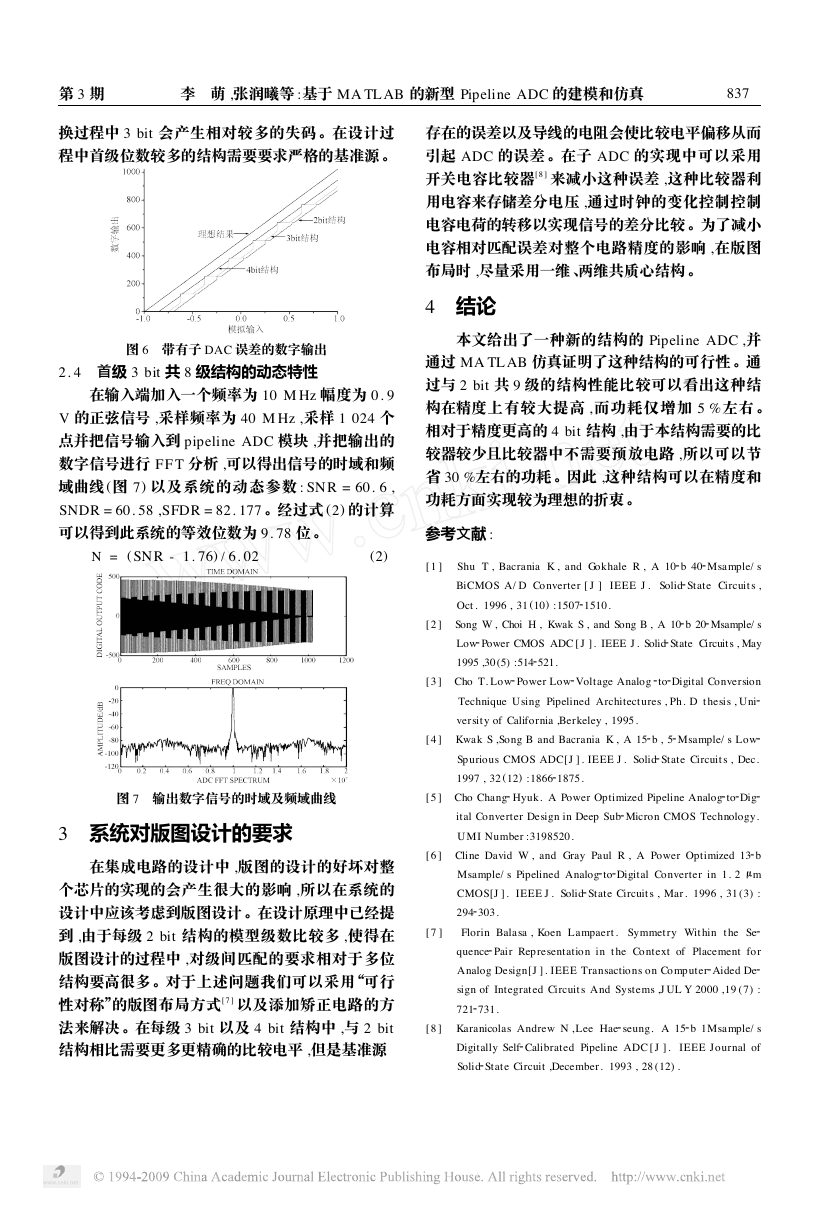

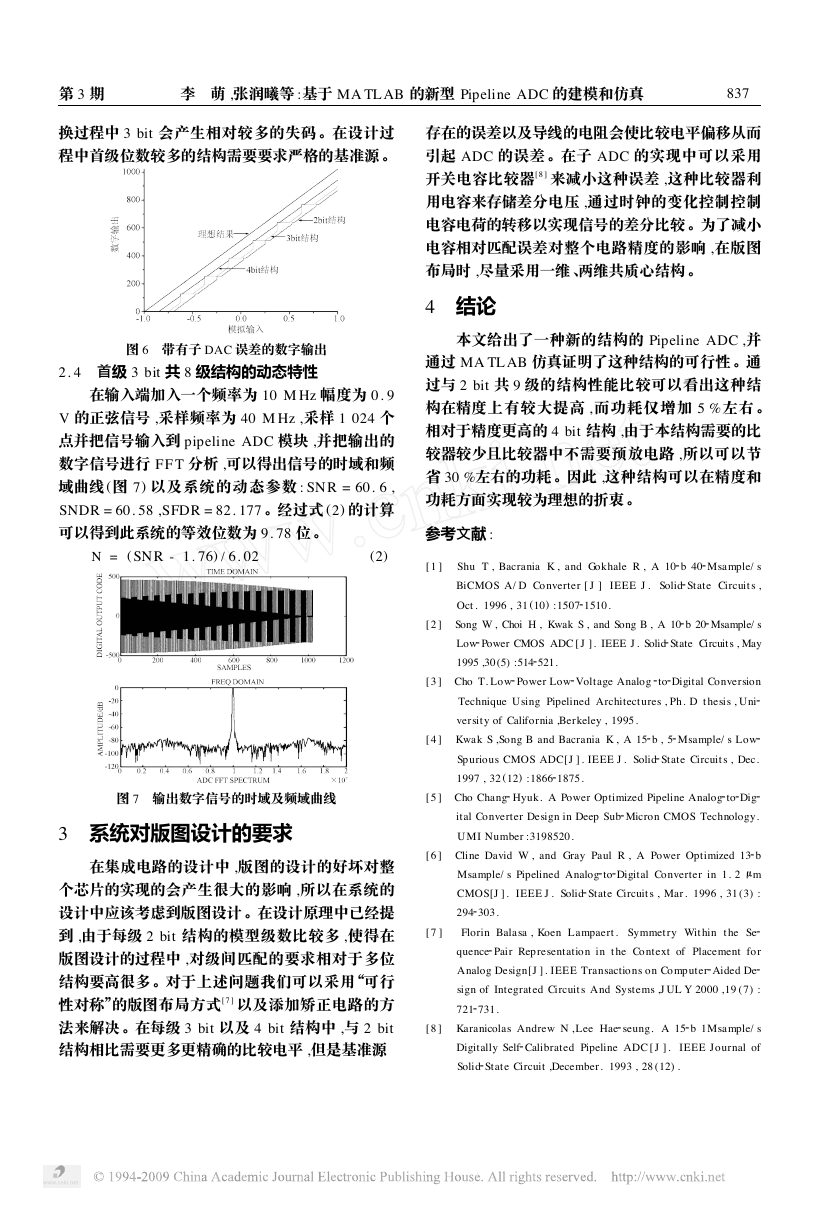

2. 4 首级 3 bit 共 8 级结构的动态特性

在输入端加入一个频率为 10 M Hz 幅度为 0. 9

V 的正弦信号 ,采样频率为 40 M Hz ,采样 1 024 个

点并把信号输入到 pipeline ADC 模块 ,并把输出的

数字信号进行 FF T 分析 ,可以得出信号的时域和频

域曲线 (图 7) 以及系统的动态参数 : SN R = 60. 6 ,

SNDR = 60. 58 ,SFDR = 82. 177 。经过式 (2) 的计算

可以得到此系统的等效位数为 9. 78 位 。

N = ( SN R - 1. 76) / 6. 02

(2)

存在的误差以及导线的电阻会使比较电平偏移从而

引起 ADC 的误差 。在子 ADC 的实现中可以采用

开关电容比较器[ 8 ] 来减小这种误差 ,这种比较器利

用电容来存储差分电压 ,通过时钟的变化控制控制

电容电荷的转移以实现信号的差分比较 。为了减小

电容相对匹配误差对整个电路精度的影响 ,在版图

布局时 ,尽量采用一维 、两维共质心结构 。

4 结论

本文给出了一种新的结构的 Pipeline ADC ,并

通过 MA TL AB 仿真证明了这种结构的可行性 。通

过与 2 bit 共 9 级的结构性能比较可以看出这种结

构在精度上有较大提高 ,而功耗仅增加 5 %左右 。

相对于精度更高的 4 bit 结构 ,由于本结构需要的比

较器较少且比较器中不需要预放电路 ,所以可以节

省 30 %左右的功耗 。因此 ,这种结构可以在精度和

功耗方面实现较为理想的折衷 。

参考文献 :

[ 1 ] Shu T , Bacrania K , and Gokhale R , A 10

IEEE J . Solid

BiCMOS A/ D Converter [ J ]

Oct . 1996 , 31 (10) :1507

1510.

b 40

Msample/ s

State Circuit s ,

[ 2 ] Song W , Choi H , Kwak S , and Song B , A 10

b 20

Msample/ s

Power CMOS ADC [ J ]. IEEE J . Solid

State Circuits , May

Low

1995 ,30 (5) :514

521.

[ 3 ] Cho T. Low

Power Low

Voltage Analog

to

Digital Conversion

Technique Using Pipelined Architect ures , Ph. D t hesis , Uni

versity of California ,Berkeley , 1995.

[ 4 ] Kwak S ,Song B and Bacrania K , A 15

b , 5

Msample/ s Low

Spurious CMOS ADC[J ] . IEEE J . Solid

1997 , 32 (12) :1866

1875.

State Circuit s , Dec.

图 7 输出数字信号的时域及频域曲线

[ 5 ] Cho Chang

Hyuk. A Power Optimized Pipeline Analog

to

Dig

3 系统对版图设计的要求

在集成电路的设计中 ,版图的设计的好坏对整

个芯片的实现的会产生很大的影响 ,所以在系统的

设计中应该考虑到版图设计 。在设计原理中已经提

到 ,由于每级 2 bit 结构的模型级数比较多 ,使得在

版图设计的过程中 ,对级间匹配的要求相对于多位

结构要高很多 。对于上述问题我们可以采用“可行

性对称”的版图布局方式[ 7 ] 以及添加矫正电路的方

法来解决 。在每级 3 bit 以及 4 bit 结构中 ,与 2 bit

结构相比需要更多更精确的比较电平 ,但是基准源

ital Converter Design in Deep Sub

Micron CMOS Technology.

UMI Number :3198520.

[ 6 ] Cline David W , and Gray Paul R , A Power Optimized 13

b

Digital Converter in 1. 2 μm

State Circuit s , Mar. 1996 , 31 (3) :

to

Msample/ s Pipelined Analog

CMOS[J ] . IEEE J . Solid

294

303.

[ 7 ] Florin Balasa , Koen Lampaert . Symmet ry Wit hin t he Se

Pair Representation in t he Context of Placement for

quence

Aided De

Analog Design[J ] . IEEE Transactions on Computer

sign of Integrated Circuit s And Systems ,J UL Y 2000 ,19 (7) :

721

731.

[ 8 ] Karanicolas Andrew N ,Lee Hae

seung. A 15

b 1Msample/ s

Digitally Self

Calibrated Pipeline ADC [ J ] .

IEEE Journal of

Solid

State Circuit ,December. 1993 , 28 (12) .

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc