硬件技术课程设计

课题名称

8 位全加器的设计与实现

组

组

班

专

名

员

级

业

陈唯 许晶晶 谭兰兰 段思雨

1201

计算机科学与技术

指导教师

范波

计算机学院

2014 年 12 月

�

课题四、8 位全加器的设计与实现

一、设计任务及要求:

1.设计和实现 8 位全加器,并完成编译、综合、适配、仿真和在 GW48-CP++实

验平台上,实验测试,即选择电路模式 NO.1;键 2、键 1 输入 8 位加数;键 4、

键 3 输入 8 位被加数;数码管 6 和数码管 5 显示加和;D8 显示进位 COUT。

2.请画出时序仿真图

3.进行必要的数据测试

2014 年 12 月 10 日

陈唯

许晶晶

谭兰兰

段思雨

二、成绩:

设计报告

调试答辩

合

计

指导教师签名:

2014 年

月

日

�

目 录

1. 设计目的……………………………………………1

2. 设计内容……………………………………………2

3. 实验原理图

3.1 半加器原理图

3.2 一位全加器原理图

3.3 位全加器原理图

3.4 锁引脚原理图

4. 设计与说明

5. 时序仿真

5.1 时序仿真图

6. 实现步骤

7. 实验总结

8. 参考文献

9. 附

�

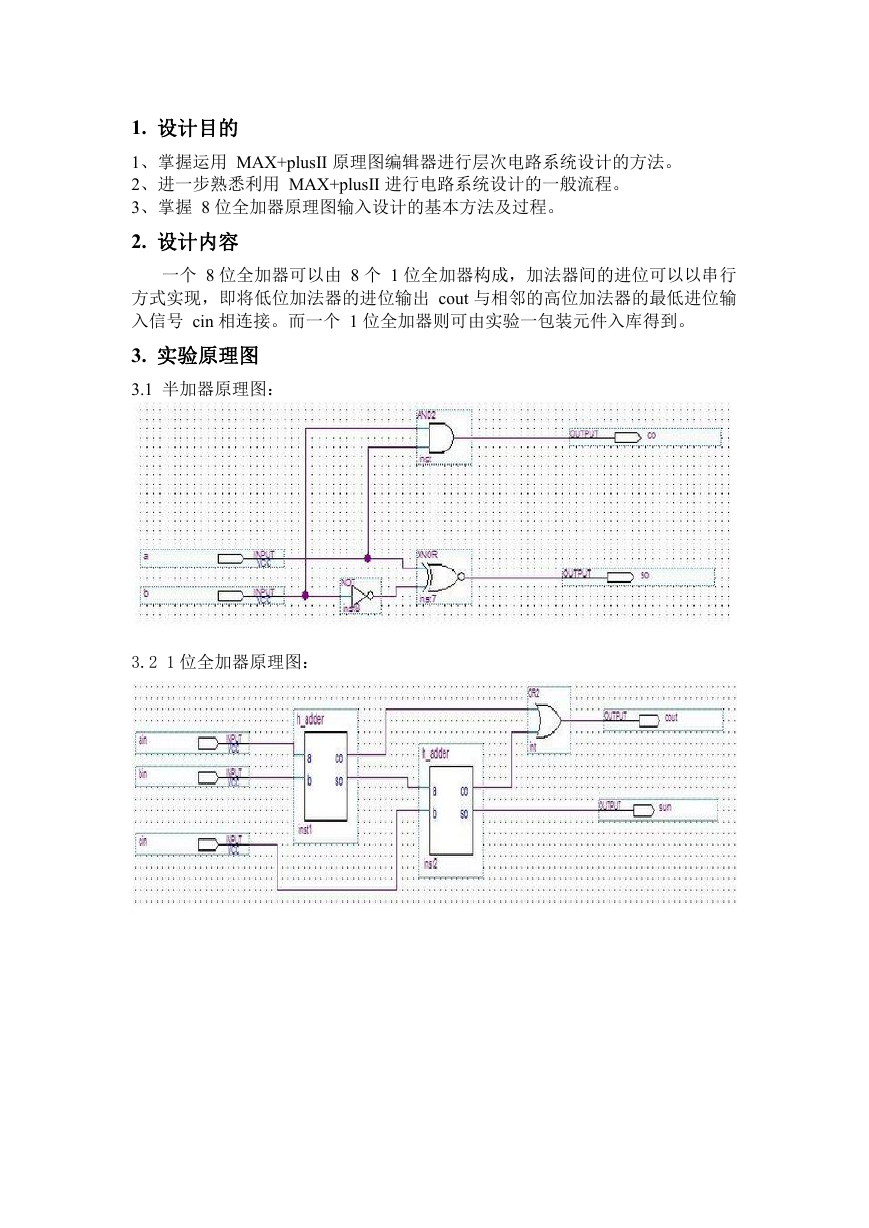

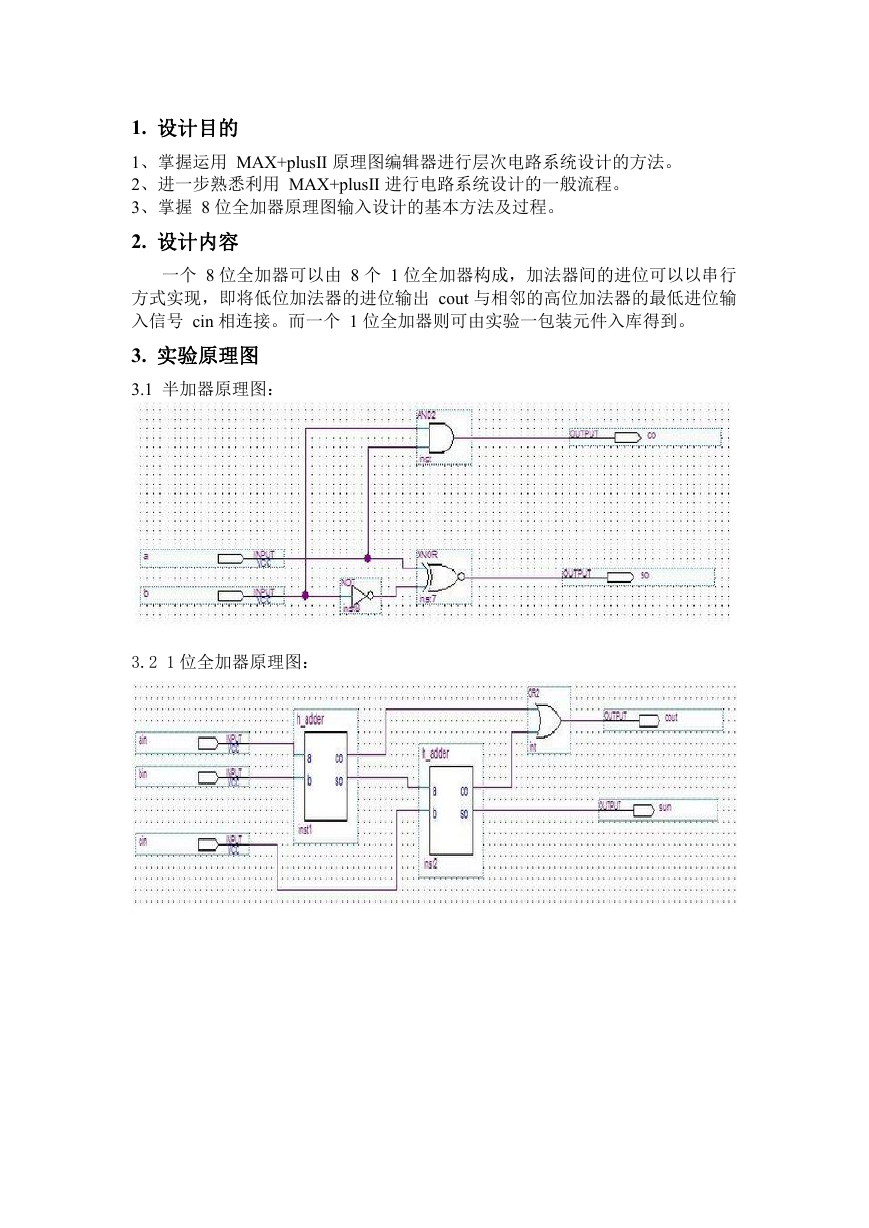

1. 设计目的

1、掌握运用 MAX+plusII 原理图编辑器进行层次电路系统设计的方法。

2、进一步熟悉利用 MAX+plusII 进行电路系统设计的一般流程。

3、掌握 8 位全加器原理图输入设计的基本方法及过程。

2. 设计内容

一个 8 位全加器可以由 8 个 1 位全加器构成,加法器间的进位可以以串行

方式实现,即将低位加法器的进位输出 cout 与相邻的高位加法器的最低进位输

入信号 cin 相连接。而一个 1 位全加器则可由实验一包装元件入库得到。

3. 实验原理图

3.1 半加器原理图:

3.2 1 位全加器原理图:

�

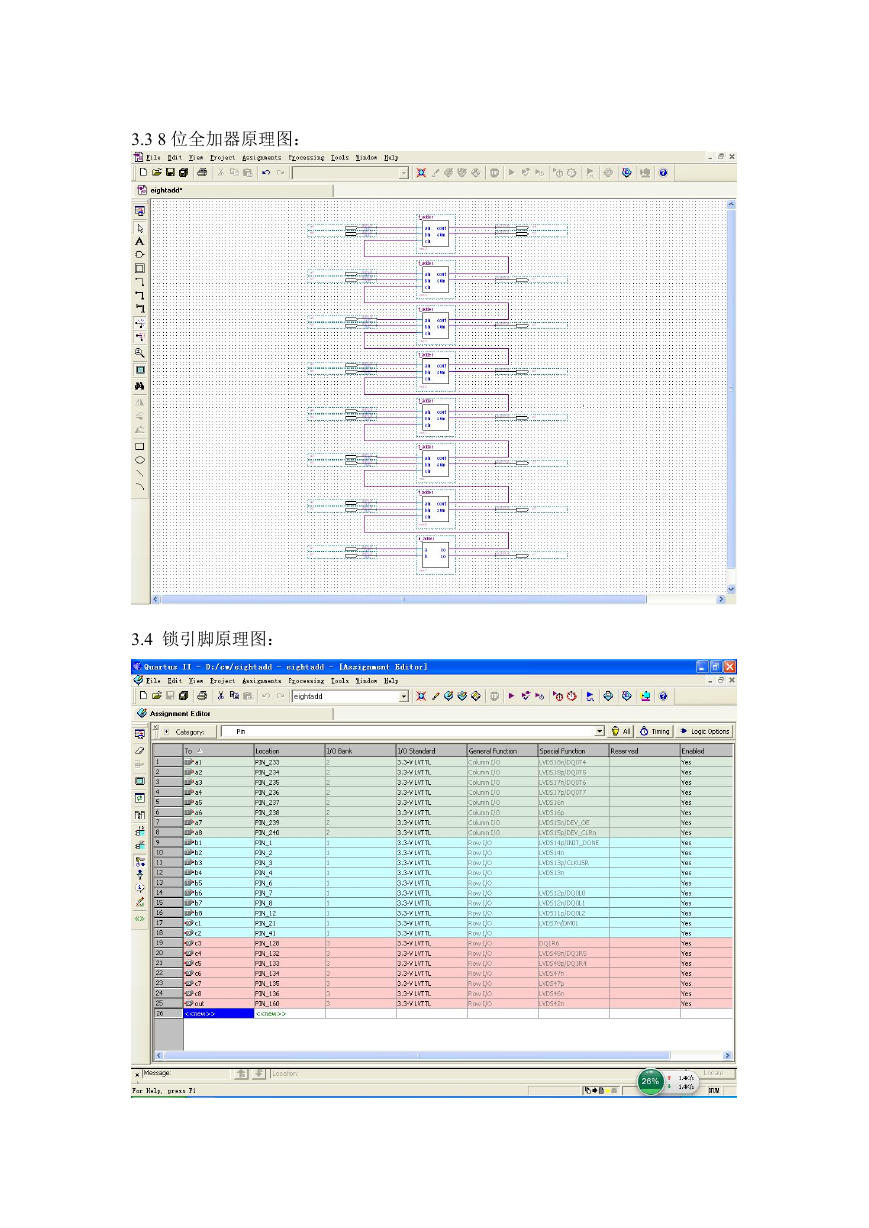

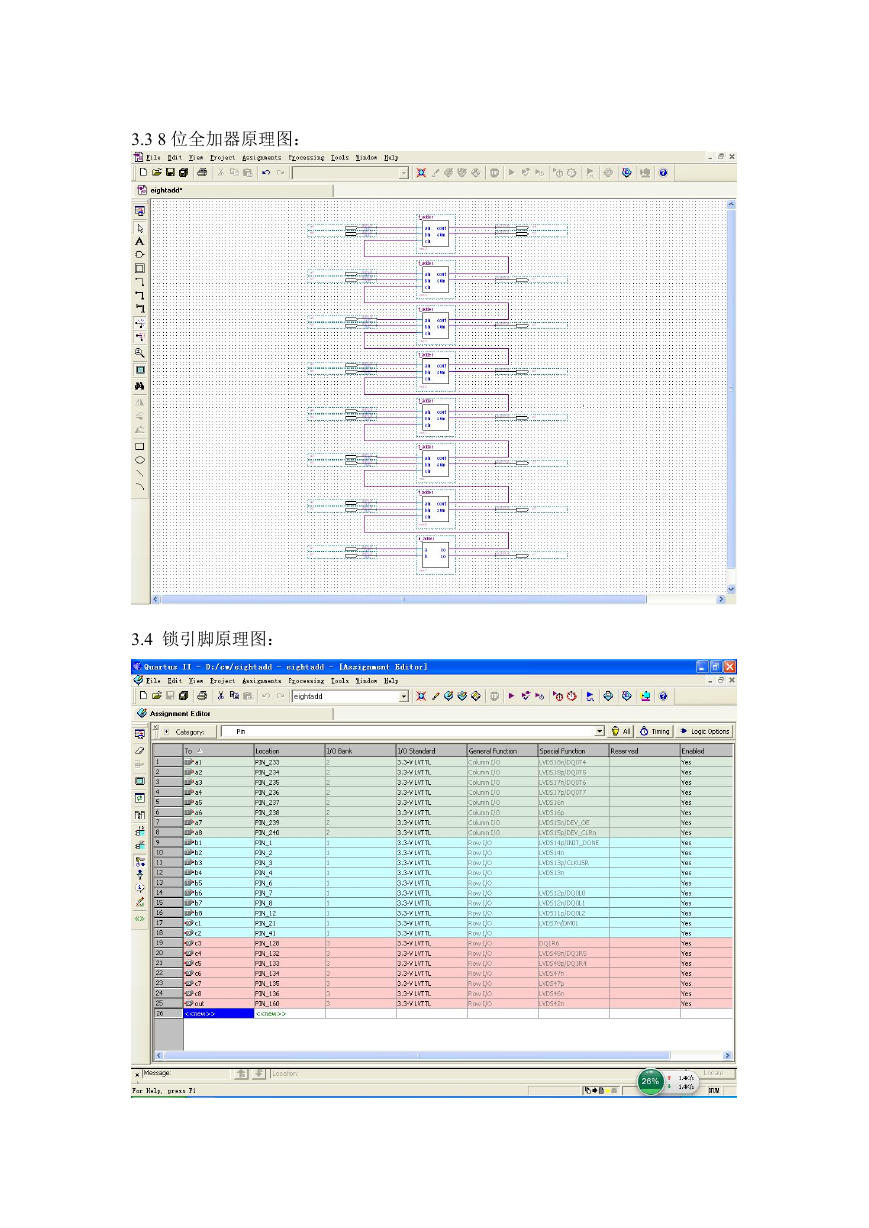

3.3 8 位全加器原理图:

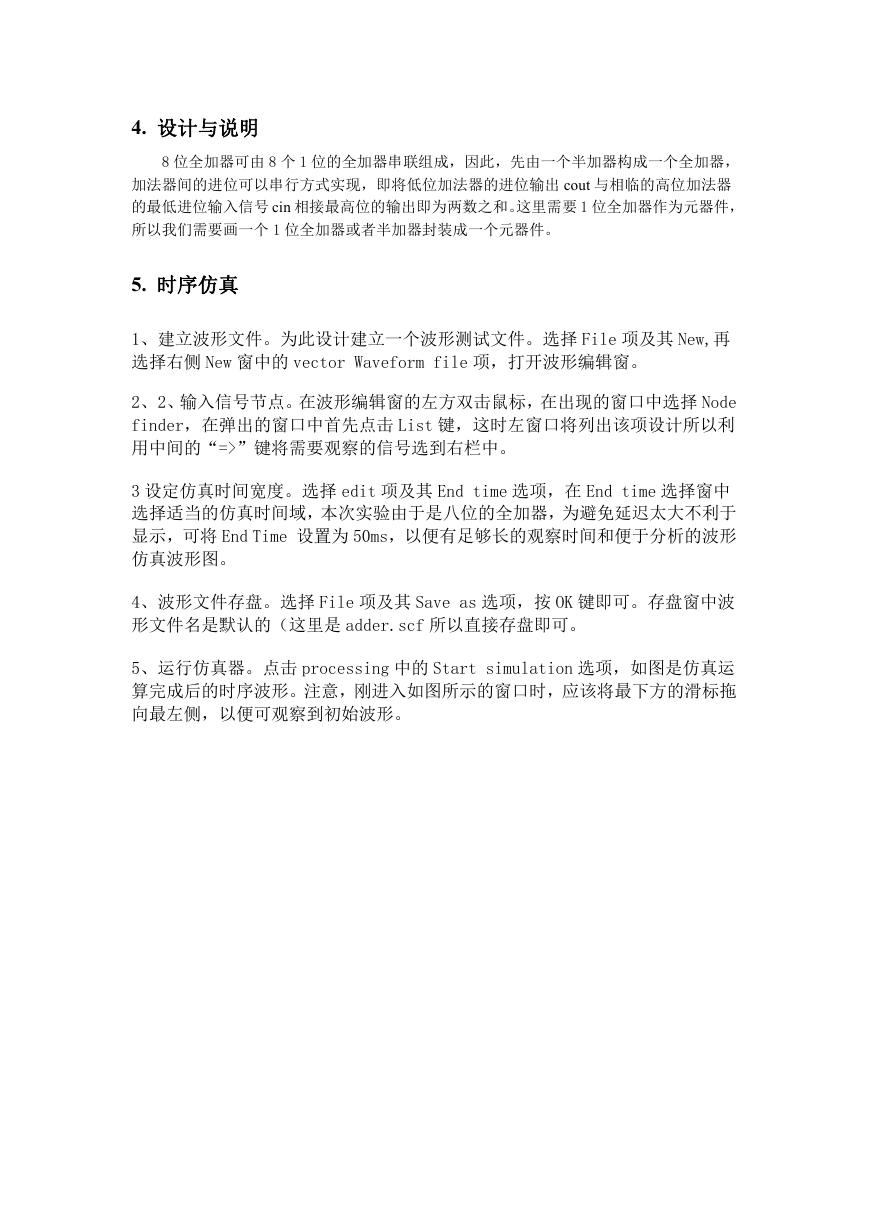

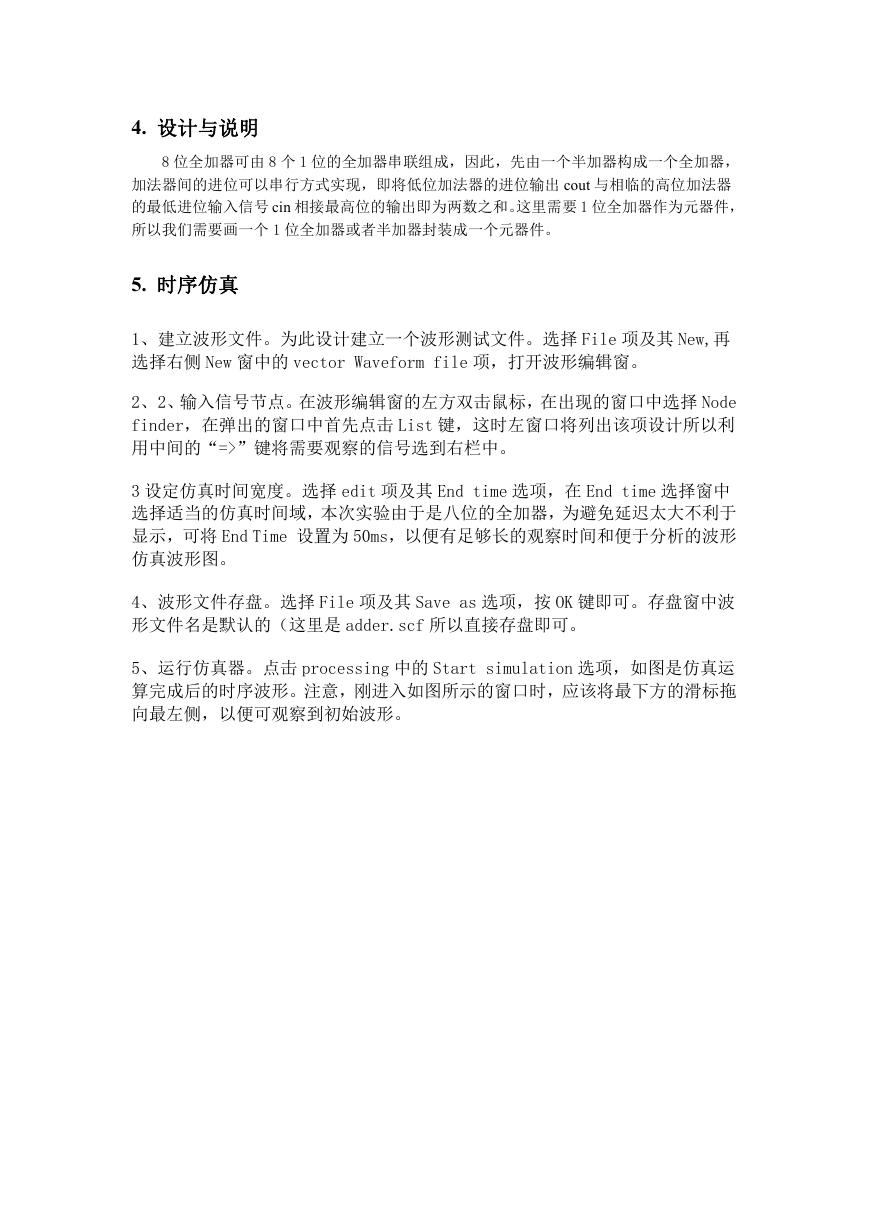

3.4 锁引脚原理图:

�

4. 设计与说明

8 位全加器可由 8 个 1 位的全加器串联组成,因此,先由一个半加器构成一个全加器,

加法器间的进位可以串行方式实现,即将低位加法器的进位输出 cout 与相临的高位加法器

的最低进位输入信号 cin 相接最高位的输出即为两数之和。这里需要 1 位全加器作为元器件,

所以我们需要画一个 1 位全加器或者半加器封装成一个元器件。

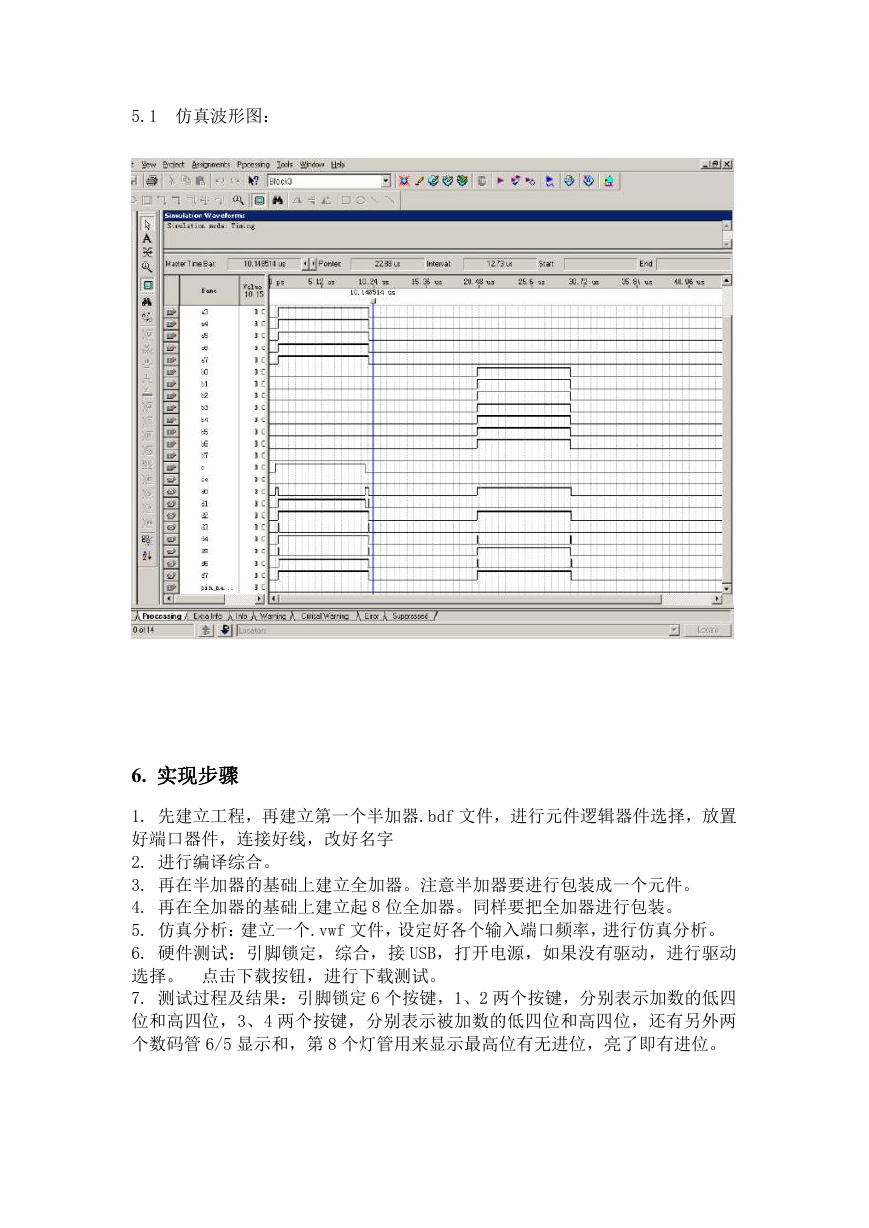

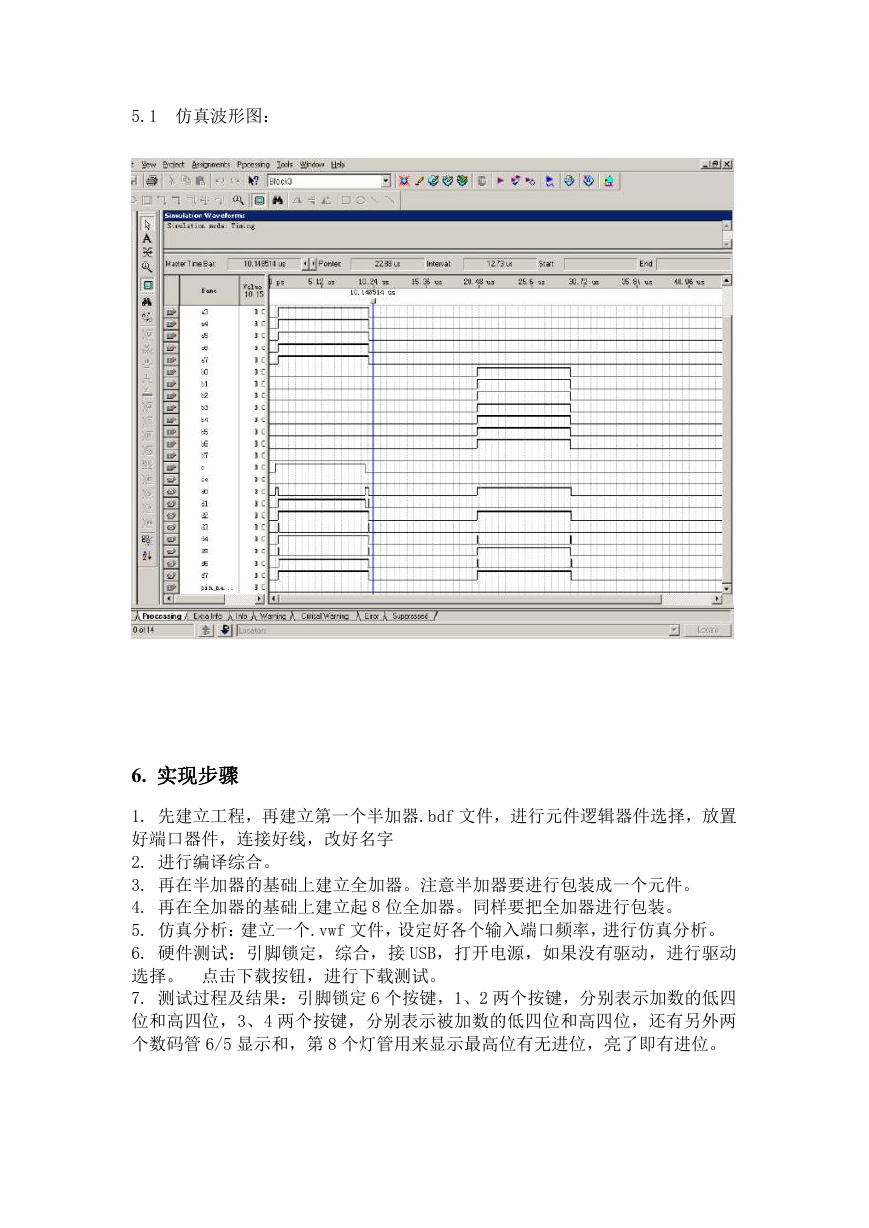

5. 时序仿真

1、建立波形文件。为此设计建立一个波形测试文件。选择 File 项及其 New,再

选择右侧 New 窗中的 vector Waveform file 项,打开波形编辑窗。

2、2、输入信号节点。在波形编辑窗的左方双击鼠标,在出现的窗口中选择 Node

finder,在弹出的窗口中首先点击 List 键,这时左窗口将列出该项设计所以利

用中间的“=>”键将需要观察的信号选到右栏中。

3 设定仿真时间宽度。选择 edit 项及其 End time 选项,在 End time 选择窗中

选择适当的仿真时间域,本次实验由于是八位的全加器,为避免延迟太大不利于

显示,可将 End Time 设置为 50ms,以便有足够长的观察时间和便于分析的波形

仿真波形图。

4、波形文件存盘。选择 File 项及其 Save as 选项,按 OK 键即可。存盘窗中波

形文件名是默认的(这里是 adder.scf 所以直接存盘即可。

5、运行仿真器。点击 processing 中的 Start simulation 选项,如图是仿真运

算完成后的时序波形。注意,刚进入如图所示的窗口时,应该将最下方的滑标拖

向最左侧,以便可观察到初始波形。

�

5.1 仿真波形图:

6. 实现步骤

1. 先建立工程,再建立第一个半加器.bdf 文件,进行元件逻辑器件选择,放置

好端口器件,连接好线,改好名字

2. 进行编译综合。

3. 再在半加器的基础上建立全加器。注意半加器要进行包装成一个元件。

4. 再在全加器的基础上建立起 8 位全加器。同样要把全加器进行包装。

5. 仿真分析:建立一个.vwf 文件,设定好各个输入端口频率,进行仿真分析。

6. 硬件测试:引脚锁定,综合,接 USB,打开电源,如果没有驱动,进行驱动

选择。 点击下载按钮,进行下载测试。

7. 测试过程及结果:引脚锁定 6 个按键,1、2 两个按键,分别表示加数的低四

位和高四位,3、4 两个按键,分别表示被加数的低四位和高四位,还有另外两

个数码管 6/5 显示和,第 8 个灯管用来显示最高位有无进位,亮了即有进位。

�

7. 设计总结:

通过本次实验,我们进一步地熟悉了利用 quartusII 的原理图输入法设计简单

的组合电路,并顺利完成通过一个八位全加器的设计。通过理论与实际相结合,

更深层次了了解了所学的知识,使其得以进一步巩固。在设计过程中也遇到一些

问题,比如:引脚锁定的时候由于模式没有选择正确,引脚锁定遇到了很大麻烦,

经过重新选择模式过后引脚可以正常锁定,并测试正确。不仅锻炼动手能力,学

习到了知识,还感受到团队合作的力量是强大的。

8. 参考文献:

[1] 潘松,潘明 《现代计算机组成原理》 科学出版社

[2] 康华光 《电子技术基础—数字部分》 高等教育出版社

[3] 张文希、谢明华《EDA 技术实验指导书》

[4] 王锁平《电子设计自动化(EDA)教程》电子科技大学出版社

附:心得总结

组员陈唯:

对于我们这样的初设计者来说每次说到从理论到实际的实践,往往感到

无从下手,还好前面有了设计 4 位加法器的经验,以及老师在实验过程中对

我们的指导,所以我们在整个过程中采取由浅入深的方法,从设计 1 位加法

器开始,不仅巩固了之前的知识,也为此次课程设计做铺垫。虽然遇到不少

问题,不过通过和组员的讨论及向老师请教基本上得以解决,不过时序仿真

还不够熟练,需加强。

通过这次设计,使我们能清楚的了解设计程序和设计步骤、设计思路和

硬件测试,最终能清晰的建立起整体概念,也为团队合作的精神感到可贵。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc