5

10

15

20

25

30

35

40

45

中国科技论文在线

http://www.paper.edu.cn

基于 FPGA 的电梯控制系统设计 #

王军华,王赛飞,方勇**

(上海大学通信与信息工程学院,上海 200444)

摘要:针对常见电梯的控制系统抗干扰性差、常见基于 FPGA 平台的电梯控制器辅助提示功能

不完善的问题,设计了该以 FPGA 平台为基准的全新电梯控制系统。该系统以 FPGA 为平台而

开发,使用 VHDL 语言,并以 Altera 公司生产的以 FPGA 为实现平台的芯片 EP2C70F896C6 作

为主控芯片,该芯片属于 CyloneⅡ系列。控制过程由执行状态切换及显示功能的状态机进程和

实现请求信号的分析、处理功能的信号灯控制进程完成。经测试,该系统实现了对各请求信号的

采集、记忆和处理,验证了该平台的稳定性和高效性,新设开或关门图案提示、提前以及延时关

门等功能,对快速开发新型电梯以及控制系统具有积极作用。

关键词:FPGA;VHDL;电梯控制;状态机

中图分类号:TN791

The design of elevator control system based on FPGA

WANG Junhua, WANG Saifei, FANG Yong

(Institute of Communication and Information Engineering, Shanghai University 200444)

Abstract: A new elevator control system based on FPGA is designed in view of the problem that the

traditional elevator control system has poor anti-interference and the function of the common FPGA

elevator controller is not complete. The system is based on Field-Programmable Gate Array (FPGA)

platform, using VHDL language, and use Altera's Cylone II Series FPGA chip EP2C70F896C6 as the

main control chip. The control process is completed by the state machine process executing state switch

and display function and the signal lamp control process for analyzing and processing the request

signal. After testing, the systeThe design of elevator control system based on FPGAm realizes the

collection, memory and processing of the request signal, verify the stability and efficiency of the

platform. The new pattern of opening and closing, and prompt advance delay closed function, has a

positive effect on the rapid development of new elevator and control system.

Keywords: FPGA; VHDL; elevator control; state machine

0 引言

随着城市化的高速发展,电梯的使用愈加广泛,电梯已经是大型商业广场、高层写字楼、立

体停车场、各档小区、酒店的必备设施。整体上分析电梯,其通常由机械动作装置和电气指令响

应与生成装置构成。钢丝绳与滑轮装置构成牵引系统、轿厢与铁门组成承载系统、梯井中的配重

组成平衡系统以及由减震弹簧构成的机械保护系统等部分组成[1];而电气指令响应与生成装置由

电机拖动模块、工作状态逻辑控制模块等分支构成。对于一部运转正常的电梯来说,最核心的部

分是控制系统。

依据当前控制领域的发展进度,实现对电梯的控制主要有以下两种方法,其一是基于微型计

算机的控制方法,还可以采用基于单板机和单片机的控制以及人工智能控制等[2];另一种是基于

FPGA 的控制实现。尽管微机控制系统具有出色的智能与模糊控制优势,但是该系统由于工艺问

题,导致其在抗干扰性方面存在致命短板,并且技术实现相对复杂、后台算法晦涩难懂,不利于

后期的维护与维修[3]。而 FPGA 控制系统相对微机化控制来说,由于运行可靠性高,使用维修方

便,抗干扰性强,开发和测试时间不长等优势,已成为市场上核心地电梯控制实现方式。

常见 FPGA 控制器的功能单一,仅能实现开关门、上行下载过程,不能提供良好的人性化功

基金项目:国家自然基金(61271213,61673253);国家教育部博士点基金(20133108110014)

作者简介:王军华(1973-),男,副教授、硕导,主要研究方向:通信信号处理

通信联系人:方勇(1964-),教授、博导,主要研究方向:通信信号处理. E-mail: yfang@staff.shu.edu.cn

- 1 -

�

中国科技论文在线

http://www.paper.edu.cn

能设计以及便利的后期维修保养功能,且大多采用严重落伍的硬件设备进行仿真。软件实现方面,

后台程序设计混乱,可扩展性极差,代码冗余度偏高。本文借助最新型 FPGA 器件实现了对于整

个系统的控制功能,应用 VHDL 语言开发了一套 n 楼层的电梯控制系统,该控制系统目前只针

对单个载客轿厢,且整个实体使用模块化编程,易于使用和维护,能完成对任意多层的电梯控制。

1 电梯控制系统的总体设计

1.1 系统功能要求

n 层电梯控制器的设计要求如下:

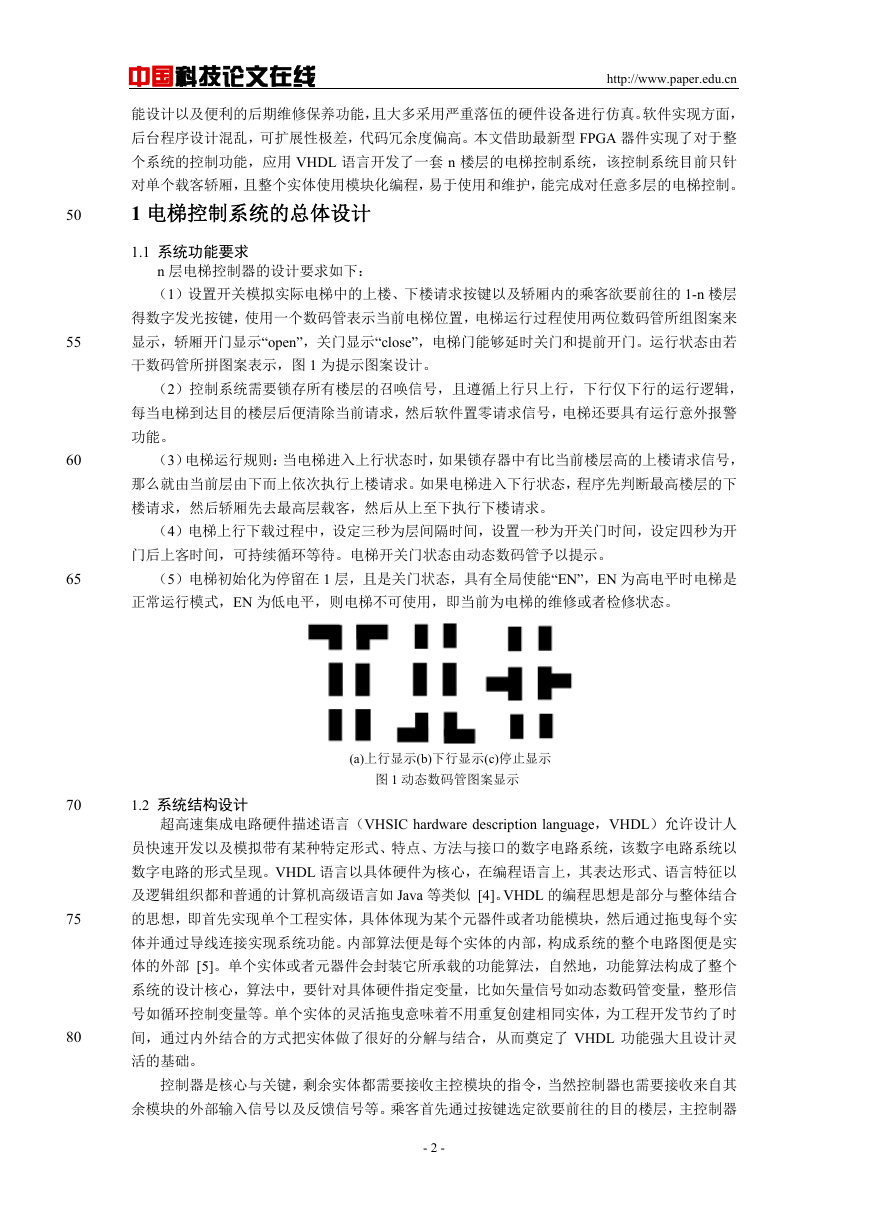

(1)设置开关模拟实际电梯中的上楼、下楼请求按键以及轿厢内的乘客欲要前往的 1-n 楼层

得数字发光按键,使用一个数码管表示当前电梯位置,电梯运行过程使用两位数码管所组图案来

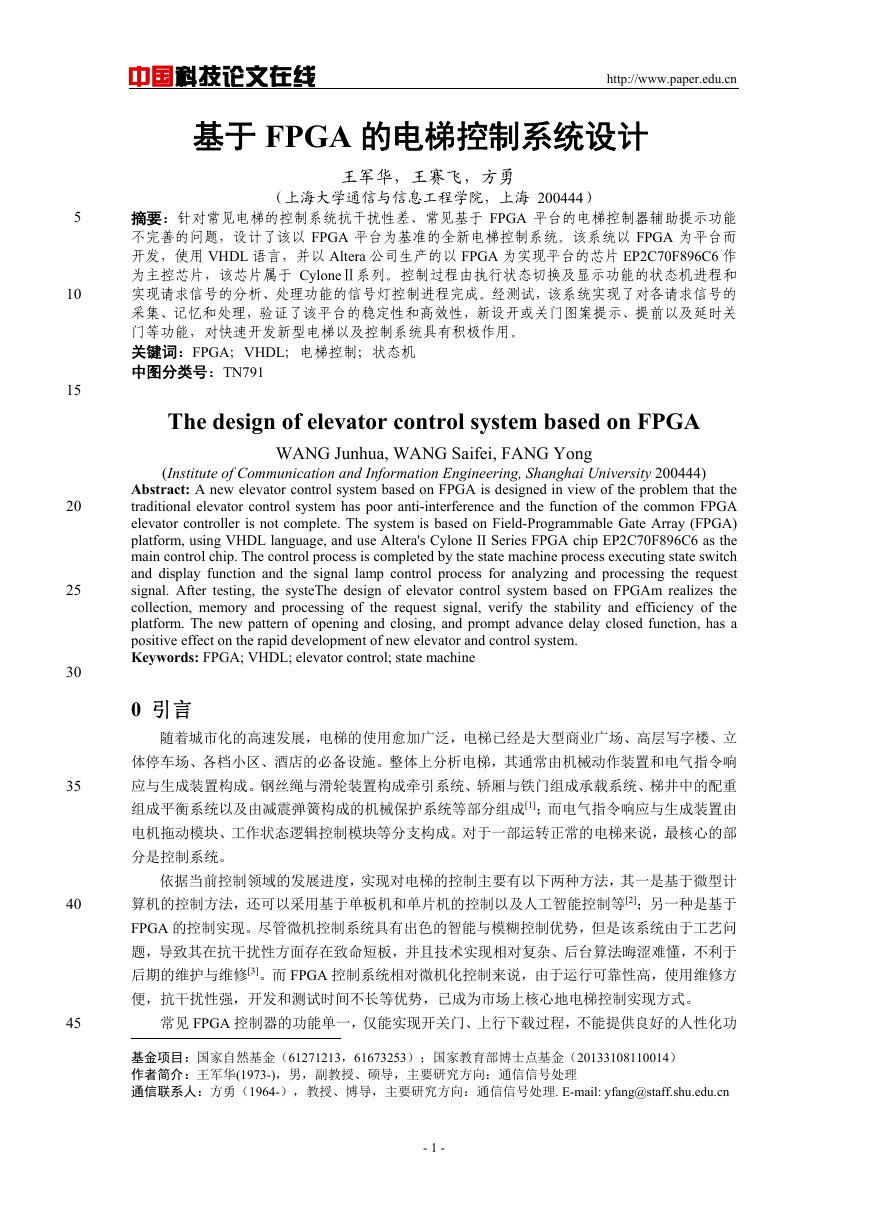

显示,轿厢开门显示“open”,关门显示“close”,电梯门能够延时关门和提前开门。运行状态由若

干数码管所拼图案表示,图 1 为提示图案设计。

(2)控制系统需要锁存所有楼层的召唤信号,且遵循上行只上行,下行仅下行的运行逻辑,

每当电梯到达目的楼层后便清除当前请求,然后软件置零请求信号,电梯还要具有运行意外报警

功能。

(3)电梯运行规则:当电梯进入上行状态时,如果锁存器中有比当前楼层高的上楼请求信号,

那么就由当前层由下而上依次执行上楼请求。如果电梯进入下行状态,程序先判断最高楼层的下

楼请求,然后轿厢先去最高层载客,然后从上至下执行下楼请求。

(4)电梯上行下载过程中,设定三秒为层间隔时间,设置一秒为开关门时间,设定四秒为开

门后上客时间,可持续循环等待。电梯开关门状态由动态数码管予以提示。

(5)电梯初始化为停留在 1 层,且是关门状态,具有全局使能“EN”,EN 为高电平时电梯是

正常运行模式,EN 为低电平,则电梯不可使用,即当前为电梯的维修或者检修状态。

(a)上行显示(b)下行显示(c)停止显示

图 1 动态数码管图案显示

1.2 系统结构设计

超高速集成电路硬件描述语言(VHSIC hardware description language,VHDL)允许设计人

员快速开发以及模拟带有某种特定形式、特点、方法与接口的数字电路系统,该数字电路系统以

数字电路的形式呈现。VHDL 语言以具体硬件为核心,在编程语言上,其表达形式、语言特征以

及逻辑组织都和普通的计算机高级语言如 Java 等类似 [4]。VHDL 的编程思想是部分与整体结合

的思想,即首先实现单个工程实体,具体体现为某个元器件或者功能模块,然后通过拖曳每个实

体并通过导线连接实现系统功能。内部算法便是每个实体的内部,构成系统的整个电路图便是实

体的外部 [5]。单个实体或者元器件会封装它所承载的功能算法,自然地,功能算法构成了整个

系统的设计核心,算法中,要针对具体硬件指定变量,比如矢量信号如动态数码管变量,整形信

号如循环控制变量等。单个实体的灵活拖曳意味着不用重复创建相同实体,为工程开发节约了时

间,通过内外结合的方式把实体做了很好的分解与结合,从而奠定了 VHDL 功能强大且设计灵

活的基础。

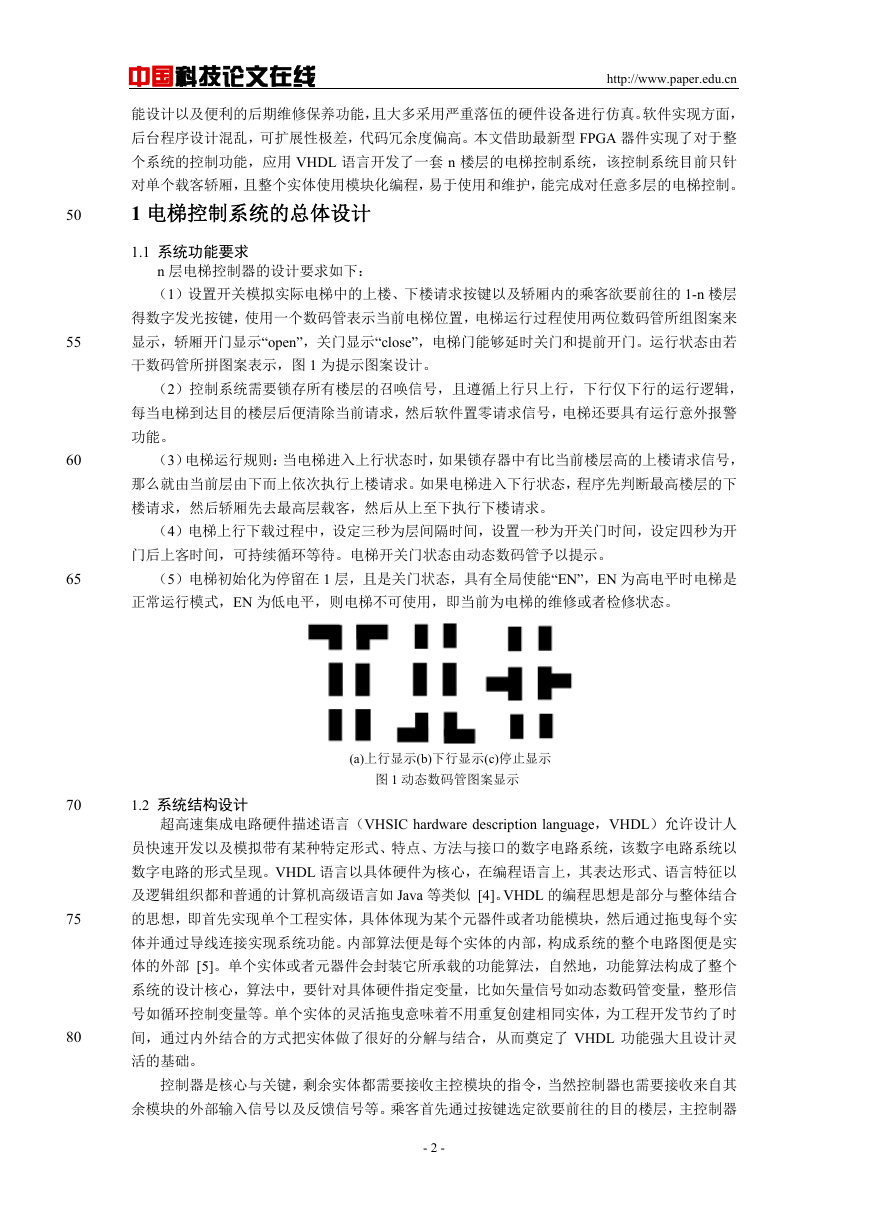

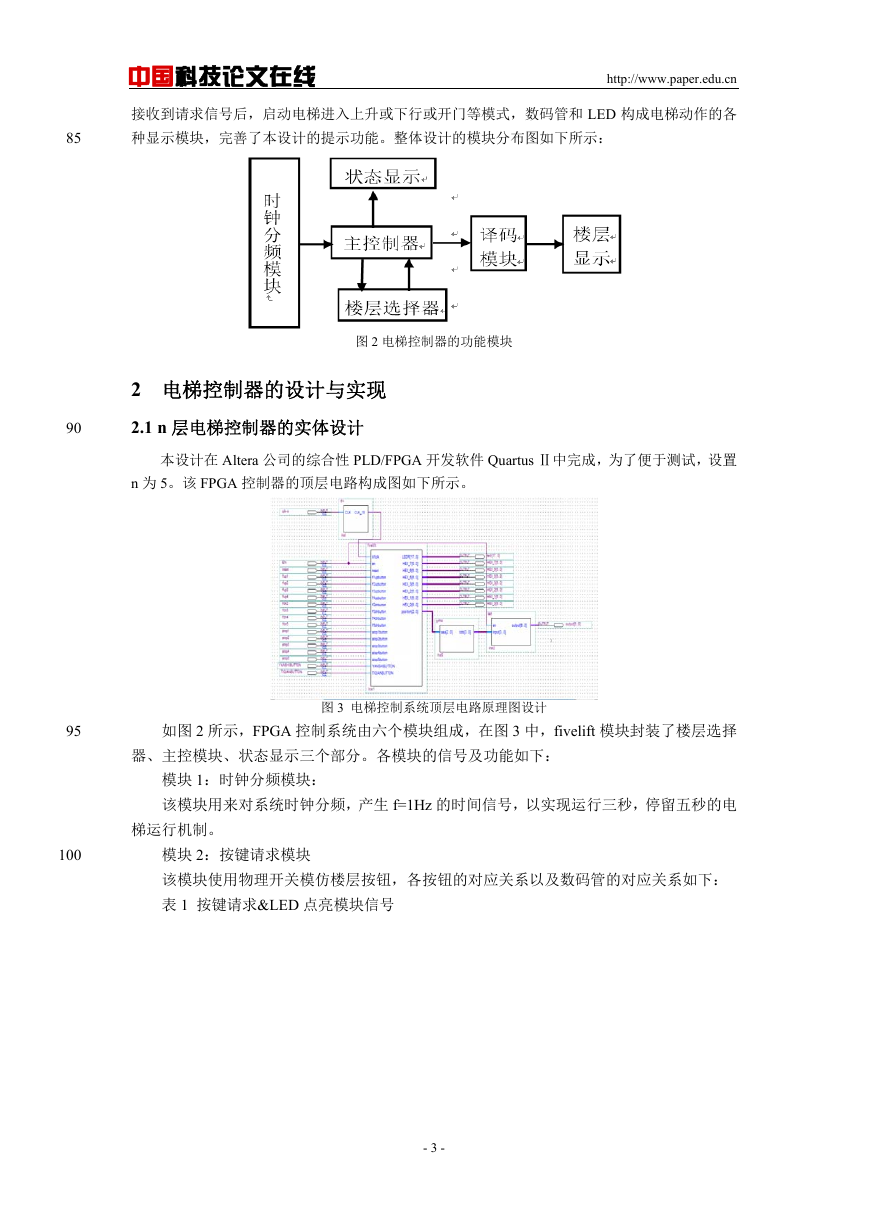

控制器是核心与关键,剩余实体都需要接收主控模块的指令,当然控制器也需要接收来自其

余模块的外部输入信号以及反馈信号等。乘客首先通过按键选定欲要前往的目的楼层,主控制器

- 2 -

50

55

60

65

70

75

80

�

中国科技论文在线

http://www.paper.edu.cn

接收到请求信号后,启动电梯进入上升或下行或开门等模式,数码管和 LED 构成电梯动作的各

种显示模块,完善了本设计的提示功能。整体设计的模块分布图如下所示:

85

图 2 电梯控制器的功能模块

2 电梯控制器的设计与实现

2.1 n 层电梯控制器的实体设计

90

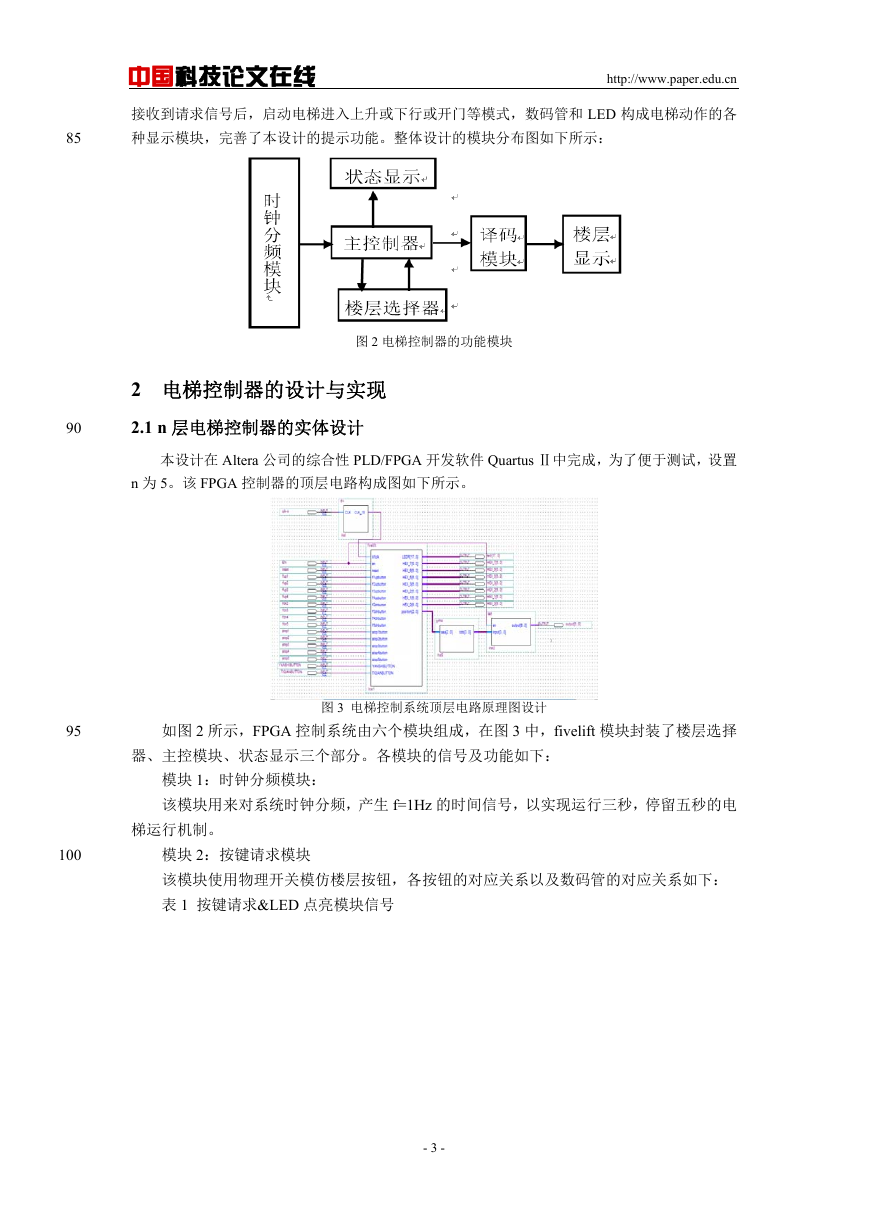

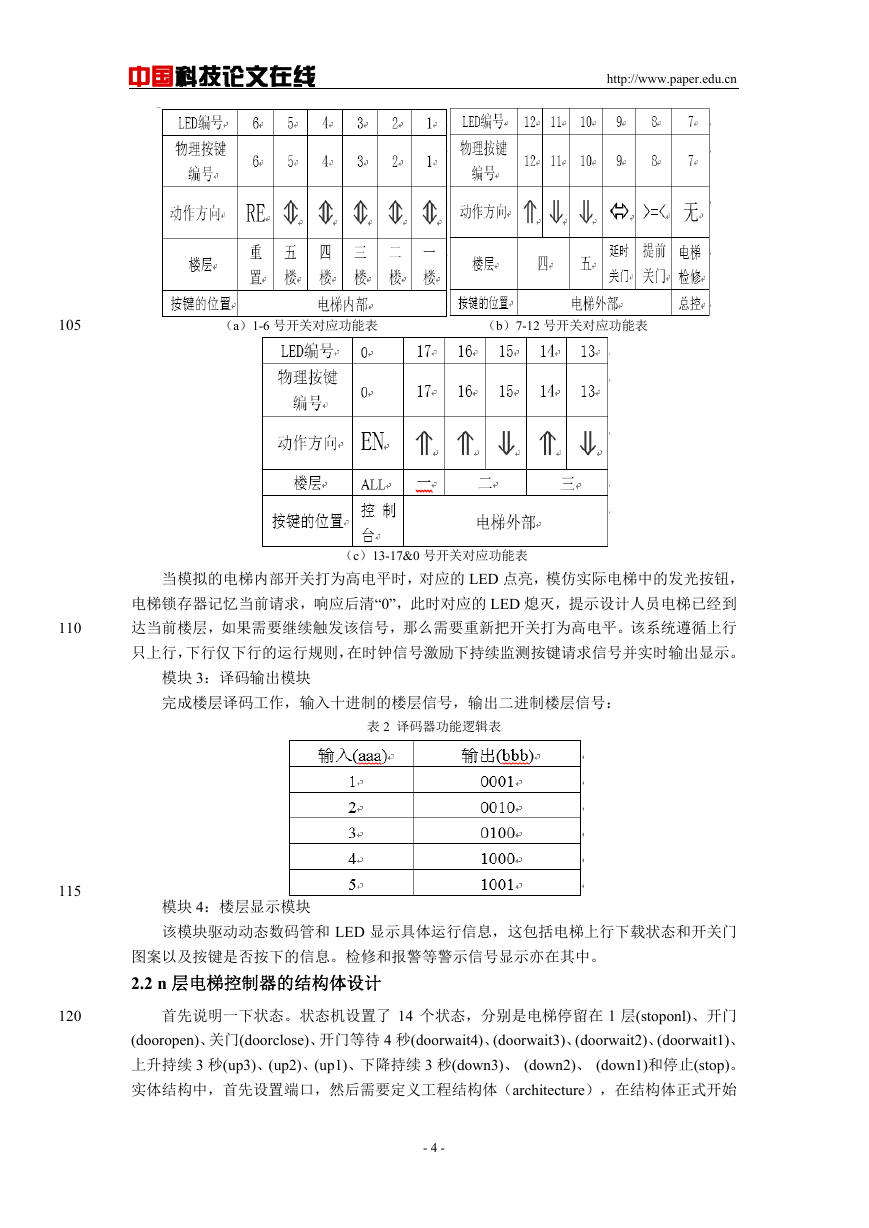

本设计在 Altera 公司的综合性 PLD/FPGA 开发软件 Quartus Ⅱ中完成,为了便于测试,设置

n 为 5。该 FPGA 控制器的顶层电路构成图如下所示。

图 3 电梯控制系统顶层电路原理图设计

95

如图 2 所示,FPGA 控制系统由六个模块组成,在图 3 中,fivelift 模块封装了楼层选择

器、主控模块、状态显示三个部分。各模块的信号及功能如下:

模块 1:时钟分频模块:

该模块用来对系统时钟分频,产生 f=1Hz 的时间信号,以实现运行三秒,停留五秒的电

梯运行机制。

100

模块 2:按键请求模块

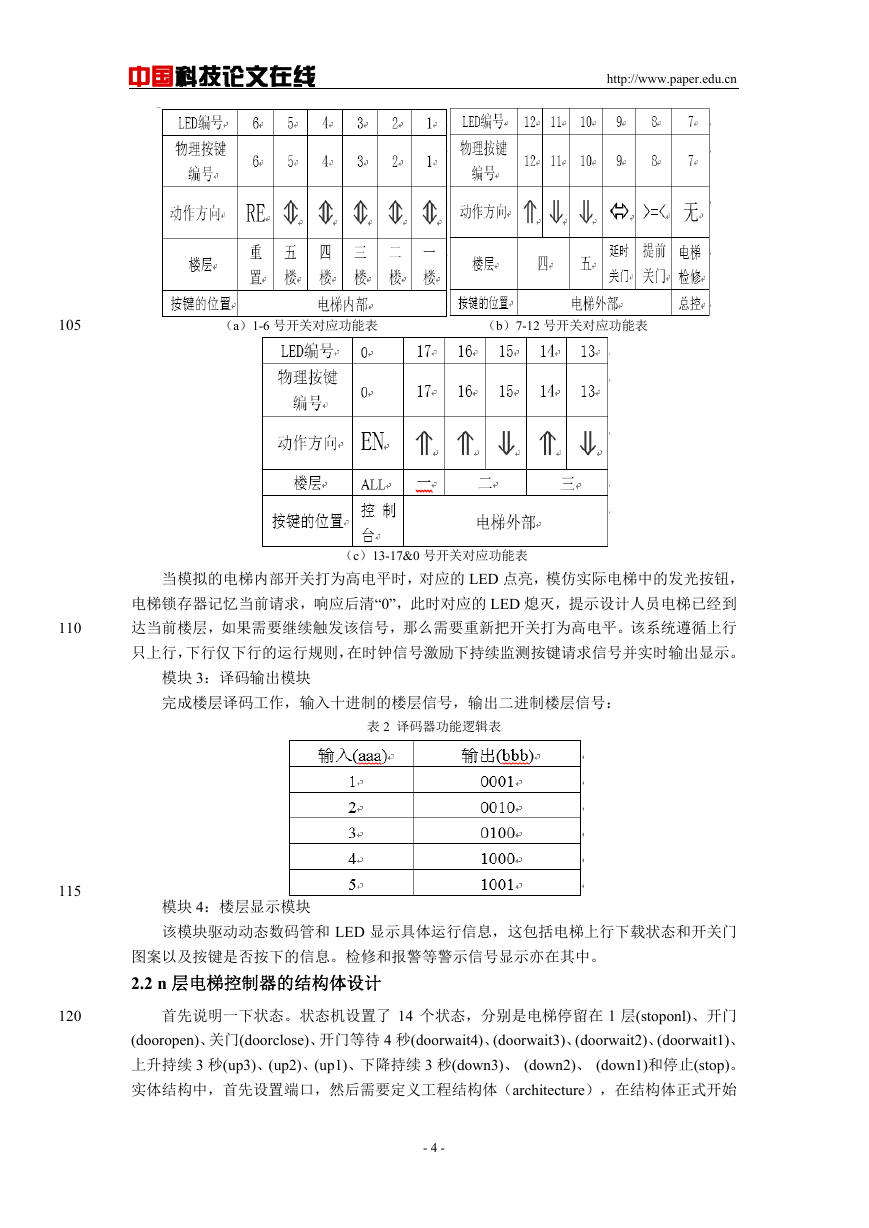

该模块使用物理开关模仿楼层按钮,各按钮的对应关系以及数码管的对应关系如下:

表 1 按键请求&LED 点亮模块信号

- 3 -

�

中国科技论文在线

http://www.paper.edu.cn

105

(a)1-6 号开关对应功能表 (b)7-12 号开关对应功能表

(c)13-17&0 号开关对应功能表

当模拟的电梯内部开关打为高电平时,对应的 LED 点亮,模仿实际电梯中的发光按钮,

电梯锁存器记忆当前请求,响应后清“0”,此时对应的 LED 熄灭,提示设计人员电梯已经到

达当前楼层,如果需要继续触发该信号,那么需要重新把开关打为高电平。该系统遵循上行

只上行,下行仅下行的运行规则,在时钟信号激励下持续监测按键请求信号并实时输出显示。

110

模块 3:译码输出模块

完成楼层译码工作,输入十进制的楼层信号,输出二进制楼层信号:

表 2 译码器功能逻辑表

115

120

模块 4:楼层显示模块

该模块驱动动态数码管和 LED 显示具体运行信息,这包括电梯上行下载状态和开关门

图案以及按键是否按下的信息。检修和报警等警示信号显示亦在其中。

2.2 n 层电梯控制器的结构体设计

首先说明一下状态。状态机设置了 14 个状态,分别是电梯停留在 l 层(stoponl)、开门

(dooropen)、关门(doorclose)、开门等待 4 秒(doorwait4)、(doorwait3)、(doorwait2)、(doorwait1)、

上升持续 3 秒(up3)、(up2)、(up1)、下降持续 3 秒(down3)、 (down2)、 (down1)和停止(stop)。

实体结构中,首先设置端口,然后需要定义工程结构体(architecture),在结构体正式开始

- 4 -

�

125

中国科技论文在线

http://www.paper.edu.cn

is

( begin ) 之 前 , 需 要 先 定 义 本 设 计 所 需 的 所 有 状 态 机 : type

(stopon1,dooropen,dooclose,doorwait4, doorwait3, doorwait2,doorwait1,up3, up2, up1, down3,

down2, down1,stop);结构体(architecture)主要有两个进程构成,状态机进程需完成各个状

态间切换,是核心进程[5]。信号灯进程负责采集、存储、输出各种请求信号,为状态机切

换状态提供激励,是次要进程。状态机进程接收信号灯进程信号同时会给予其反馈信号,以

控制按键及数码管等的熄灭并清除已动作过的请求信号。

lift state

130

在状态机[6]进程中,在电梯下降状态中,通过对信号灯的判断,决定下一个状态是继

续下降还是停止,上升状态与下降状态原理相同;在所有请求信号响应结束后,电梯进入侯

135

140

145

150

客状态,即状态机需要完成状态切换,同时程序会不断扫描是否有请求信号被触发,一旦外

界出现请求,那么电梯会立即进入上行或下载状态。在状态机进程中,按键后产生的点亮的

信号灯(逻辑值为‘1’)用于作为状态机进程中的判断条件,是程序执行的指令源。‘EN’开关控

制数码管是否显示系统预设内容。逻辑值为‘1’显示电梯状态信息,逻辑值为‘0’显示特设的

八位数字“12015480”。

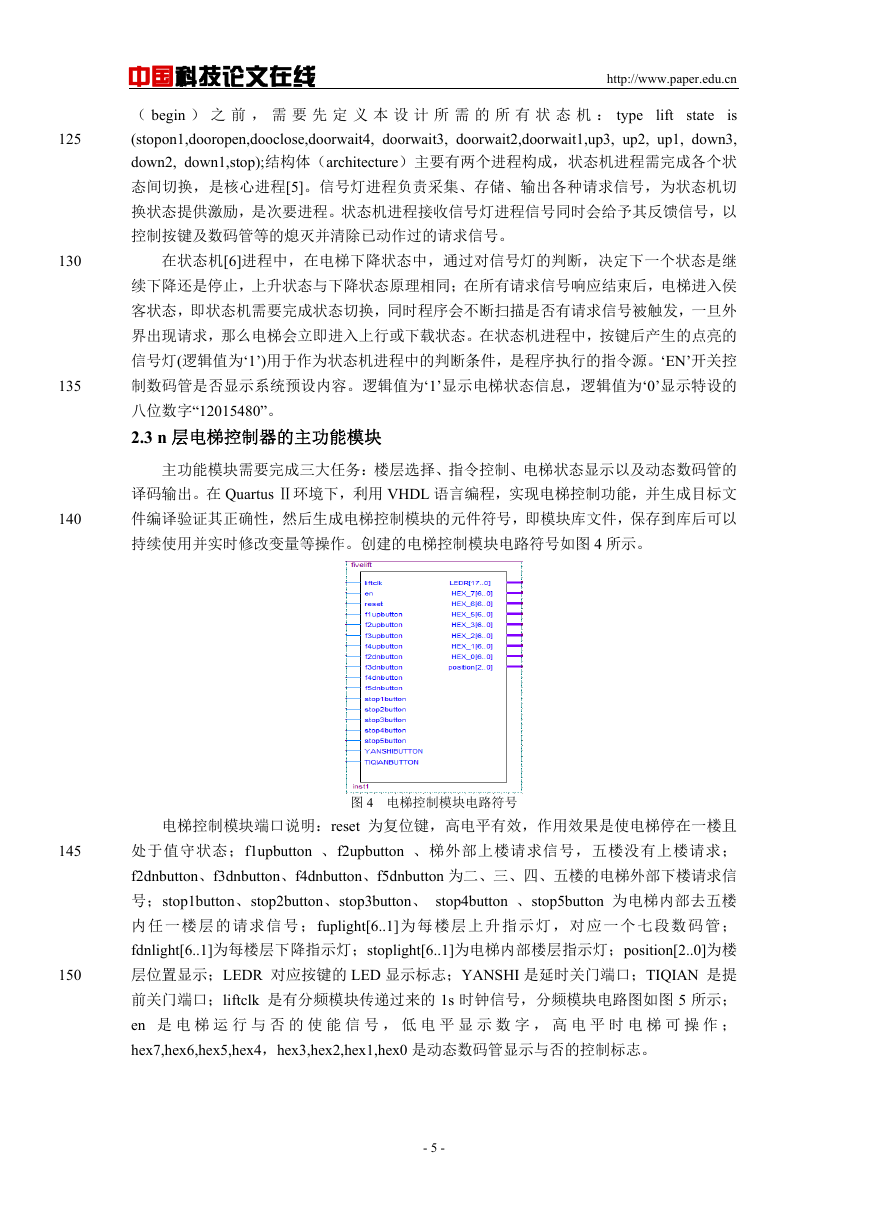

2.3 n 层电梯控制器的主功能模块

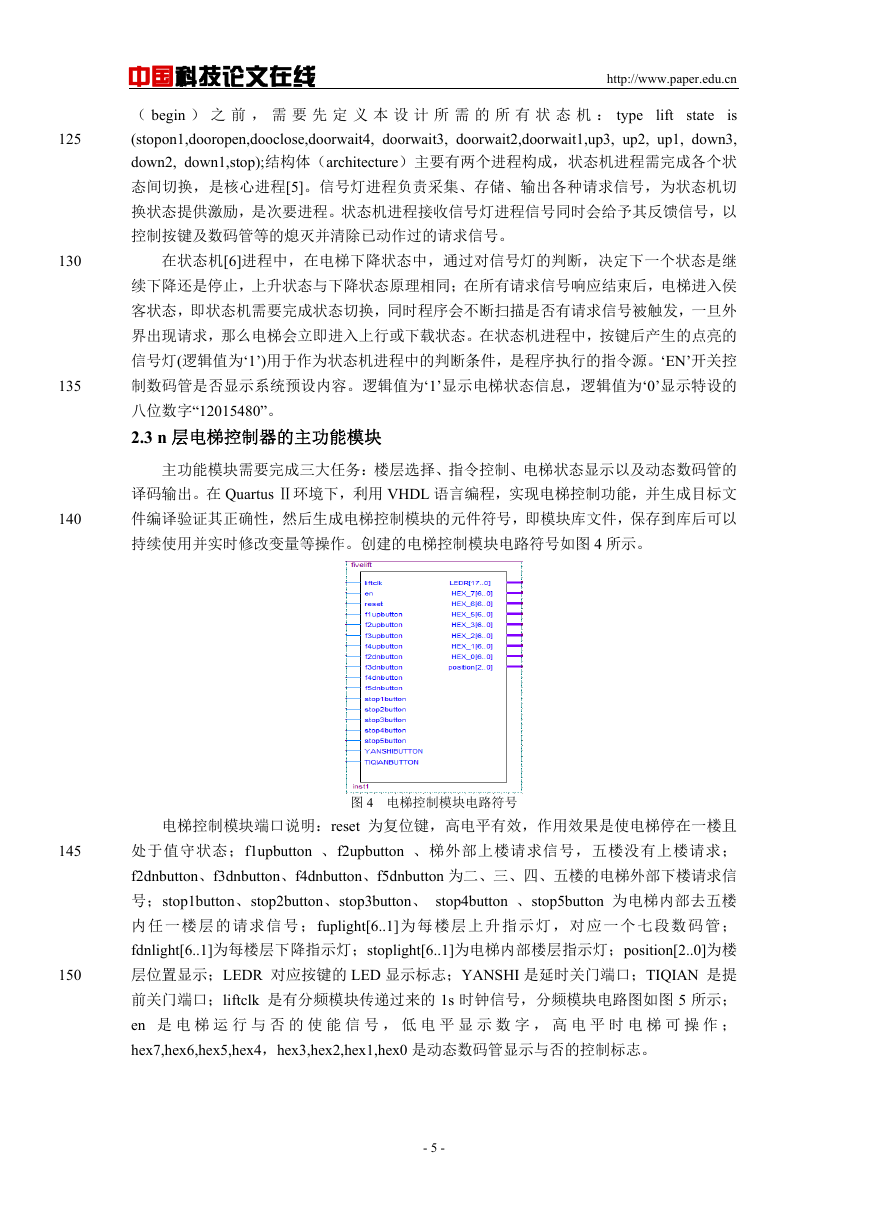

主功能模块需要完成三大任务:楼层选择、指令控制、电梯状态显示以及动态数码管的

译码输出。在 Quartus Ⅱ环境下,利用 VHDL 语言编程,实现电梯控制功能,并生成目标文

件编译验证其正确性,然后生成电梯控制模块的元件符号,即模块库文件,保存到库后可以

持续使用并实时修改变量等操作。创建的电梯控制模块电路符号如图 4 所示。

图 4 电梯控制模块电路符号

电梯控制模块端口说明:reset 为复位键,高电平有效,作用效果是使电梯停在一楼且

处于值守状态;f1upbutton 、f2upbutton 、梯外部上楼请求信号,五楼没有上楼请求;

f2dnbutton、f3dnbutton、f4dnbutton、f5dnbutton 为二、三、四、五楼的电梯外部下楼请求信

号;stop1button、stop2button、stop3button、 stop4button 、stop5button 为电梯内部去五楼

内 任 一 楼 层 的 请 求 信 号 ;fuplight[6..1]为 每 楼 层 上 升 指 示 灯 , 对 应 一 个 七 段 数 码 管 ;

fdnlight[6..1]为每楼层下降指示灯;stoplight[6..1]为电梯内部楼层指示灯;position[2..0]为楼

层位置显示;LEDR 对应按键的 LED 显示标志;YANSHI 是延时关门端口;TIQIAN 是提

前关门端口;liftclk 是有分频模块传递过来的 1s 时钟信号,分频模块电路图如图 5 所示;

en 是 电 梯 运 行 与 否 的 使 能 信 号 , 低 电 平 显 示 数 字 , 高 电 平 时 电 梯 可 操 作 ;

hex7,hex6,hex5,hex4,hex3,hex2,hex1,hex0 是动态数码管显示与否的控制标志。

- 5 -

�

中国科技论文在线

http://www.paper.edu.cn

155

160

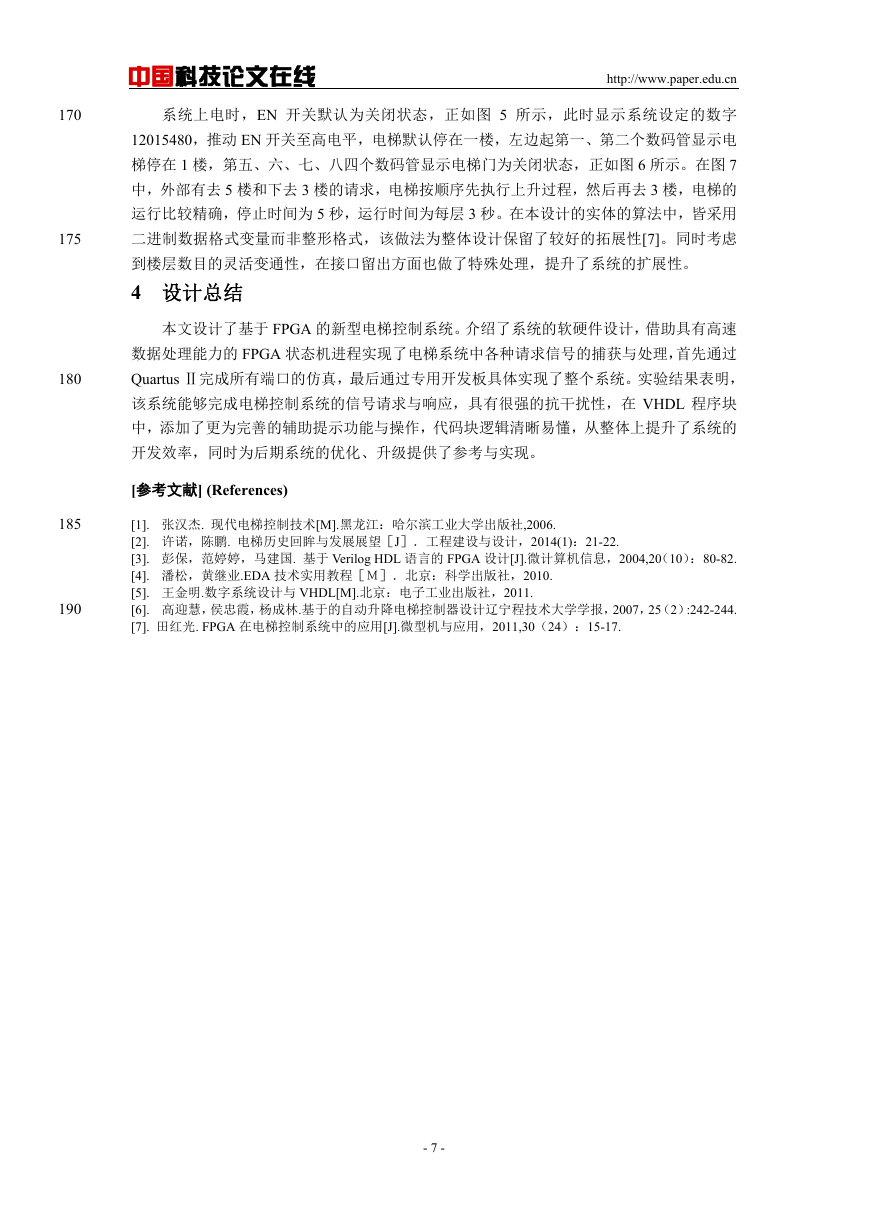

3 电梯控制程序的硬件验证

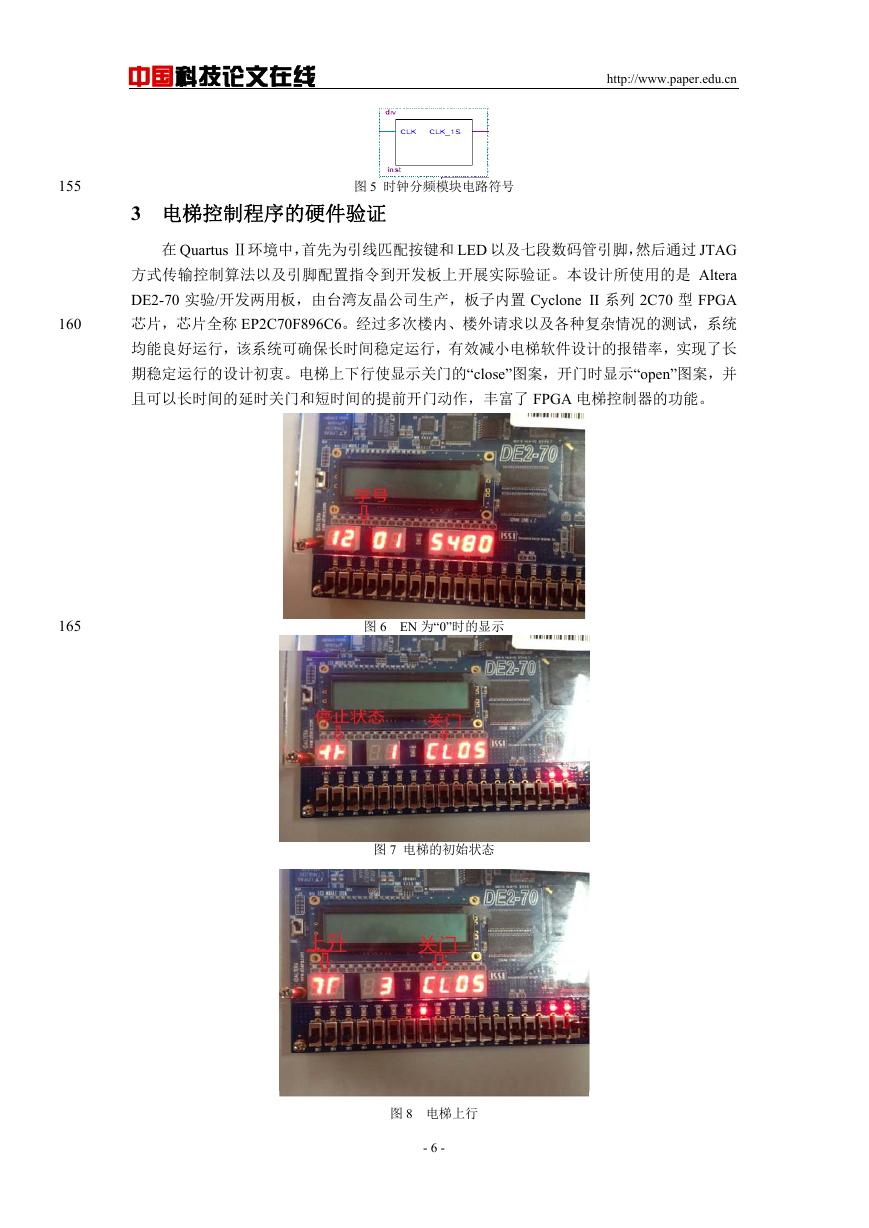

图 5 时钟分频模块电路符号

在 Quartus Ⅱ环境中,首先为引线匹配按键和 LED 以及七段数码管引脚,然后通过 JTAG

方式传输控制算法以及引脚配置指令到开发板上开展实际验证。本设计所使用的是 Altera

DE2-70 实验/开发两用板,由台湾友晶公司生产,板子内置 Cyclone II 系列 2C70 型 FPGA

芯片,芯片全称 EP2C70F896C6。经过多次楼内、楼外请求以及各种复杂情况的测试,系统

均能良好运行,该系统可确保长时间稳定运行,有效减小电梯软件设计的报错率,实现了长

期稳定运行的设计初衷。电梯上下行使显示关门的“close”图案,开门时显示“open”图案,并

且可以长时间的延时关门和短时间的提前开门动作,丰富了 FPGA 电梯控制器的功能。

165

图 6 EN 为“0”时的显示

图 7 电梯的初始状态

图 8 电梯上行

- 6 -

�

中国科技论文在线

http://www.paper.edu.cn

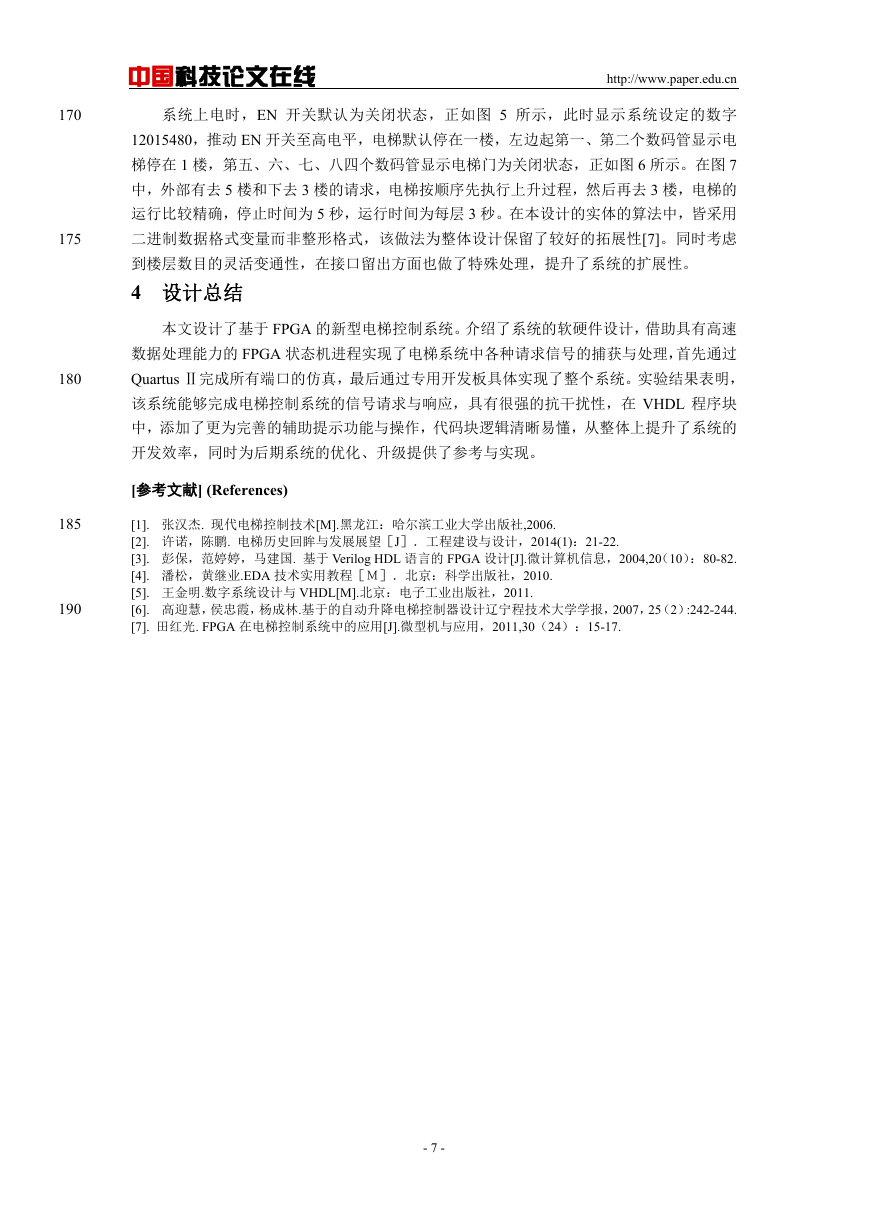

系统上电时,EN 开关默认为关闭状态,正如图 5 所示,此时显示系统设定的数字

12015480,推动 EN 开关至高电平,电梯默认停在一楼,左边起第一、第二个数码管显示电

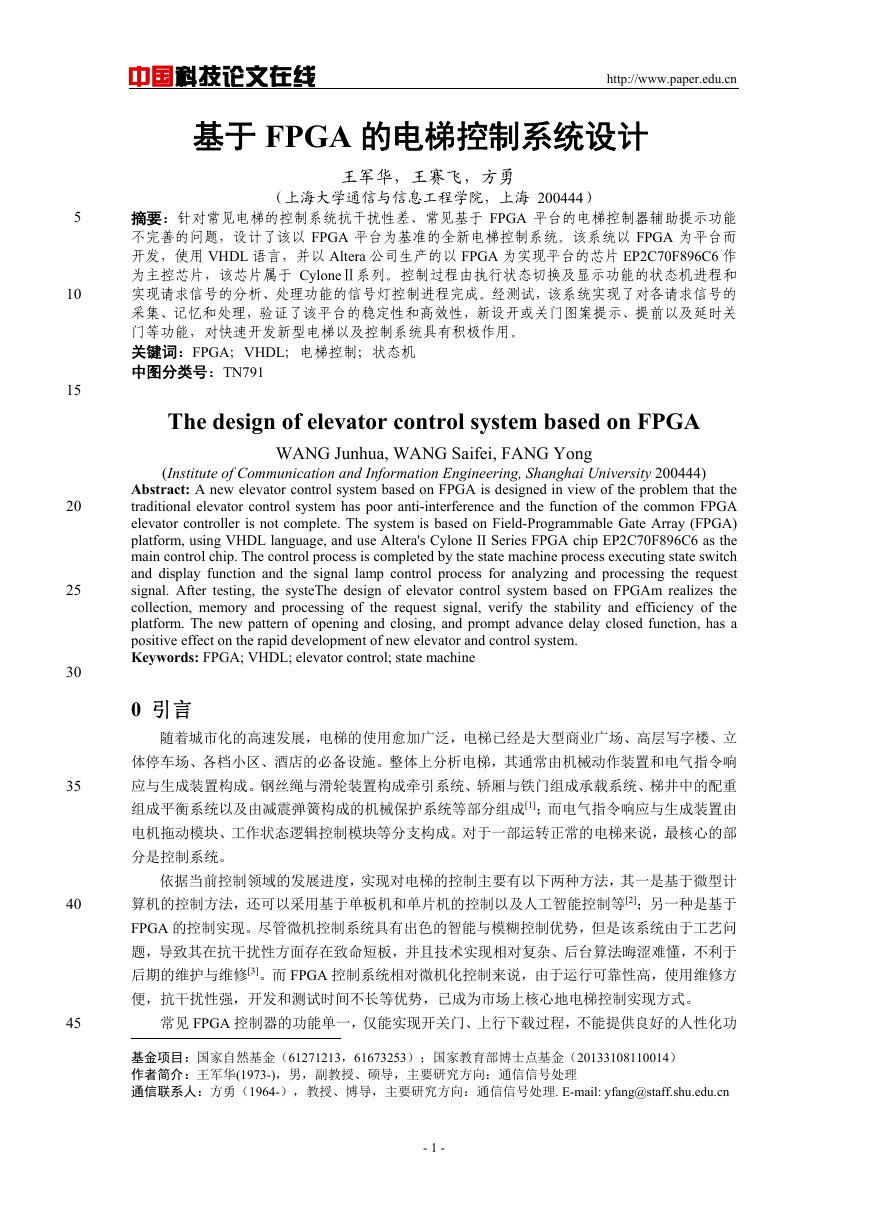

梯停在 1 楼,第五、六、七、八四个数码管显示电梯门为关闭状态,正如图 6 所示。在图 7

中,外部有去 5 楼和下去 3 楼的请求,电梯按顺序先执行上升过程,然后再去 3 楼,电梯的

运行比较精确,停止时间为 5 秒,运行时间为每层 3 秒。在本设计的实体的算法中,皆采用

二进制数据格式变量而非整形格式,该做法为整体设计保留了较好的拓展性[7]。同时考虑

到楼层数目的灵活变通性,在接口留出方面也做了特殊处理,提升了系统的扩展性。

4 设计总结

本文设计了基于 FPGA 的新型电梯控制系统。介绍了系统的软硬件设计,借助具有高速

数据处理能力的 FPGA 状态机进程实现了电梯系统中各种请求信号的捕获与处理,首先通过

Quartus Ⅱ完成所有端口的仿真,最后通过专用开发板具体实现了整个系统。实验结果表明,

该系统能够完成电梯控制系统的信号请求与响应,具有很强的抗干扰性,在 VHDL 程序块

中,添加了更为完善的辅助提示功能与操作,代码块逻辑清晰易懂,从整体上提升了系统的

开发效率,同时为后期系统的优化、升级提供了参考与实现。

[参考文献] (References)

[1]. 张汉杰. 现代电梯控制技术[M].黑龙江:哈尔滨工业大学出版社,2006.

[2]. 许诺,陈鹏. 电梯历史回眸与发展展望[J].工程建设与设计,2014(1):21-22.

[3]. 彭保,范婷婷,马建国. 基于 Verilog HDL 语言的 FPGA 设计[J].微计算机信息,2004,20(10):80-82.

[4]. 潘松,黄继业.EDA 技术实用教程[M].北京:科学出版社,2010.

[5]. 王金明.数字系统设计与 VHDL[M].北京:电子工业出版社,2011.

[6]. 高迎慧,侯忠霞,杨成林.基于的自动升降电梯控制器设计辽宁程技术大学学报,2007,25(2):242-244.

[7]. 田红光. FPGA 在电梯控制系统中的应用[J].微型机与应用,2011,30(24):15-17.

170

175

180

185

190

- 7 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc