Title Page

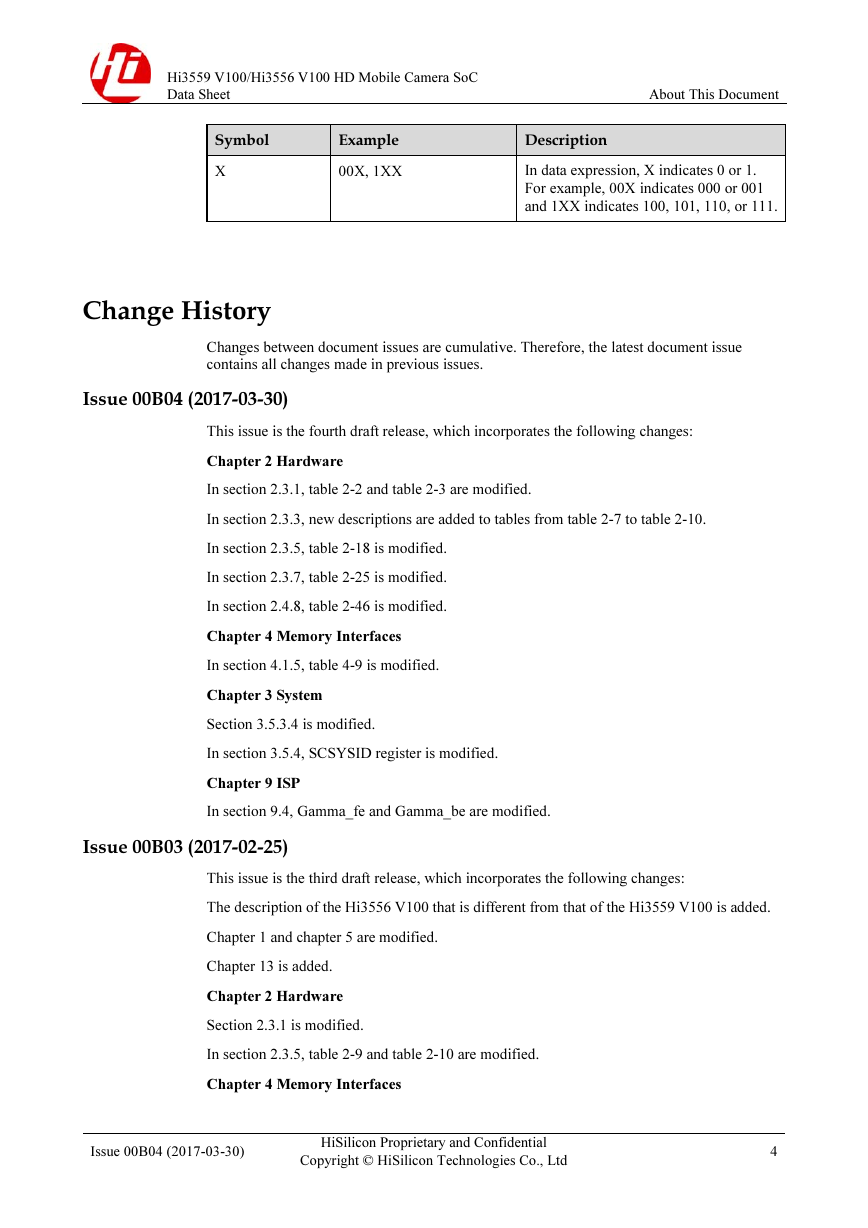

About This Document

1 Product Description

Contents

Figures

Tables

1.1 Hi3559 V100 Description

1.2 Hi3556 V100 Description

1.3 Application Scenarios

1.3.1 Hi3559 V100/Hi3556 V100 Motion Camera and Professional Camera Solution

1.3.2 Hi3559 V100/ Hi3556 V100 3D/VR Camera Solution

1.3.3 Hi3559 V100/Hi3556 V100 Drone Camera Solution

1.4 Architecture

1.4.1 Overview

1.4.2 Processor Core

1.4.3 Video Encoding

1.4.4 Video Encoding Performance

1.4.5 Intelligent Video Analysis

1.4.6 Video and Graphics Processing

1.4.7 ISP

1.4.8 Audio Encoding/Decoding

1.4.9 Security Engine

1.4.10 Video Interfaces

1.4.11 Audio Interfaces

1.4.12 Peripheral Interfaces

1.4.13 External Memory Interfaces

1.4.14 SDK

1.4.15 Physical Specifications

1.5 Boot Modes

1.6 Address Space Mapping

2 Hardware

Contents

Figures

Tables

2.1 Package and Pinout

2.1.1 Package

2.1.2 Pinout

2.2 Pin Description

2.3 Electrical Specifications

2.3.1 Power Consumption Parameters

2.3.2 Temperature and Thermal Resistance Parameters

2.3.3 Operating Conditions

2.3.4 Power-On and Power-Off Sequences

2.3.5 DC and AC Electrical Parameters

2.3.6 MIPI/LVDS RX Electrical Parameters

2.3.7 SDIO Electrical Parameters

2.3.8 Audio CODEC Electrical Parameters

2.3.9 PCIe Electrical Parameters

2.4 Interface Timings

2.4.1 DDR Interface Timings

2.4.1.1 Write Timings

Write Timings of dqs_out Relative to dq_out

Write Timings of dqs_out Relative to CK

Write Timing of CMD/ADDR Relative to CK

2.4.1.2 Read Timings

Read Timing of CMD/ADDR Relative to CK

Read Timings of dqs_in Relative to dq_in

2.4.1.3 Timing Parameters

2.4.2 NANDC Interface Timings

2.4.2.1 Command Cycle Timing

2.4.2.2 Address Cycle Timing

2.4.2.3 Write Data Timing

2.4.2.4 Read Data Timing

2.4.3 SFC Interface Timings

2.4.4 VI Interface Timing

2.4.5 VO Interface Timings

2.4.6 AIAO Interface Timings

2.4.6.1 I2S Interface Timing

2.4.6.2 PCM Interface Timings

2.4.7 I2C Interface Timing

2.4.8 SPI Timings

2.4.9 MIPI RX Timings

2.4.10 SDIO/MMC Interface Timings

3 System

Contents

Figures

Tables

3.1 Reset

3.1.1 Overview

3.1.2 Reset Control

3.1.3 Reset Configuration

3.1.3.1 Power-On Reset

3.1.3.2 System Reset

3.1.3.3 Soft Reset

3.2 Clock

3.2.1 Overview

3.2.2 Clock Control Block Diagram

3.2.3 Clock Distribution

3.2.4 PLL Configuration

3.2.5 Frequency Configurations

3.2.5.1 Frequency Configurations of CPU/DDR/SYSAXI

3.2.5.2 Frequency Configurations of Module Clocks

3.2.5.3 Precautions

3.2.6 Register Summary

3.2.7 Register Description

PERI_CRG_PLL0

PERI_CRG_PLL1

PERI_CRG_PLL4

PERI_CRG_PLL5

PERI_CRG_PLL6

PERI_CRG_PLL7

PERI_CRG_PLL8

PERI_CRG_PLL9

PERI_CRG10

PERI_CRG11

PERI_CRG12

PERI_CRG13

PERI_CRG15

PERI_CRG16

PERI_CRG17

PERI_CRG18

PERI_CRG19

PERI_CRG20

PERI_CRG21

PERI_CRG22

PERI_CRG23

PERI_CRG24

PERI_CRG25

PERI_CRG27

PERI_CRG29

PERI_CRG31

PERI_CRG32

PERI_CRG33

PERI_CRG43

PERI_CRG44

PERI_CRG45

PERI_CRG46

PERI_CRG48

PERI_CRG49

PERI_CRG54

PERI_CRG55

PERI_CRG56

PERI_CRG57

PERI_CRG58

PERI_CRG79

3.3 Processor Subsystem

3.4 Interrupt System

3.4.1 Interrupt Source Allocation

3.5 System Controller

3.5.1 Overview

3.5.2 Features

3.5.3 Function Description

3.5.3.1 Soft Reset

3.5.3.2 System Address Remap Control

3.5.3.3 Write Protection for Key Registers

3.5.3.4 System ID Register of the Chip

3.5.4 System Controller Registers

3.5.4.1 Register Summary

3.5.4.2 Register Description

SC_CTRL

SC_SYSRES

SOFT_INT

SC_LOCKEN

SYSSTAT

SCSYSID

3.5.5 Peripheral Control Registers

3.5.5.1 Register Summary

3.5.5.2 Register Description

MISC_CTRL0

MISC_CTRL1

MISC_CTRL2

MISC_CTRL3

MISC_CTRL4

MISC_CTRL5

MISC_CTRL6

MISC_CTRL7

MISC_CTRL8

MISC_CTRL9

MISC_CTRL11

MISC_CTRL12

MISC_CTRL14

MISC_CTRL15

MISC_CTRL16

MISC_CTRL18

MISC_CTRL21

MISC_CTRL22

MISC_CTRL23

MISC_CTRL24

MISC_CTRL25

MISC_CTRL26

MISC_CTRL27

MISC_CTRL28

MISC_CTRL29

MISC_CTRL30

MISC_CTRL31

MISC_CTRL32

MISC_CTRL33

MISC_CTRL34

MISC_CTRL45

MISC_CTRL46

MISC_CTRL47

MISC_CTRL48

MISC_CTRL51

MISC_CTRL52

MISC_CTRL53

MISC_CTRL54

MISC_CTRL56

MISC_CTRL80

MISC_CTRL81

MISC_CTRL85

MISC_CTRL88

MISC_CTRL89

MISC_CTRL93

MISC_CTRL94

MISC_CTRL95

MISC_CTRL96

3.6 DMA Controller

3.6.1 Overview

3.6.2 Features

3.6.3 Function Description

Functional Block Diagram

Workflow

Connection Between the DMA and Peripherals

DMAC Request Signals

DMA Linked List

3.6.4 Operating Mode

Clock Gating

Initialization

Enabling a Channel

Usage of DMAC_Cn_CONTROL

Usage of DMAC_Cn_CONFIG

Interrupt Handling

3.6.5 Register Summary

3.6.6 Register Description

DMAC_INT_STAT

DMAC_INT_TC_STAT

DMAC_INT_TC_CLR

DMAC_INT_ERR_STAT

DMAC_INT_ERR_CLR

DMAC_RAW_INT_TC_STAT

DMAC_RAW_INT_ERR_STAT

DMAC_ENABLED_CHNS

DMAC_SOFT_BREQ

DMAC_SOFT_SREQ

DMAC_SOFT_LBREQ

DMAC_SOFT_LSREQ

DMAC_CONFIG

DMAC_SYNC

DMAC_Cn_SRC_ADDR

DMAC_Cn_DEST_ADDR

DMAC_Cn_LLI

DMAC_Cn_CONTROL

DMAC_Cn_CONFIG

3.7 Timer

3.7.1 Overview

3.7.2 Features

3.7.3 Function Description

3.7.4 Operating Mode

Initialization

Interrupt Processing

Clock Selection

3.7.5 Register Summary

3.7.6 Register Description

TIMERx_LOAD

TIMERx_VALUE

TIMERx_CONTROL

TIMERx_INTCLR

TIMERx_RIS

TIMERx_MIS

TIMERx_BGLOAD

3.8 Watchdog

3.8.1 Overview

3.8.2 Features

3.8.3 Function Description

Application Block Diagram

Function Principle

3.8.4 Operating Mode

Configuring the Frequency of the Count Clock

Initializing the System

Processing an Interrupt

Disabling the Watchdog

3.8.5 Register Summary

3.8.6 Register Description

WDG_LOAD

WDG_VALUE

WDG_CONTROL

WDG_INTCLR

WDG_RIS

WDG_MIS

WDG_LOCK

3.9 RTC

3.9.1 Overview

3.9.2 Features

3.9.3 Function Description

3.9.4 Operating Mode

3.9.4.1 Count Clock Frequency

3.9.4.2 Soft Reset

3.9.4.3 Initializing the RTC

3.9.4.4 Handling Interrupts

3.9.4.5 Accessing RTC Registers

3.9.5 Register Summary

3.9.6 RTC Register Description

SPI_CLK_DIV

SPI_RW

CONVER_T

CRC_EN

INT_MASK

INT_CLEAR

BUSY

INT_RAW

INT_TCAP

T_VALUE

FILTER_NUM

3.9.7 Internal Register Description

RTC_10MS_COUNT

RTC_S_COUNT

RTC_M_COUNT

RTC_H_COUNT

RTC_D_COUNT_L

RTC_D_COUNT_H

RTC_MR_10MS

RTC_MR_S

RTC_MR_M

RTC_MR_H

RTC_MR_D_L

RTC_MR_D_H

RTC_LR_10MS

RTC_LR_S

RTC_LR_M

RTC_LR_H

RTC_LR_D_L

RTC_LR_D_H

RTC_LORD

RTC_IMSC

RTC_INT_CLR

RTC_MSC_INT

RTC_RAW_INT

RTC_CLK

RTC_POR_N

RTC_UV_CTRL

SDM_COEF_OUSIDE_H

SDM_COEF_OUSIDE_L

USER_REGISTER1

USER_REGISTER2

USER_REGISTER3

USER_REGISTER4

USER_REGISTER5

USER_REGISTER6

USER_REGISTER7

USER_REGISTER8

3.10 Power Management and Low-Power Mode Control

3.10.1 Overview

3.10.2 Power Management

3.10.2.1 Features

3.10.2.2 Function Description

3.10.2.3 Summary of Power Controller Registers

3.10.2.4 Description of Power Controller Registers

PWR_WAKEUP0_IO_CTRL

PWR_WAKEUP1_IO_CTRL

PWR_WAKEUP2_IO_CTRL

PWR_BUTTON0_IO_CTRL

PWR_BUTTON1_IO_CTRL

PWR_SEQ0_IO_CTRL

PWR_SEQ1_IO_CTRL

PWR_SEQ2_IO_CTRL

PWR_EN0_IO_CTRL

PWR_EN1_IO_CTRL

PWR_EN2_IO_CTRL

PWR_CTRL0

PWR_CTRL1

PWR_USER_REG0

PWR_USER_REG1

PWR_USER_REG2

PWR_USER_REG3

3.10.3 Clock Gating and Clock Frequency Adjustment

3.10.4 Module Low-Power Control

3.10.5 DDR Low-Power Control

3.10.6 DVFS and AVS

3.10.7 PMC

3.10.7.1 Function Description

3.10.7.2 Operating Mode

PWM Output

HPM Control

Hardware AVS

Internal Temperature Detection

Power-on/Power-off Control for the CPU A17 Core

3.10.7.3 PMC Register Summary

3.10.7.4 PMC Register Description

PERI_PMC0

PERI_PMC1

PERI_PMC2

PERI_PMC3

PERI_PMC4

PERI_PMC5

PERI_PMC6

PERI_PMC7

PERI_PMC8

PERI_PMC10

PERI_PMC11

PERI_PMC12

PERI_PMC13

PERI_PMC14

PERI_PMC15

PERI_PMC16

PERI_PMC17

PERI_PMC18

PERI_PMC19

PERI_PMC20

PERI_PMC21

PERI_PMC22

PERI_PMC23

PERI_PMC24

PERI_PMC25

PERI_PMC30

PERI_PMC31

PERI_PMC68

PERI_PMC69

PERI_PMC70

PERI_PMC71

PERI_PMC72

PERI_PMC73

PERI_PMC74

PERI_PMC75

PERI_PMC76

PERI_PMC77

PERI_PMC78

PERI_PMC79

PERI_PMC80

PERI_PMC81

PERI_PMC82

PERI_PMC83

PERI_PMC84

PERI_PMC85

PERI_PMC86

PERI_PMC87

PERI_PMC88

4 Memory Interfaces

Contents

Figures

Tables

4.1 DDRC

4.1.1 Overview

4.1.2 Features

4.1.3 Function Description

4.1.3.1 Application Block Diagram

4.1.3.2 Function Implementation

Command Truth Value Table

Auto Refresh

Low-Power Management

Arbitration Mechanism

Traffic Statistics and Command Latency Statistics

Address Mapping

4.1.4 Operating Mode

4.1.4.1 Soft Reset

4.1.4.2 Initializing the DDR SDRAM

4.1.5 AXI Registers of the DDRC

4.1.5.1 Register Summary

4.1.5.2 Register Description

AXI_CFG_LOCK

AXI_CKG

AXI_ACTION

AXI_REGION_MAP

AXI_REGION_ATTRIB

AXI_QOS_MAP

AXI_QOS_WRPRIn

AXI_QOS_RDPRIn

AXI_QOS_ADPTn

AXI_OSTD_PRTn

AXI_OSTD_PRT_STn

AXI_OSTD_GROUPn

AXI_OSTD_PRI0

AXI_OSTD_PRI1

AXI_OSTD_GROUP_STn

AXI_STATUS

AXI_INT_STATUS

4.1.6 QOSBUF Registers of the DDRC

4.1.6.1 Register Summary

4.1.6.2 Register Description

QOSB_ADPT_CTRL

QOSB_BUF_BYP

QOSB_WRTOUT0

QOSB_WRTOUT1

QOSB_WRTOUT2

QOSB_WRTOUT3

QOSB_RDTOUT0

QOSB_RDTOUT1

QOSB_RDTOUT2

QOSB_RDTOUT3

QOSB_WRTOUT_MAP

QOSB_RDTOUT_MAP

QOSB_CKG_CFG

QOSB_DMC_LVL

QOSB_CFG_PERF

QOSB_CMD_SUM

QOSB_CMD_CNT

QOSB_RNK_CNT

QOSB_BNK_CNT0

QOSB_BNK_CNT1

QOSB_BNK_CNT2

QOSB_BNK_CNT3

QOSB_OSTD_CNT

QOSB_WR_CMD_SUM

QOSB_RD_CMD_SUM

QOSB_TIMEOUT_MODE

4.1.7 DMC Registers of the DDRC

4.1.7.1 Register Summary

4.1.7.2 Register Description

DDRC_CTRL_SREF

DDRC_CTRL_PERF

DDRC_CFG_SREF

DDRC_CFG_PD

DDRC_CFG_AREF

DDRC_CFG_WORKMODE

DDRC_CFG_DDRMODE

DDRC_CFG_SCRAMB

DDRC_CFG_RNKVOLn

DDRC_CFG_ODT

DDRC_CFG_TIMING0

DDRC_CFG_TIMING1

DDRC_CFG_TIMING2

DDRC_CFG_TIMING3

DDRC_CFG_TIMING4

DDRC_CFG_TIMING5

DDRC_CFG_TIMING6

DDRC_CFG_BLDATA

DDRC_CFG_DMCLVL

DDRC_CFG_DDRPHY

4.2 Flash Memory Controller

4.2.1 Overview

4.2.2 Features

4.2.3 Function Description

4.2.3.1 Interface Block Diagram

4.2.3.2 Interfaces

Standard SPI

Dual-Output/Dual-Input SPI

Dual I/O SPI

Quad-Output/Quad-Input SPI

Quad I/O SPI

4.2.3.3 SPI Timings

4.2.3.4 SPI NAND Flash Address

4.2.3.5 Boot Function

SPI NOR Flash

SPI NAND Flash and NAND Flash

Dual-Image Function

4.2.3.6 Operations in Register Mode

4.2.3.7 Operations in Internal DMA Mode

4.2.3.8 ECC

4.2.3.9 Randomizer

4.2.3.10 Timeout

4.2.4 Working Process

4.2.4.1 Initialization Process

4.2.4.2 FMC_OP Operation Process (Register Operation Mode)

4.2.4.3 Process of Reading the Component Status

4.2.4.4 Process of Changing the Address Mode of the SPI NOR Flash

4.2.4.5 Erase Operation Process (SPI NAND flash and SPI NOR flash)

4.2.4.6 FMC_OP Erase Operation Process (NAND Flash)

4.2.4.7 Process of Reading Data in Internal DMA Mode (FMC_OP_CTRL Read Operation)

4.2.4.8 Process of Writing Data in Internal DMA Mode (FMC_OP_CTRL Read Operation)

4.2.4.9 Notes

4.2.5 Data Structures (NAND Flash/SPI NAND Flash)

4.2.5.2 4-Bit ECC Mode (8-Bit/1 KB Error Correction Performance)

2 KB Page Size

4 KB Page Size

4.2.5.3 8-Bit ECC Mode (16-Bit/1 KB Error Correction Performance)

2 KB Page Size

4 KB Page Size

4.2.5.4 24-Bit ECC Mode (24-Bit/1 KB Error Correction Performance)

2 KB Page Size

4 KB Page Size

8 KB Page Size

4.2.5.5 28-Bit ECC Mode (28-Bit/1 KB Error Correction Performance)

2 KB Page Size

4 KB Page Size

8 KB Page Size

4.2.5.6 40-Bit ECC Mode (40-Bit/1 KB Error Correction Performance)

8 KB Page Size

16 KB Page Size

4.2.5.7 64-Bit ECC Mode (40-Bit/1 KB Error Correction Performance)

8 KB Page Size

16 KB Page Size

4.2.6 ECC Mode Selection

4.2.7 FMC Registers

4.2.8 Register Description

FMC_CFG

GLOBAL_CFG

TIMING_SPI_CFG

PND_PWIDTH_CFG

PND_OPIDLE_CFG

FMC_INT

FMC_INT_EN

FMC_INT_CLR

FMC_CMD

FMC_ADDRH

FMC_ADDRL

FMC_OP_CFG

SPI_OP_ADDR

FMC_DATA_NUM

FMC_OP

FMC_DMA_LEN

FMC_DMA_AHB_CTRL

FMC_DMA_SADDR_D0

FMC_DMA_SADDR_D1

FMC_DMA_SADDR_D2

FMC_DMA_SADDR_D3

FMC_DMA_SADDR_OOB

FMC_OP_CTRL

FMC_TIMEOUT_WR

FMC_OP_PARA

FMC_BOOT_SET

FMC_LP_CTRL

FMC_LOCK

FMC_LOCK_SA0

FMC_LOCK_EA0

FMC_LOCK_SA1

FMC_LOCK_EA1

FMC_LOCK_SA2

FMC_LOCK_EA2

FMC_LOCK_SA3

FMC_LOCK_EA3

FMC_EXPCMD

FMC_EXBCMD

FMC_ERR_THD

FMC_FLASH_INFO

FMC_OP_CNT

FMC_VERSION

FMC_ERR_NUM0_BUF0

FMC_ERR_NUM1_BUF0

FMC_ERR_NUM0_BUF1

FMC_ERR_NUM1_BUF1

FMC_ERR_ALARM_ADDRH

FMC_ERR_ALARM_ADDRL

FMC_ECC_INVALID_ADDRH

FMC_ECC_INVALID_ADDRL

FMC_READ_TIMING_TUNE

FMC_EXP_OP_CTRL

FMC_EXP_ADDRH

FMC_EXP_ADDRL

FMC_EXP_DMA_SADDR_D0

FMC_EXP_DMA_SADDR_D1

FMC_EXP_DMA_SADDR_D2

FMC_EXP_DMA_SADDR_D3

FMC_EXP_DMA_SADDR_OOB

FMC_EXP_INT

FMC_EXP_INT_EN

FMC_EXP_INT_CLR

FMC_EXP_ERR_NUM0_BUF0

FMC_EXP_ERR_NUM1_BUF0

FMC_EXP_ERR_NUM0_BUF1

FMC_EXP_ERR_NUM1_BUF1

5 Video Encoder

Contents

Figures

5.1 Overview

5.2 VEDU

5.2.1 Overview

5.2.2 Features

5.2.3 Function Description

5.3 JPGE

5.3.1 Overview

5.3.2 Features

5.3.3 Function Description

6 Video and Graphics Processing

Contents

6.1 TDE

6.1.1 Overview

6.1.2 Function Description

6.2 VPSS

6.2.1 Overview

6.2.2 Features

6.3 VGS

6.3.1 Overview

6.3.2 Features

6.4 GDC

6.4.1 Overview

6.4.2 Features

7 Intelligent Video Engine

Contents

Figures

Tables

7.1 IVE

7.1.1 Overview

7.1.2 Function Description

7.1.3 Operating Mode

7.1.3.1 Input and Output Data Formats

7.1.3.2 Supported Functions

DMA

Filter

CSC

FilterAndCSC

Sobel

MagAndAng

Dilate

Erode

Thresh

And

Sub

Or

Integral

Histogram

Thresh_S16

Thresh_U16

16BitTo8Bit

OrdStatFilter

Map

Add

Xor

NCC

CCL

GMM

CannyHysEdge

LBP

NormGrad

LKOpticalFlow

STBoxFltAndEigCalc

STCandiCorner

GradFg

MatchBgModel

UpdateBgModel

ANN_MLP_Predict

SVM_Predict

SAD

Resize

GMM2

CNN_Predict

7.1.4 Register Summary

8 Video Interfaces

Contents

Figures

Tables

8.1 VICAP

8.1.1 Overview

8.1.2 Features

8.1.3 Function Description

8.1.3.1 Typical Applications

8.1.3.2 Function Implementation

BT.1120 Interface Timings

BT.656 Interface Timings

BT.601 Interface Timings

DC Interface Timings

8.1.3.3 Image Cropping

8.1.3.4 Image Storage Modes

8.1.4 Operating Mode

8.1.4.1 reg_newer Function

8.1.4.2 VICAP Hardware Workflow

8.1.4.3 Software Configuration Workflow

8.1.5 Register Summary

8.1.6 Register Description

AXI_CFG

ISP_SEL

BUF_MODE

SLAVE_MODE_CFG

SLAVE_MODE_VS_TIME

SLAVE_MODE_HS_TIME

SLAVE_MODE_VS_CYC

SLAVE_MODE_HS_CYC

VICAP_INT

VICAP_INT_MASK

PT_INTF_MOD

PT_OFFSET0

PT_OFFSET1

PT_OFFSET2

PT_BT656_CFG

PT_UNIFY_TIMING_CFG

PT_GEN_TIMING_CFG

PT_UNIFY_DATA_CFG

PT_GEN_DATA_CFG

PT_GEN_DATA_COEF

PT_GEN_DATA_INIT

PT_INTF_HFB

PT_INTF_HACT

PT_INTF_HBB

PT_INTF_VFB

PT_INTF_VACT

PT_INTF_VBB

PT_INTF_VBFB

PT_INTF_VBACT

PT_INTF_VBBB

PT_ID_CFG

PT_FLASH_CFG

PT_FLASH_CYC0

PT_FLASH_CYC1

PT_SHUTTER_CYC0

PT_SHUTTER_CYC1

PT_SHUTTER_CYC2

PT_SHUTTER_CYC3

PT_BT656_STATUS

PT_SIZE

PT_INT

PT_INT_MASK

DES_CTRL

DES_INT

DES_MASK

SRC_CTRL

SRC_INT

SRC_MASK

CH_CTRL

CH_REG_NEWER

CH_DLY_CFG

CH_WCH_Y_CFG

CH_WCH_Y_SIZE

CH_WCH_Y_FADDR

CH_WCH_Y_HADDR

CH_WCH_Y_STRIDE

CH_WCH_C_CFG

CH_WCH_C_SIZE

CH_WCH_C_FADDR

CH_WCH_C_HADDR

CH_WCH_C_STRIDE

CH_Y_OUT_SIZE

CH_C_OUT_SIZE

CH_INT

CH_INT_MASK

CH_Y_CROP_CFG

CH_Y_CROP0_START

CH_Y_CROP0_SIZE

CH_C_CROP_CFG

CH_C_CROP0_START

CH_C_CROP0_SIZE

ISP_BAS_CFG

ISP_BAS_OUTSIZE

ISP_BAS_ACCH

ISP_BAS_ACCV

ISP_BAS_INCH

ISP_BAS_INCV

ISP_RPH_WEIH

ISP_RPH_WEIV

ISP_BAS_HLUT_HWADDR

ISP_BAS_HLUT_HWDATA

ISP_BAS_HLUT_HRADDR

ISP_BAS_HLUT_HRDATA

ISP_BAS_HLUT_LWADDR

ISP_BAS_HLUT_LWDATA

ISP_BAS_HLUT_LRADDR

ISP_BAS_HLUT_LRDATA

ISP_BAS_VLUT_HWADDR

ISP_BAS_VLUT_HWDATA

ISP_BAS_VLUT_HRADDR

ISP_BAS_VLUT_HRDATA

ISP_BAS_VLUT_LWADDR

ISP_BAS_VLUT_LWDATA

ISP_BAS_VLUT_LRADDR

ISP_BAS_VLUT_LRDATA

ISP_BAS_CTRL_F

ISP_BAS_CTRL_I

ISP_BAS_TIMING

ISP_BAS_UPDATE

ISP_BAS_SIZE

8.2 VDP

8.2.1 Overview

8.2.2 Architecture

8.2.3 Operating Mode

8.2.3.1 Clock Configurations

8.2.3.2 Reset

8.2.3.3 Bus Configurations

AXI Master

APB Register Configuration

Outstanding Configuration

8.2.3.4 Digital Output Interfaces

8.2.3.5 Interrupts

Vertical Timing Interrupt

Low Bandwidth Interrupt

8.2.4 Function Description

8.2.4.1 Video Layer

Features

DCMP (Decompression)

Horizontal Cropping

420-422 (Vertical Chrominance Up Sampling)

422-444 (Horizontal Chrominance Up Sampling)

CSC

8.2.4.2 Graphics Layer

Features

CSC

Alpha Processing

Color key

Premultiplication

8.2.4.3 Overlaying

Features

8.2.4.4 Display Channel

Video Channel Features

Timing Configuration

8.2.4.5 BT.1120 HD Output Interface

Features

8.2.4.6 BT.656 SD Output Interface

Features

8.2.4.7 CVBS SD Output Interface

Features

8.2.4.8 RGB LCD Output Interface

Features

8.2.5 Register Summary

8.2.6 Register Description

VOCTRL

VOINTSTA

VOMSKINTSTA

VOINTMSK

VDPVERSION1

VDPVERSION2

VOMEM_CTRL

VOMIDORDER

VOAXICTRL

VO_MUX

VO_MUX_TESTSYNC

VO_MUX_TESTDATA

VO_DAC_CTRL

VO_DAC_0_CTRL

VO_DAC_STAT0

V1_CTRL

V1_UPD

V1_IRESO

V1_ORESO

V1_DCMP_SGMT_CROP

V1_CBMPARA

V1_CPOS

V1_DFPOS

V1_DLPOS

V1_CSC_IDC

V1_CSC_ODC

V1_CSC_IODC

V1_CSC_P0

V1_CSC_P1

V1_CSC_P2

V1_CSC_P3

V1_CSC_P4

V1_P0LADDR

V1_P0CADDR

V1_P0STRIDE

V1_LADDROFFSET

V1_CADDROFFSET

V1_DCMP_LSTATE0

V1_DCMP_LSTATE1

V1_DCMP_CSTATE0

V1_DCMP_CSTATE1

V1_DCMPERRCLR

V1_DCMP_ERR

G2_CTRL

G2_UPD

G2_ADDR

G2_STRIDE

G2_IRESO

G2_SFPOS

G2_CBMPARA

G2_CKEYMAX

G2_CKEYMIN

G2_CMASK

G2_DFPOS

G2_DLPOS

G2_CSC_IDC

G2_CSC_ODC

G2_CSC_IODC

G2_CSC_P0

G2_CSC_P1

G2_CSC_P2

G2_CSC_P3

G2_CSC_P4

CBM_BKG2

CBM_MIX2

DHD1_CTRL

DHD1_VSYNC

DHD1_HSYNC1

DHD1_HSYNC2

DHD1_VPLUS

DHD1_PWR

DHD1_VTTHD3

DHD1_VTTHD

DHD1_PARATHD

DHD1_START_POS

DHD1_STATE

BT_CTRL

BT_CLIP0_L

BT_CLIP0_H

BT_DITHER0_CTRL

BT_DITHER0_COEF0

BT_DITHER0_COEF1

LCD_CTRL

LCD_SYNC_INV

DATE_COEFF0

DATE_COEFF1

DATE_COEFF2

DATE_COEFF3

DATE_COEFF4

DATE_COEFF5

DATE_COEFF6

DATE_COEFF21

DATE_COEFF22

DATE_COEFF23

DATE_COEFF24

DATE_ISRMASK

DATE_ISRSTATE

DATE_ISR

DATE_COEFF37

DATE_COEFF38

DATE_COEFF39

DATE_COEFF40

DATE_COEFF41

DATE_COEFF42

DATE_DACDET1

DATE_DACDET2

DATE_COEFF50

DATE_COEFF51

DATE_COEFF52

DATE_COEFF53

DATE_COEFF54

DATE_COEFF55

DATE_COEFF56

DATE_COEFF57

DATE_COEFF58

DATE_COEFF59

8.3 MIPI RX

8.3.1 Overview

8.3.2 Features

8.3.3 Function Description

8.3.3.1 Typical Applications

8.3.3.2 Function Implementation

Data Format of the MIPI Interface

Linear Mode of the MIPI Interface

WDR Modes of the MIPI Interface

Input Data Format of the LVDS Interface

Linear Mode of the LVDS Interface

WDR Modes of the LVDS Interface

HiSPi Data Format

HiSPi Linear Mode

HiSPi WDR Mode

8.3.4 Operating Mode of the MIPI RX Controller

8.3.4.1 MIPI Mode Configuration Process

8.3.4.2 LVDS and HiSPi Mode Configuration Process

8.3.5 MIPI RX Register Summary

8.3.6 MIPI Register Description

PHY_MODE_LINK0

PHY_SKEW_LINK0

PHY_EN_LINK0

PHY_DATA_LINK0

PHY_PH_MIPI_LINK0

PHY_DATA_MIPI_LINK0

PHY_SYNC_DCT_LINK0

PHY_SYNC_CODE0_LINK0

PHY_SYNC_CODE1_LINK0

PHY_SYNC_CODE2_LINK0

PHY_SYNC_CODE3_LINK0

MIPI_CIL_INT_RAW_LINK0

MIPI_CIL_INT_LINK0

MIPI_CIL_INT_MSK_LINK0

PHY_MODE_LINK1

PHY_SKEW_LINK1

PHY_EN_LINK1

PHY_DATA_LINK1

PHY_PH_MIPI_LINK1

PHY_DATA_MIPI_LINK1

PHY_SYNC_DCT_LINK1

PHY_SYNC_CODE0_LINK1

PHY_SYNC_CODE1_LINK1

PHY_SYNC_CODE2_LINK1

PHY_SYNC_CODE3_LINK1

MIPI_CIL_INT_RAW_LINK1

MIPI_CIL_INT_LINK1

MIPI_CIL_INT_MSK_LINK1

PHY_MODE_LINK2

PHY_SKEW_LINK2

PHY_EN_LINK2

PHY_DATA_LINK2

PHY_PH_MIPI_LINK2

PHY_DATA_MIPI_LINK2

PHY_SYNC_DCT_LINK2

PHY_SYNC_CODE0_LINK2

PHY_SYNC_CODE1_LINK2

PHY_SYNC_CODE2_LINK2

PHY_SYNC_CODE3_LINK2

MIPI_CIL_INT_RAW_LINK2

MIPI_CIL_INT_LINK2

MIPI_CIL_INT_MSK_LINK2

PHY_ID

PHY_LP_SELECT

CHN0_PHY_EN

CHN0_MEM_CTRL

CHN0_LANE_EN

CHN0_PHYCFG_MODE

CHN0_PHYCFG_EN

CHN0_CLR_EN

CHN0_CIL_CTRL

CHN1_PHY_EN

CHN1_MEM_CTRL

CHN1_LANE_EN

CHN1_PHYCFG_MODE

CHN1_PHYCFG_EN

CHN1_CLR_EN

CHN1_CIL_CTRL

MIPI_CHN0_INT_RAW

MIPI_CHN0_INT

MIPI_CHN0_INT_MSK

MIPI_CHN1_INT_RAW

MIPI_CHN1_INT

MIPI_CHN1_INT_MSK

MIPI0_LANES_NUM

MIPI0_MAIN_INT_ST

MIPI0_DI_1

MIPI0_DI_2

MIPI0_PKT_INTR_ST

MIPI0_PKT_INTR_MSK

MIPI0_PKT_INTR2_ST

MIPI0_PKT_INTR2_MSK

MIPI0_FRAME_INTR_ST

MIPI0_FRAME_INTR_MSK

MIPI0_LINE_INTR_ST

MIPI0_LINE_INTR_MSK

MIPI0_USERDEF_DT

MIPI0_USER_DEF

MIPI0_CTRL_MODE_HS

MIPI0_DOL_ID_CODE0

MIPI0_DOL_ID_CODE1

MIPI0_DOL_ID_CODE2

MIPI0_CTRL_MODE_PIXEL

MIPI0_DUMMY_PIX_REG

MIPI0_IMGSIZE0_STATIS

MIPI0_IMGSIZE1_STATIS

MIPI0_IMGSIZE2_STATIS

MIPI0_IMGSIZE3_STATIS

MIPI0_CTRL_INT_RAW

MIPI0_CTRL_INT

MIPI0_CTRL_INT_MSK

LVDS0_WDR

LVDS0_CROP_START3

LVDS0_IMGSIZE

LVDS0_CTRL

LVDS0_CROP_START0

LVDS0_CROP_START1

LVDS0_CROP_START2

LVDS0_LANE0_SOF_01

LVDS0_LANE0_SOF_23

LVDS0_LANE0_EOF_01

LVDS0_LANE0_EOF_23

LVDS0_LANE0_SOL_01

LVDS0_LANE0_SOL_23

LVDS0_LANE0_EOL_01

LVDS0_LANE0_EOL_23

LVDS0_LANE1_SOF_01

LVDS0_LANE1_SOF_23

LVDS0_LANE1_EOF_01

LVDS0_LANE1_EOF_23

LVDS0_LANE1_SOL_01

LVDS0_LANE1_SOL_23

LVDS0_LANE1_EOL_01

LVDS0_LANE1_EOL_23

LVDS0_LANE2_SOF_01

LVDS0_LANE2_SOF_23

LVDS0_LANE2_EOF_01

LVDS0_LANE2_EOF_23

LVDS0_LANE2_SOL_01

LVDS0_LANE2_SOL_23

LVDS0_LANE2_EOL_01

LVDS0_LANE2_EOL_23

LVDS0_LANE3_SOF_01

LVDS0_LANE3_SOF_23

LVDS0_LANE3_EOF_01

LVDS0_LANE3_EOF_23

LVDS0_LANE3_SOL_01

LVDS0_LANE3_SOL_23

LVDS0_LANE3_EOL_01

LVDS0_LANE3_EOL_23

LVDS0_LANE4_SOF_01

LVDS0_LANE4_SOF_23

LVDS0_LANE4_EOF_01

LVDS0_LANE4_EOF_23

LVDS0_LANE4_SOL_01

LVDS0_LANE4_SOL_23

LVDS0_LANE4_EOL_01

LVDS0_LANE4_EOL_23

LVDS0_LANE5_SOF_01

LVDS0_LANE5_SOF_23

LVDS0_LANE5_EOF_01

LVDS0_LANE5_EOF_23

LVDS0_LANE5_SOL_01

LVDS0_LANE5_SOL_23

LVDS0_LANE5_EOL_01

LVDS0_LANE5_EOL_23

LVDS0_LANE6_SOF_01

LVDS0_LANE6_SOF_23

LVDS0_LANE6_EOF_01

LVDS0_LANE6_EOF_23

LVDS0_LANE6_SOL_01

LVDS0_LANE6_SOL_23

LVDS0_LANE6_EOL_01

LVDS0_LANE6_EOL_23

LVDS0_LANE7_SOF_01

LVDS0_LANE7_SOF_23

LVDS0_LANE7_EOF_01

LVDS0_LANE7_EOF_23

LVDS0_LANE7_SOL_01

LVDS0_LANE7_SOL_23

LVDS0_LANE7_EOL_01

LVDS0_LANE7_EOL_23

LVDS0_LANE8_SOF_01

LVDS0_LANE8_SOF_23

LVDS0_LANE8_EOF_01

LVDS0_LANE8_EOF_23

LVDS0_LANE8_SOL_01

LVDS0_LANE8_SOL_23

LVDS0_LANE8_EOL_01

LVDS0_LANE8_EOL_23

LVDS0_LANE9_SOF_01

LVDS0_LANE9_SOF_23

LVDS0_LANE9_EOF_01

LVDS0_LANE9_EOF_23

LVDS0_LANE9_SOL_01

LVDS0_LANE9_SOL_23

LVDS0_LANE9_EOL_01

LVDS0_LANE9_EOL_23

LVDS0_LANE10_SOF_01

LVDS0_LANE10_SOF_23

LVDS0_LANE10_EOF_01

LVDS0_LANE10_EOF_23

LVDS0_LANE10_SOL_01

LVDS0_LANE10_SOL_23

LVDS0_LANE10_EOL_01

LVDS0_LANE10_EOL_23

LVDS0_LANE11_SOF_01

LVDS0_LANE11_SOF_23

LVDS0_LANE11_EOF_01

LVDS0_LANE11_EOF_23

LVDS0_LANE11_SOL_01

LVDS0_LANE11_SOL_23

LVDS0_LANE11_EOL_01

LVDS0_LANE11_EOL_23

LVDS0_LANE0_NXT_SOF_01

LVDS0_LANE0_NXT_SOF_23

LVDS0_LANE0_NXT_EOF_01

LVDS0_LANE0_NXT_EOF_23

LVDS0_LANE0_NXT_SOL_01

LVDS0_LANE0_NXT_SOL_23

LVDS0_LANE0_NXT_EOL_01

LVDS0_LANE0_NXT_EOL_23

LVDS0_LANE1_NXT_SOF_01

LVDS0_LANE1_NXT_SOF_23

LVDS0_LANE1_NXT_EOF_01

LVDS0_LANE1_NXT_EOF_23

LVDS0_LANE1_NXT_SOL_01

LVDS0_LANE1_NXT_SOL_23

LVDS0_LANE1_NXT_EOL_01

LVDS0_LANE1_NXT_EOL_23

LVDS0_LANE2_NXT_SOF_01

LVDS0_LANE2_NXT_SOF_23

LVDS0_LANE2_NXT_EOF_01

LVDS0_LANE2_NXT_EOF_23

LVDS0_LANE2_NXT_SOL_01

LVDS0_LANE2_NXT_SOL_23

LVDS0_LANE2_NXT_EOL_01

LVDS0_LANE2_NXT_EOL_23

LVDS0_LANE3_NXT_SOF_01

LVDS0_LANE3_NXT_SOF_23

LVDS0_LANE3_NXT_EOF_01

LVDS0_LANE3_NXT_EOF_23

LVDS0_LANE3_NXT_SOL_01

LVDS0_LANE3_NXT_SOL_23

LVDS0_LANE3_NXT_EOL_01

LVDS0_LANE3_NXT_EOL_23

LVDS0_LANE4_NXT_SOF_01

LVDS0_LANE4_NXT_SOF_23

LVDS0_LANE4_NXT_EOF_01

LVDS0_LANE4_NXT_EOF_23

LVDS0_LANE4_NXT_SOL_01

LVDS0_LANE4_NXT_SOL_23

LVDS0_LANE4_NXT_EOL_01

LVDS0_LANE4_NXT_EOL_23

LVDS0_LANE5_NXT_SOF_01

LVDS0_LANE5_NXT_SOF_23

LVDS0_LANE5_NXT_EOF_01

LVDS0_LANE5_NXT_EOF_23

LVDS0_LANE5_NXT_SOL_01

LVDS0_LANE5_NXT_SOL_23

LVDS0_LANE5_NXT_EOL_01

LVDS0_LANE5_NXT_EOL_23

LVDS0_LANE6_NXT_SOF_01

LVDS0_LANE6_NXT_SOF_23

LVDS0_LANE6_NXT_EOF_01

LVDS0_LANE6_NXT_EOF_23

LVDS0_LANE6_NXT_SOL_01

LVDS0_LANE6_NXT_SOL_23

LVDS0_LANE6_NXT_EOL_01

LVDS0_LANE6_NXT_EOL_23

LVDS0_LANE7_NXT_SOF_01

LVDS0_LANE7_NXT_SOF_23

LVDS0_LANE7_NXT_EOF_01

LVDS0_LANE7_NXT_EOF_23

LVDS0_LANE7_NXT_SOL_01

LVDS0_LANE7_NXT_SOL_23

LVDS0_LANE7_NXT_EOL_01

LVDS0_LANE7_NXT_EOL_23

LVDS0_LANE8_NXT_SOF_01

LVDS0_LANE8_NXT_SOF_23

LVDS0_LANE8_NXT_EOF_01

LVDS0_LANE8_NXT_EOF_23

LVDS0_LANE8_NXT_SOL_01

LVDS0_LANE8_NXT_SOL_23

LVDS0_LANE8_NXT_EOL_01

LVDS0_LANE8_NXT_EOL_23

LVDS0_LANE9_NXT_SOF_01

LVDS0_LANE9_NXT_SOF_23

LVDS0_LANE9_NXT_EOF_01

LVDS0_LANE9_NXT_EOF_23

LVDS0_LANE9_NXT_SOL_01

LVDS0_LANE9_NXT_SOL_23

LVDS0_LANE9_NXT_EOL_01

LVDS0_LANE9_NXT_EOL_23

LVDS0_LANE10_NXT_SOF_01

LVDS0_LANE10_NXT_SOF_23

LVDS0_LANE10_NXT_EOF_01

LVDS0_LANE10_NXT_EOF_23

LVDS0_LANE10_NXT_SOL_01

LVDS0_LANE10_NXT_SOL_23

LVDS0_LANE10_NXT_EOL_01

LVDS0_LANE10_NXT_EOL_23

LVDS0_LANE11_NXT_SOF_01

LVDS0_LANE11_NXT_SOF_23

LVDS0_LANE11_NXT_EOF_01

LVDS0_LANE11_NXT_EOF_23

LVDS0_LANE11_NXT_SOL_01

LVDS0_LANE11_NXT_SOL_23

LVDS0_LANE11_NXT_EOL_01

LVDS0_LANE11_NXT_EOL_23

LVDS0_LI_WORD0

LVDS0_LI_WORD1

LVDS0_LI_WORD2

LVDS0_LI_WORD3

LVDS0_IMGSIZE0_STATIS

LVDS0_IMGSIZE1_STATIS

LVDS0_IMGSIZE2_STATIS

LVDS0_IMGSIZE3_STATIS

LVDS0_CTRL_INT_RAW

LVDS0_CTRL_INT

LVDS0_CTRL_INT_MSK

LANE_ID0_CHN0

LANE_ID1_CHN0

LANE_ID2_CHN0

ALIGN0_INT_RAW

ALIGN0_INT

ALIGN0_INT_MSK

MIPI1_LANES_NUM

MIPI1_MAIN_INT_ST

MIPI1_DI_1

MIPI1_DI_2

MIPI1_PKT_INTR_ST

MIPI1_PKT_INTR_MSK

MIPI1_PKT_INTR2_ST

MIPI1_PKT_INTR2_MSK

MIPI1_FRAME_INTR_ST

MIPI1_FRAME_INTR_MSK

MIPI1_LINE_INTR_ST

MIPI1_LINE_INTR_MSK

MIPI1_USERDEF_DT

MIPI1_USER_DEF

MIPI1_CTRL_MODE_HS

MIPI1_DOL_ID_CODE0

MIPI1_DOL_ID_CODE1

MIPI1_DOL_ID_CODE2

MIPI1_CTRL_MODE_PIXEL

MIPI1_DUMMY_PIX_REG

MIPI1_IMGSIZE0_STATIS

MIPI1_IMGSIZE1_STATIS

MIPI1_IMGSIZE2_STATIS

MIPI1_IMGSIZE3_STATIS

MIPI1_CTRL_INT_RAW

MIPI1_CTRL_INT

MIPI1_CTRL_INT_MSK

LVDS1_WDR

LVDS1_CROP_START3

LVDS1_IMGSIZE

LVDS1_CTRL

LVDS1_CROP_START0

LVDS1_CROP_START1

LVDS1_CROP_START2

LVDS1_LANE0_SOF_01

LVDS1_LANE0_SOF_23

LVDS1_LANE0_EOF_01

LVDS1_LANE0_EOF_23

LVDS1_LANE0_SOL_01

LVDS1_LANE0_SOL_23

LVDS1_LANE0_EOL_01

LVDS1_LANE0_EOL_23

LVDS1_LANE1_SOF_01

LVDS1_LANE1_SOF_23

LVDS1_LANE1_EOF_01

LVDS1_LANE1_EOF_23

LVDS1_LANE1_SOL_01

LVDS1_LANE1_SOL_23

LVDS1_LANE1_EOL_01

LVDS1_LANE1_EOL_23

LVDS1_LANE2_SOF_01

LVDS1_LANE2_SOF_23

LVDS1_LANE2_EOF_01

LVDS1_LANE2_EOF_23

LVDS1_LANE2_SOL_01

LVDS1_LANE2_SOL_23

LVDS1_LANE2_EOL_01

LVDS1_LANE2_EOL_23

LVDS1_LANE3_SOF_01

LVDS1_LANE3_SOF_23

LVDS1_LANE3_EOF_01

LVDS1_LANE3_EOF_23

LVDS1_LANE3_SOL_01

LVDS1_LANE3_SOL_23

LVDS1_LANE3_EOL_01

LVDS1_LANE3_EOL_23

LVDS1_LANE0_NXT_SOF_01

LVDS1_LANE0_NXT_SOF_23

LVDS1_LANE0_NXT_EOF_01

LVDS1_LANE0_NXT_EOF_23

LVDS1_LANE0_NXT_SOL_01

LVDS1_LANE0_NXT_SOL_23

LVDS1_LANE0_NXT_EOL_01

LVDS1_LANE0_NXT_EOL_23

LVDS1_LANE1_NXT_SOF_01

LVDS1_LANE1_NXT_SOF_23

LVDS1_LANE1_NXT_EOF_01

LVDS1_LANE1_NXT_EOF_23

LVDS1_LANE1_NXT_SOL_01

LVDS1_LANE1_NXT_SOL_23

LVDS1_LANE1_NXT_EOL_01

LVDS1_LANE1_NXT_EOL_23

LVDS1_LANE2_NXT_SOF_01

LVDS1_LANE2_NXT_SOF_23

LVDS1_LANE2_NXT_EOF_01

LVDS1_LANE2_NXT_EOF_23

LVDS1_LANE2_NXT_SOL_01

LVDS1_LANE2_NXT_SOL_23

LVDS1_LANE2_NXT_EOL_01

LVDS1_LANE2_NXT_EOL_23

LVDS1_LANE3_NXT_SOF_01

LVDS1_LANE3_NXT_SOF_23

LVDS1_LANE3_NXT_EOF_01

LVDS1_LANE3_NXT_EOF_23

LVDS1_LANE3_NXT_SOL_01

LVDS1_LANE3_NXT_SOL_23

LVDS1_LANE3_NXT_EOL_01

LVDS1_LANE3_NXT_EOL_23

LVDS1_LI_WORD0

LVDS1_LI_WORD1

LVDS1_LI_WORD2

LVDS1_LI_WORD3

LVDS1_LANE_ORDERS2

LVDS1_IMGSIZE0_STATIS

LVDS1_IMGSIZE1_STATIS

LVDS1_IMGSIZE2_STATIS

LVDS1_IMGSIZE3_STATIS

LVDS1_CTRL_INT_RAW

LVDS1_CTRL_INT

LVDS1_CTRL_INT_MSK

LANE_ID0_CHN1

ALIGN1_INT_RAW

ALIGN1_INT

ALIGN1_INT_MSK

9 ISP

Contents

Figures

Tables

9.1 Introduction

9.2 Overview

Functional Block Diagram

Operating Mode

Memory Read and Write Solutions

9.3 Interrupt System

Function Description

Interrupt Timing

9.4 Module Functions

Crop

FPN

Video test gen

Sensor Offset

DPC

GE

WDR

Gamma FE

Digital Gain

DNR

Gamma BE

WB

Mesh Shading

Radial Shading

DRC

Demosaic

Color Matrix

Gamma_RGB

AF

AE

AWB Sum

Dehaze

CSC

DCI

ACM

Sharpen

MCDS

9.5 Register Summary

9.6 Register Description

ISP_AF_CFG

ISP_AF_ZONE

ISP_AF_CROP_START

ISP_AF_CROP_SIZE

ISP_AF_MEAN_THRES

ISP_AF_IIRG0

ISP_AF_IIRG1

ISP_AF_IIRG2

ISP_AF_IIRG3

ISP_AF_IIRG4

ISP_AF_IIRG5

ISP_AF_IIRG6

ISP_AF_IIRPL

ISP_AF_SHIFT

ISP_AF_FIRH0

ISP_AF_FIRH1

ISP_AF_FIRH2

ISP_AF_FIRH3

ISP_AF_FIRH4

ISP_AF_ACC_SHIFT

ISP_AF_CNT_SHIFT

ISP_AF_STAT_IND_RADDR

ISP_AF_STAT_IND_RDATA

ISP_AF_CTRL_I

ISP_AF_UPDATE

ISP_AF_SIZE

ISP_AF_IIRTHRE

ISP_AF_IIRGAIN

ISP_AF_IIRSLOPE

ISP_AF_IIRDILATE

ISP_AF_FIRTHRE

ISP_AF_FIRGAIN

ISP_AF_FIRSLOPE

ISP_AF_IIRTHRE_CORING

ISP_AF_IIRPEAK_CORING

ISP_AF_IIRSLOPE_CORING

ISP_AF_FIRTHRE_CORING

ISP_AF_FIRPEAK_CORING

ISP_AF_FIRSLOPE_CORING

ISP_AF_HILIGHT

ISP_AF_OFFSET

ISP_AF_INT

ISP_AF_INT_MASK

ISPFE_ACTIVE_WIDTH

ISPFE_ACTIVE_HEIGHT

ISPFE_RGGB_START

ISPFE_CHANNEL_SELECT

ISPFE_DELAY_LINE_MEMORY

ISPFE_FLUSH_HBLANK

ISPFE_FS_CHANNEL_SELECT

ISPFE_CONFIG_BUFFER_MODE

ISPFE_CLK_DIS

ISPFE_CG_DIS

ISPFE_MODULE_BYPASS

ISPFE_BYPASS_MODE

ISPFE_AE_SWITCH

ISPFE_AWB_SWITCH

ISPFE_HISTOGRAM_SWITCH

ISPFE_HISTOGRAM_PE_SWITCH

ISPFE_GLOBAL_FSM_RESET

ISPFE_FIELD_STATUS

ISPFE_INTERRUPT01

ISPFE_INTERRUPT23

ISPFE_INTERRUPT45

ISPFE_INTERRUPT67

ISPFE_INTERRUPT89

ISPFE_INTERRUPT1011

ISPFE_INTERRUPT1213

ISPFE_INTERRUPT1415

ISPFE_INTERRUPT_STATUS

ISPFE_INTERRUPT_CLEAR

WDR_GAIN_COEF1

WDR_GAIN_COEF2

WDR_GAIN_COEF3

WDR_GAIN_COEF4

SENSOR_OFFSET_WDR_1_BLACK00

SENSOR_OFFSET_WDR_1_BLACK01

SENSOR_OFFSET_WDR_1_BLACK10

SENSOR_OFFSET_WDR_1_BLACK11

SENSOR_OFFSET_WDR_2_BLACK00

SENSOR_OFFSET_WDR_2_BLACK01

SENSOR_OFFSET_WDR_2_BLACK10

SENSOR_OFFSET_WDR_2_BLACK11

SENSOR_OFFSET_WDR_3_BLACK00

SENSOR_OFFSET_WDR_3_BLACK01

SENSOR_OFFSET_WDR_3_BLACK10

SENSOR_OFFSET_WDR_3_BLACK11

SENSOR_OFFSET_WDR_4_BLACK00

SENSOR_OFFSET_WDR_4_BLACK01

SENSOR_OFFSET_WDR_4_BLACK10

SENSOR_OFFSET_WDR_4_BLACK11

INPUTPORT_HC_LIMIT

INPUTPORT_HC_START0

INPUTPORT_HC_SIZE0

INPUTPORT_HC_START1

INPUTPORT_HC_SIZE1

INPUTPORT_VC_LIMIT

INPUTPORT_VC_START

INPUTPORT_VC_SIZE

INPUTPORT_CTRL

INPUTPORT_STATUS

INPUT_FORMATTER_MODE

INPUT_FORMATTER_FACTORML

INPUT_FORMATTER_FACTORMS

INPUT_FORMATTER_BLACKLEVEL

INPUT_FORMATTER_KNEEPOINT01

INPUT_FORMATTER_KNEEPOINT2

INPUT_FORMATTER_SLOPESELECT

VIDEO_TEST_GEN_CTRL

VIDEO_TEST_PATTREN_TYPE

VIDEO_TEST_R_BACKGND

VIDEO_TEST_G_BACKGND

VIDEO_TEST_B_BACKGND

VIDEO_TEST_R_FOREGND

VIDEO_TEST_G_FOREGND

VIDEO_TEST_B_FOREGND

VIDEO_TEST_RGB_GRADIENT

VIDEO_TEST_RGB_GRADIENT_START

VIDEO_TEST_RGB_GRADIENT_START12

VIDEO_TEST_RGB_GRADIENT_START34

VIDEO_TEST_RECT_TOP

VIDEO_TEST_RECT_LEFT

VIDEO_TEST_RECT_RIGHT

SENSOR_OFFSET_BLACK00

SENSOR_OFFSET_BLACK01

SENSOR_OFFSET_BLACK10

SENSOR_OFFSET_BLACK11

NP_RAW_FRONTEND1_EXP_THRESH

NP_RAW_FRONTEND1_SHORT_RATIO

NP_RAW_FRONTEND1_LONG_RATIO

NP_RAW_FRONTEND1_OFF

NP_RAW_FRONTEND2_EXP_THRESH

NP_RAW_FRONTEND2_SHORT_RATIO

NP_RAW_FRONTEND2_LONG_RATIO

NP_RAW_FRONTEND2_OFF

NP_RAW_FRONTEND3_EXP_THRESH

NP_RAW_FRONTEND3_SHORT_RATIO

NP_RAW_FRONTEND3_LONG_RATIO

NP_RAW_FRONTEND3_OFF

NP_RAW_FRONTEND4_EXP_THRESH

NP_RAW_FRONTEND4_SHORT_RATIO

NP_RAW_FRONTEND4_LONG_RATIO

NP_RAW_FRONTEND4_OFF

RAW_FRONTEND1_CTRL1

RAW_FRONTEND1_GE_STRENGTH

RAW_FRONTEND1_DEBUG_SEL

RAW_FRONTEND1_DP_THRESHOLD

RAW_FRONTEND1_GE_THRESHOLD

RAW_FRONTEND1_DP_SLOPE

RAW_FRONTEND1_GE_SLOPE

RAW_FRONTEND1_GE_SENS

RAW_FRONTEND1_DPDEV_THRESHOLD

RAW_FRONTEND1_LINE_THRESH

RAW_FRONTEND1_DP_BLEND

RAW_FRONTEND1_SIGMA_IN

RAW_FRONTEND1_THRESH_SHORT

RAW_FRONTEND1_THRESH_LONG

RAW_FRONTEND2_CTRL1

RAW_FRONTEND2_GE_STRENGTH

RAW_FRONTEND2_DP_THRESHOLD

RAW_FRONTEND2_GE_THRESHOLD

RAW_FRONTEND2_DP_SLOPE

RAW_FRONTEND2_GE_SLOPE

RAW_FRONTEND2_GE_SENS

RAW_FRONTEND2_DPDEV_THRESHOLD

RAW_FRONTEND2_LINE_THRESH

RAW_FRONTEND2_DP_BLEND

RAW_FRONTEND2_SIGMA_IN

RAW_FRONTEND2_THRESH_SHORT

RAW_FRONTEND2_THRESH_LONG

STATIC_DPC_MULTI_CH_MODE

STATIC_DPC_CTRL

STATIC_DPC_OVERFLOW

STATIC_DPC_COUNT

STATIC_DPC_TABLE_START

STATIC_DPC_COUNT_IN

WDR_CTRL

WDR_LONG_CTRL1

WDR_LONG_CTRL2

WDR_LONG_STITCH_ERROR_LIMIT

WDR_MED_CTRL1

WDR_MED_CTRL2

WDR_MED_CTRL3

WDR_MED_STITCH_ERROR_LIMIT

WDR_SHORT_CTRL1

WDR_SHORT_CTRL2

WDR_SHORT_CTRL3

WDR_SHORT_STITCH_ERROR_LIMIT

WDR_BLACK_LEVEL_LONG

WDR_BLACK_LEVEL_MEDIUM1

WDR_BLACK_LEVEL_MEDIUM2

WDR_BLACK_LEVEL_SHORT

WDR_BLACK_LEVEL_OUT

WDR_MODE_IN

FRONTEND_LUT_CTRL

FRONTEND_LUT_MCU_READY

FRONTEND_LUT_ALPHA

DG_GAIN

DG_OFFSET

DNR_CTRL

DNR_RM_CENTER_X

DNR_RM_CENTER_Y

DNR_RM_OFF_CENTER_MULT

DNR_THRESH_H01

DNR_THRESH_H24

DNR_THRESH_V01

DNR_THRESH_V24

DNR_THRESH_SHORT

DNR_THRESH_LONG

DNR_STRENGTH1

DNR_STRENGTH4

BACKEND_LUT_CRTL

BACKEND_LUT_MCU_READY

BACKEND_LUT_ALPHA

NP_FOR_DNR_EXP_THRESH

NP_FOR_DNR_SHORT_RATIO

NP_FOR_DNR_LONG_RATIO

NP_FOR_DNR_OFF

WB_GAIN00

WB_GAIN01

WB_GAIN10

WB_GAIN11

BLC_BLACK00

BLC_BLACK01

BLC_BLACK10

BLC_BLACK11

RADIAL_SHADING_CTRL

RADIAL_SHADING_MCU_READY

RADIAL_SHADING_RX

RADIAL_SHADING_RY

RADIAL_SHADING_GX

RADIAL_SHADING_GY

RADIAL_SHADING_BX

RADIAL_SHADING_BY

RADIAL_SHADING_MULTR

RADIAL_SHADING_MULTG

RADIAL_SHADING_MULTB

MESH_SHADING_CTRL

MESH_SHADING_RELOAD

MESH_SHADING_ALPHAMODE

MESH_SHADING_ALPHA_BANK

MESH_SHADING_ALPHA

MESH_SHADING_STRENGTH

DRC_ENABLE

DRC_CTRL

DRC_BLACK_LEVEL

DRC_WHITE_LEVEL

DRC_STRENGTH_INROI

DRC_STRENGTH_OUTROI

DRC_ROI_HOR_START_END

DRC_ROI_VER_END

DRC_FILTER_MUX

DRC_DARK_ENH

DRC_MCU_READY

DEMOSAIC_VH_SLOPE

DEMOSAIC_AA_SLOPE

DEMOSAIC_VA_SLOPE

DEMOSAIC_UU_SLOPE

DEMOSAIC_SAT_SLOPE

DEMOSAIC_VH_THRESH

DEMOSAIC_AA_THRESH

DEMOSAIC_VA_THRESH

DEMOSAIC_UU_THRESH

DEMOSAIC_SAT_THRESH

DEMOSAIC_VH_OFFSET

DEMOSAIC_AA_OFFSET

DEMOSAIC_VA_OFFSET

DEMOSAIC_UU_OFFSET

DEMOSAIC_SAT_OFFSET

DEMOSAIC_SHARP_ALT_D

DEMOSAIC_SHARP_ALT_UD

DEMOSAIC_LUM_THRESH

DEMOSAIC_NP_OFFSET

DEMOSAIC_DMSC_CONFIG

DEMOSAIC_AC_THRESH

DEMOSAIC_AC_SLOPE

DEMOSAIC_AC_OFFSET

DEMOSAIC_FC_SLPOE

DEMOSAIC_FC_ALIAS_SLPOE

DEMOSAIC_FC_ALIAS_THRESH

DEMOSAIC_NP_OFF

DEMOSAIC_SHARP

DEMOSAIC_MIN_THRESHOLD

DEMOSAIC_SHARPEN_ALG_SELECT

COLOR_MATRIX_COEFFT_RR

COLOR_MATRIX_COEFFT_RG

COLOR_MATRIX_COEFFT_RB

COLOR_MATRIX_COEFFT_GR

COLOR_MATRIX_COEFFT_GG

COLOR_MATRIX_COEFFT_GB

COLOR_MATRIX_COEFFT_BR

COLOR_MATRIX_COEFFT_BG

COLOR_MATRIX_COEFFT_BB

COLOR_MATRIX_CTRL

COLOR_MATRIX_COEFFT_WBR

COLOR_MATRIX_COEFFT_WBG

COLOR_MATRIX_COEFFT_WBB

COLOR_MATRIX_COEFFT_FOG_OFFSETR

COLOR_MATRIX_COEFFT_FOG_OFFSETG

COLOR_MATRIX_COEFFT_FOG_OFFSETB

GAMMA_RGB_CTRL

GAMMA_RGB_MCU_READY

GAMMA_BANK_SELECT

DITHER_CTRL

STATISTICS_AEXP_NODES_USED

STATISTICS_PLANE_TOTAL_0

STATISTICS_PLANE_TOTAL_1

STATISTICS_PLANE_TOTAL_2

STATISTICS_PLANE_TOTAL_3

STATISTICS_PLANE_COUNTED_0

STATISTICS_PLANE_COUNTED_1

STATISTICS_PLANE_COUNTED_2

STATISTICS_PLANE_COUNTED_3

STATISTICS_HISTOGRAM_CTRL

STATISTICS_SCALE

STATISTICS_TOTAL_PIXELS

STATISTICS_COUNTED_PIXELS

STATISTICS_PE_HISTOGRAM_CTRL

STATISTICS_PE_SCALE

STATISTICS_PE_TOTAL_PIXELS

STATISTICS_PE_COUNTED_PIXELS

STATISTICS_PLANE_TOTAL_PE_0

STATISTICS_PLANE_TOTAL_PE_1

STATISTICS_PLANE_TOTAL_PE_2

STATISTICS_PLANE_TOTAL_PE_3

STATISTICS_PLANE_COUNTED_PE_0

STATISTICS_PLANE_COUNTED_PE_1

STATISTICS_PLANE_COUNTED_PE_2

STATISTICS_PLANE_COUNTED_PE_3

STATISTICS_SUM_R

STATISTICS_SUM_RG

STATISTICS_SUM_BG

STATISTICS_SUM_B

STATISTICS_AE_SUM_NODES_USED

STATISTICS_AVG_R

STATISTICS_AVG_G

STATISTICS_AVG_B

STATISTICS_COUNT_ALL

STATISTICS_COUNT_MIN

STATISTICS_COUNT_MAX

STATISTICS_AWB_SUM_NODES_USED

STATISTICS_MIN_THRESHOLD

STATISTICS_MAX_THRESHOLD

STATISTICS_AWB_SUM_CLIP

STATISTICS_CR_REF

STATISTICS_CB_REF

STATISTICS_CR_HL_REF

STATISTICS_CB_HL_REF

FRAME_STATS_STATS_RESET

FRAME_STATS_STATS_HOLD

FRAME_STATS_ACTIVE_WIDTH_MIN

FRAME_STATS_ACTIVE_WIDTH_MAX

FRAME_STATS_ACTIVE_WIDTH_SUM

FRAME_STATS_ACTIVE_WIDTH_NUM

FRAME_STATS_ACTIVE_HEIGHT_MIN

FRAME_STATS_ACTIVE_HEIGHT_MAX

FRAME_STATS_ACTIVE_HEIGHT_SUM

FRAME_STATS_ACTIVE_HEIGHT_NUM

FRAME_STATS_HBLANK_MIN

FRAME_STATS_HBLANK_MAX

FRAME_STATS_HBLANK_SUM

FRAME_STATS_HBLANK_NUM

FRAME_STATS_VBLANK_MIN

FRAME_STATS_VBLANK_MAX

FRAME_STATS_VBLANK_SUM

FRAME_STATS_VBLANK_NUM

NOISE_PROFILE_WDR_4

NOISE_PROFILE_WDR_3

NOISE_PROFILE_WDR_2

NOISE_PROFILE_WDR_1

NOISE_PROFILE_FRAME_STITCH_LUT_1

NOISE_PROFILE_FRAME_STITCH_LUT_2

NOISE_PROFILE_FRAME_STITCH_LUT_3

NOISE_PROFILE_FRAME_STITCH_LUT_4

DNR_SHADING

DNR_SHADING_LAST

NOISE_PROFILE_RAW_FRONTEND_LUT_1

NOISE_PROFILE_RAW_FRONTEND_LUT_2

NOISE_PROFILE_RAW_FRONTEND_LUT_3

NOISE_PROFILE_RAW_FRONTEND_LUT_4

NOISE_PROFILE_LUT

NOISE_PROFILE_DEMOSAIC_LUT

AEXP_WEIGHT

AEXP_WEIGHT_LAST

AEXP_PE_WEIGHT

AEXP_PE_WEIGHT_LAST

AWB_WEIGHT

GAMMA_FE0_MEM0

GAMMA_FE0_MEM1

GAMMA_FE1_MEM0

GAMMA_FE1_MEM1

GAMMA_BE0_MEM0

GAMMA_BE0_MEM1

GAMMA_BE1_MEM0

GAMMA_BE1_MEM1

RADIAL_SHADING_MEM_R

RADIAL_SHADING_MEM_G

RADIAL_SHADING_MEM_B

METERING_MEM

DEFECT_PIXEL_MEM

HISTOGRAM_4CH_MEM

HISTOGRAM1_MEM

HISTOGRAM2_MEM

HISTOGRAM3_MEM

HISTOGRAM4_MEM

GAMMA_RGB_MEM0

GAMMA_RGB_MEM1

DRC_FWD_MEM

DRC_REV_MEM

CMD_QUEUES

SHADING_MEM

ISP_BE_FSTART_DELAY

ISP_BE_USER_DEFINE0

ISP_BE_USER_DEFINE1

ISP_BE_INT

ISP_BE_INT_MASK

ISP_BE_CTRL_F

ISP_BE_CTRL_I

ISP_BE_TIMING_CFG

ISP_BE_REG_UPDATE

ISP_CLIP_Y_CFG

ISP_CLIP_C_CFG

ISP_SKIP_Y_CFG

ISP_SKIP_C_CFG

ISP_CROP_Y_CFG

ISP_CROP_Y_START

ISP_CROP_Y_SIZE

ISP_CROP_C_CFG

ISP_CROP_C_START

ISP_CROP_C_SIZE

ISP_Y_SUM0

ISP_Y_SUM1

ISP_CSC_CFG

ISP_CSC_COEF0

ISP_CSC_COEF1

ISP_CSC_COEF2

ISP_CSC_COEF3

ISP_CSC_COEF4

ISP_CSC_IN_DC0

ISP_CSC_IN_DC1

ISP_CSC_OUT_DC0

ISP_CSC_OUT_DC1

ISP_MCDS_CFG

ISP_HCDS_SIZE

ISP_MIDF_SIZE

ISP_MCDS_PARA

ISP_MCDS_SIZE

ISP_SHARPEN_CFG

ISP_SHARPEN_AMT

ISP_SHARPEN_SHOOTAMT

ISP_SHARPEN_EDGEJAG

ISP_SHARPEN_OSHTJAG

ISP_SHARPEN_USHTJAG

ISP_SHARPEN_MID0

ISP_SHARPEN_MID1

ISP_SHARPEN_MID2

ISP_SHARPEN_LINETHD

ISP_SHARPEN_THD2

ISP_SHARPEN_CTRL

ISP_SHARPEN_LUMATH

ISP_SHARPEN_LUMAWGT

ISP_SHARPEN_OSHTVARTH

ISP_SHARPEN_OSHTVAR

ISP_SHARPEN_USHTVARTH

ISP_SHARPEN_USHTVAR

ISP_SHARPEN_OSHTLUMA

ISP_SHARPEN_USHTLUMA

ISP_SHARPEN_SHIFT

ISP_SHARPEN_SIZE

ISP_DEHAZE_CFG

ISP_DEHAZE_PRE_UPDATE

ISP_DEHAZE_BLK_SIZE

ISP_DEHAZE_BLK_SUM

ISP_DEHAZE_DC_SIZE

ISP_DEHAZE_X

ISP_DEHAZE_Y

ISP_DEHAZE_STAT_MODE

ISP_DEHAZE_NEG_MODE

ISP_DEHAZE_AIR

ISP_DEHAZE_THLD

ISP_DEHAZE_GSTRTH

ISP_DEHAZE_BLTHLD

ISP_DEHAZE_STR_LUT_UPDATE

ISP_DEHAZE_MINSTAT_WADDR

ISP_DEHAZE_MINSTAT_WDATA

ISP_DEHAZE_MINSTAT_RADDR

ISP_DEHAZE_MINSTAT_RDATA

ISP_DEHAZE_MAXSTAT_WADDR

ISP_DEHAZE_MAXSTAT_WDATA

ISP_DEHAZE_MAXSTAT_RADDR

ISP_DEHAZE_MAXSTAT_RDATA

ISP_DEHAZE_PRESTAT_WADDR

ISP_DEHAZE_PRESTAT_WDATA

ISP_DEHAZE_PRESTAT_RADDR

ISP_DEHAZE_PRESTAT_RDATA

ISP_DEHAZE_LUT_WADDR

ISP_DEHAZE_LUT_WDATA

ISP_DEHAZE_LUT_RADDR

ISP_DEHAZE_LUT_RDATA

ISP_DEHAZE_SIZE

ISP_DCI_CFG

ISP_DCICTRL

ISP_DCIHISBLD

ISP_DCIHISOFT

ISP_DCIHISCOR

ISP_DCIMERBLD

ISP_DCIADJWGT

ISP_DCICLIP0

ISP_DCICLIP1

ISP_DCICLIP2

ISP_DCIGLBGAIN

ISP_DCIPOSTHR0

ISP_DCIPOSTHR1

ISP_DCIPOSGAIN0

ISP_DCIPOSGAIN1

ISP_DCIPOSSLP0

ISP_DCIPOSSLP1

ISP_DCIPOSSLP2

ISP_DCINEGTHR0

ISP_DCINEGTHR1

ISP_DCINEGGAIN0

ISP_DCINEGGAIN1

ISP_DCINEGSLP0

ISP_DCINEGSLP1

ISP_DCINEGSLP2

ISP_BINWGT0_WADDR

ISP_VDDCIBINWGT0

ISP_BINWGT0_RADDR

ISP_VDDCIBINWGT0_RDATA

ISP_BINWGT1_WADDR

ISP_VDDCIBINWGT1

ISP_BINWGT1_RADDR

ISP_VDDCIBINWGT1_RDATA

ISP_BINWGT2_WADDR

ISP_VDDCIBINWGT2

ISP_BINWGT2_RADDR

ISP_VDDCIBINWGT2_RDATA

ISP_ADJLUT0_WADDR

ISP_VDDCIADJLUT0

ISP_ADJLUT0_RADDR

ISP_VDDCIADJLUT0_RDATA

ISP_ADJLUT1_WADDR

ISP_VDDCIADJLUT1

ISP_ADJLUT1_RADDR

ISP_VDDCIADJLUT1_RDATA

ISP_ADJLUT2_WADDR

ISP_VDDCIADJLUT2

ISP_ADJLUT2_RADDR

ISP_VDDCIADJLUT2_RDATA

ISP_DCI_CTRL_I

ISP_DCI_UPDATE

ISP_DCI_SIZE

ISP_DCIADJSW0

ISP_DCIADJSW1

ISP_DCIADJSW2

ISP_DCIADJSW3

ISP_DCIADJSW4

ISP_DCIADJSW5

ISP_DCIADJSW6

ISP_DCIADJSW7

ISP_DCIADJSW8

ISP_DCIADJSW9

ISP_DCIADJSW10

ISP_DCI_SPLIT

ISP_DCI_MBLEND

ISP_DCI_HIST_CLIP

ISP_DCICTRL2

ISP_DCI_TOTAL_PIX_BS

ISP_DCIHPOS

ISP_DCIVPOS

ISP_DCI_OUT_HREGION

ISP_DCI_OUT_VREGION

ISP_DCI_BLEND

ISP_DCI_BS_EN

ISP_DCI_BLACK0_STRETCH

ISP_DCI_BLACK1_STRETCH

ISP_DCI_BLACK2_STRETCH

ISP_DCI_NEW_POINT

ISP_DIVLUT_WADDR

ISP_VDDCIDIVLUT

ISP_DIVLUT_RADDR

ISP_VDDCIDIVLUT_RDATA

ISP_BSDELTA_WADDR

ISP_DCIBSDELTA

ISP_BSDELTA_RADDR

ISP_DCIBSDELTA_RDATA

ISP_HIST32_RADDR

ISP_HIST32_RDATA

ISP_ACM_CTRL

ISP_ACM_ADJ

ISP_ACM_SIZE

ISP_ACM_PARA_ADDR

ISP_ACM_PARA_UP

ISPFE_MAX_ADDR

ISPFE_MAX_ADDR2

ISPFE_MAX_ADDR_NR1

ISPFE_MAX_ADDR_NR2

ISPFE_TIMING

ISPFE_MAX_ADDR3

ISPFE_MAX_ADDR4

ISPFE_BYTE_EN

ISPFE_CH_SWITCH

ISPFE_FE_BYPASS_CFG

ISPFE_CROP_CFG

ISPFE_CROP_WIN

ISPFE_CROP0_START

ISPFE_CROP0_SIZE

ISPFE_HSYNC_INT_CFG

ISPFE_INT

ISPFE_INT_MASK

ISP_DIS_CFG

ISP_DIS_BLK

ISP_DIS_V0POS

ISP_DIS_V4POS

ISP_DIS_V8POS

ISP_DIS_V0POSE

ISP_DIS_V4POSE

ISP_DIS_V8POSE

ISP_DIS_H0POS

ISP_DIS_H4POS

ISP_DIS_H8POS

ISP_DIS_H0POSE

ISP_DIS_H4POSE

ISP_DIS_H8POSE

ISP_DIS_RAW_LUMA

ISP_DIS_GAMMA_EN

ISP_DIS_H_STAT_RADDR

ISP_DIS_H_STAT_RDATA

ISP_DIS_V_STAT_RADDR

ISP_DIS_V_STAT_RDATA

ISP_DIS_CTRL_F

ISP_DIS_CTRL_I

ISP_DIS_UPDATE

ISP_FPN_CFG

ISP_FPN_CALIB_START

ISP_FPN_CORR_CFG

ISP_FPN_STAT

ISP_FPN_WHITE_LEVEL

ISP_FPN_DIVCOEF

ISP_FPN_FRAMELOG2

ISP_FPN_SUM0

ISP_FPN_SUM1

ISP_FPN_CORR0

ISP_FPN_CORR1

ISP_FPN_CORR2

ISP_FPN_CORR3

ISP_FPN_SHIFT

ISP_FPN_MAX_O

ISP_FPN_OVERFLOWTHR

ISP_FPN_LINE_WADDR

ISP_FPN_LINE_WDATA

ISP_FPN_LINE_RADDR

ISP_FPN_LINE_RDATA

ISP_FPN_CTRL_F

ISP_FPN_CTRL_I

ISP_FPN_TIMING

ISP_FPN_UPDATE

ISP_FPN_SIZE

10 Audio Interfaces

Contents

Figures

Tables

10.1 AIAO

10.1.1 Overview

10.1.2 Features

PCM Interfaces

I2S Interfaces

10.1.3 Function Description

Typical Application

Function Principle

10.1.4 Operating Mode

Channel Multiplexing Configuration

Clock Gating and Configuration

Soft Reset

Recording Process

Playback Process

10.1.5 Register Summary

10.1.6 Register Description

AIAO_INT_ENA

AIAO_INT_STATUS

AIAO_INT_RAW

I2S_CRG_CFG0_00

I2S_CRG_CFG1_00

I2S_CRG_CFG1_08

RX_IF_ATTRI

RX_DSP_CTRL

RX_BUFF_SADDR

RX_BUFF_SIZE

RX_BUFF_WPTR

RX_BUFF_RPTR

RX_BUFF_ALFULL_TH

RX_TRANS_SIZE

RX_INT_ENA

RX_INT_RAW

RX_INT_STATUS

RX_INT_CLR

TX_IF_ATTRI

TX_DSP_CTRL

TX_BUFF_SADDR

TX_BUFF_SIZE

TX_BUFF_WPTR

TX_BUFF_RPTR

TX_BUFF_ALEMPTY_TH

TX_TRANS_SIZE

TX_INT_ENA

TX_INT_RAW

TX_INT_STATUS

TX_INT_CLR

10.2 Audio CODEC

10.2.1 Overview

10.2.2 Features

10.2.3 Function Description

Recording Mode

Playing Mode

10.2.4 Register Summary

10.2.5 Register Description

11 Peripherals

Contents

Figures

Tables

11.1 I2C Controller

11.1.1 Overview

11.1.2 Function Description

11.1.3 Timing Description

Single Write Timing in Standard Timing Mode

Single Read Timing in Standard Timing Mode

Consecutive Write Timing in Standard Timing Mode

Consecutive Read Timing in Standard Timing Mode

Non-standard Timing

Timing of Bytes on the SDA Traces

11.1.4 Operating Mode

11.1.4.1 Timing Mode Selection

11.1.4.2 Operation Process

Standard Timing Operation Process

Non-standard Timing Operation Process

Non-standard Data Read Process

11.1.5 Register Summary

11.1.6 Register Description

I2C_CON

I2C_TAR

I2C_DATA_CMD

I2C_SCL_HCNT

I2C_SCL_LCNT

I2C_INTR_STAT

I2C_INTR_MASK

I2C_INTR_RAW

I2C_CLR_INTR

I2C_ENABLE

I2C_STATUS

I2C_SDA_HOLD

I2C_TX_ABRT_SRC

I2C_DMA_CR

I2C_DMA_TDLR

I2C_DMA_RDLR

I2C_LOCK

I2C_MST_SINGLE_CTRL

I2C_MST_SINGLE_CMD

I2C_SEQUENCE_CMD0

I2C_SEQUENCE_CMD1

I2C_SEQUENCE_CMD2

MODE2_I2C_CTRL

MODE2_I2C_COM

MODE2_I2C_ICR

MODE2_I2C_SR

MODE2_I2C_SCL_H

MODE2_I2C_SCL_L

MODE2_I2C_TXR

MODE2_I2C_RXR

11.2 UART

11.2.1 Overview

11.2.2 Features

11.2.3 Function Description

Application Block Diagram

Function Principle

11.2.4 Operating Mode

11.2.4.1 Baud Rate Configuration

11.2.4.2 Soft Reset

11.2.4.3 Data Transfer in Interrupt or Query Mode

Initialization

Data Transmission

Data Reception

11.2.4.4 Data Transfer in DMA Mode

Initialization

Data Transfer

Data Reception

11.2.5 Register Summary

11.2.6 Register Description

UART_DR

UART_RSR

UART_FR

UART_IBRD

UART_FBRD

UART_LCR_H

UART_CR

UART_IFLS

UART_IMSC

UART_RIS

UART_MIS

UART_ICR

UART_DMACR

11.3 SPI

11.3.1 Overview

11.3.2 Features

11.3.3 Function Description

Typical Application

11.3.4 Peripheral Bus Timings

SPI

TI Synchronous Serial Interface

National Semiconductor Microwire Interface

11.3.5 Operating Mode

Working Modes

Clock and Reset

Interrupts

Initialization

Data Transfer in Query Mode

Data Transfer in Interrupt Mode

Data Transfer in DMA Mode

11.3.6 Register Summary

11.3.7 Register Description

SPICR0

SPICR1

SPIDR

SPISR

SPICPSR

SPIIMSC

SPIRIS

SPIMIS

SPIICR

SPIDMACR

SPITXFIFOCR

SPIRXFIFOCR

11.4 3-Wire SPI

11.4.1 Operating Mode

11.4.2 spi_3wire Register Summary

11.4.3 spi_3wire Register Description

SPI_3WIRE_COEF0

SPI_3WIRE_COEF1

SPI_3WIRE_COEF2

11.5 eMMC/SD/SDIO Controller

11.5.1 Function Description

Functional Block Diagram

Typical Application

Commands and Responses

Data Transfer

Speed Mode and Voltage Switching Supported by SD3.0

11.5.2 Application Notes

Clock Gating

Soft Reset

Configuring the Working Clock

Configuring the Interface Clock

Initialization

Non-Data Transfer Command

Reading a Single Data Block or Multiple Data Blocks

Writing a Single Data Block or Multiple Data Blocks

Reading/Writing Stream Data

Transferring Data in ADMA3 Mode

Initializing the ADMA3

Transferring Data by Using the IDMAC

Descriptor

Initialization

Transmission

Reception

Auto-Stop Function Configuration

Stopping or Aborting the Data Transfer

Suspend and Resume Operations

Read Wait Operation

11.5.3 Register Summary

11.5.4 Register Description

MMC_CTRL

MMC_PWREN

MMC_CLKDIV

MMC_CLKENA

MMC_TMOUT

MMC_CTYPE

MMC_BLKSIZ

MMC_BYTCNT

MMC_INTMASK

MMC_CMDARG

MMC_CMD

MMC_RESP0

MMC_RESP1

MMC_RESP2

MMC_RESP3

MMC_MINTSTS

MMC_RINTSTS

MMC_STATUS

MMC_FIFOTH

MMC_CDETECT

MMC_WRTPRT

MMC_TCBCNT

MMC_TBBCNT

MMC_DEBNCE

MMC_UHS_REG

MMC_CARD_RSTN

MMC_BMOD

MMC_PLDMND

MMC_DBADDR

MMC_IDSTS

MMC_IDINTEN

MMC_DSCADDR

MMC_BUFADDR

ADMA_CONTROL

ADMA_IDS_ADDR

ADMA_DEEPTH

ADMA_ID_RDPTR

ADMA_ID_WRPTR

ADMA_TIMEOUT

MMC_CARDTHRCTL

MMC_UHS_REG_EXT

MMC_DDR_REG

MMC_ENABLE_SHIFT

MMC_DATA

11.6 IR Interface

11.6.1 Overview

11.6.2 Features

11.6.3 Function Description

11.6.3.1 NEC with Simple Repeat Code

Frame Format

Code Format

11.6.3.2 NEC with Full Repeat Code

Frame Format

Code Format

11.6.3.3 TC9012 Code

Frame Format

Code Format

11.6.3.4 SONY Code

Frame Format

Code Format

11.6.4 Operating Mode

Working Clock and Soft Reset

Instances of Configuring Registers

11.6.5 Register Summary

11.6.6 Register Description

IR_EN

IR_CFG

IR_LEADS

IR_LEADE

IR_SLEADE

IR_B0

IR_B1

IR_BUSY

IR_DATAH

IR_DATAL

IR_INT_MASK

IR_INT_STATUS

IR_INT_CLR

IR_START

11.7 GPIO

11.7.1 Overview

11.7.2 Features

11.7.3 Operating Mode

Interface Reset

GPIO

Interrupt Operation

11.7.4 Register Summary

11.7.5 Register Description

GPIO_DATA

GPIO_DIR

GPIO_IS

GPIO_IBE

GPIO_IEV

GPIO_IE

GPIO_RIS

GPIO_MIS

GPIO_IC

11.8 PCIe

11.8.1 Overview

11.8.2 Features

11.8.3 Signal Description

11.8.4 Function Description

RC Mode

EP Mode

11.8.5 Operating Mode

11.8.5.1 Clock and Reset

Clock

Soft Reset

11.8.5.2 Enabling the PCIe Controller

11.8.5.3 Initiating the PCIe Transaction by the CPU

Configuration Transaction

Memory Transaction

I/O transaction

11.8.5.4 Initiating a PCIe Transaction by the DMA

DMA Control Register

Enabling DMA Read/Write Channels

Source Address (SAR) and Target Address (DAR) of the DMA

DMA Transfer Length

Starting the DMA Transfer

Stopping the DMA transfer

DMA Interrupt

11.8.5.5 Address Translation

Address Space

ATU

ATU Control Register

11.8.6 PCIe Controller Registers

11.8.6.1 Register Summary

11.8.6.2 Register Description

ATU_VIEWPORT

ATU_REGION_CTRL1

ATU_REGION_CTRL2

ATU_BASE_LOW

ATU_BASE_HIGH

ATU_LIMIT

ATU_TARGET_LOW

ATU_TARGET_HIGH

11.8.6.3 Register Summary

11.8.6.4 Register Description

DMA_WR_ENGINE_EN

DMA_WR_DOORBELL

DMA_RD_ENGINE_EN

DMA_RD_DOORBELL

DMA_WR_INT_STAT

DMA_WR_INT_MASK

DMA_WR_INT_CLR

DMA_WR_ERR_STAT

DMA_WR_DONE_IMWR_ADDR_LOW

DMA_WR_DONE_IMWR_ADDR_HIGH

DMA_WR_ABORT_IMWR_ADDR_LOW

DMA_WR_ABORT_IMWR_ADDR_HIGH

DMA_WR_IMWR_DATA_0

DMA_RD_INT_STAT

DMA_RD_INT_MASK

DMA_RD_INT_CLR

DMA_RD_ERR_STAT_LOW

DMA_RD_ERR_STAT_HIGH

DMA_RD_DONE_IMWR_ADDR_LOW

DMA_RD_DONE_IMWR_ADDR_HIGH

DMA_RD_ABORT_IMWR_ADDR_LOW

DMA_RD_ABORT_IMWR_ADDR_HIGH

DMA_RD_IMWR_DATA

DMA_CH_INDEX

DMA_CH_CTRL

DMA_TRANS_SIZE

DMA_SAR_LOW

DMA_SAR_HIGH

DMA_DAR_LOW

DMA_DAR_HIGH

11.8.6.5 Register Summary

11.8.6.6 PCIe Internal System Control Register Description

PCIE_SYS_CTRL0

PCIE_SYS_CTRL1

PCIE_SYS_CTRL2

PCIE_SYS_CTRL7

PERI_PCIE_STAT

11.9 USB 2.0

11.9.1 Overview

11.9.2 Function Description

Logic Block Diagram

Typical Application

Functions

Working Principle

11.9.3 Operating Mode

Host/Device Switching

Pin Polarity Control

Clock Gating

Reset Deassert

Separately Resetting Ports During the Working Process

Variables in the Offset Addresses for USB 2.0 Registers

11.9.4 Register Summary

USB HOST Register

USB Device Register Overview

11.9.5 Register Description

11.9.5.1 USB HOST Register Description

INTNREG00

INSNREG01

INSNREG02

INSNREG03

INTNREG04

INTNREG05

INTNREG06

INTNREG07

11.9.5.2 USB Device Register Description

GOTGCTL

GOTGINT

GAHBCFG

GUSBCFG

GRSTCTL

GINTSTS

GINTMSK

GRXSTSR

GRXSTSP

GRXFSIZ

GNPTXFSIZ

GNPTXSTS

GI2CCTL

GPVNDCTL

GGPIO

GUID

GSNPSID

GHWCFG1

GHWCFG2

GHWCFG3

GHWCFG4

GLPMCFG

GPWRDN

GDFIFOCFG

GADPCTL

HPTXFSIZ

DPTXFSIZN

DIEPTXFN

DCFG

DCTL

DSTS

DIEPMSK

DOEPMSK

DAINT

DAINTMSK

DTKNQR1

DTKNQR2

DTKNQR3

DTKNQR4

DVBUSDIS

DVBUSPULSE

DTHRCTL

DIEPEMPMSK

DEACHINT

DEACHINTMSK

DIEPEACHMSKN

DOEPEACHMSKN

DIEPCTL0

DOEPCTL0

DIEPCTLN

DOEPCTLN

DIEPINTn

DOEPINTn

DIEPTSIZ0

DOEPTSIZ0

DIEPTSIZn

DOEPTSIZn

DIEPDMAN

DOEPDMAN

DIEPDMABN

DOEPDMABN

DTXFSTSn

11.10 USB 3.0 DRD

11.10.1 Overview

11.10.2 Function Description

Logical Block Diagram

Typical Applications

Features

Function Implementation

11.10.3 Operating Mode

Clock and Reset

Host/Device Mode Switchover

11.10.4 Register Summary

11.10.5 USB3.0 Register Description

PERI_USB3_GSBUSCFG0

PERI_USB3_GSBUSCFG1

PERI_USB3_GTXTHRCFG

PERI_USB3_GRXTHRCFG

PERI_USB3_GCTL

PERI_USB3_GSTS

PERI_USB3_GUCTL1

PERI_USB3_GGPIO

PERI_USB3_GUID

PERI_USB3_GUCTL

PERI_USB3_GBUSERRADDR_HI

PERI_USB3_GBUSERRADDR_LO

PERI_USB3_GPRTBIMAP_HI

PERI_USB3_GPRTBIMAP_LO

PERI_USB3_GPRTBIMAP_HS_HI

PERI_USB3_GPRTBIMAP_HS_LO

PERI_USB3_GPRTBIMAP_FS_HI

PERI_USB3_GPRTBIMAP_FS

PERI_USB3_GUSB2PHYCFGN

PERI_USB3_GUSB3PIPECTLN

PERI_USB3_GTXFIFOSIZN

PERI_USB3_GRXFIFOSIZN

PERI_USB3_GEVNTADRN_HI

PERI_USB3_GEVNTADRN_LO

PERI_USB3_GEVNTSIZN

PERI_USB3_GEVNTCOUNTN

PERI_USB3_GTXFIFOPRIDEV

PERI_USB3_GTXFIFOPRIHST

PERI_USB3_GRXFIFOPRIHST

PERI_USB3_GFIFOPRIDBC

PERI_USB3_GDMAHLRATIO

PERI_USB3_GFLADJ

PERI_USB3_DCFG

PERI_USB3_DCTL

PERI_USB3_DEVTEN

PERI_USB3_DSTS

PERI_USB3_DGCMDPAR

PERI_USB3_DGCMD

PERI_USB3_DALEPENA

PERI_USB3_DEPCMDPAR2N

PERI_USB3_DEPCMDPAR1N

PERI_USB3_DEPCMDPAR0N

PERI_USB3_DEPCMDN

11.11 LSADC

11.11.1 Overview

11.11.2 Features

11.11.3 Operating Mode

Single Scanning Procedure

Continuous Scanning Procedure

Deglitch Procedure

Sampling Depth Configuration

11.11.4 Register Summary

11.11.5 Register Description

LSADC_CTRL0

LSADC_CTRL1

LSADC_CTRL2

LSADC_CTRL4

LSADC_CTRL5

LSADC_CTRL6

LSADC_CTRL7

LSADC_CTRL8

LSADC_CTRL9

LSADC_CTRL10

LSADC_CTRL12

LSADC_CTRL13

LSADC_CTRL14

11.12 PWM

11.12.1 Overview

11.12.2 Features

11.12.3 Operating Mode

11.12.4 Register Summary

11.12.5 Register Description

PWM0_CFG0

PWM0_CFG1

PWM0_CFG2

PWM0_CTRL

PWM0_STATE0

PWM0_STATE1

PWM0_STATE2

12 Security Modules

Contents

Figures

Tables

12.1 Cipher

12.1.1 Overview

12.1.2 Features

12.1.3 Function Description

3DES Algorithm

ECB Mode

CBC Mode

CFB Mode

OFB Mode

CTR Mode

CCM Mode

GCM Mode

12.1.4 Operating Mode

Single-Block Operation Process of the Cipher Module

Multi-Block Operation Process of the Cipher Module

Clock Gating

Soft Reset

12.1.5 Register Summary

12.1.6 Register Description

CHAN0_CIPHER_DOUT

CHAN0_CIPHER_IVOUT

CHAN_CIPHER_IVOUT

CIPHER_KEY

CHAN0_GCM_A_LEN_0

CHAN0_GCM_A_LEN_1

CHAN1_GCM_A_LEN_0

CHAN1_GCM_A_LEN_1

CHAN2_GCM_A_LEN_0

CHAN2_GCM_A_LEN_1

CHAN3_GCM_A_LEN_0

CHAN3_GCM_A_LEN_1

CHAN4_GCM_A_LEN_0

CHAN4_GCM_A_LEN_1

CHAN5_GCM_A_LEN_0

CHAN5_GCM_A_LEN_1

CHAN6_GCM_A_LEN_0

CHAN6_GCM_A_LEN_1

CHAN7_GCM_A_LEN_0

CHAN7_GCM_A_LEN_1

CHAN0_GCM_PC_LEN_0

CHAN0_GCM_PC_LEN_1

CHAN1_GCM_PC_LEN_0

CHAN1_GCM_PC_LEN_1

CHAN2_GCM_PC_LEN_0

CHAN2_GCM_PC_LEN_1

CHAN3_GCM_PC_LEN_0

CHAN3_GCM_PC_LEN_1

CHAN4_GCM_PC_LEN_0

CHAN4_GCM_PC_LEN_1

CHAN5_GCM_PC_LEN_0

CHAN5_GCM_PC_LEN_1

CHAN6_GCM_PC_LEN_0

CHAN6_GCM_PC_LEN_1

CHAN7_GCM_PC_LEN_0

CHAN7_GCM_PC_LEN_1

CHAN0_3_GCM_IV_LEN

CHAN4_7_GCM_IV_LEN

CHANn_GCM_IV_LEN_VLD

CHANn_GCM_TAG_VLD

CHANn_GCM_GHASH_A_END

CHANn_GCM_TAG_0

CHANn_GCM_TAG_1

CHANn_GCM_TAG_2

CHANn_GCM_TAG_3

CHAN0_CIPHER_CTRL

CHAN0_CIPHER_IVIN

CHAN0_CIPHER_DIN

CHANn_IBUF_NUM

CHANn_IBUF_CNT

CHANn_IEMPTY_CNT

CHANn_INT_ICNTCFG

CHANn_CIPHER_CTRL

CHANn_SRC_LST_SADDR

CHANn_IAGE_TIMER

CHANn_OBUF_NUM

CHANn_OBUF_CNT

CHANn_OFULL_CNT

CHANn_INT_OCNTCFG

CHANn_DEST_LST_SADDR

CHANn_OAGE_TIMER

INT_STATUS

INT_EN

INT_RAW

RST_STATUS

CHAN0_CFG

12.2 HASH

12.2.1 Overview

12.2.2 Features

12.2.3 Function Description

12.2.4 Operating Mode

SHA1 Operation Process in CPU Mode

SHA1 Operation Process in DMA Mode

SHA256 Operation Process in CPU Mode

SHA256 Operation Process in DMA Mode

HMAC_SHA1 Operation Process in CPU Mode

HMAC_SHA1 Operation Process in DMA Mode

HMAC_SHA256 Operation Process in CPU Mode

HMAC_SHA256 Operation Process in DMA Mode

Clock Gating

Soft Reset

12.2.5 Register Summary

12.2.6 Register Description

TOTAL_LEN1

TOTAL_LEN2

HASH_STATUS

HASH_CTRL

SHA_START

DMA_START_ADDR

DMA_LEN

DATA_IN

REC_LEN1

REC_LEN2

SHA_OUT1

SHA_OUT2

SHA_OUT3

SHA_OUT4

SHA_OUT5

SHA_OUT6

SHA_OUT7

SHA_OUT8

MCU_KEY0

MCU_KEY1

MCU_KEY2

MCU_KEY3

SHA_INIT1_UPDATE

SHA_INIT2_UPDATE

SHA_INIT3_UPDATE

SHA_INIT4_UPDATE

SHA_INIT5_UPDATE

SHA_INIT6_UPDATE

SHA_INIT7_UPDATE

SHA_INIT8_UPDATE

12.3 HISEC_TRNG_CTRL

12.3.1 Overview

12.3.2 Features

12.3.3 Operating Mode

HISEC_TRNG_CTRL Operation Process

12.3.4 Register Summary

12.3.5 Register Description

HISEC_COM_TRNG_CTRL

HISEC_COM_TRNG_FIFO_DATA

HISEC_COM_TRNG_DATA_ST

HISEC_COM_TRNG_ERR0_CNT

HISEC_COM_TRNG_ERR1_CNT

HISEC_COM_TRNG_ERR2_CNT

HISEC_COM_TRNG_ERR3_CNT

12.4 RSA

12.4.1 Overview

12.4.2 Features

12.4.3 Function Description

12.4.4 Operating Mode

Encrypting/Decrypting Data by Using RSA

Debugging the Key by Using CRC16

Clearing the RAM

12.4.5 Register Summary

12.4.6 Register Description

SEC_RSA_BUSY_REG

SEC_RSA_MOD_REG

SEC_RSA_WSEC_REG

SEC_RSA_WPKT_REG

SEC_RSA_RPKT_REG

SEC_RSA_RRSLT_REG

SEC_RSA_START_REG

SEC_RSA_ADDR_REG

SEC_RSA_ERROR_REG

SEC_CRC16_REG

12.5 OTP Key Ctrl

12.5.1 Operating Mode

12.5.1.1 Burning the Key to the OTP

12.5.1.2 Reading the Key Use Status in the OTP

12.5.1.3 Loading the Key to the Cipher or RSA Key Management Module

12.5.1.4 Loading the Key to the Hash

12.5.2 OTP Key Ctrl Register Summary

12.5.3 OTP Key Ctrl Register Description

KL_WKEY0

KL_WKEY1

KL_WKEY2

KL_WKEY3

KL_CTRL

KL_STA

KL_STA1

RBC_WKEY0_STA

RBC_WKEY1_STA

RBC_WKEY2_STA

RBC_WKEY3_STA

13 Differences Between Hi3556 V100 and Hi3559 V100

A Ordering Information

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc