Π

折叠式共源共栅运算放大器的 0. 6μm CMOS 设计

王志亮 , 段 伟 , 王 琴

(南通大学电子信息学院 , 南通 226007)

2009 年第 3 期

信息技术

Information Technology

中图分类号 :TN432 文献标识码 :A 文章编号 :1009 - 2552 (2009) 03 - 0007 - 04

摘 要 : 折叠式共源共栅结构的运算放大器不仅能提高增益 、增加电源电压噪声抑制能力 , 而

且在输出端允许自补偿 。基于0. 6μm CMOS 工艺 , 验证了一种折叠共源共栅的运算放大器的参数

指标 。理论计算和实际分析相结合 , 仿真结果达到设计指标要求 。

关键词 : 0. 6μm CMOS 工艺 ; 折叠式共源共栅 ; 运算放大器 ; Hspice

Design of a folded

cascade operational amplifier

based on 0. 6μm CMOS technology

WANG Zhi

liang , DUAN Wei , WANG Qin

(School of Electronics and Information , Nantong University , Nantong 226007 ,China)

Abstract : Operational amplifier using the cascade configuration not only is useful for increasing the gain ,

increasing the value of PSRR , but also allowing self compensation at the output. The parameter of this

operational amplifier is validated based on 0. 6μm CMOS technology. Combined with the theory calculation and

actual analysis , the simulation result satisfied the design specification.

Key words : 0. 6μm CMOS ; folded

cascade ; operational amplifier ; Hspice

0 引言

随着集成电路技术的不断发展 ,高性能运算放

大器得到广泛应用 ,成为模拟集成电路和混合信号

集成电路设计的核心单元电路 ,其性能直接影响电

路及系统的整体性能 。

折叠式共源共栅运算运算放大器具有二阶优化

性能 ,因此设计一个有实用价值的折叠式共源共栅

运算放大器是非常有现实意义的 。在实际设计过程

中 ,电路设计固然重要 ,参数正确选取同样决定设计

成败 。CMOS 管的参数并不能通过简单的理论计算

或计算机仿真进行准确的预测 ,例如在给定工艺条

件下 ,理论计算出的管子宽长如不考虑实际情况下

工艺条件等诸多外界因素 ,仿真的结果会和设计指

标有很大差距 。所以必须在深入理解电路工作原理

的基础上 ,将科学计算和计算机仿真综合运用 。

1 折叠式共源共栅运算放大器的参数设计

本文采用图 1 所示折叠式共源共栅运算放大器

结构[1 ] 。

其中 :

M1

M3

M2

M3A

M1A

M2A :构成折叠式差分电路 。

M4A :构成共源共栅电路 。

M4

M6 :构成运放偏置的电流镜电路 。

M5

M8 :构成 M9 ,M10 and M11 的镜像 MOS 管 。

M7 :差分电路的尾电流 NMOS 管 。

M9

M13

M10 :构成运放两支路的偏置电流源 。

M14 : 提供 给 M1A

M2A

M3A

M4A 栅 极 +

1V 的偏置电压 。

M12 :输出级 (共源放大器) 。

M11

基于 0. 6μm CMOS 工艺 ,运算放大器的设计指

标如表 1 所示 :

收稿日期 : 2008 - 08 - 07

基金项目 : 南通大学大学生课外学术科技作品立项课题 (140

146) ;

江苏省教育厅自然科学基金 (07KJD120167)

作者简介 : 王志亮 (1978 - ) ,男 ,讲师 ,硕士 ,主要从事模拟集成电路

研究。

—7—

�

Π

图 1 运算放大器电路图

表 1 设计指标

参数 小信号低频电压增益 单位增益带宽 相位裕度 转换速率 共模抑制比 电源电压 共模输入范围 电压输出范围 负载电容 功耗

指标

> 10000 (80dB)

> 100MHz

> 50° 100V

us

> 80dB

5V

1. 5V~3. 5V 0. 3V~4. 7V

2pF

17mW

根据以上给出的性能指标 ,结合 CMOS 器件理

论计算公式 ,计算出各 MOS 管理论参数 。计算过程

如下 :

取μp Cox = 44 ×10- 6μA

因为 SR = IS

取(W

V2 ,μnCox = 108 ×10- 6μA

CL ,所以 IS = SR ×CL = 200μA ;

V2 ,

L) 5 = (W

L) 6 = (W

0. 6 ,因

为管子 M8 工作于饱和状态 ,所以 ID8 = - KP (VGS8 -

Vth) 2 ,得 VGS8 = 1. 37V ,Vbias = 3. 63V ;

L) 7 = (W

L) 8 = 30

43. 8

(W

L) 2A = 22. 9

0. 6 ;

同理取 Veff1A = 0. 25V ,根据公式 ID = - KpV2

L) 1A = (W

取 VGS = 0. 882V ,得 (W

取 Veff3A ,4A = 0. 25V ,得 (W

对 M13 而言 ,VGS = - 1. 37V

L) 3A ,4A = 9. 33

L) 3 ,4 = 17. 6

0. 6 ;

0. 6 ;

0. 6 ;

eff ,得

(W

L) 13 =

μp Cox·(Vgs13 - Vth ) 2 = 86. 4

0. 6

2ID13

M9 ,M10 两管对称 , ID9 = - KP (VGS9 - Vth ) 2 , (W

同理 ,VGS11 = - 1. 37V , ID11 = 1500μA , (W

L) 11 =

L) 9 ,10 = 18. 52

0. 6 ;

185. 2

0. 6 ;

因为 fu = 100MHz ,ωta = gm

CL ,所以 gm = 2πfuCL =

1. 256ms ;

根据公式 ( W

L

) =

g2

m

2IDμnCox

,得 (W

L) 1 = (W

L) 2 =

取 Veff12 = 0. 25V ,3. 14 , (W

同样取 Veff14 = 0. 25V , (W

各 MOS 管理论计算结果如表 2 所示 :

L) 12 = 267

L) 14 = 124

0. 6 ;

0. 6 。

表 2 MOS 管理论计算结果

MOS 管名称

MOS 宽度 (单位μm)

MOS 管长 (单位μm)

M1 ,M2

M3 ,M4

M5 ,M6 ,M7 ,M8

M9 ,M10

43. 8

0. 6

17. 6

0. 6

30

0. 6

18. 52

0. 6

M11

185. 2

0. 6

M12

267

0. 6

M13

86. 4

0. 6

M14

124

0. 6

M1A ,M2A

22. 9

0. 6

经 DC 仿真分析 ,SR 较小 ,因为 SR = I

CP ,所以

可以改变电流 I 和 Cp 来满足要求 。首先增加流过

M9 ,M10 的电流为原来的二倍 ,可以通过改变 M9 ,

M10 的管子宽长比为原来的二倍来实现 , 相应的

M1A ,M2A 两管子的宽长比也增大为原来的二倍 。

经过调整 ,补偿电容上的电压有所增加 ,通过调整

M3 ,M4 ,M3A ,M4A 来降低该电压值 ,使电压值保持

在 1V 左右 ,这样才可以使管子 M12 工作在比较稳

—8—

�

Π

Π

Π

定的饱和状态 。

另外 ,还要调节输出端 out 的电压值 ,要使该处

电压值在 2. 5V 左右 ,可以通过改变 M12 的宽长比

来实现 。表 3 为调整后 MOS 管参数 。

管子名称

M1 ,M2

M3 ,M4

M5 ,M6 ,M7 ,M8

M9 ,M10

M11

表 3 调整后 MOS 管参数

管子宽 (单位μm)

30

管子长 (单位μm)

2 Hspice 仿真测试

0. 6

14

0. 6

30

0. 6

33

0. 6

500

1. 2

运放的输出端接 2pF 的负载电容 ,在电源电压

为 5V ,共模输入电压为 2. 5V ,在运放输入端接差分

交流信号 1V ,两输入端的输入交流信号相位相反的

条件下做交流小信号分析 ,电路图连接如图 2 所示 。

M12

195

1. 2

M13

60

0. 6

M14 M1A ,M2A M3A ,M4A

20

0. 6

60

1. 2

90

0. 6

图 2 低频小信号特性仿真电路连接图

小信号低频电压增益 :小信号低频电压增益为

95. 7dB ,如图 3 所示 ,满足设计指标 ( > 80dB) 。

图 4 低频小信号单位带宽分析图

图 5 相位裕度分析图

图 3 低频小信号电压增益分析图

单位增益带宽 :单位增益带宽为 223MHz ,如图 4

所示 ,满足设计指标 ( > 100MHz) 。

相位裕度 :相位裕度为 180°- 129°= 51°,如图 5

所示 ,满足设计指标 ( > 50°) 。

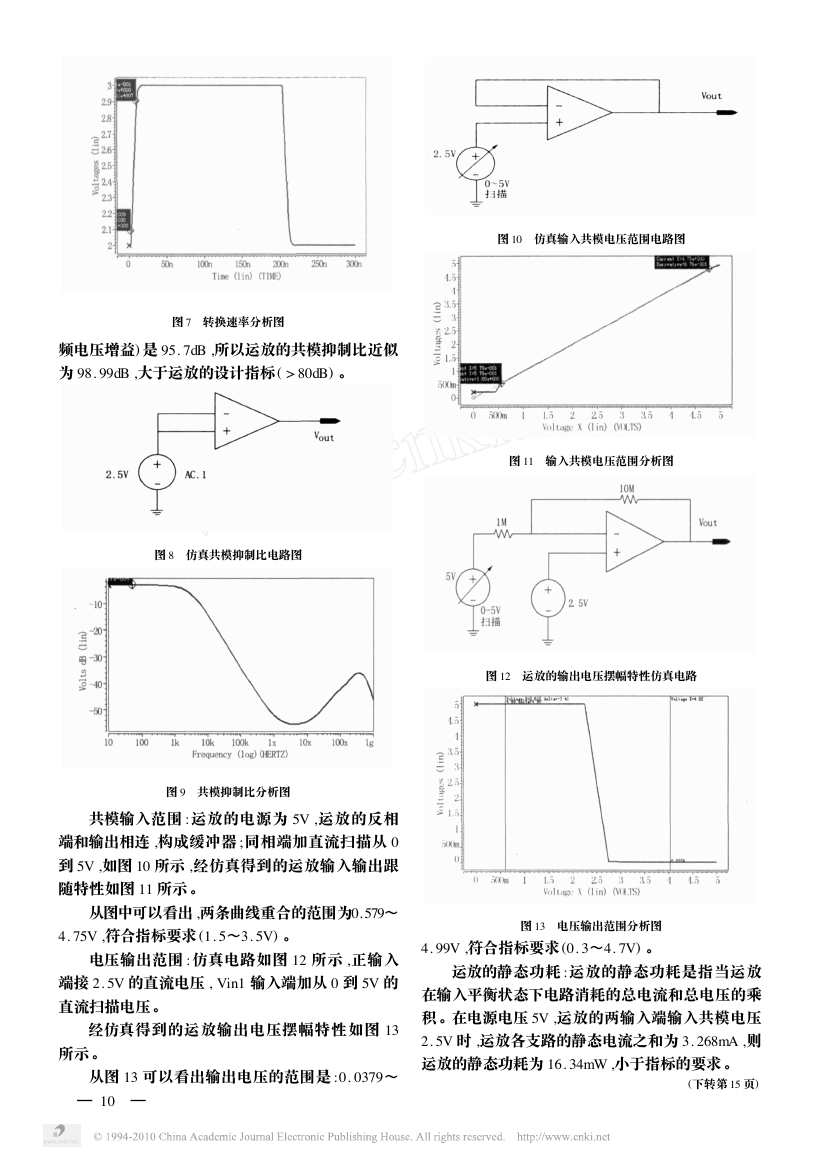

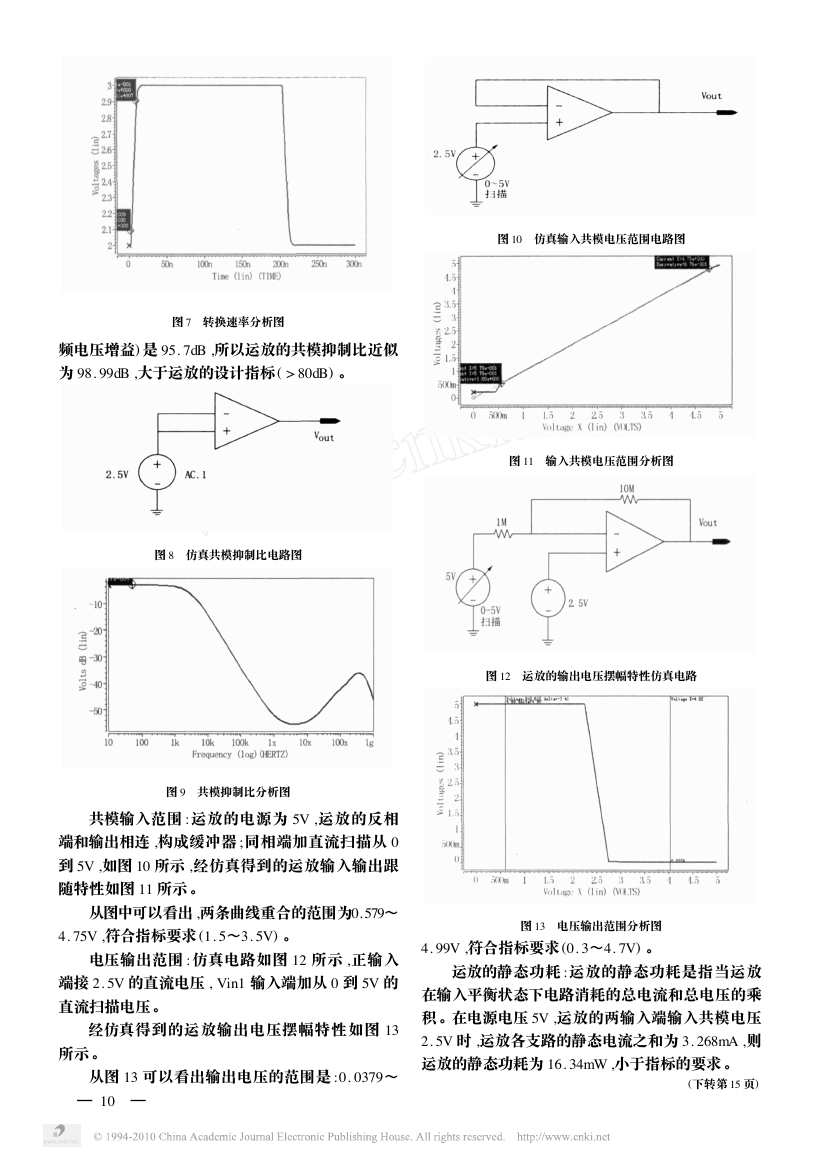

转换速率 :运放的同相输入端输入 2V 到 3V 的

阶跃信号 ,电路如图 6 所示 。运放瞬态分析得到的

输出波形如图 7 所示 ,从仿真波形得到 :在输出上升

曲线的 10 %和 90 %处 ,其电压分别为 2. 9V 和 2. 1V ;

时间 分 别 为 10. 7μs 和 3. 32μs。运 放 的 转 换 速 率

μs ,

SR = (2. 9V - 2. 1V)

满足设计指标 (100V

(10. 7μs - 3. 32μs) = 108. 4V

μs) 。

图 6 转换速率电路图

共模抑制比 :在运放的开环状态下 ,在运放的同

相和反相输入端同时加入一个幅度为 1V 的交流小

信号源 ,电路如图 8 所示 。从图 9 的仿真结果可知 ,

运放的低频共模电压增益为 - 3. 29dB 。因为运放的

共模抑制比 (dB 为单位) 等于其差模电压增益 ( dB)

减去共模电压增益 (dB) ,差模电压增益 (即小信号低

—9—

�

图 7 转换速率分析图

频电压增益) 是 95. 7dB ,所以运放的共模抑制比近似

为 98. 99dB ,大于运放的设计指标 ( > 80dB) 。

图 8 仿真共模抑制比电路图

图 10 仿真输入共模电压范围电路图

图 11 输入共模电压范围分析图

图 12 运放的输出电压摆幅特性仿真电路

图 9 共模抑制比分析图

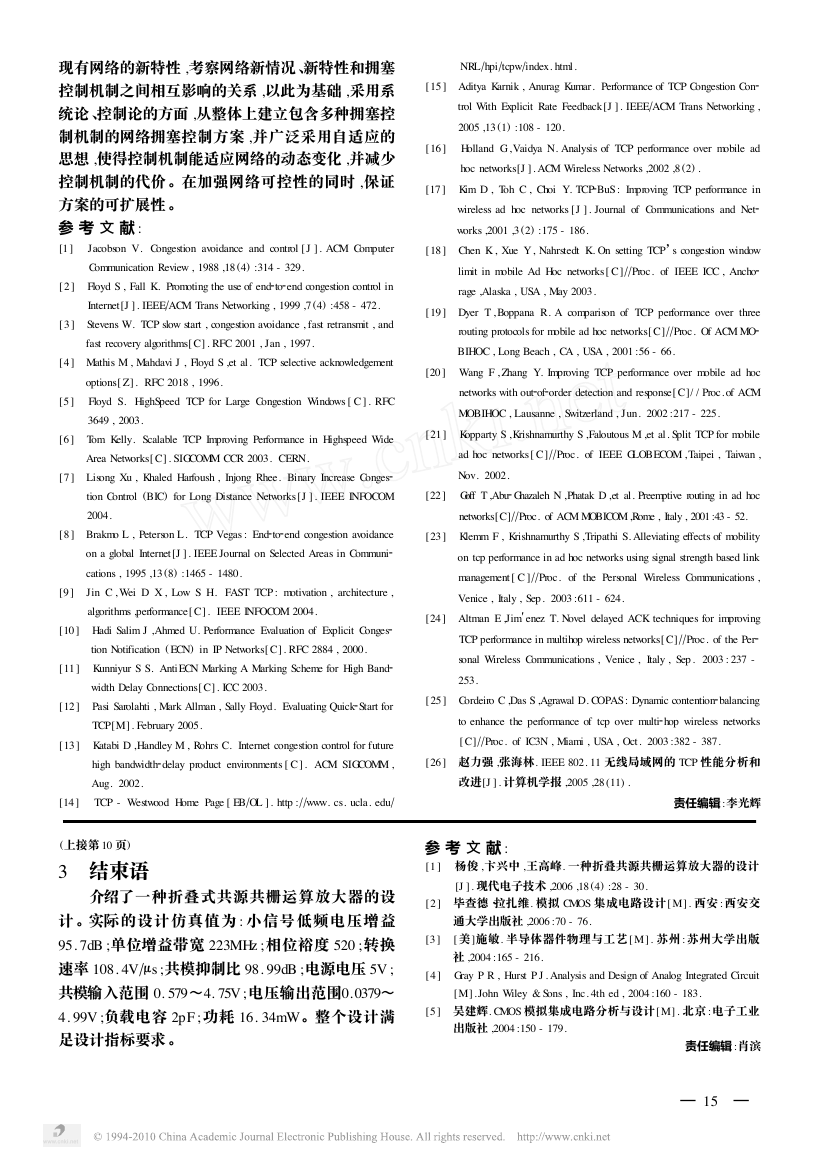

共模输入范围 :运放的电源为 5V ,运放的反相

端和输出相连 ,构成缓冲器 ;同相端加直流扫描从 0

到 5V ,如图 10 所示 ,经仿真得到的运放输入输出跟

随特性如图 11 所示 。

从图中可以看出 ,两条曲线重合的范围为0. 579~

4. 75V ,符合指标要求 (1. 5~3. 5V) 。

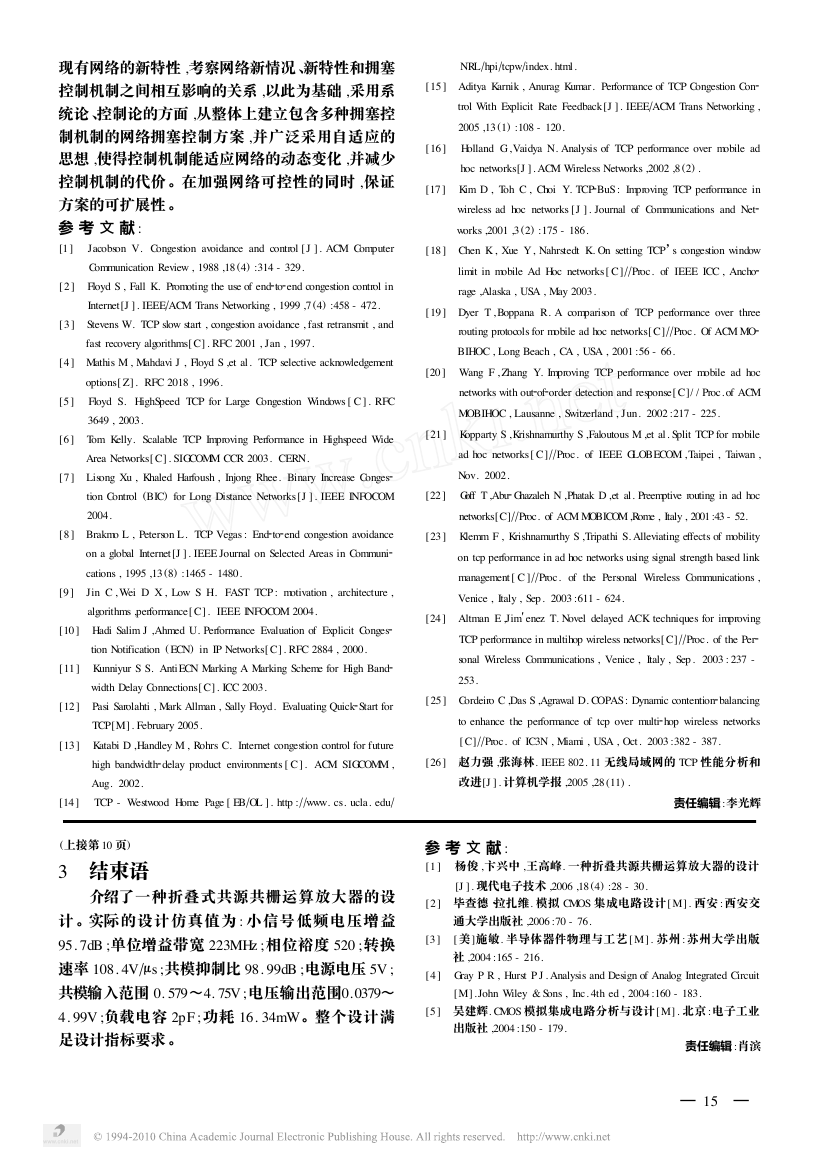

电压输出范围 :仿真电路如图 12 所示 ,正输入

端接 2. 5V 的直流电压 , Vin1 输入端加从 0 到 5V 的

直流扫描电压 。

经仿真得到的运放输出电压摆幅特性如图 13

所示 。

从图 13 可以看出输出电压的范围是 :0. 0379~

—01—

图 13 电压输出范围分析图

4. 99V ,符合指标要求 (0. 3~4. 7V) 。

运放的静态功耗 :运放的静态功耗是指当运放

在输入平衡状态下电路消耗的总电流和总电压的乘

积 。在电源电压 5V ,运放的两输入端输入共模电压

2. 5V 时 ,运放各支路的静态电流之和为 3. 268mA ,则

运放的静态功耗为 16. 34mW ,小于指标的要求 。

(下转第 15 页)

�

2

Π

ΠΠ

Π

现有网络的新特性 ,考察网络新情况 、新特性和拥塞

控制机制之间相互影响的关系 ,以此为基础 ,采用系

统论 、控制论的方面 ,从整体上建立包含多种拥塞控

制机制的网络拥塞控制方案 ,并广泛采用自适应的

思想 ,使得控制机制能适应网络的动态变化 ,并减少

控制机制的代价 。在加强网络可控性的同时 ,保证

方案的可扩展性 。

参 考 文 献 :

[1 ] Jacobson V. Congestion avoidance and control [ J ] . ACM Computer

Communication Review , 1988 ,18 (4) :314 - 329.

[ 2 ] Floyd S , Fall K. Promoting the use of end

to

end congestion control in

Internet[J ] . IEEE

ACM Trans Networking , 1999 ,7 (4) :458 - 472.

[ 3 ] Stevens W. TCP slow start , congestion avoidance , fast retransmit , and

fast recovery algorithms[ C] . RFC 2001 , Jan , 1997.

[4 ] Mathis M , Mahdavi J , Floyd S ,et al. TCP selective acknowledgement

options[ Z] . RFC 2018 , 1996.

[5 ] Floyd S. HighSpeed TCP for Large Congestion Windows [ C ] . RFC

3649 , 2003.

[6 ] Tom Kelly. Scalable TCP Improving Performance in Highspeed Wide

Area Networks[ C] . SIGCOMM CCR 2003. CERN.

NRL

hpi

tcpw

index. html.

[ 15 ] Aditya Karnik , Anurag Kumar. Performance of TCP Congestion Con

trol With Explicit Rate Feedback[J ] . IEEE

ACM Trans Networking ,

2005 ,13 (1) :108 - 120.

[16 ] Holland G,Vaidya N. Analysis of TCP performance over mobile ad

hoc networks[J ] . ACM Wireless Networks ,2002 ,8 (2) .

[17 ] Kim D , Toh C , Choi Y. TCP

BuS : Improving TCP performance in

wireless ad hoc networks [J ] . Journal of Communications and Net

works ,2001 ,3 (2) :175 - 186.

[18 ] Chen K, Xue Y, Nahrstedt K. On setting TCP’s congestion window

limit in mobile Ad Hoc networks[ C]

Proc. of IEEE ICC , Ancho

rage ,Alaska , USA , May 2003.

[19 ] Dyer T , Boppana R. A comparison of TCP performance over three

Proc. Of ACM MO

routing protocols for mobile ad hoc networks[ C]

BIHOC , Long Beach , CA , USA , 2001 :56 - 66.

[20 ] Wang F , Zhang Y. Improving TCP performance over mobile ad hoc

networks with out

of

order detection and response[ C]/ / Proc. of ACM

MOBIHOC , Lausanne , Switzerland , Jun. 2002 :217 - 225.

[ 21 ] Kopparty S , Krishnamurthy S ,Faloutous M ,et al. Split TCP for mobile

ad hoc networks[ C]

Proc. of IEEE GLOBECOM , Taipei , Taiwan ,

[7 ] Lisong Xu , Khaled Harfoush , Injong Rhee. Binary Increase Conges

tion Control (BIC) for Long Distance Networks[J ] . IEEE INFOCOM

Nov. 2002.

[22 ] Goff T ,Abu

Ghazaleh N ,Phatak D ,et al. Preemptive routing in ad hoc

2004.

networks[C]

Proc. of ACM MOBICOM ,Rome , Italy , 2001 :43 - 52.

[8 ] Brakmo L , Peterson L. TCP Vegas : End

to

end congestion avoidance

[23 ] Klemm F , Krishnamurthy S ,Tripathi S. Alleviating effects of mobility

on a global Internet[J ] . IEEE Journal on Selected Areas in Communi

cations , 1995 ,13 (8) :1465 - 1480.

[9 ] Jin C , Wei D X , Low S H. FAST TCP : motivation , architecture ,

algorithms ,performance[ C] . IEEE INFOCOM 2004.

[10 ] Hadi Salim J ,Ahmed U. Performance Evaluation of Explicit Conges

tion Notification ( ECN) in IP Networks[ C] . RFC 2884 , 2000.

[11 ] Kunniyur S S. AntiECN Marking A Marking Scheme for High Band

width Delay Connections[ C] . ICC 2003.

[12 ] Pasi Sarolahti , Mark Allman , Sally Floyd. Evaluating Quick

Start for

TCP[M] . February 2005.

[13 ] Katabi D ,Handley M , Rohrs C. Internet congestion control for future

delay product environments [ C ] . ACM SIGCOMM ,

high bandwidth

Aug. 2002.

on tcp performance in ad hoc networks using signal strength based link

management [ C ]

Proc. of the Personal Wireless Communications ,

Venice , Italy , Sep . 2003 :611 - 624.

[24 ] Altman E ,Jim′enez T. Novel delayed ACK techniques for improving

TCP performance in multihop wireless networks[ C]

Proc. of the Per

sonal Wireless Communications , Venice , Italy , Sep . 2003 : 237 -

253.

[ 25 ] Cordeiro C ,Das S ,Agrawal D. COPAS : Dynamic contention

balancing

to enhance the performance of tcp over multi

hop wireless networks

[ C]

Proc. of IC3N , Miami , USA , Oct. 2003 :382 - 387.

[26 ] 赵力强 ,张海林. IEEE 802. 11 无线局域网的 TCP 性能分析和

改进[J ] . 计算机学报 ,2005 ,28 (11) .

[14 ] TCP - Westwood Home Page [ EB

OL ] . http :

www. cs. ucla. edu

责任编辑 :李光辉

(上接第 10 页)

3 结束语

介绍了一种折叠式共源共栅运算放大器的设

计 。实际的设计仿真值为 : 小信号低频电压增益

95. 7dB ;单位增益带宽 223MHz ;相位裕度 520 ;转换

μs ;共模抑制比 98. 99dB ;电源电压 5V ;

速率 108. 4V

共模输入范围 0. 579~4. 75V ;电压输出范围0. 0379~

4. 99V ;负载电容 2pF ;功耗 16. 34mW。整个设计满

足设计指标要求 。

参 考 文 献 :

[1 ] 杨俊 ,卞兴中 ,王高峰. 一种折叠共源共栅运算放大器的设计

[J ] . 现代电子技术 ,2006 ,18 (4) :28 - 30.

[2 ] 毕查德·拉扎维. 模拟 CMOS 集成电路设计 [ M] . 西安 :西安交

通大学出版社 ,2006 :70 - 76.

[3 ] [ 美 ]施敏. 半导体器件物理与工艺 [ M] . 苏州 : 苏州大学出版

社 ,2004 :165 - 216.

[4 ] Gray P R , Hurst P J . Analysis and Design of Analog Integrated Circuit

[M] .John Wiley & Sons , Inc. 4th ed , 2004 :160 - 183.

[5 ] 吴建辉. CMOS 模拟集成电路分析与设计[ M] . 北京 :电子工业

出版社 ,2004 :150 - 179.

责任编辑 :肖滨

—51—

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc