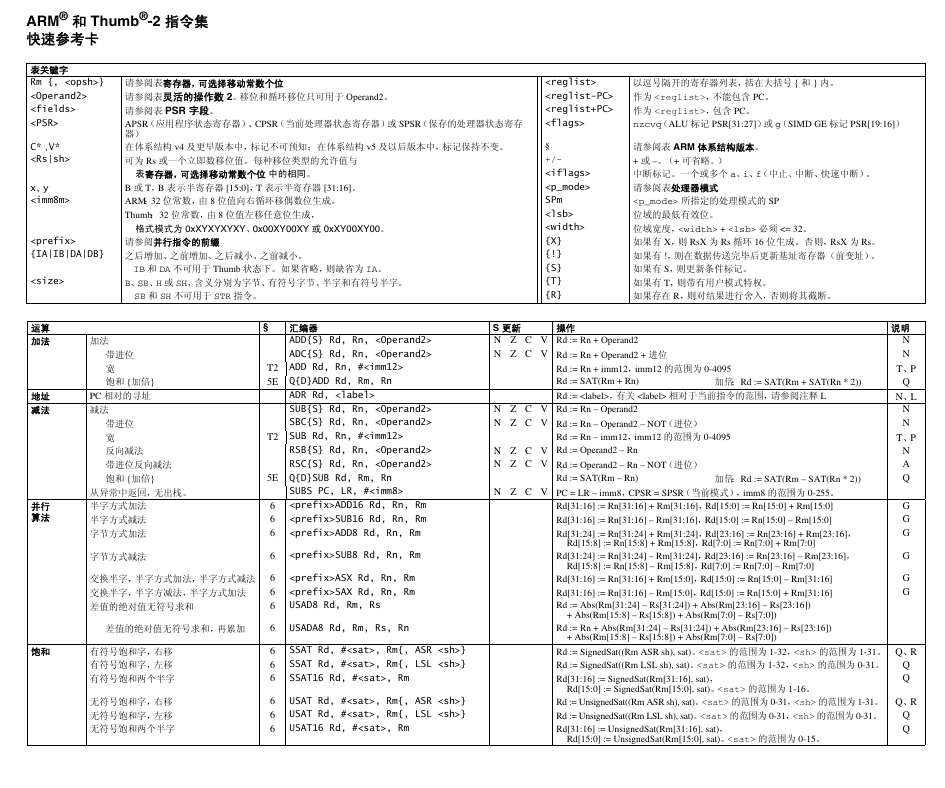

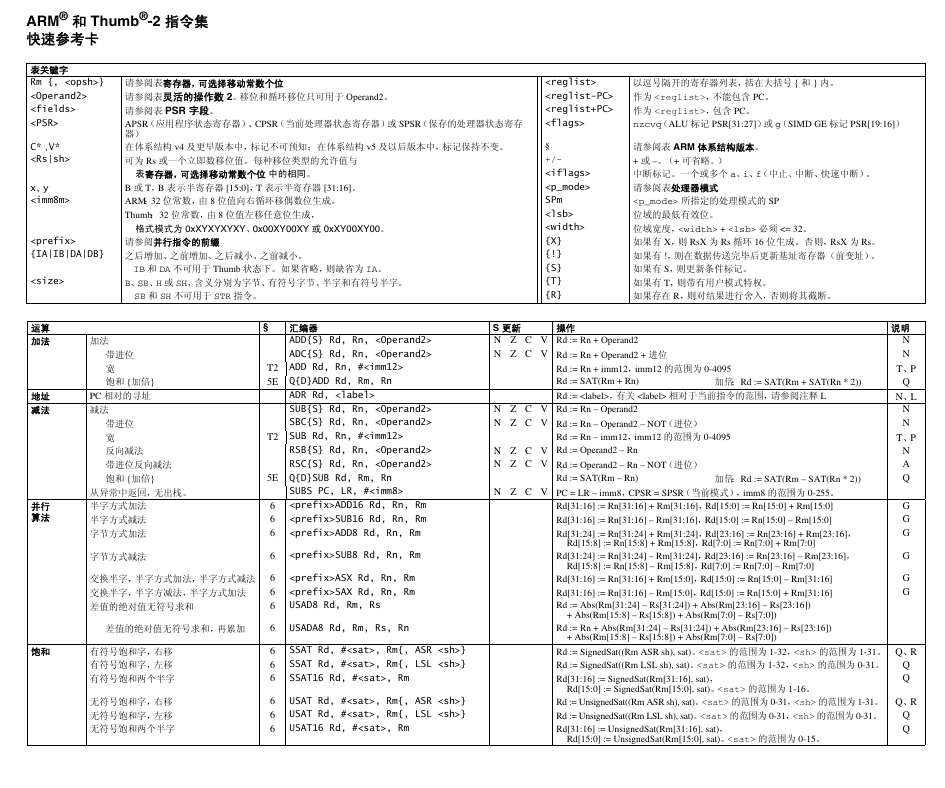

ARM® 和 Thumb®-2 指令集

快速参考卡

表关键字

Rm {,

}

C*,V*

x、y

请参阅表寄存器,可选择移动常数个位

请参阅表灵活的操作数 2。移位和循环移位只可用于 Operand2。

请参阅表 PSR 字段。

APSR(应用程序状态寄存器)、CPSR(当前处理器状态寄存器)或 SPSR(保存的处理器状态寄存

器)

在体系结构 v4 及更早版本中,标记不可预知;在体系结构 v5 及以后版本中,标记保持不变。

可为 Rs 或一个立即数移位值。 每种移位类型的允许值与

表寄存器,可选择移动常数个位 中的相同。

B 或 T,B 表示半寄存器 [15:0],T 表示半寄存器 [31:16]。

ARM:32 位常数,由 8 位值向右循环移偶数位生成。

Thumb: 32 位常数,由 8 位值左移任意位生成,

格式模式为 0xXYXYXYXY、0x00XY00XY 或 0xXY00XY00。

{IA|IB|DA|DB}

请参阅并行指令的前缀

之后增加、之前增加、之后减小、之前减小。

IB 和 DA 不可用于 Thumb 状态下。 如果省略,则缺省为 IA。

B、SB、H 或 SH,含义分别为字节、有符号字节、半字和有符号半字。

SB 和 SH 不可用于 STR 指令。

以逗号隔开的寄存器列表,括在大括号 { 和 } 内。

作为 ,不能包含 PC。

作为 ,包含 PC。

nzcvq(ALU 标记 PSR[31:27])或 g(SIMD GE 标记 PSR[19:16])

§

+/-

SPm

{X}

{!}

{S}

{T}

{R}

请参阅表 ARM 体系结构版本。

+ 或 –。 (+ 可省略。)

中断标记。 一个或多个 a、i、f(中止、中断、快速中断)。

请参阅表处理器模式

所指定的处理模式的 SP

位域的最低有效位。

位域宽度, + 必须 <= 32。

如果有 X,则 RsX 为 Rs 循环 16 位生成。 否则,RsX 为 Rs。

如果有 !,则在数据传送完毕后更新基址寄存器 (前变址)。

如果有 S,则更新条件标记。

如果有 T,则带有用户模式特权。

如果存在 R,则对结果进行舍入,否则将其截断。

运算

加法

地址

减法

并行

算法

饱和

加法

带进位

宽

饱和 {加倍}

PC 相对的寻址

减法

带进位

宽

反向减法

带进位反向减法

饱和 {加倍}

从异常中返回,无出栈。

半字方式加法

半字方式减法

字节方式加法

字节方式减法

§

汇编器

ADD{S} Rd, Rn,

ADC{S} Rd, Rn,

T2 ADD Rd, Rn, #

5E Q{D}ADD Rd, Rm, Rn

ADR Rd, §

汇编器

MUL{S} Rd, Rm, Rs

MLA{S} Rd, Rm, Rs, Rn

T2 MLS Rd, Rm, Rs, Rn

S 更新

N Z C*

N Z C*

操作

Rd := (Rm * Rs)[31:0]

Rd := (Rn + (Rm * Rs))[31:0]

Rd := (Rn – (Rm * Rs))[31:0]

UMULL{S} RdLo, RdHi, Rm, Rs

UMLAL{S} RdLo, RdHi, Rm, Rs

UMAAL RdLo, RdHi, Rm, Rs

SMULL{S} RdLo, RdHi, Rm, Rs

SMLAL{S} RdLo, RdHi, Rm, Rs

N Z C* V* RdHi,RdLo := unsigned(Rm * Rs)

N Z C* V* RdHi,RdLo := unsigned(RdHi,RdLo + Rm * Rs)

RdHi,RdLo := unsigned(RdHi + RdLo + Rm * Rs)

N Z C* V* RdHi,RdLo := signed(Rm * Rs)

N Z C* V* RdHi,RdLo := signed(RdHi,RdLo + Rm * Rs)

无符号长乘法,两次加法

6

(如果 Rs 为 Rd,则 S 可用于 Thumb-2 中)

说明

N、S

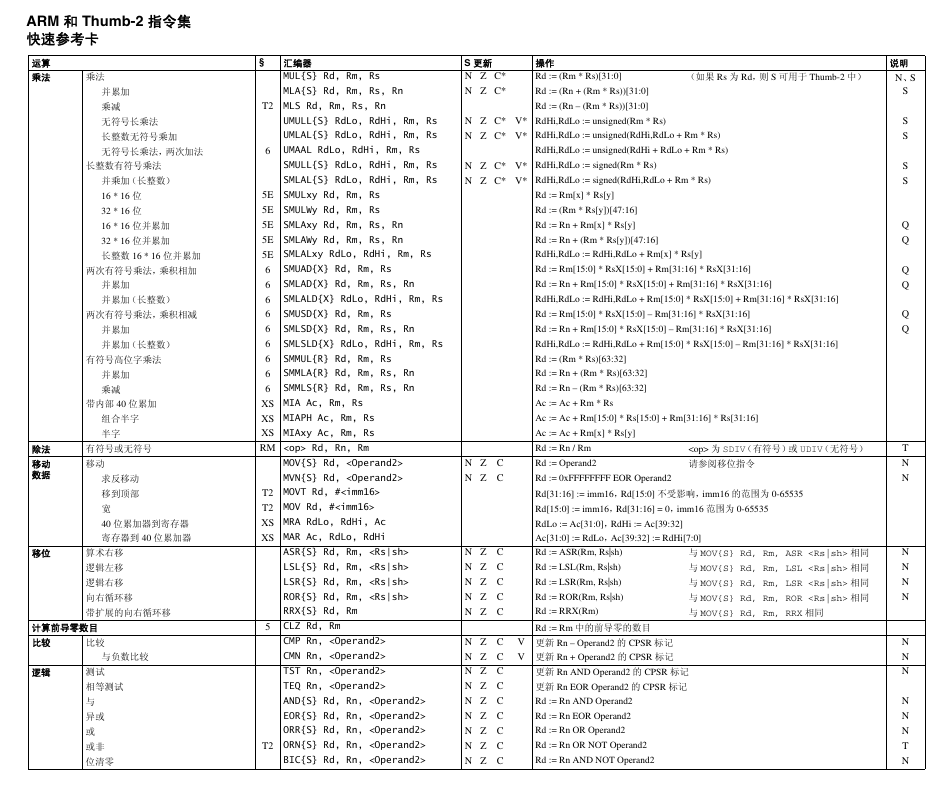

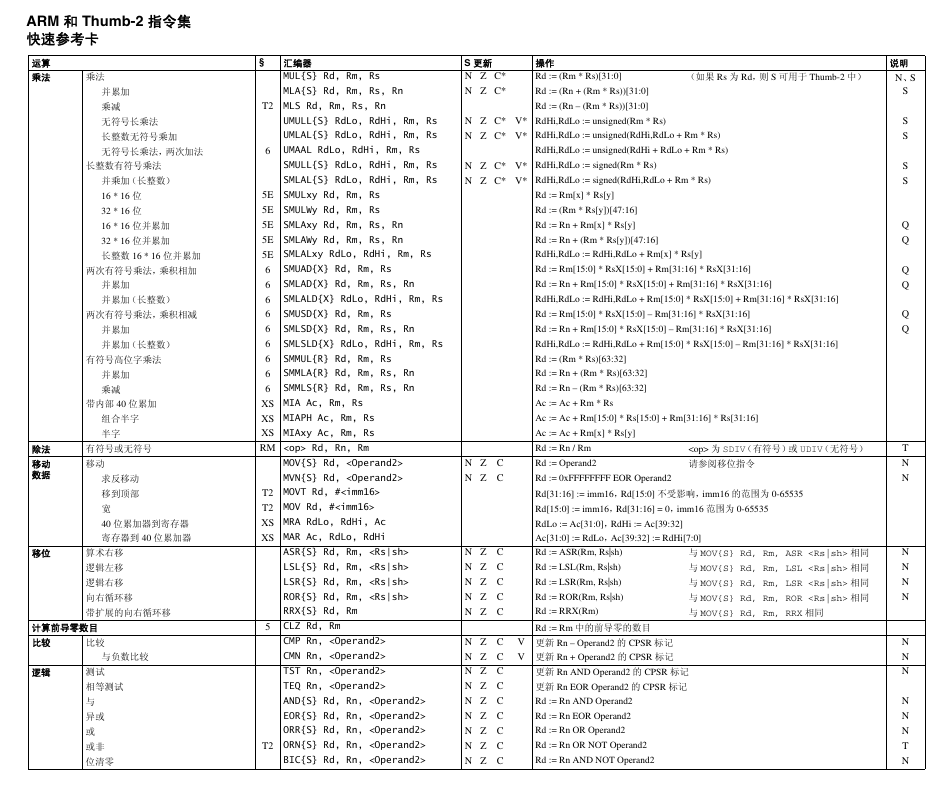

ARM 和 Thumb-2 指令集

快速参考卡

运算

乘法

乘法

并累加

乘减

无符号长乘法

长整数无符号乘加

长整数有符号乘法

并乘加(长整数)

16 * 16 位

32 * 16 位

16 * 16 位并累加

32 * 16 位并累加

长整数 16 * 16 位并累加

两次有符号乘法,乘积相加

并累加

并累加(长整数)

两次有符号乘法,乘积相减

并累加

并累加(长整数)

有符号高位字乘法

并累加

乘减

带内部 40 位累加

组合半字

半字

有符号或无符号

移动

求反移动

移到顶部

宽

40 位累加器到寄存器

寄存器到 40 位累加器

算术右移

逻辑左移

逻辑右移

向右循环移

除法

移动

数据

移位

带扩展的向右循环移

计算前导零数目

比较

比较

与负数比较

逻辑

测试

相等测试

与

异或

或

或非

位清零

5E SMULxy Rd, Rm, Rs

5E SMULWy Rd, Rm, Rs

5E SMLAxy Rd, Rm, Rs, Rn

5E SMLAWy Rd, Rm, Rs, Rn

5E SMLALxy RdLo, RdHi, Rm, Rs

6

6

6

6

6

6

6

6

6

XS MIA Ac, Rm, Rs

XS MIAPH Ac, Rm, Rs

XS MIAxy Ac, Rm, Rs

RM Rd, Rn, Rm

SMUAD{X} Rd, Rm, Rs

SMLAD{X} Rd, Rm, Rs, Rn

SMLALD{X} RdLo, RdHi, Rm, Rs

SMUSD{X} Rd, Rm, Rs

SMLSD{X} Rd, Rm, Rs, Rn

SMLSLD{X} RdLo, RdHi, Rm, Rs

SMMUL{R} Rd, Rm, Rs

SMMLA{R} Rd, Rm, Rs, Rn

SMMLS{R} Rd, Rm, Rs, Rn

MOV{S} Rd,

MVN{S} Rd,

N Z C

N Z C

T2 MOVT Rd, #

T2 MOV Rd, #

XS MRA RdLo, RdHi, Ac

XS MAR Ac, RdLo, RdHi

5

ASR{S} Rd, Rm,

LSL{S} Rd, Rm,

LSR{S} Rd, Rm,

ROR{S} Rd, Rm,

RRX{S} Rd, Rm

CLZ Rd, Rm

CMP Rn,

CMN Rn,

TST Rn,

TEQ Rn,

AND{S} Rd, Rn,

EOR{S} Rd, Rn,

ORR{S} Rd, Rn,

T2 ORN{S} Rd, Rn,

BIC{S} Rd, Rn,

Rd := Rm[x] * Rs[y]

Rd := (Rm * Rs[y])[47:16]

Rd := Rn + Rm[x] * Rs[y]

Rd := Rn + (Rm * Rs[y])[47:16]

RdHi,RdLo := RdHi,RdLo + Rm[x] * Rs[y]

Rd := Rm[15:0] * RsX[15:0] + Rm[31:16] * RsX[31:16]

Rd := Rn + Rm[15:0] * RsX[15:0] + Rm[31:16] * RsX[31:16]

RdHi,RdLo := RdHi,RdLo + Rm[15:0] * RsX[15:0] + Rm[31:16] * RsX[31:16]

Rd := Rm[15:0] * RsX[15:0] – Rm[31:16] * RsX[31:16]

Rd := Rn + Rm[15:0] * RsX[15:0] – Rm[31:16] * RsX[31:16]

RdHi,RdLo := RdHi,RdLo + Rm[15:0] * RsX[15:0] – Rm[31:16] * RsX[31:16]

Rd := (Rm * Rs)[63:32]

Rd := Rn + (Rm * Rs)[63:32]

Rd := Rn – (Rm * Rs)[63:32]

Ac := Ac + Rm * Rs

Ac := Ac + Rm[15:0] * Rs[15:0] + Rm[31:16] * Rs[31:16]

Ac := Ac + Rm[x] * Rs[y]

Rd := Rn / Rm

Rd := Operand2

Rd := 0xFFFFFFFF EOR Operand2

为 SDIV(有符号)或 UDIV(无符号)

请参阅移位指令

Rd[31:16] := imm16,Rd[15:0] 不受影响,imm16 的范围为 0-65535

Rd[15:0] := imm16,Rd[31:16] = 0,imm16 范围为 0-65535

RdLo := Ac[31:0],RdHi := Ac[39:32]

Ac[31:0] := RdLo,Ac[39:32] := RdHi[7:0]

Rd := ASR(Rm, Rs|sh)

Rd := LSL(Rm, Rs|sh)

Rd := LSR(Rm, Rs|sh)

Rd := ROR(Rm, Rs|sh)

Rd := RRX(Rm)

与 MOV{S} Rd, Rm, ASR 相同

与 MOV{S} Rd, Rm, LSL 相同

与 MOV{S} Rd, Rm, LSR 相同

与 MOV{S} Rd, Rm, ROR 相同

与 MOV{S} Rd, Rm, RRX 相同

N Z C

N Z C

N Z C

N Z C

N Z C

Rd := Rm 中的前导零的数目

N Z C V 更新 Rn – Operand2 的 CPSR 标记

N Z C V 更新 Rn + Operand2 的 CPSR 标记

N Z C

N Z C

N Z C

N Z C

N Z C

N Z C

N Z C

更新 Rn AND Operand2 的 CPSR 标记

更新 Rn EOR Operand2 的 CPSR 标记

Rd := Rn AND Operand2

Rd := Rn EOR Operand2

Rd := Rn OR Operand2

Rd := Rn OR NOT Operand2

Rd := Rn AND NOT Operand2

S

S

S

S

S

Q

Q

Q

Q

Q

Q

T

N

N

N

N

N

N

N

N

N

N

N

N

T

N

�

ARM 和 Thumb-2 指令集

快速参考卡

运算

位域

组合

有符号

扩展

无符号

扩展

有符号

扩展,

带加法

无符号

扩展,

带加法

反转

位域清零

位域插入

有符号位域提取

无符号位域提取

组合:低半字 + 高半字

组合:高半字 + 低半字

半字到字

两个字节到半字

字节到字

半字到字

两个字节到半字

字节到字

半字到字,加法

两个字节到半字,加法

字节到字,加法

半字到字,加法

两个字节到半字,加法

字节到字,加法

字中的位

字中的字节

两个半字中的字节

低半字中的字节,符号扩展

选择

选择字节

条件判断

条件判断

跳转

跳转

带链接的跳转

跳转并交换

带链接和交换 (1)

§

T2

T2

T2

T2

6

6

6

6

6

6

6

6

6

6

6

6

6

6

T2

6

6

6

6

T2

4T

5T

汇编器

BFC Rd, #

, #

BFI Rd, Rn, #, #

SBFX Rd, Rn, #, #

UBFX Rd, Rn, #, #

PKHBT Rd, Rn, Rm{, LSL #}

PKHTB Rd, Rn, Rm{, ASR #}

SXTH Rd, Rm{, ROR #}

SXTB16 Rd, Rm{, ROR #}

SXTB Rd, Rm{, ROR #}

UXTH Rd, Rm{, ROR #}

UXTB16 Rd, Rm{, ROR #}

UXTB Rd, Rm{, ROR #}

SXTAH Rd, Rn, Rm{, ROR #}

SXTAB16 Rd, Rn, Rm{, ROR #}

SXTAB Rd, Rn, Rm{, ROR #}

UXTAH Rd, Rn, Rm{, ROR #}

UXTAB16 Rd, Rn, Rm{, ROR #}

UXTAB Rd, Rn, Rm{, ROR #}

RBIT Rd, Rm

REV Rd, Rm

REV16 Rd, Rm

REVSH Rd, Rm

SEL Rd, Rn, Rm

IT{pattern} {cond}

B

BL

BX Rm

BLX

带链接和交换 (2)

跳转并更改为 Jazelle 状态

5

5J

比较,如果为(非)零,则跳转 T2

BLX Rm

BXJ Rm

CB{N}Z Rn,

操作

Rd[(width+lsb–1):lsb] := 0,Rd 的其他位不受影响

Rd[(width+lsb–1):lsb] := Rn[(width-1):0],Rd 的其他位不受影响

Rd[(width–1):0] = Rn[(width+lsb–1):lsb],Rd[31:width] = 复制 ( Rn[width+lsb–1] )

Rd[(width–1):0] = Rn[(width+lsb–1):lsb],Rd[31:width] = 复制 ( 0 )

Rd[15:0] := Rn[15:0],Rd[31:16] := (Rm LSL sh)[31:16]。sh 的范围为 0-31。

Rd[31:16] := Rn[31:16],Rd[15:0] := (Rm ASR sh)[15:0]。sh 的范围为 1-32。

Rd[31:0] := SignExtend((Rm ROR (8 * sh))[15:0])。sh 的范围为 0-3。

Rd[31:16] := SignExtend((Rm ROR (8 * sh))[23:16]),

Rd[15:0] := SignExtend((Rm ROR (8 * sh))[7:0])。sh 的范围为 0-3。

Rd[31:0] := SignExtend((Rm ROR (8 * sh))[7:0])。sh 的范围为 0-3。

Rd[31:0] := ZeroExtend((Rm ROR (8 * sh))[15:0])。sh 的范围为 0-3。

Rd[31:16] := ZeroExtend((Rm ROR (8 * sh))[23:16]),

Rd[15:0] := ZeroExtend((Rm ROR (8 * sh))[7:0])。sh 的范围为 0-3。

Rd[31:0] := ZeroExtend((Rm ROR (8 * sh))[7:0])。sh 的范围为 0-3。

Rd[31:0] := Rn[31:0] + SignExtend((Rm ROR (8 * sh))[15:0])。sh 的范围为 0-3。

Rd[31:16] := Rn[31:16] + SignExtend((Rm ROR (8 * sh))[23:16]),

Rd[15:0] := Rn[15:0] + SignExtend((Rm ROR (8 * sh))[7:0])。sh 的范围为 0-3。

Rd[31:0] := Rn[31:0] + SignExtend((Rm ROR (8 * sh))[7:0])。sh 的范围为 0-3。

Rd[31:0] := Rn[31:0] + ZeroExtend((Rm ROR (8 * sh))[15:0])。sh 的范围为 0-3。

Rd[31:16] := Rn[31:16] + ZeroExtend((Rm ROR (8 * sh))[23:16]),

Rd[15:0] := Rn[15:0] + ZeroExtend((Rm ROR (8 * sh))[7:0])。sh 的范围为 0-3。

Rd[31:0] := Rn[31:0] + ZeroExtend((Rm ROR (8 * sh))[7:0])。sh 的范围为 0-3。

For (i = 0; i < 32; i++) : Rd[i] = Rm[31– i]

Rd[31:24] := Rm[7:0],Rd[23:16] := Rm[15:8],Rd[15:8] := Rm[23:16],Rd[7:0] := Rm[31:24]

Rd[15:8] := Rm[7:0],Rd[7:0] := Rm[15:8],Rd[31:24] := Rm[23:16],Rd[23:16] := Rm[31:24]

Rd[15:8] := Rm[7:0],Rd[7:0] := Rm[15:8],Rd[31:16] := Rm[7] * &FFFF

如果 GE[0] = 1,则 Rd[7:0] := Rn[7:0],否则 Rd[7:0] := Rm[7:0]

GE[1]、GE[2]、GE[3] 时位 [15:8]、[23:16]、[31:24] 的选择方法与 GE[0] 相似

依据不同的模式,最多由连续四个条件指令句组成。模式为一个字符串,最多三个字母。 所有字母都可为

IT 之后的第一条指令可有条件 cond。 如果相应的字母为 T,则后续指令可有条件 cond;如果相应的字母

T(然后)或 E(否则)。

为 E,则为该 cond 的反面情况。

有关可用条件代码的信息,请参阅表条件字段。

PC := label。label 为此指令 ±32MB(T2: ±16MB,T: –252 - +256B)

LR := 下一指令的地址,PC := label。label 为此指令 ±32MB (T2: ±16MB)。

PC := Rm。 如果 Rm[0] 为 1,目标为 Thumb;如果 Rm[0] 为 0,目标则为 ARM。

LR := 下一指令的地址,PC := label,更改指令集。

label 为此指令 ±32MB (T2: ±16MB)。

说明

N

N

N

N

N

N

N

T、U

N、B

N

C

LR := 下一指令的地址,PC := Rm[31:1]。 如果 Rm[0] 为 1,更改为 Thumb;如果 Rm[0] 为 0,则更改为 ARM。 N

如果可用,更改为 Jazelle

如果 Rn {== 或 !=} 0,则 PC := label。label 为(此指令 + 4-130)。

N、T、

U

移到 PSR

或从 PSR

移出

处理器

状态

更改

表跳转字节

表跳转半字

PSR 到寄存器

寄存器标记到 APSR 标记

立即数标记到 APSR 标记

寄存器到 PSR

立即数到 PSR

更改处理器状态

改变处理器模式

设置端标记

T2

T2

6

6

6

6

TBB [Rn, Rm]

TBH [Rn, Rm, LSL #1]

MRS Rd,

MSR APSR_, Rm

MSR APSR_, #

MSR _, Rm

MSR _, #

CPSID {, #}

CPSIE {, #}

CPS #

SETEND

PC = PC + ZeroExtend( Memory( Rn + Rm, 1) << 1)。 跳转范围为 4-512。 Rn 可为 PC。

PC = PC + ZeroExtend( Memory( Rn + Rm << 1, 2) << 1)。 跳转范围为 4-131072。 Rn 可为 PC。

Rd := PSR

APSR_ := Rm

APSR_ := immed_8r

PSR := Rm(仅选择字节)

PSR := immed_8r(仅选择字节)

禁用指定的中断,可选择更改模式。

启用指定的中断,可选择更改模式。

为加载和存储设置端标记。 可为 BE(大端)或 LE(小端)。

T、U

T、U

U、N

U、N

U

U、N

�ARM 和 Thumb-2 指令集

快速参考卡

加载和存储单个数据项

加载

或存储

字、字节

或半字

直接偏移量

加载或存储

双字

后变址,立即数

寄存器偏移量

后变址,寄存器

PC 相对的

直接偏移量

后变址,立即数

寄存器偏移量

后变址,寄存器

PC 相对的

§

5E

5E

5E

5E

5E

汇编器

{size}{T} Rd, [Rn {, #}]{!}

{size}{T} Rd, [Rn], #

{size} Rd, [Rn, +/-Rm {, }]{!}

{size}{T} Rd, [Rn], +/-Rm {, }

{size} Rd,

D Rd1, Rd2, [Rn {, #}]{!}

D Rd1, Rd2, [Rn], #

D Rd1, Rd2, [Rn, +/-Rm {, }]{!}

D Rd1, Rd2, [Rn], +/-Rm {, }

D Rd1, Rd2,

当 为 LDR 时执行的操作

Rd := [address, size]

Rd := [address, size]

Rd := [address, size]

Rd := [address, size]

Rd := [label, size]

Rd1 := [address],Rd2 := [address + 4]

Rd1 := [address],Rd2 := [address + 4]

Rd1 := [address],Rd2 := [address + 4]

Rd1 := [address],Rd2 := [address + 4]

Rd1 := [label],Rd2 := [label + 4]

当 为 STR 时执行的操作

[address, size] := Rd

[address, size] := Rd

[address, size] := Rd

[address, size] := Rd

不可用

[address] := Rd1,[address + 4] := Rd2

[address] := Rd1,[address + 4] := Rd2

[address] := Rd1,[address + 4] := Rd2

[address] := Rd1,[address + 4] := Rd2

不可用

说明

1、N

2

3、N

4

5、N

6、 9

6、 9

7、 9

7、 9

8、 9

预载数据或指令

§(PLD) §(PLI) §(PLDW) 汇编器

直接偏移量

寄存器偏移量

PC 相对的

5E

5E

5E

其他内存操作

加载多个

数据块加载

7

7

7

§

返回(并交换)

并恢复 CPSR

用户模式寄存器

信号运算

6

弹出

加载

独占

7MP

7MP

[Rn {, #}]

[Rn, +/-Rm {, }]

汇编器

LDM{IA|IB|DA|DB} Rn{!},

LDM{IA|IB|DA|DB} Rn{!},

LDM{IA|IB|DA|DB} Rn{!}, ^

LDM{IA|IB|DA|DB} Rn, ^

POP

LDREX Rd, [Rn]

半字或字节

6K LDREX{H|B} Rd, [Rn]

双字

6K LDREXD Rd1, Rd2, [Rn]

存储多个

推入或阻止数据存储

用户模式寄存器

推入

存储

独占

信号运算

半字或字节

STM{IA|IB|DA|DB} Rn{!},

STM{IA|IB|DA|DB} Rn{!}, ^

PUSH

STREX Rd, Rm, [Rn]

6

6K STREX{H|B} Rd, Rm, [Rn]

双字

6K STREXD Rd, Rm1, Rm2, [Rn]

当 为 PLI 时执行的操作

当 为 PLD 时执行的

操作

预载 [address, 32](数据) 预载 [address, 32](指令)

预载 [address, 32](数据) 预载 [address, 32](指令)

预载 [label, 32](数据)

预载 [label, 32](指令)

当 为 PLDW 时执行的操作

说明

预载以写入 [address, 32](数据)

预载以写入 [address, 32](数据)

操作

从 [Rn] 加载寄存器列表

加载寄存器,PC := [address][31:1](§ 5T: 当 [address][0] 为 1 时,更改为 Thumb)

加载寄存器,跳转(§ 5T: 并交换),CPSR := SPSR。 仅限异常模式。

从 [Rn] 加载用户模式寄存器列表。 仅限特权模式。

LDM SP!, 的规范格式

Rd := [Rn],将地址标记为独占访问。 如果不是共享地址,则为突出显示的标记设置。

Rd、Rn 不可为 PC。

Rd[15:0] := [Rn] 或 Rd[7:0] := [Rn],将地址标记为独占访问。

如果不是共享地址,则为突出显示的标记设置。 Rd、Rn 不可为 PC。

Rd1 := [Rn],Rd2 := [Rn+4],将地址标记为独占访问

如果不是共享地址,则为突出显示的标记设置。 Rd1、Rd2、Rn 不可为 PC。

将寄存器列表存储到 [Rn] 中

将用户模式寄存器列表存储到 [Rn] 中。 仅限特权模式。

STMDB SP!, 的规范格式

如果允许,则 [Rn] := Rm,清除独占标记,Rd := 0。否则 Rd := 1。Rd、Rm、Rn 不可为 PC。

如果允许,则 [Rn] := Rm[15:0] 或 [Rn] := Rm[7:0],清除独占标记,Rd := 0。否则 Rd := 1

Rd、Rm、Rn 不可为 PC。

如果允许,则 [Rn] := Rm1,[Rn+4] := Rm2,清除独占标记,Rd := 0。否则 Rd := 1

Rd、Rm1、Rm2、Rn 不可为 PC。

1、C

3、C

5、C

说明

N、I

I

I

I

N

9

N、I

I

N

10

C

清除独占

6K CLREX

清除局部处理器独占标记

说明: 加载、存储和预载操作的可用性和选项范围

注释

1

ARM 字、B、D

偏移量:–4095 到 +4095

ARM SB、H、SH

偏移量: –255 到 +255

ARM T、BT

不可用

2

3

4

5

6

7

8

9

10

偏移量: –4095 到 +4095

整个 {, } 范围

整个 {, } 范围

当前指令的 +/– 4092 范围内的标签

偏移量: –255 到 +255

{, } 不允许

当前指令的 +/– 252 范围内的标签

Rd1 编号为偶数,但不可为 r14,Rd2 ==

Rd1 + 1。

Rm1 编号为偶数,但不可为 r14,Rm2 ==

Rm1 + 1。

偏移量: –255 到 +255

{, } 不允许

{, } 不允许

不可用

-

-

-

-

偏移量: –4095 到 +4095

不可用

整个 {, } 范围

不可用

-

-

-

-

-

-

Rm1 != PC,Rm2 != PC

Thumb-2 字、B、SB、H、SH、D

偏移量: 如果回写,则为 –255 到 +255,否则,为 –255 到

+4095

偏移量: –255 到 +255

限制为 LSL #, 的范围为 0 到 3

不可用

当前指令的 +/– 4092 范围内的标签

偏移量: –1020 到 +1020,必须是 4 的倍数。

不可用

不可用

Rd1 != PC,Rd2 != PC

Thumb-2 T、BT、SBT、HT、SHT

偏移量: 0 到 +255,不允许回写

不可用

不可用

不可用

不可用

-

-

-

-

-

�

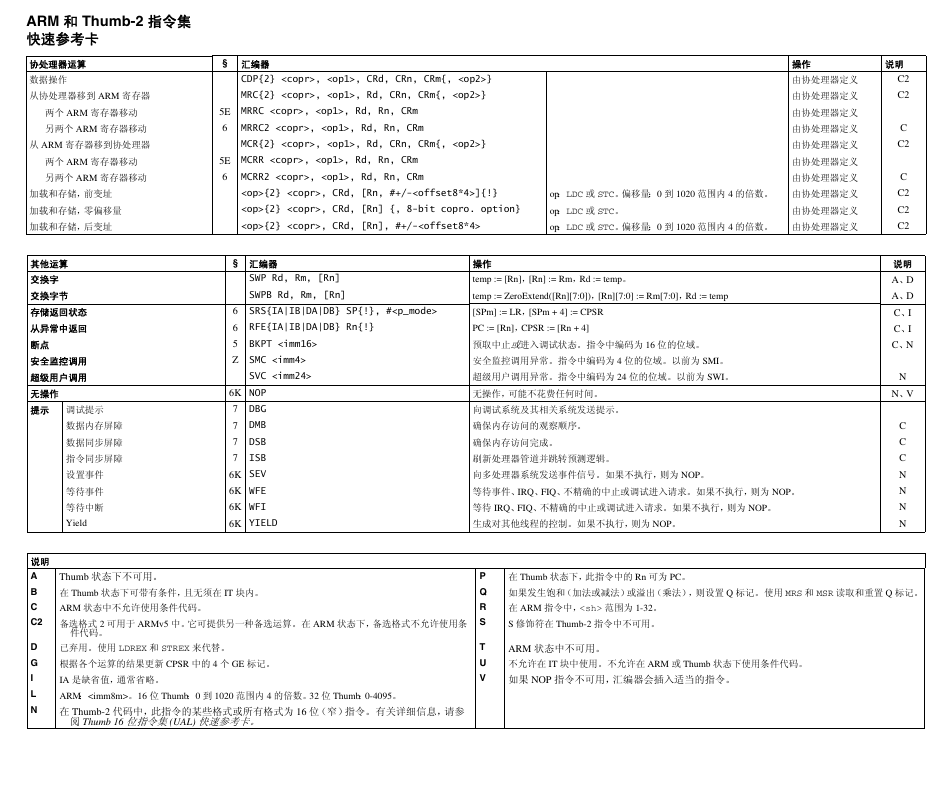

ARM 和 Thumb-2 指令集

快速参考卡

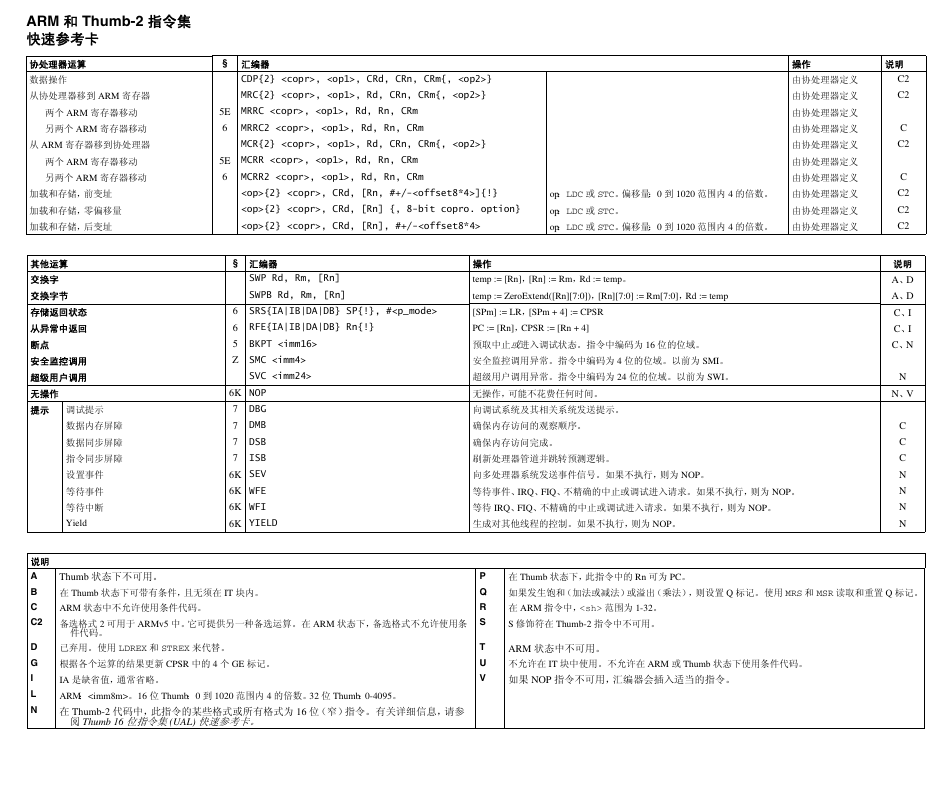

协处理器运算

数据操作

从协处理器移到 ARM 寄存器

两个 ARM 寄存器移动

另两个 ARM 寄存器移动

从 ARM 寄存器移到协处理器

两个 ARM 寄存器移动

另两个 ARM 寄存器移动

加载和存储,前变址

加载和存储,零偏移量

加载和存储,后变址

其他运算

交换字

交换字节

存储返回状态

从异常中返回

断点

安全监控调用

超级用户调用

无操作

提示 调试提示

数据内存屏障

数据同步屏障

指令同步屏障

设置事件

等待事件

等待中断

Yield

§ 汇编器

CDP{2}

, , CRd, CRn, CRm{, }

MRC{2} , , Rd, CRn, CRm{, }

5E MRRC , , Rd, Rn, CRm

MRRC2 , , Rd, Rn, CRm

6

MCR{2} , , Rd, CRn, CRm{, }

5E MCRR , , Rd, Rn, CRm

MCRR2 , , Rd, Rn, CRm

6

{2} , CRd, [Rn, #+/-]{!}

op: LDC 或 STC。偏移量: 0 到 1020 范围内 4 的倍数。 由协处理器定义

{2} , CRd, [Rn] {, 8-bit copro. option}

op: LDC 或 STC。

由协处理器定义

{2} , CRd, [Rn], #+/-

op: LDC 或 STC。偏移量: 0 到 1020 范围内 4 的倍数。 由协处理器定义

§ 汇编器

SWP Rd, Rm, [Rn]

SWPB Rd, Rm, [Rn]

6 SRS{IA|IB|DA|DB} SP{!}, #

6 RFE{IA|IB|DA|DB} Rn{!}

5 BKPT

Z SMC

SVC

操作

temp := [Rn],[Rn] := Rm,Rd := temp。

temp := ZeroExtend([Rn][7:0]),[Rn][7:0] := Rm[7:0],Rd := temp

[SPm] := LR,[SPm + 4] := CPSR

PC := [Rn],CPSR := [Rn + 4]

预取中止或进入调试状态。 指令中编码为 16 位的位域。

安全监控调用异常。 指令中编码为 4 位的位域。 以前为 SMI。

超级用户调用异常。 指令中编码为 24 位的位域。 以前为 SWI。

6K NOP

7 DBG

7 DMB

7 DSB

7 ISB

6K SEV

6K WFE

6K WFI

6K YIELD

无操作,可能不花费任何时间。

向调试系统及其相关系统发送提示。

确保内存访问的观察顺序。

确保内存访问完成。

刷新处理器管道并跳转预测逻辑。

向多处理器系统发送事件信号。 如果不执行,则为 NOP。

等待事件、IRQ、FIQ、不精确的中止或调试进入请求。 如果不执行,则为 NOP。

等待 IRQ、FIQ、不精确的中止或调试进入请求。 如果不执行,则为 NOP。

生成对其他线程的控制。 如果不执行,则为 NOP。

操作

说明

由协处理器定义

由协处理器定义

由协处理器定义

由协处理器定义

由协处理器定义

由协处理器定义

由协处理器定义

C2

C2

C

C2

C

C2

C2

C2

说明

A、D

A、D

C、I

C、I

C、N

N

N、V

C

C

C

N

N

N

N

说明

A

B

C

C2 备选格式 2 可用于 ARMv5 中。它可提供另一种备选运算。 在 ARM 状态下,备选格式不允许使用条

Thumb 状态下不可用。

在 Thumb 状态下可带有条件,且无须在 IT 块内。

ARM 状态中不允许使用条件代码。

件代码。

D

G

I

L

N

已弃用。 使用 LDREX 和 STREX 来代替。

根据各个运算的结果更新 CPSR 中的 4 个 GE 标记。

IA 是缺省值,通常省略。

ARM: 。 16 位 Thumb: 0 到 1020 范围内 4 的倍数。32 位 Thumb:0-4095。

在 Thumb-2 代码中,此指令的某些格式或所有格式为 16 位(窄)指令。 有关详细信息,请参

阅 Thumb 16 位指令集 (UAL) 快速参考卡。

P

Q

R

S

T

U

V

在 Thumb 状态下,此指令中的 Rn 可为 PC。

如果发生饱和(加法或减法)或溢出(乘法),则设置 Q 标记。 使用 MRS 和 MSR 读取和重置 Q 标记。

在 ARM 指令中, 范围为 1-32。

S 修饰符在 Thumb-2 指令中不可用。

ARM 状态中不可用。

不允许在 IT 块中使用。 不允许在 ARM 或 Thumb 状态下使用条件代码。

如果 NOP 指令不可用,汇编器会插入适当的指令。

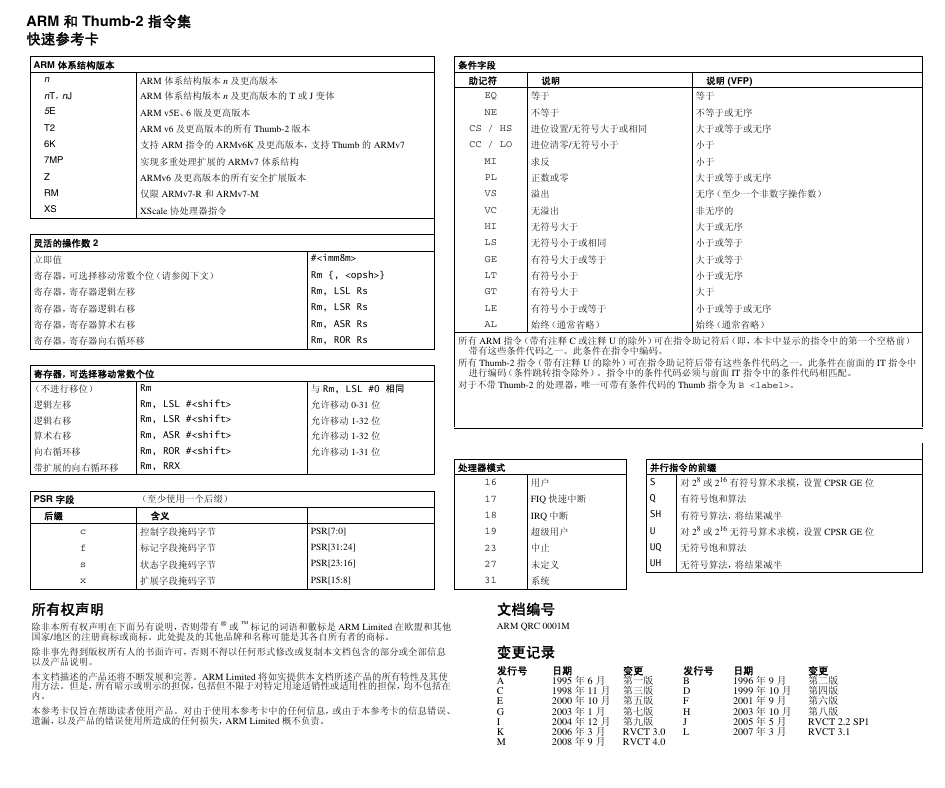

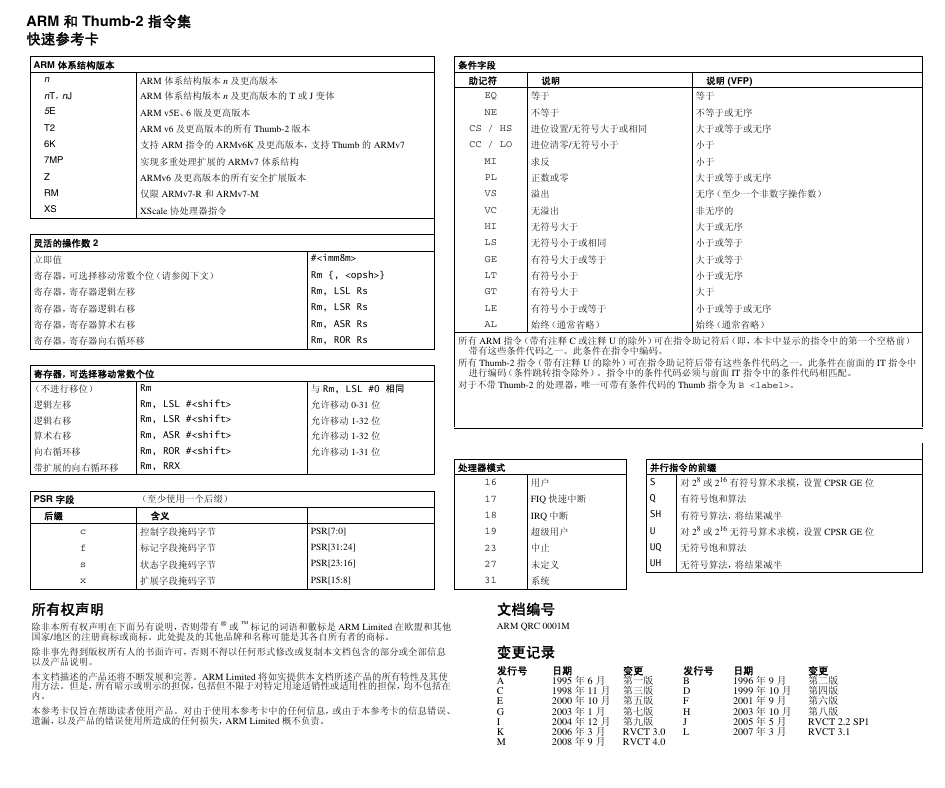

�ARM 和 Thumb-2 指令集

快速参考卡

ARM 体系结构版本

n

nT,nJ

5E

T2

6K

7MP

Z

RM

XS

ARM 体系结构版本 n 及更高版本

ARM 体系结构版本 n 及更高版本的 T 或 J 变体

ARM v5E、6 版及更高版本

ARM v6 及更高版本的所有 Thumb-2 版本

支持 ARM 指令的 ARMv6K 及更高版本,支持 Thumb 的 ARMv7

实现多重处理扩展的 ARMv7 体系结构

ARMv6 及更高版本的所有安全扩展版本

仅限 ARMv7-R 和 ARMv7-M

XScale 协处理器指令

灵活的操作数 2

立即值

寄存器,可选择移动常数个位(请参阅下文)

寄存器,寄存器逻辑左移

寄存器,寄存器逻辑右移

寄存器,寄存器算术右移

寄存器,寄存器向右循环移

(不进行移位)

寄存器,可选择移动常数个位

Rm

Rm, LSL #

Rm, LSR #

Rm, ASR #

Rm, ROR #

Rm, RRX

带扩展的向右循环移

向右循环移

逻辑左移

逻辑右移

算术右移

#

Rm {, }

Rm, LSL Rs

Rm, LSR Rs

Rm, ASR Rs

Rm, ROR Rs

与 Rm, LSL #0 相同

允许移动 0-31 位

允许移动 1-32 位

允许移动 1-32 位

允许移动 1-31 位

PSR 字段

后缀

c

f

s

x

(至少使用一个后缀)

含义

控制字段掩码字节

标记字段掩码字节

状态字段掩码字节

扩展字段掩码字节

PSR[7:0]

PSR[31:24]

PSR[23:16]

PSR[15:8]

所有权声明

除非本所有权声明在下面另有说明,否则带有 ® 或 ™ 标记的词语和徽标是 ARM Limited 在欧盟和其他

国家/地区的注册商标或商标。 此处提及的其他品牌和名称可能是其各自所有者的商标。

除非事先得到版权所有人的书面许可,否则不得以任何形式修改或复制本文档包含的部分或全部信息

以及产品说明。

本文档描述的产品还将不断发展和完善。 ARM Limited 将如实提供本文档所述产品的所有特性及其使

用方法。 但是,所有暗示或明示的担保,包括但不限于对特定用途适销性或适用性的担保,均不包括在

内。

本参考卡仅旨在帮助读者使用产品。 对由于使用本参考卡中的任何信息,或由于本参考卡的信息错误、

遗漏,以及产品的错误使用所造成的任何损失,ARM Limited 概不负责。

条件字段

助记符

EQ

NE

说明

等于

不等于

CS / HS 进位设置/无符号大于或相同

CC / LO 进位清零/无符号小于

MI

PL

VS

VC

HI

LS

GE

LT

GT

LE

AL

求反

正数或零

溢出

无溢出

无符号大于

无符号小于或相同

有符号大于或等于

有符号小于

有符号大于

有符号小于或等于

始终(通常省略)

说明 (VFP)

等于

不等于或无序

大于或等于或无序

小于

小于

大于或等于或无序

无序(至少一个非数字操作数)

非无序的

大于或无序

小于或等于

大于或等于

小于或无序

大于

小于或等于或无序

始终(通常省略)

所有 ARM 指令(带有注释 C 或注释 U 的除外)可在指令助记符后(即,本卡中显示的指令中的第一个空格前)

带有这些条件代码之一。 此条件在指令中编码。

所有 Thumb-2 指令(带有注释 U 的除外)可在指令助记符后带有这些条件代码之一。 此条件在前面的 IT 指令中

进行编码(条件跳转指令除外)。 指令中的条件代码必须与前面 IT 指令中的条件代码相匹配。

对于不带 Thumb-2 的处理器,唯一可带有条件代码的 Thumb 指令为 B 。

处理器模式

16

17

18

19

23

27

31

用户

FIQ 快速中断

IRQ 中断

超级用户

中止

未定义

系统

文档编号

ARM QRC 0001M

并行指令的前缀

S

对 28 或 216 有符号算术求模,设置 CPSR GE 位

有符号饱和算法

Q

SH 有符号算法,将结果减半

U

UQ 无符号饱和算法

UH 无符号算法,将结果减半

对 28 或 216 无符号算术求模,设置 CPSR GE 位

变更记录

发行号

A

C

E

G

I

K

M

变更

日期

1995 年 6 月 第一版

1998 年 11 月 第三版

2000 年 10 月 第五版

2003 年 1 月 第七版

2004 年 12 月 第九版

2006 年 3 月 RVCT 3.0

2008 年 9 月 RVCT 4.0

发行号 日期

B

D

F

H

J

L

变更

1996 年 9 月

第二版

1999 年 10 月 第四版

2001 年 9 月

第六版

2003 年 10 月 第八版

2005 年 5 月

2007 年 3 月

RVCT 2.2 SP1

RVCT 3.1

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc