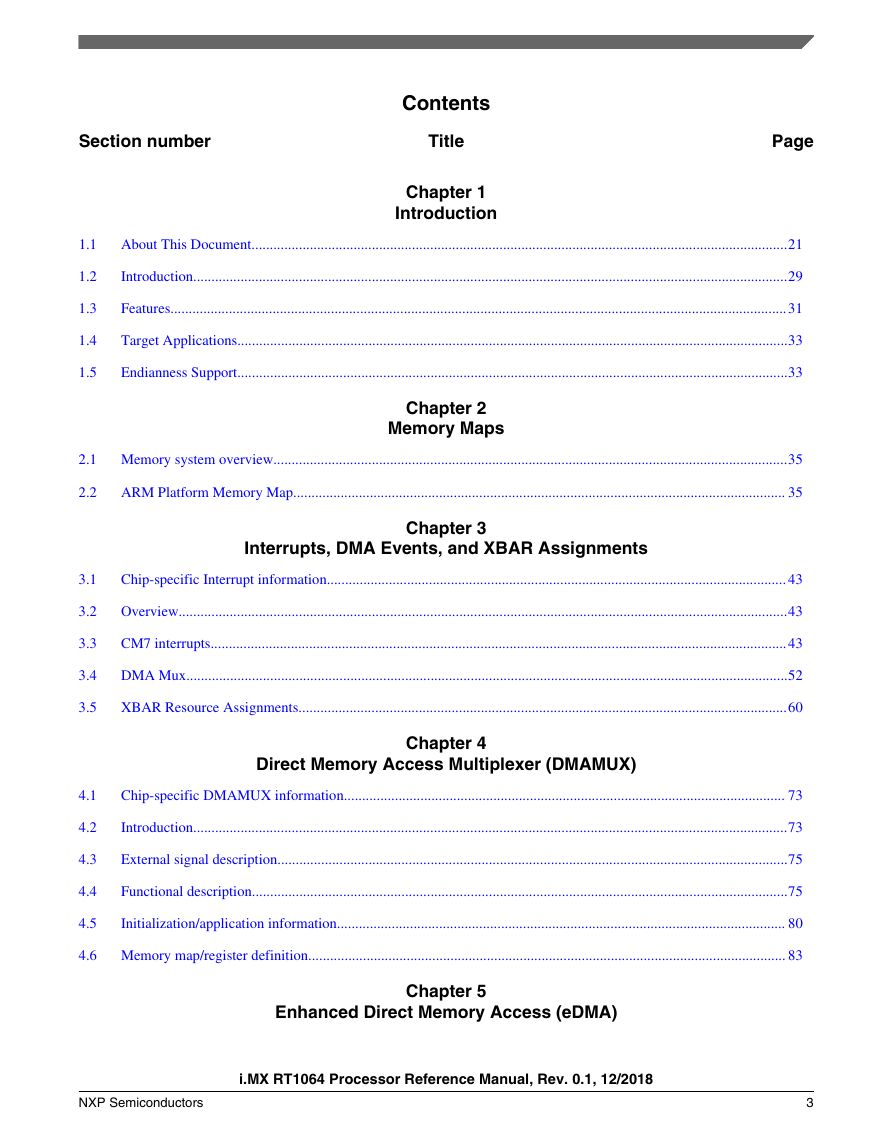

Chapter 1: Introduction

About This Document

Audience

Organization

Suggested Reading

General Information

Related Documentation

Conventions

Register Access

Register Diagram Field Access Type Legend

Register Macro Usage

Signal Conventions

Acronyms and Abbreviations

Introduction

Block Diagram

Features

Target Applications

Endianness Support

Chapter 2: Memory Maps

Memory system overview

ARM Platform Memory Map

Chapter 3-5: Interrupts and DMA

Chapter 3: Interrupts, DMA Events, and XBAR Assignments

Chip-specific Interrupt information

Overview

CM7 interrupts

DMA Mux

XBAR Resource Assignments

Chapter 4: Direct Memory Access Multiplexer (DMAMUX)

Chip-specific DMAMUX information

Introduction

Overview

Features

Modes of operation

External signal description

Functional description

DMA channels with periodic triggering capability

Always-enabled DMA sources

Initialization/application information

Reset

Enabling and configuring sources

Memory map/register definition

DMA_CH_MUX Register Descriptions

DMA_CH_MUX Memory Map

Channel a Configuration (CHCFGa)

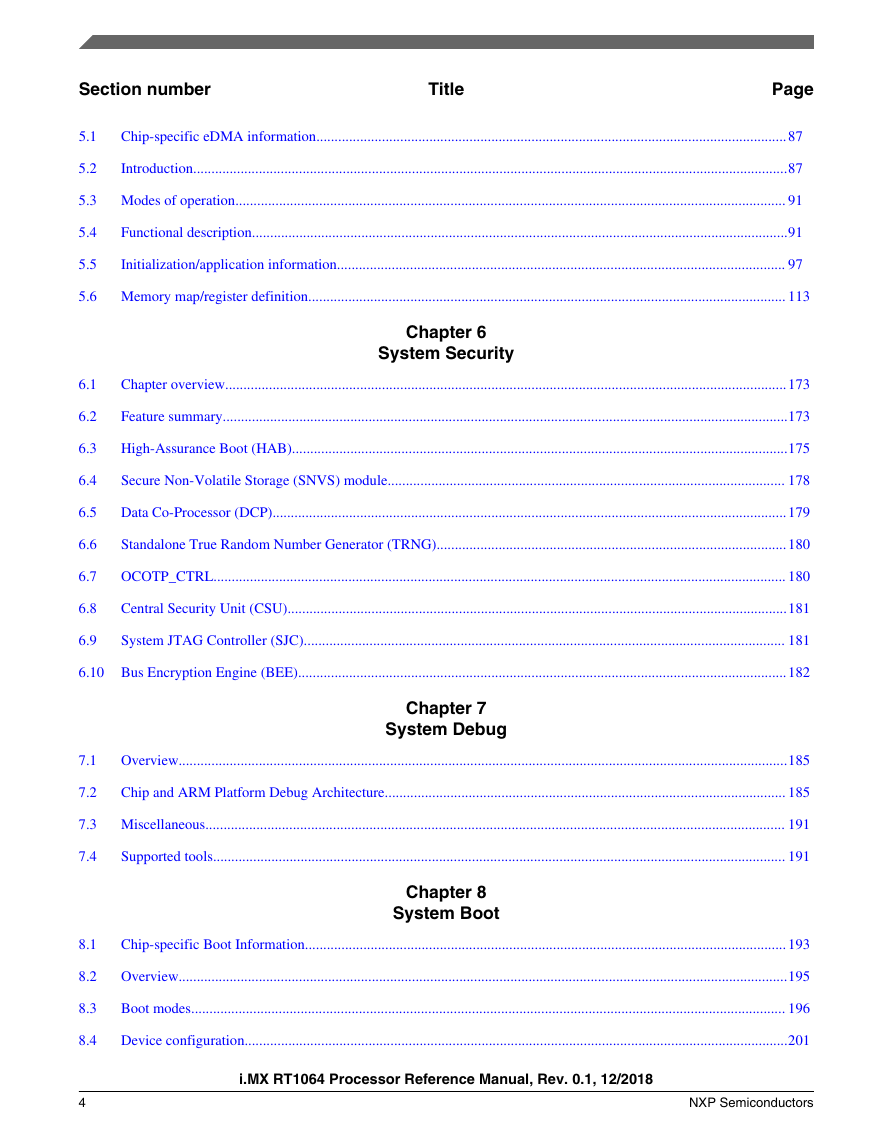

Chapter 5: Enhanced Direct Memory Access (eDMA)

Chip-specific eDMA information

Introduction

eDMA system block diagram

Block parts

Features

Modes of operation

Functional description

eDMA basic data flow

Fault reporting and handling

Channel preemption

Initialization/application information

eDMA initialization

Programming errors

Arbitration mode considerations

Fixed group arbitration, Fixed channel arbitration

Fixed group arbitration, Round-robin channel arbitration

Performing DMA transfers

Single request

Multiple requests

Using the modulo feature

Monitoring transfer descriptor status

Testing for minor loop completion

Reading the transfer descriptors of active channels

Checking channel preemption status

Channel Linking

Dynamic programming

Dynamically changing the channel priority

Dynamic channel linking

Dynamic scatter/gather

Method 1 (channel not using major loop channel linking)

Method 2 (channel using major loop channel linking)

Suspend/resume a DMA channel with active hardware service requests

Suspend an active DMA channel

Resume a DMA channel

Memory map/register definition

TCD memory

TCD initialization

TCD structure

Reserved memory and bit fields

DMA register descriptions

DMA Memory map

Control Register (CR)

Error Status Register (ES)

Enable Request Register (ERQ)

Enable Error Interrupt Register (EEI)

Clear Enable Error Interrupt Register (CEEI)

Set Enable Error Interrupt Register (SEEI)

Clear Enable Request Register (CERQ)

Set Enable Request Register (SERQ)

Clear DONE Status Bit Register (CDNE)

Set START Bit Register (SSRT)

Clear Error Register (CERR)

Clear Interrupt Request Register (CINT)

Interrupt Request Register (INT)

Error Register (ERR)

Hardware Request Status Register (HRS)

Enable Asynchronous Request in Stop Register (EARS)

Channel Priority Register (DCHPRI0 - DCHPRI31)

TCD Source Address (TCD0_SADDR - TCD31_SADDR)

TCD Signed Source Address Offset (TCD0_SOFF - TCD31_SOFF)

TCD Transfer Attributes (TCD0_ATTR - TCD31_ATTR)

TCD Minor Byte Count (Minor Loop Mapping Disabled) (TCD0_NBYTES_MLNO - TCD31_NBYTES_MLNO)

TCD Signed Minor Loop Offset (Minor Loop Mapping Enabled and Offset Disabled) (TCD0_NBYTES_MLOFFNO - TCD31_NBYTES_MLOFFNO)

TCD Signed Minor Loop Offset (Minor Loop Mapping and Offset Enabled) (TCD0_NBYTES_MLOFFYES - TCD31_NBYTES_MLOFFYES)

TCD Last Source Address Adjustment (TCD0_SLAST - TCD31_SLAST)

TCD Destination Address (TCD0_DADDR - TCD31_DADDR)

TCD Signed Destination Address Offset (TCD0_DOFF - TCD31_DOFF)

TCD Current Minor Loop Link, Major Loop Count (Channel Linking Disabled) (TCD0_CITER_ELINKNO - TCD31_CITER_ELINKNO)

TCD Current Minor Loop Link, Major Loop Count (Channel Linking Enabled) (TCD0_CITER_ELINKYES - TCD31_CITER_ELINKYES)

TCD Last Destination Address Adjustment/Scatter Gather Address (TCD0_DLASTSGA - TCD31_DLASTSGA)

TCD Control and Status (TCD0_CSR - TCD31_CSR)

TCD Beginning Minor Loop Link, Major Loop Count (Channel Linking Disabled) (TCD0_BITER_ELINKNO - TCD31_BITER_ELINKNO)

TCD Beginning Minor Loop Link, Major Loop Count (Channel Linking Enabled) (TCD0_BITER_ELINKYES - TCD31_BITER_ELINKYES)

Chapter 6: System Security

Chapter overview

Feature summary

High-Assurance Boot (HAB)

HAB process flow

HAB feature summary

Secure Non-Volatile Storage (SNVS) module

SNVS architecture

Data Co-Processor (DCP)

Standalone True Random Number Generator (TRNG)

OCOTP_CTRL

Central Security Unit (CSU)

System JTAG Controller (SJC)

Scan protection

Bus Encryption Engine (BEE)

Chapter 7: System Debug

Overview

Chip and ARM Platform Debug Architecture

Debug Features

Debug system components

AMBA Trace Bus (ATB)

CoreSight trace port interface (TPIU)

Embedded Trace Macrocell (ETM)

Instrumentation Trace Macrocell

Chip-Specific SJC Features

JTAG Disable Mode

JTAG ID

System JTAG controller main features

SJC TAP Port

SJC main blocks

Miscellaneous

Clock/Reset/Power

Supported tools

Chapter 8: System Boot

Chip-specific Boot Information

Overview

Boot modes

Boot mode pin settings

High-level boot sequence

Boot From Fuses mode (BOOT_MODE[1:0] = 00b)

Serial Downloader (BOOT_MODE[1:0] = 01b)

Internal Boot mode (BOOT_MODE[1:0] = 0b10)

Boot security settings

Device configuration

Boot eFUSE descriptions

GPIO boot overrides

Device Configuration Data (DCD)

Device initialization

Internal ROM/RAM memory map

Boot block activation

Clocks at boot time

Enabling Caches

Exception handling

Interrupt handling during boot

Persistent bits

Boot devices (internal boot)

Serial NOR Flash Boot via FlexSPI

Serial NOR eFUSE Configuration

FlexSPI Serial NOR Flash Boot Operation

FlexSPI NOR boot flow chart

Serial NOR and NAND configuration based on FlexSPI interface

FlexSPI Configuration Block

Serial NOR configuration block (512 bytes)

Parallel NOR and NAND configuration based on SEMC interface

SEMC Configuration Block

Parallel NOR Configuration Block (80 bytes)

Parallel NAND Configuration Block (256 bytes)

Expansion device

Expansion device eFUSE configuration

MMC and eMMC boot

SD, eSD, and SDXC

IOMUX configuration for SD/MMC

Redundant boot support for expansion device

Serial NOR/EEPROM through LPSPI

Serial NOR/EEPROM eFUSE configuration

Program image

Image Vector Table and Boot Data

Image vector table structure

Boot data structure

Device Configuration Data (DCD)

Write data command

Check data command

NOP command

Unlock command

Plugin image

Serial Downloader

USB

USB configuration details

IOMUX configuration for USB

Serial Download Protocol (SDP)

SDP commands

READ_REGISTER

WRITE_REGISTER

WRITE_FILE

ERROR_STATUS

DCD_WRITE

JUMP_ADDRESS

SET_BAUDRATE

Recovery devices

SD/MMC manufacture mode

High-Assurance Boot (HAB)

HAB API vector table addresses

ROM APIs

Chapter 9-11: Chip IO

Chapter 9: External Signals and Pin Multiplexing

Overview

Muxing Options

Chapter 10: IOMUX Controller (IOMUXC)

Overview

Features

Clocks

Functional description

ALT6 and ALT7 extended muxing modes

SW Loopback through SION bit

Daisy chain - multi pads driving same module input pin

IOMUXC GPR Memory Map/Register Definition

IOMUXC_GPR

IOMUXC_GPR_GPR0

IOMUXC_GPR_GPR1

IOMUXC_GPR_GPR2

IOMUXC_GPR_GPR3

IOMUXC_GPR_GPR4

IOMUXC_GPR_GPR5

IOMUXC_GPR_GPR6

IOMUXC_GPR_GPR7

IOMUXC_GPR_GPR8

IOMUXC_GPR_GPR9

IOMUXC_GPR_GPR10

IOMUXC_GPR_GPR11

IOMUXC_GPR_GPR12

IOMUXC_GPR_GPR13

IOMUXC_GPR_GPR14

IOMUXC_GPR_GPR15

IOMUXC_GPR_GPR16

IOMUXC_GPR_GPR17

IOMUXC_GPR_GPR18

IOMUXC_GPR_GPR19

IOMUXC_GPR_GPR20

IOMUXC_GPR_GPR21

IOMUXC_GPR_GPR22

IOMUXC_GPR_GPR23

IOMUXC_GPR_GPR24

IOMUXC_GPR_GPR25

IOMUXC_GPR_GPR26

IOMUXC_GPR_GPR27

IOMUXC_GPR_GPR28

IOMUXC_GPR_GPR29

IOMUXC_GPR_GPR30

IOMUXC_GPR_GPR31

IOMUXC_GPR_GPR32

IOMUXC_GPR_GPR33

IOMUXC_GPR_GPR34

IOMUXC SNVS Memory Map/Register Definition

IOMUXC_SNVS

IOMUXC_SNVS_SW_MUX_CTL_PAD_WAKEUP

IOMUXC_SNVS_SW_MUX_CTL_PAD_PMIC_ON_REQ

IOMUXC_SNVS_SW_MUX_CTL_PAD_PMIC_STBY_REQ

IOMUXC_SNVS_SW_PAD_CTL_PAD_TEST_MODE

IOMUXC_SNVS_SW_PAD_CTL_PAD_POR_B

IOMUXC_SNVS_SW_PAD_CTL_PAD_ONOFF

IOMUXC_SNVS_SW_PAD_CTL_PAD_WAKEUP

IOMUXC_SNVS_SW_PAD_CTL_PAD_PMIC_ON_REQ

IOMUXC_SNVS_SW_PAD_CTL_PAD_PMIC_STBY_REQ

IOMUXC SNVS GPR Memory Map/Register Definition

IOMUXC_SNVS_GPR

IOMUXC_SNVS_GPR_GPR0

IOMUXC_SNVS_GPR_GPR1

IOMUXC_SNVS_GPR_GPR2

IOMUXC_SNVS_GPR_GPR3

IOMUXC Memory Map/Register Definition

IOMUXC

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_00

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_01

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_02

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_03

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_04

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_05

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_06

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_07

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_08

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_09

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_10

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_11

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_12

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_13

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_14

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_15

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_16

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_17

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_18

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_19

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_20

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_21

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_22

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_23

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_24

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_25

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_26

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_27

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_28

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_29

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_30

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_31

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_32

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_33

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_34

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_35

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_36

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_37

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_38

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_39

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_40

IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_41

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_00

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_01

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_02

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_03

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_04

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_05

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_06

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_07

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_08

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_09

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_10

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_11

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_12

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_13

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_14

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B0_15

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_00

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_01

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_02

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_03

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_04

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_05

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_06

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_07

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_08

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_09

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_10

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_11

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_12

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_13

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_14

IOMUXC_SW_MUX_CTL_PAD_GPIO_AD_B1_15

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_00

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_01

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_02

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_03

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_04

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_05

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_06

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_07

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_08

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_09

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_10

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_11

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_12

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_13

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_14

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_15

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_00

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_01

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_02

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_03

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_04

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_05

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_06

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_07

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_08

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_09

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_10

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_11

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_12

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_13

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_14

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_15

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B0_00

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B0_01

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B0_02

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B0_03

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B0_04

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B0_05

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B1_00

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B1_01

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B1_02

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B1_03

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B1_04

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B1_05

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B1_06

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B1_07

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B1_08

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B1_09

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B1_10

IOMUXC_SW_MUX_CTL_PAD_GPIO_SD_B1_11

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_00

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_01

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_02

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_03

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_04

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_05

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_06

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_07

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_08

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_09

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_10

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_11

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_12

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_13

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_14

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_15

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_16

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_17

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_18

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_19

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_20

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_21

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_22

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_23

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_24

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_25

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_26

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_27

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_28

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_29

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_30

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_31

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_32

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_33

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_34

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_35

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_36

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_37

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_38

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_39

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_40

IOMUXC_SW_PAD_CTL_PAD_GPIO_EMC_41

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_00

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_01

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_02

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_03

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_04

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_05

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_06

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_07

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_08

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_09

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_10

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_11

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_12

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_13

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_14

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_15

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_00

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_01

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_02

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_03

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_04

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_05

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_06

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_07

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_08

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_09

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_10

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_11

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_12

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_13

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_14

IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B1_15

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_00

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_01

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_02

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_03

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_04

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_05

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_06

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_07

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_08

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_09

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_10

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_11

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_12

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_13

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_14

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_15

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_00

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_01

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_02

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_03

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_04

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_05

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_06

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_07

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_08

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_09

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_10

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_11

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_12

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_13

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_14

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_15

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B0_00

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B0_01

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B0_02

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B0_03

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B0_04

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B0_05

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B1_00

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B1_01

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B1_02

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B1_03

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B1_04

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B1_05

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B1_06

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B1_07

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B1_08

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B1_09

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B1_10

IOMUXC_SW_PAD_CTL_PAD_GPIO_SD_B1_11

IOMUXC_ANATOP_USB_OTG1_ID_SELECT_INPUT

IOMUXC_ANATOP_USB_OTG2_ID_SELECT_INPUT

IOMUXC_CCM_PMIC_READY_SELECT_INPUT

IOMUXC_CSI_DATA02_SELECT_INPUT

IOMUXC_CSI_DATA03_SELECT_INPUT

IOMUXC_CSI_DATA04_SELECT_INPUT

IOMUXC_CSI_DATA05_SELECT_INPUT

IOMUXC_CSI_DATA06_SELECT_INPUT

IOMUXC_CSI_DATA07_SELECT_INPUT

IOMUXC_CSI_DATA08_SELECT_INPUT

IOMUXC_CSI_DATA09_SELECT_INPUT

IOMUXC_CSI_HSYNC_SELECT_INPUT

IOMUXC_CSI_PIXCLK_SELECT_INPUT

IOMUXC_CSI_VSYNC_SELECT_INPUT

IOMUXC_ENET_IPG_CLK_RMII_SELECT_INPUT

IOMUXC_ENET_MDIO_SELECT_INPUT

IOMUXC_ENET0_RXDATA_SELECT_INPUT

IOMUXC_ENET1_RXDATA_SELECT_INPUT

IOMUXC_ENET_RXEN_SELECT_INPUT

IOMUXC_ENET_RXERR_SELECT_INPUT

IOMUXC_ENET0_TIMER_SELECT_INPUT

IOMUXC_ENET_TXCLK_SELECT_INPUT

IOMUXC_FLEXCAN1_RX_SELECT_INPUT

IOMUXC_FLEXCAN2_RX_SELECT_INPUT

IOMUXC_FLEXPWM1_PWMA3_SELECT_INPUT

IOMUXC_FLEXPWM1_PWMA0_SELECT_INPUT

IOMUXC_FLEXPWM1_PWMA1_SELECT_INPUT

IOMUXC_FLEXPWM1_PWMA2_SELECT_INPUT

IOMUXC_FLEXPWM1_PWMB3_SELECT_INPUT

IOMUXC_FLEXPWM1_PWMB0_SELECT_INPUT

IOMUXC_FLEXPWM1_PWMB1_SELECT_INPUT

IOMUXC_FLEXPWM1_PWMB2_SELECT_INPUT

IOMUXC_FLEXPWM2_PWMA3_SELECT_INPUT

IOMUXC_FLEXPWM2_PWMA0_SELECT_INPUT

IOMUXC_FLEXPWM2_PWMA1_SELECT_INPUT

IOMUXC_FLEXPWM2_PWMA2_SELECT_INPUT

IOMUXC_FLEXPWM2_PWMB3_SELECT_INPUT

IOMUXC_FLEXPWM2_PWMB0_SELECT_INPUT

IOMUXC_FLEXPWM2_PWMB1_SELECT_INPUT

IOMUXC_FLEXPWM2_PWMB2_SELECT_INPUT

IOMUXC_FLEXPWM4_PWMA0_SELECT_INPUT

IOMUXC_FLEXPWM4_PWMA1_SELECT_INPUT

IOMUXC_FLEXPWM4_PWMA2_SELECT_INPUT

IOMUXC_FLEXPWM4_PWMA3_SELECT_INPUT

IOMUXC_FLEXSPIA_DQS_SELECT_INPUT

IOMUXC_FLEXSPIA_DATA0_SELECT_INPUT

IOMUXC_FLEXSPIA_DATA1_SELECT_INPUT

IOMUXC_FLEXSPIA_DATA2_SELECT_INPUT

IOMUXC_FLEXSPIA_DATA3_SELECT_INPUT

IOMUXC_FLEXSPIB_DATA0_SELECT_INPUT

IOMUXC_FLEXSPIB_DATA1_SELECT_INPUT

IOMUXC_FLEXSPIB_DATA2_SELECT_INPUT

IOMUXC_FLEXSPIB_DATA3_SELECT_INPUT

IOMUXC_FLEXSPIA_SCK_SELECT_INPUT

IOMUXC_LPI2C1_SCL_SELECT_INPUT

IOMUXC_LPI2C1_SDA_SELECT_INPUT

IOMUXC_LPI2C2_SCL_SELECT_INPUT

IOMUXC_LPI2C2_SDA_SELECT_INPUT

IOMUXC_LPI2C3_SCL_SELECT_INPUT

IOMUXC_LPI2C3_SDA_SELECT_INPUT

IOMUXC_LPI2C4_SCL_SELECT_INPUT

IOMUXC_LPI2C4_SDA_SELECT_INPUT

IOMUXC_LPSPI1_PCS0_SELECT_INPUT

IOMUXC_LPSPI1_SCK_SELECT_INPUT

IOMUXC_LPSPI1_SDI_SELECT_INPUT

IOMUXC_LPSPI1_SDO_SELECT_INPUT

IOMUXC_LPSPI2_PCS0_SELECT_INPUT

IOMUXC_LPSPI2_SCK_SELECT_INPUT

IOMUXC_LPSPI2_SDI_SELECT_INPUT

IOMUXC_LPSPI2_SDO_SELECT_INPUT

IOMUXC_LPSPI3_PCS0_SELECT_INPUT

IOMUXC_LPSPI3_SCK_SELECT_INPUT

IOMUXC_LPSPI3_SDI_SELECT_INPUT

IOMUXC_LPSPI3_SDO_SELECT_INPUT

IOMUXC_LPSPI4_PCS0_SELECT_INPUT

IOMUXC_LPSPI4_SCK_SELECT_INPUT

IOMUXC_LPSPI4_SDI_SELECT_INPUT

IOMUXC_LPSPI4_SDO_SELECT_INPUT

IOMUXC_LPUART2_RX_SELECT_INPUT

IOMUXC_LPUART2_TX_SELECT_INPUT

IOMUXC_LPUART3_CTS_B_SELECT_INPUT

IOMUXC_LPUART3_RX_SELECT_INPUT

IOMUXC_LPUART3_TX_SELECT_INPUT

IOMUXC_LPUART4_RX_SELECT_INPUT

IOMUXC_LPUART4_TX_SELECT_INPUT

IOMUXC_LPUART5_RX_SELECT_INPUT

IOMUXC_LPUART5_TX_SELECT_INPUT

IOMUXC_LPUART6_RX_SELECT_INPUT

IOMUXC_LPUART6_TX_SELECT_INPUT

IOMUXC_LPUART7_RX_SELECT_INPUT

IOMUXC_LPUART7_TX_SELECT_INPUT

IOMUXC_LPUART8_RX_SELECT_INPUT

IOMUXC_LPUART8_TX_SELECT_INPUT

IOMUXC_NMI_SELECT_INPUT

IOMUXC_QTIMER2_TIMER0_SELECT_INPUT

IOMUXC_QTIMER2_TIMER1_SELECT_INPUT

IOMUXC_QTIMER2_TIMER2_SELECT_INPUT

IOMUXC_QTIMER2_TIMER3_SELECT_INPUT

IOMUXC_QTIMER3_TIMER0_SELECT_INPUT

IOMUXC_QTIMER3_TIMER1_SELECT_INPUT

IOMUXC_QTIMER3_TIMER2_SELECT_INPUT

IOMUXC_QTIMER3_TIMER3_SELECT_INPUT

IOMUXC_SAI1_MCLK2_SELECT_INPUT

IOMUXC_SAI1_RX_BCLK_SELECT_INPUT

IOMUXC_SAI1_RX_DATA0_SELECT_INPUT

IOMUXC_SAI1_RX_DATA1_SELECT_INPUT

IOMUXC_SAI1_RX_DATA2_SELECT_INPUT

IOMUXC_SAI1_RX_DATA3_SELECT_INPUT

IOMUXC_SAI1_RX_SYNC_SELECT_INPUT

IOMUXC_SAI1_TX_BCLK_SELECT_INPUT

IOMUXC_SAI1_TX_SYNC_SELECT_INPUT

IOMUXC_SAI2_MCLK2_SELECT_INPUT

IOMUXC_SAI2_RX_BCLK_SELECT_INPUT

IOMUXC_SAI2_RX_DATA0_SELECT_INPUT

IOMUXC_SAI2_RX_SYNC_SELECT_INPUT

IOMUXC_SAI2_TX_BCLK_SELECT_INPUT

IOMUXC_SAI2_TX_SYNC_SELECT_INPUT

IOMUXC_SPDIF_IN_SELECT_INPUT

IOMUXC_USB_OTG2_OC_SELECT_INPUT

IOMUXC_USB_OTG1_OC_SELECT_INPUT

IOMUXC_USDHC1_CD_B_SELECT_INPUT

IOMUXC_USDHC1_WP_SELECT_INPUT

IOMUXC_USDHC2_CLK_SELECT_INPUT

IOMUXC_USDHC2_CD_B_SELECT_INPUT

IOMUXC_USDHC2_CMD_SELECT_INPUT

IOMUXC_USDHC2_DATA0_SELECT_INPUT

IOMUXC_USDHC2_DATA1_SELECT_INPUT

IOMUXC_USDHC2_DATA2_SELECT_INPUT

IOMUXC_USDHC2_DATA3_SELECT_INPUT

IOMUXC_USDHC2_DATA4_SELECT_INPUT

IOMUXC_USDHC2_DATA5_SELECT_INPUT

IOMUXC_USDHC2_DATA6_SELECT_INPUT

IOMUXC_USDHC2_DATA7_SELECT_INPUT

IOMUXC_USDHC2_WP_SELECT_INPUT

IOMUXC_XBAR1_IN02_SELECT_INPUT

IOMUXC_XBAR1_IN03_SELECT_INPUT

IOMUXC_XBAR1_IN04_SELECT_INPUT

IOMUXC_XBAR1_IN05_SELECT_INPUT

IOMUXC_XBAR1_IN06_SELECT_INPUT

IOMUXC_XBAR1_IN07_SELECT_INPUT

IOMUXC_XBAR1_IN08_SELECT_INPUT

IOMUXC_XBAR1_IN09_SELECT_INPUT

IOMUXC_XBAR1_IN17_SELECT_INPUT

IOMUXC_XBAR1_IN18_SELECT_INPUT

IOMUXC_XBAR1_IN20_SELECT_INPUT

IOMUXC_XBAR1_IN22_SELECT_INPUT

IOMUXC_XBAR1_IN23_SELECT_INPUT

IOMUXC_XBAR1_IN24_SELECT_INPUT

IOMUXC_XBAR1_IN14_SELECT_INPUT

IOMUXC_XBAR1_IN15_SELECT_INPUT

IOMUXC_XBAR1_IN16_SELECT_INPUT

IOMUXC_XBAR1_IN25_SELECT_INPUT

IOMUXC_XBAR1_IN19_SELECT_INPUT

IOMUXC_XBAR1_IN21_SELECT_INPUT

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B0_00

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B0_01

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B0_02

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B0_03

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B0_04

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B0_05

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B0_06

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B0_07

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B0_08

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B0_09

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B0_10

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B0_11

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B0_12

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B0_13

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B1_00

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B1_01

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B1_02

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B1_03

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B1_04

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B1_05

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B1_06

IOMUXC_SW_PAD_CTL_PAD_GPIO_SPI_B1_07

IOMUXC_ENET2_IPG_CLK_RMII_SELECT_INPUT

IOMUXC_ENET2_IPP_IND_MAC0_MDIO_SELECT_INPUT

IOMUXC_ENET2_IPP_IND_MAC0_RXDATA_SELECT_INPUT_0

IOMUXC_ENET2_IPP_IND_MAC0_RXDATA_SELECT_INPUT_1

IOMUXC_ENET2_IPP_IND_MAC0_RXEN_SELECT_INPUT

IOMUXC_ENET2_IPP_IND_MAC0_RXERR_SELECT_INPUT

IOMUXC_ENET2_IPP_IND_MAC0_TIMER_SELECT_INPUT_0

IOMUXC_ENET2_IPP_IND_MAC0_TXCLK_SELECT_INPUT

IOMUXC_GPT1_IPP_IND_CAPIN1_SELECT_INPUT

IOMUXC_GPT1_IPP_IND_CAPIN2_SELECT_INPUT

IOMUXC_GPT1_IPP_IND_CLKIN_SELECT_INPUT

IOMUXC_GPT2_IPP_IND_CAPIN1_SELECT_INPUT

IOMUXC_GPT2_IPP_IND_CAPIN2_SELECT_INPUT

IOMUXC_GPT2_IPP_IND_CLKIN_SELECT_INPUT

IOMUXC_SAI3_IPG_CLK_SAI_MCLK_SELECT_INPUT_2

IOMUXC_SAI3_IPP_IND_SAI_RXBCLK_SELECT_INPUT

IOMUXC_SAI3_IPP_IND_SAI_RXDATA_SELECT_INPUT_0

IOMUXC_SAI3_IPP_IND_SAI_RXSYNC_SELECT_INPUT

IOMUXC_SAI3_IPP_IND_SAI_TXBCLK_SELECT_INPUT

IOMUXC_SAI3_IPP_IND_SAI_TXSYNC_SELECT_INPUT

IOMUXC_SEMC_I_IPP_IND_DQS4_SELECT_INPUT

IOMUXC_CANFD_IPP_IND_CANRX_SELECT_INPUT

Chapter 11: General Purpose Input/Output (GPIO)

Chip-specific GPIO information

Overview

Block Diagram

Features

Clocks

GPIO Functional Description

GPIO Function

GPIO pad structure

Input Driver

Schmitt trigger

Input keeper

Output Driver

Drive strength

Output keeper

PU / PD / Keeper Logic

Open drain

GPIO Programming

GPIO Read Mode

GPIO Write Mode

Interrupt Control Unit

GPIO Register Descriptions

GPIO Memory map

GPIO data register (DR)

GPIO direction register (GDIR)

GPIO pad status register (PSR)

GPIO interrupt configuration register1 (ICR1)

GPIO interrupt configuration register2 (ICR2)

GPIO interrupt mask register (IMR)

GPIO interrupt status register (ISR)

GPIO edge select register (EDGE_SEL)

GPIO data register SET (DR_SET)

GPIO data register CLEAR (DR_CLEAR)

GPIO data register TOGGLE (DR_TOGGLE)

Chapter 12-18: Clocking and Power

Chapter 12: Clock and Power Management

Introduction

Device Power Management Architecture Components

Centralized components of clock generation and management

Centralized components of power generation, distribution and management

Reset generation and distribution system

Power and clock management framework

Clock Management

Centralized components of clock management system

Clock generation

Crystal Oscillator (XTALOSC)

PLLs

General PLL Control and Status Functions

CCM

Low Power Clock Gating unit (LPCG)

Peripheral components of clock management system

Interface and functional clock

Block level clock management

Master clock protocol

Slave clock protocol

Clock Domain(s)

Domain level clock management

Domain dependencies

Power management

Centralized Components of Power Management System

Integrated PMU

DCDC Regulator

Analog LDO regulators

USB LDO

SNVS regulator

GPC - General Power Controller

SRC - System reset Controller

Power domain(s)

Power distribution

Domain memory and domain logic state retention in case of power gating

Power Gating Domain Management

ARM Core Platform

SoC

Power Gating domain dependencies

Voltage domains

Voltage domain management

Dynamic

Voltage Scaling

Static

Standby Leakage reduction (SLR)

System domains layout

Power management techniques

Power saving techniques

Thermal-aware power management

Peripheral Power management

IO power reduction

Examples of External Power Supply Interface

ONOFF (Button)

WAKEUP Pin

Chapter 13: Clock Controller Module (CCM)

Chip-specific CCM information

Overview

Features

CCM Block Diagram

External Signals

CCM Clock Tree

System Clocks

Functional Description

Clock Generation

External Low Frequency Clock - CKIL

CKIL synchronizing to IPG_CLK

External High Frequency Clock - CKIH and internal oscillator

PLL reference clock

ARM PLL (PLL1)

System PLL (PLL2)

USB1 PLL (PLL3)

Audio PLL (PLL4)

Video PLL (PLL5)

Ethernet PLL (PLL6)

USB2 PLL (PLL7)

Phase Fractional Dividers (PFD)

CCM internal clock generation

Clock Switcher

PLL bypass procedure

PLL clock change

Clock Root Generator

Divider change handshake

Disabling / Enabling PLLs

Clock Switching Multiplexers

Low Power Clock Gating module (LPCG)

DVFS support

Power modes

RUN mode

WAIT mode

Entering WAIT mode

Exiting WAIT mode

STOP mode

Entering STOP mode

Exiting STOP mode

CCM Memory Map/Register Definition

CCM

CCM_CCR

CCM_CSR

CCM_CCSR

CCM_CACRR

CCM_CBCDR

CCM_CBCMR

CCM_CSCMR1

CCM_CSCMR2

CCM_CSCDR1

CCM_CS1CDR

CCM_CS2CDR

CCM_CDCDR

CCM_CSCDR2

CCM_CSCDR3

CCM_CDHIPR

CCM_CLPCR

CCM_CISR

CCM_CIMR

CCM_CCOSR

CCM_CGPR

CCM_CCGR0

CCM_CCGR1

CCM_CCGR2

CCM_CCGR3

CCM_CCGR4

CCM_CCGR5

CCM_CCGR6

CCM_CCGR7

CCM_CMEOR

CCM Analog Memory Map/Register Definition

CCM_ANALOG

CCM_ANALOG_PLL_ARMn

CCM_ANALOG_PLL_USB1n

CCM_ANALOG_PLL_USB2n

CCM_ANALOG_PLL_SYSn

CCM_ANALOG_PLL_SYS_SS

CCM_ANALOG_PLL_SYS_NUM

CCM_ANALOG_PLL_SYS_DENOM

CCM_ANALOG_PLL_AUDIOn

CCM_ANALOG_PLL_AUDIO_NUM

CCM_ANALOG_PLL_AUDIO_DENOM

CCM_ANALOG_PLL_VIDEOn

CCM_ANALOG_PLL_VIDEO_NUM

CCM_ANALOG_PLL_VIDEO_DENOM

CCM_ANALOG_PLL_ENETn

CCM_ANALOG_PFD_480n

CCM_ANALOG_PFD_528n

CCM_ANALOG_MISC0n

CCM_ANALOG_MISC1n

CCM_ANALOG_MISC2n

Chapter 14: Crystal Oscillator (XTALOSC)

Chip-specific XTALOSC information

Overview

External Signals

Crystal Oscillator 24 MHz

Oscillator Configuration (24 MHz)

Bypass Configuration (24 MHz)

RC Oscillator (24 MHz)

Crystal Frequency Detection(24 MHz)

Crystal Oscillator 32 kHz

Oscillator Configuration (32 kHz)

Bypass Configuration (32 kHz)

XTALOSC 24MHz Memory Map/Register Definition

XTALOSC24M

XTALOSC24M_MISC0n

XTALOSC24M_LOWPWR_CTRLn

XTALOSC24M_OSC_CONFIG0n

XTALOSC24M_OSC_CONFIG1n

XTALOSC24M_OSC_CONFIG2n

Chapter 15: Power Management Unit (PMU)

Chip-specific PMU information

Overview

Digital LDO Regulators

Analog LDO Regulators

LDO 1P1

LDO 2P5

Low Power Operation

USB LDO Regulator

SNVS Regulator

PMU Memory Map/Register Definition

PMU

PMU_REG_1P1n

PMU_REG_3P0n

PMU_REG_2P5n

PMU_REG_COREn

PMU_MISC0n

PMU_MISC1n

PMU_MISC2n

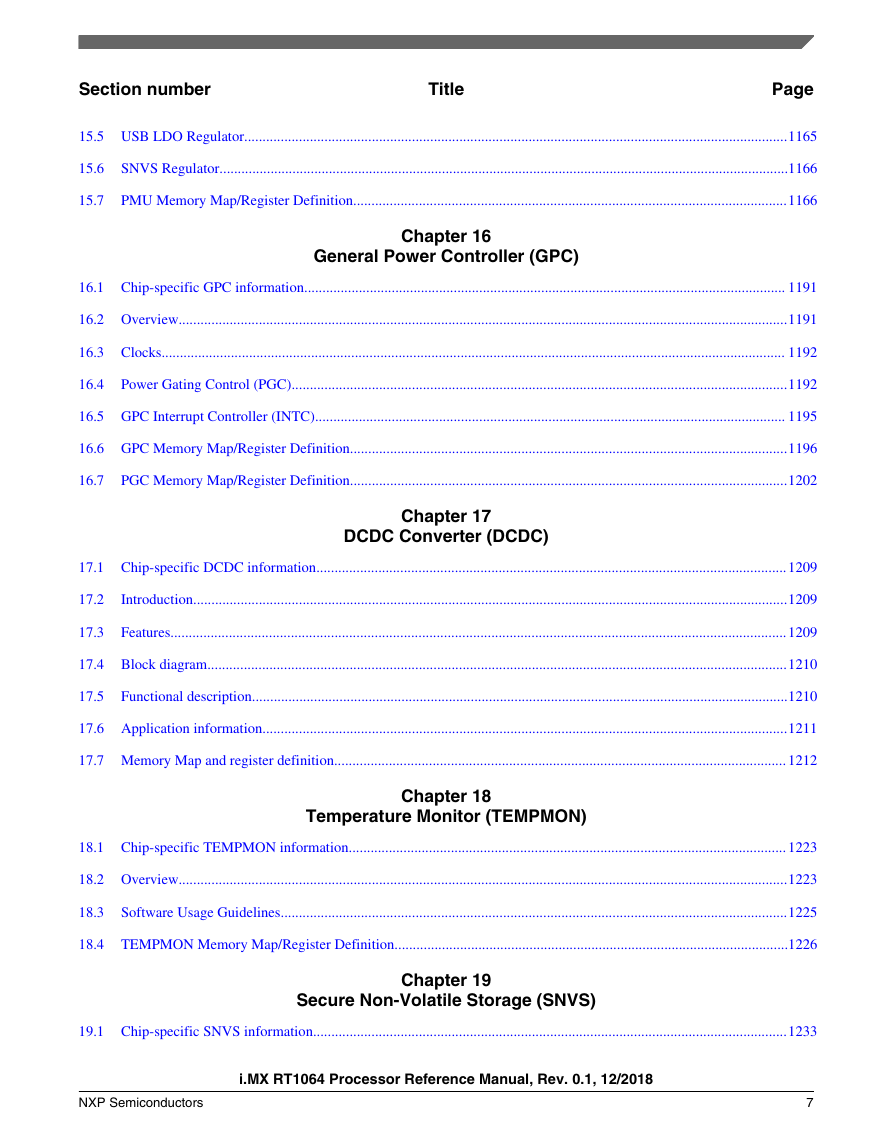

Chapter 16: General Power Controller (GPC)

Chip-specific GPC information

Overview

Clocks

Power Gating Control (PGC)

Overview

Features

GPC Interrupt Controller (INTC)

Interrupt Controller features

GPC Memory Map/Register Definition

GPC

GPC_CNTR

GPC_IMR1

GPC_IMR2

GPC_IMR3

GPC_IMR4

GPC_ISR1

GPC_ISR2

GPC_ISR3

GPC_ISR4

GPC_IMR5

GPC_ISR5

PGC Memory Map/Register Definition

PGC

PGC_MEGA_CTRL

PGC_MEGA_PUPSCR

PGC_MEGA_PDNSCR

PGC_MEGA_SR

PGC_CPU_CTRL

PGC_CPU_PUPSCR

PGC_CPU_PDNSCR

PGC_CPU_SR

Chapter 17: DCDC Converter (DCDC)

Chip-specific DCDC information

Introduction

Features

Block diagram

Functional description

Application information

Memory Map and register definition

DCDC register descriptions

DCDC Memory map

DCDC Register 0 (REG0)

DCDC Register 1 (REG1)

DCDC Register 2 (REG2)

DCDC Register 3 (REG3)

Chapter 18: Temperature Monitor (TEMPMON)

Chip-specific TEMPMON information

Overview

Software Usage Guidelines

TEMPMON Memory Map/Register Definition

TEMPMON

TEMPMON_TEMPSENSE0n

TEMPMON_TEMPSENSE1n

TEMPMON_TEMPSENSE2n

Chapter 19-22: SNVS, Reset and Fuse

Chapter 19: Secure Non-Volatile Storage (SNVS)

Chip-specific SNVS information

SNVS introduction

SNVS feature list

SNVS functional description

SNVS Structure

SNVS power domains

SNVS clock sources

Runtime Procedures

Using SNVS Timer Facilities

SNVS_HP Real Time Counter

RTC/SRTC control bits setting

Reading RTC and SRTC values

Using Other SNVS Registers

Using the General-Purpose Register

Reset and Initialization of SNVS

Initialization Checklists

SNVS register descriptions

SNVS Memory map

SNVS_HP Lock Register (HPLR)

SNVS_HP Command Register (HPCOMR)

SNVS_HP Control Register (HPCR)

SNVS_HP Status Register (HPSR)

SNVS_HP Real Time Counter MSB Register (HPRTCMR)

SNVS_HP Real Time Counter LSB Register (HPRTCLR)

SNVS_HP Time Alarm MSB Register (HPTAMR)

SNVS_HP Time Alarm LSB Register (HPTALR)

SNVS_LP Lock Register (LPLR)

SNVS_LP Control Register (LPCR)

SNVS_LP Status Register (LPSR)

SNVS_LP Secure Monotonic Counter MSB Register (LPSMCMR)

SNVS_LP Secure Monotonic Counter LSB Register (LPSMCLR)

SNVS_LP General Purpose Register 0 (legacy alias) (LPGPR0_legacy_alias)

SNVS_LP General Purpose Registers 0 .. 3 (LPGPR0_alias - LPGPR3_alias)

SNVS_LP General Purpose Registers 0 .. 3 (LPGPR0 - LPGPR3)

SNVS_HP Version ID Register 1 (HPVIDR1)

SNVS_HP Version ID Register 2 (HPVIDR2)

Chapter 20: System Reset Controller (SRC)

Chip-specific SRC information

SRC Overview

Features

External Signals

Clocks

Top-level resets, power-up sequence and external supply integration

Reset and Power-up Flow

Finite-State Machine (FSM)

Power mode transitions

Power-On Reset and power sequencing

External POR using SRC_POR_B

Internal POR

Functional Description

Reset Control

Reset inputs and outputs

Reset Handling

POR (SRC_POR_B)

COLD RESET

Parallel Reset Requests

Boot Mode Control

BOOT_MODE Pin Latching

SRC Memory Map/Register Definition

SRC

SRC_SCR

SRC_SBMR1

SRC_SRSR

SRC_SBMR2

SRC_GPR1

SRC_GPR2

SRC_GPR3

SRC_GPR4

SRC_GPR5

SRC_GPR6

SRC_GPR7

SRC_GPR8

SRC_GPR9

SRC_GPR10

Chapter 21: Fusemap

Boot Fusemap

Lock Fusemap

Fusemap Descriptions Table

Chapter 22: On-Chip OTP Controller (OCOTP_CTRL)

Chip-specific OCOTP_CTRL information

Overview

Features

Clocks

Top-Level Symbol and Functional Overview

Operation

Shadow Register Reload

Fuse and Shadow register read

Fuse and Shadow Register Writes

Write Postamble

Fuse Shadow Memory Footprint

OTP Read/Write Timing Parameters

Hardware Visible Fuses

Behavior During Reset

Secure JTAG control

Fuse Map

OCOTP Memory Map/Register Definition

OCOTP register descriptions

OCOTP Memory map

OTP Controller Control Register (CTRL)

OTP Controller Control Register (CTRL_SET)

OTP Controller Control Register (CTRL_CLR)

OTP Controller Control Register (CTRL_TOG)

OTP Controller Timing Register (TIMING)

OTP Controller Write Data Register (DATA)

OTP Controller Write Data Register (READ_CTRL)

OTP Controller Read Data Register (READ_FUSE_DATA)

Sticky bit Register (SW_STICKY)

Software Controllable Signals Register (SCS)

Software Controllable Signals Register (SCS_SET)

Software Controllable Signals Register (SCS_CLR)

Software Controllable Signals Register (SCS_TOG)

OTP Controller CRC test address (CRC_ADDR)

OTP Controller CRC Value Register (CRC_VALUE)

OTP Controller Version Register (VERSION)

OTP Controller Timing Register (TIMING2)

Value of OTP Bank0 Word0 (Lock controls) (LOCK)

Value of OTP Bank0 Word1 (Configuration and Manufacturing Info.) (CFG0)

Value of OTP Bank0 Word2 (Configuration and Manufacturing Info.) (CFG1)

Value of OTP Bank0 Word3 (Configuration and Manufacturing Info.) (CFG2)

Value of OTP Bank0 Word4 (Configuration and Manufacturing Info.) (CFG3)

Value of OTP Bank0 Word5 (Configuration and Manufacturing Info.) (CFG4)

Value of OTP Bank0 Word6 (Configuration and Manufacturing Info.) (CFG5)

Value of OTP Bank0 Word7 (Configuration and Manufacturing Info.) (CFG6)

Value of OTP Bank1 Word0 (Memory Related Info.) (MEM0)

Value of OTP Bank1 Word1 (Memory Related Info.) (MEM1)

Value of OTP Bank1 Word2 (Memory Related Info.) (MEM2)

Value of OTP Bank1 Word3 (Memory Related Info.) (MEM3)

Value of OTP Bank1 Word4 (Memory Related Info.) (MEM4)

Value of OTP Bank1 Word5 (Analog Info.) (ANA0)

Value of OTP Bank1 Word6 (Analog Info.) (ANA1)

Value of OTP Bank1 Word7 (Analog Info.) (ANA2)

Value of OTP Bank2 Word0 (OTPMK Key) (OTPMK0)

Value of OTP Bank2 Word1 (OTPMK Key) (OTPMK1)

Value of OTP Bank2 Word2 (OTPMK Key) (OTPMK2)

Value of OTP Bank2 Word3 (OTPMK Key) (OTPMK3)

Value of OTP Bank2 Word4 (OTPMK Key) (OTPMK4)

Value of OTP Bank2 Word5 (OTPMK Key) (OTPMK5)

Value of OTP Bank2 Word6 (OTPMK Key) (OTPMK6)

Value of OTP Bank2 Word7 (OTPMK Key) (OTPMK7)

Shadow Register for OTP Bank3 Word0 (SRK Hash) (SRK0)

Shadow Register for OTP Bank3 Word1 (SRK Hash) (SRK1)

Shadow Register for OTP Bank3 Word2 (SRK Hash) (SRK2)

Shadow Register for OTP Bank3 Word3 (SRK Hash) (SRK3)

Shadow Register for OTP Bank3 Word4 (SRK Hash) (SRK4)

Shadow Register for OTP Bank3 Word5 (SRK Hash) (SRK5)

Shadow Register for OTP Bank3 Word6 (SRK Hash) (SRK6)

Shadow Register for OTP Bank3 Word7 (SRK Hash) (SRK7)

Value of OTP Bank4 Word0 (Secure JTAG Response Field) (SJC_RESP0)

Value of OTP Bank4 Word1 (Secure JTAG Response Field) (SJC_RESP1)

Value of OTP Bank4 Word2 (MAC Address) (MAC0)

Value of OTP Bank4 Word3 (MAC Address) (MAC1)

Value of OTP Bank4 Word4 (MAC Address) (MAC2)

Value of OTP Bank4 Word5 (CRC Key) (OTPMK_CRC32)

Value of OTP Bank4 Word6 (General Purpose Customer Defined Info) (GP1)

Value of OTP Bank4 Word7 (General Purpose Customer Defined Info) (GP2)

Value of OTP Bank5 Word0 (SW GP1) (SW_GP1)

Value of OTP Bank5 Word1 (SW GP2) (SW_GP20)

Value of OTP Bank5 Word2 (SW GP2) (SW_GP21)

Value of OTP Bank5 Word3 (SW GP2) (SW_GP22)

Value of OTP Bank5 Word4 (SW GP2) (SW_GP23)

Value of OTP Bank5 Word5 (Misc Conf) (MISC_CONF0)

Value of OTP Bank5 Word6 (Misc Conf) (MISC_CONF1)

Value of OTP Bank5 Word7 (SRK Revoke) (SRK_REVOKE)

Value of OTP Bank6 Word0 (ROM Patch) (ROM_PATCH0)

Value of OTP Bank6 Word1 (ROM Patch) (ROM_PATCH1)

Value of OTP Bank6 Word2 (ROM Patch) (ROM_PATCH2)

Value of OTP Bank6 Word3 (ROM Patch) (ROM_PATCH3)

Value of OTP Bank6 Word4 (ROM Patch) (ROM_PATCH4)

Value of OTP Bank6 Word5 (ROM Patch) (ROM_PATCH5)

Value of OTP Bank6 Word6 (ROM Patch) (ROM_PATCH6)

Value of OTP Bank6 Word7 (ROM Patch) (ROM_PATCH7)

Value of OTP Bank7 Word0 (GP3) (GP30)

Value of OTP Bank7 Word1 (GP3) (GP31)

Value of OTP Bank7 Word2 (GP3) (GP32)

Value of OTP Bank7 Word3 (GP3) (GP33)

Value of OTP Bank7 Word4 (GP4) (GP40)

Value of OTP Bank7 Word5 (GP4) (GP41)

Value of OTP Bank7 Word6 (GP4) (GP42)

Value of OTP Bank7 Word7 (GP4) (GP43)

Chapter 23-26: External Memory Interfaces and Controllers

Chapter 23: External Memory Controllers

Overview

Smart External Memory Controller (SEMC) Overview

eMMC/eSD/SDIO

Quad Serial Peripheral Interface

SIP 4M Flash Memory

Chapter 24: Smart External Memory Controller (SEMC)

Chip-specific SEMC information

About this module

Introduction

Features

Operation Modes

Block diagram

Signals

Memory Map and register definition

SEMC register descriptions

SEMC Memory map

Module Control Register (MCR)

IO Mux Control Register (IOCR)

Master Bus (AXI) Control Register 0 (BMCR0)

Master Bus (AXI) Control Register 1 (BMCR1)

Base Register 0 (For SDRAM CS0 device) (BR0)

Base Register 1 (For SDRAM CS1 device) (BR1)

Base Register 2 (For SDRAM CS2 device) (BR2)

Base Register 3 (For SDRAM CS3 device) (BR3)

Base Register 4 (For NAND device) (BR4)

Base Register 5 (For NOR device) (BR5)

Base Register 6 (For PSRAM device) (BR6)

Base Register 7 (For DBI-B (MIPI Display Bus Interface Type B) device) (BR7)

Base Register 8 (For NAND device) (BR8)

DLL Control Register (DLLCR)

Interrupt Enable Register (INTEN)

Interrupt Enable Register (INTR)

SDRAM control register 0 (SDRAMCR0)

SDRAM control register 1 (SDRAMCR1)

SDRAM control register 2 (SDRAMCR2)

SDRAM control register 3 (SDRAMCR3)

NAND control register 0 (NANDCR0)

NAND control register 1 (NANDCR1)

NAND control register 2 (NANDCR2)

NAND control register 3 (NANDCR3)

NOR control register 0 (NORCR0)

NOR control register 1 (NORCR1)

NOR control register 2 (NORCR2)

NOR control register 3 (NORCR3)

SRAM control register 0 (SRAMCR0)

SRAM control register 1 (SRAMCR1)

SRAM control register 2 (SRAMCR2)

SRAM control register 3 (SRAMCR3)

DBI-B control register 0 (DBICR0)

DBI-B control register 1 (DBICR1)

IP Command control register 0 (IPCR0)

IP Command control register 1 (IPCR1)

IP Command control register 2 (IPCR2)

IP Command register (IPCMD)

TX DATA register (for IP Command) (IPTXDAT)

RX DATA register (for IP Command) (IPRXDAT)

Status register 0 (STS0)

Status register 1 (STS1)

Status register 2 (STS2)

Status register 3 (STS3)

Status register 4 (STS4)

Status register 5 (STS5)

Status register 6 (STS6)

Status register 7 (STS7)

Status register 8 (STS8)

Status register 9 (STS9)

Status register 10 (STS10)

Status register 11 (STS11)

Status register 12 (STS12)

Status register 13 (STS13)

Status register 14 (STS14)

Status register 15 (STS15)

Functional description

Clocks

Reset

Pin Mux in SEMC

Device access by AXI Command

Device access by IP Command

SDRAM Controller Operations

SDRAM address map

SDRAM device access by IP Command

IP command - SDRAM Self Refresh

IP command - SDRAM Auto Refresh

IP command - SDRAM Mode Register Set

IP command - SDRAM Precharge

IP command - SDRAM Precharge ALL

IP command - SDRAM Active

IP command - SDRAM READ

IP command - SDRAM WRITE

SDRAM device access by AXI Command

SDRAM device read access by AXI Command

SDRAM device write access by AXI Command

SDRAM device pipelined access by AXI Command

SDRAM back-to-back access

SDRAM read-to-read access

SDRAM read-to-write access

SDRAM write-to-write access

SDRAM write-to-read access

Refresh command - SDRAM AUTO Refresh

SDRAM low power feature

Stop mode - SDRAM

BUS Idle - SDRAM

SDRAM Page Management

SDRAM Timers

Prescaler

Refresh interval timer

Urgent Refresh timer

Beat timer

ACTIVE to READ/WRITE timer

PRECHARGE to ACTIVE timer

CKE OFF timer

SELF REFRESH recover timer

AUTO REFRESH recover timer

Refresh to Refresh timer

ACTIVE to ACTIVE timer

ACTIVE to PRECHARGE timer

Write recovery timer

NAND Flash Controller Operations

NAND Flash address map

NAND Flash access address type

One Byte Column Address

Two Byte Column Address

One Byte Row Address

Two Byte Row Address

Three Byte Row Address

Five Byte Row/Column Address

NAND Flash access command type

Command Phase Only

Command + Wait Phase

Command + Address Phase

Command + Address + Wait Phase

Command + Address + Read Phase

Command + Address + Write Phase (For IP command)

Command + Read Phase

Command + Write Phase

Read Phase Only

Write Phase Only

Command + Address + Command + Read Phase

Command + Address + Write Phase (For AXI command)

NAND Flash read access EDO and non-EDO mode

NOR Flash Controller Operations

NOR Flash Read Operation in ASYNC Mode

NOR Flash Write Operation in ASYNC mode

NOR Flash Read Operation in SYNC mode

SRAM Controller Operations

SRAM Read Operation in ASYNC Mode

SRAM Write Operation in ASYNC mode

SRAM Read Operation in SYNC mode

SRAM Write Operation in SYNC mode

Display Bus Interface Controller Operations

Chapter 25: Ultra Secured Digital Host Controller (uSDHC)

Chip-specific uSDHC information

Overview

Features

Modes and Operations

Data transfer Modes

External Signals

Signals Overview

Clocks

Functional Description

Data Buffer

Write Operation Sequence

Read Operation Sequence

Data Buffer and Block Size

Dividing Large Data Transfer

DMA AHB Interface

Internal DMA Request

DMA Burst Length

AHB Master Interface

ADMA Engine

ADMA Concept and Descriptor Format

ADMA Interrupt

ADMA Error

Register Bank with IP Bus Interface

SD Protocol Unit

SD control misc

SD Clock control

Command control

Data control

Clock & Reset Manager

Clock Generator

SDIO Card Interrupt

Interrupts in 1-bit Mode

Interrupt in 4-bit Mode

Card Interrupt Handling

Card Insertion and Removal Detection

Power Management and Wake Up Events

Setting Wake Up Events

MMC fast boot

Boot operation

Alternative boot operation

Initialization/Application of uSDHC

Command Send & Response Receive Basic Operation

Card Identification Mode

Card Detect

Reset

Voltage Validation

Card Registry

Card Access

Block Write

Normal Write

DDR Write

Write with Pause

Block Read

Normal Read

DDR Read

Read with Pause

DLL (Delay Line) in Read Path

Suspend Resume

Suspend

Resume

ADMA Usage

Transfer Error

CRC Error

Internal DMA Error

Transfer ADMA Error

Auto CMD12 Error

Card Interrupt

Switch Function

Query, Enable and Disable SDIO High Speed Mode

Query, Enable and Disable SD High Speed Mode/SDR50/SDR104/DDR50

Query, Enable and Disable MMC High Speed Mode

Set MMC Bus Width

ADMA Operation

ADMA1 Operation

ADMA2 Operation

Fast Boot Operation

Normal fast boot flow

Alternative fast boot flow

Fast boot application case (in DMA mode)

Commands for MMC/SD/SDIO

Software Restrictions

Initialization Active

Software Polling Procedure

Suspend Operation

Data Length Setting

(A)DMA Address Setting

Data Port Access

Change Clock Frequency

Multi-block Read

uSDHC Memory Map/Register Definition

uSDHC register descriptions

uSDHC Memory map

DMA System Address (DS_ADDR)

Block Attributes (BLK_ATT)

Command Argument (CMD_ARG)

Command Transfer Type (CMD_XFR_TYP)

Command Response0 (CMD_RSP0)

Command Response1 (CMD_RSP1)

Command Response2 (CMD_RSP2)

Command Response3 (CMD_RSP3)

Data Buffer Access Port (DATA_BUFF_ACC_PORT)

Present State (PRES_STATE)

Protocol Control (PROT_CTRL)

System Control (SYS_CTRL)

Interrupt Status (INT_STATUS)

Interrupt Status Enable (INT_STATUS_EN)

Interrupt Signal Enable (INT_SIGNAL_EN)

Auto CMD12 Error Status (AUTOCMD12_ERR_STATUS)

Host Controller Capabilities (HOST_CTRL_CAP)

Watermark Level (WTMK_LVL)

Mixer Control (MIX_CTRL)

Force Event (FORCE_EVENT)

ADMA Error Status Register (ADMA_ERR_STATUS)

ADMA System Address (ADMA_SYS_ADDR)

DLL (Delay Line) Control (DLL_CTRL)

DLL Status (DLL_STATUS)

CLK Tuning Control and Status (CLK_TUNE_CTRL_STATUS)

Vendor Specific Register (VEND_SPEC)

MMC Boot Register (MMC_BOOT)

Vendor Specific 2 Register (VEND_SPEC2)

Tuning Control Register (TUNING_CTRL)

Chapter 26: FlexSPI Controller

Chip-specific FlexSPI information

Master ID allocation

Introduction

Features

Block diagram

Operation Modes

Glossary for FlexSPI module

External Signal Description

Memory Map and register definition

Register Access

FlexSPI register descriptions

FlexSPI Memory map

Module Control Register 0 (MCR0)

Module Control Register 1 (MCR1)

Module Control Register 2 (MCR2)

AHB Bus Control Register (AHBCR)

Interrupt Enable Register (INTEN)

Interrupt Register (INTR)

LUT Key Register (LUTKEY)

LUT Control Register (LUTCR)

AHB RX Buffer 0 Control Register 0 (AHBRXBUF0CR0)

AHB RX Buffer 1 Control Register 0 (AHBRXBUF1CR0)

AHB RX Buffer 2 Control Register 0 (AHBRXBUF2CR0)

AHB RX Buffer 3 Control Register 0 (AHBRXBUF3CR0)

Flash a Control Register 0 (FLSHA1CR0 - FLSHB2CR0)

Flash a Control Register 1 (FLSHA1CR1 - FLSHB2CR1)

Flash a Control Register 2 (FLSHA1CR2 - FLSHB2CR2)

Flash Control Register 4 (FLSHCR4)

IP Control Register 0 (IPCR0)

IP Control Register 1 (IPCR1)

IP Command Register (IPCMD)

IP RX FIFO Control Register (IPRXFCR)

IP TX FIFO Control Register (IPTXFCR)

DLL Control Register 0 (DLLACR - DLLBCR)

Status Register 0 (STS0)

Status Register 1 (STS1)

Status Register 2 (STS2)

AHB Suspend Status Register (AHBSPNDSTS)

IP RX FIFO Status Register (IPRXFSTS)

IP TX FIFO Status Register (IPTXFSTS)

IP RX FIFO Data Register a (RFDR0 - RFDR31)

IP TX FIFO Data Register a (TFDR0 - TFDR31)

LUT a (LUT0 - LUT63)

AHB Memory Map definition

AHB Memory Map for Serial Flash memory access

AHB Memory Map for IP RX FIFO read access

AHB Memory Map for IP TX FIFO write access

Functional description

Clocks

Interrupts

Flash Connection

Flash Access mode

SPI clock mode

Flash Individual mode and Parallel mode

SDR mode and DDR mode

Single, Dual, Quad, Octal mode

Flash memory map

Flash address sent to Device

Look Up Table

Programmable Sequence Engine

Instruction execution on SPI interface

Flash access sequence example

Flash access by IP Command

Reading Data from IP RX FIFO

Filling Data to IP TX FIFO

Flash access by AHB Command

AHB write access to Flash

AHB read access to Flash

AHB RX Buffer Management

Command Arbitration

Command Abort and Suspend

SCK stop feature

FlexSPI Output Timing

Output timing between Data and SCK

Output timing between Chip selection and SCK

FlexSPI Input Timing

RX Clock Source Features

Input timing for sampling with dummy read strobe

Input timing for sampling with flash provided read strobe

DLL configuration for sampling

Execute-In-Place Enhance mode

Application information

FlexSPI Initialization

Overview of Error Flags

Application on Serial NOR Flash device

Write Enable command

Write Registers command

Page Program command

Read Status 1 command

Read command

Fast Read command

Dual IO Fast Read command

Quad IO Fast Read command

DDR Quad IO Fast Read command

Application on HyperBus device

HyperFlash

HyperRAM

Application on Serial NAND Flash device

Application on FPGA device

Chapter 27-31: ARM Core Platform

Chapter 27: ARM Cortex M7 Platform

Chip-specific Arm Cortex M7 information

ARM Cortex M7 Platform

Overview

Block Diagram

External Signals

Clocks

Chapter 28: Network Interconnect Bus System (NIC-301)

Chip-specific NIC-301 information

Overview

NIC-301 Main Features

Modes and Operations

External Signals

Memory Map and Register Definition

Chapter 29: On-Chip RAM Memory Controller (OCRAM)

Chip-specific OCRAM information

Overview

Basic Functions

Read/Write Arbitration

Advanced Features

Read Data Wait State

Read Address Pipeline

Write Data Pipeline

Write Address Pipeline

Programmable Registers

Chapter 30: FlexRAM

Chip-specific FlexRAM information

Overview

Introduction

Features

Block diagram

Functional description

Interface Conversion

RAM Bank Allocation

Low power modes

Clocks

Reset

Interrupts

Memory Map and register definition

FLEXRAM register descriptions

FLEXRAM Memory map

TCM CRTL Register (TCM_CTRL)

Interrupt Status Register (INT_STATUS)

Interrupt Status Enable Register (INT_STAT_EN)

Interrupt Enable Register (INT_SIG_EN)

Chapter 31: AHB to IP Bridge (AIPSTZ)

Chip-specific AIPSTZ information

Overview

Features

Clocks

Functional Description

Access Protections

Access Support

Initialization Information

Security Block

AIPSTZ Memory Map/Register Definition

AIPSTZx

AIPSTZx_MPR

AIPSTZx_OPACR

AIPSTZx_OPACR1

AIPSTZx_OPACR2

AIPSTZx_OPACR3

AIPSTZx_OPACR4

Chapter 32-35: Display and Camera

Chapter 32: Display and Camera Overview

Display and Camera Overview

PiXel Processing Pipeline

LCD Interface

CMOS Sensor Interface

Chapter 33: CMOS Sensor Interface (CSI)

Chip-specific CSI information

Overview

External Signals

Clocks

Principles of Operation

Data Transfer with the Embedded DMA Controllers

Gated Clock Mode

Non-Gated Clock Mode

CCIR656 Interlace Mode

CCIR656 Progressive Mode

Error Correction for CCIR656 Coding

Interrupt Generation

Start Of Frame Interrupt (SOF_INT)

End Of Frame Interrupt (EOF_INT)

Change Of Field Interrupt (COF_INT)

CCIR Error Interrupt (ECC_INT)

RxFIFO Full Interrupt (RxFF_INT)

Statistic FIFO Full Interrupt (STATFF_INT)

RxFIFO Overrun Interrupt (RFF_OR_INT)

Statistic FIFO Overrun Interrupt (SFF_OR_INT)

Frame Buffer1 DMA Transfer Done Interrupt (DMA_TSF_DONE_FB1)

Frame Buffer2 DMA Transfer Done Interrupt (DMA_TSF_DONE_FB2)

Statistic FIFO DMA Transfer Done Interrupt (DMA_TSF_DONE_SFF)

AHB Bus Response Error Interrupt (HRESP_ERR_INT)

Data Packing Style

STAT FIFO Path

CSI Memory Map/Register Definition

CSI

CSI_CSICR1

CSI_CSICR2

CSI_CSICR3

CSI_CSISTATFIFO

CSI_CSIRFIFO

CSI_CSIRXCNT

CSI_CSISR

CSI_CSIDMASA_STATFIFO

CSI_CSIDMATS_STATFIFO

CSI_CSIDMASA_FB1

CSI_CSIDMASA_FB2

CSI_CSIFBUF_PARA

CSI_CSIIMAG_PARA

CSI_CSICR18

CSI_CSICR19

Chapter 34: Enhanced LCD Interface (eLCDIF)

Chip-specific eLCDIF information

Overview

External Signals

Clocks

Functional Description

Bus Interface Mechanisms

Bus Master Operation in Write/Display Modes

System Bus Master Performance

DMA Operation in MPU Read Mode

Write Data Path

LCDIF Interrupts

Initializing the LCDIF

Write Modes

DOTCLK Interface

Code Example

LUT

Panel Interface Generator (Pigeon Mode)

LCDIF Pin Usage by Interface Mode

Behavior During Reset

LCDIF Memory Map/Register Definition

LCDIF

LCDIF_CTRLn

LCDIF_CTRL1n

LCDIF_CTRL2n

LCDIF_TRANSFER_COUNT

LCDIF_CUR_BUF

LCDIF_NEXT_BUF

LCDIF_VDCTRL0n

LCDIF_VDCTRL1

LCDIF_VDCTRL2

LCDIF_VDCTRL3

LCDIF_VDCTRL4

LCDIF_BM_ERROR_STAT

LCDIF_CRC_STAT

LCDIF_STAT

LCDIF_PIGEONCTRL0n

LCDIF_PIGEONCTRL1n

LCDIF_PIGEONCTRL2n

LCDIF_PIGEONn

LCDIF_PIGEONn

LCDIF_PIGEONn

LCDIF_LUT_CTRL

LCDIF_LUT0_ADDR

LCDIF_LUT0_DATA

LCDIF_LUT1_ADDR

LCDIF_LUT1_DATA

Chapter 35: Pixel Pipeline (PXP)

Chip-specific PXP information

Overview

Clocks

Top-level architecture

Processing Details

Scaling Operation

Decimation Image Scaling

Bilinear Image Scaling Filter

YUV 4:2:2 Image Scaling

YUV 4:2:0 Image Scaling

RGB/YUV444 Image Scaling

Color Space Conversion (CSC)

CSC1 Operation

YUV versus YCbCr Support

Alpha Blending/Color Key

Alpha Blend

Porter-Duff Alpha Blend

Color Key

Rotation

Output Buffer

Address calculator

Block size selection

Interlaced Video Support

LCDIF Handshake

LCDIF Abort

Theory of Operation

Pixel Handling

Output Buffer Composition

PS Image Processing

Letterboxing

Clipping source images

Color Key Processing

In Place Processing (PS buffer is destination buffer)

Alpha Surface (AS) Processing

Alpha Handling

Color Key Processing (AS_CTRL)

Output Image Processing

Output Image Size

Output Format

Rotation/Flip operations

Queuing PXP transactions

Error Handling

Known PXP Limitations/Issues

PXP Memory Map/Register Definition

PXP

PXP_CTRLn

PXP_STATn

PXP_OUT_CTRLn

PXP_OUT_BUF

PXP_OUT_BUF2

PXP_OUT_PITCH

PXP_OUT_LRC

PXP_OUT_PS_ULC

PXP_OUT_PS_LRC

PXP_OUT_AS_ULC

PXP_OUT_AS_LRC

PXP_PS_CTRLn

PXP_PS_BUF

PXP_PS_UBUF

PXP_PS_VBUF

PXP_PS_PITCH

PXP_PS_BACKGROUND

PXP_PS_SCALE

PXP_PS_OFFSET

PXP_PS_CLRKEYLOW

PXP_PS_CLRKEYHIGH

PXP_AS_CTRL

PXP_AS_BUF

PXP_AS_PITCH

PXP_AS_CLRKEYLOW

PXP_AS_CLRKEYHIGH

PXP_CSC1_COEF0

PXP_CSC1_COEF1

PXP_CSC1_COEF2

PXP_POWER

PXP_NEXT

PXP_PORTER_DUFF_CTRL

Chapter 36-39: Audio

Chapter 36: Audio Overview

Audio Overview

Audio Module Overview

Medium Quality Sound (MQS)

Synchronous Audio Interface (SAI)

Sony/Philips Digital Interface (SPDIF)

Chapter 37: Synchronous Audio Interface (SAI)

Chip-specific SAI information

Introduction

Features

Block diagram

Modes of operation

External signals

Functional description

SAI clocking

SAI resets

Synchronous modes

Frame sync configuration

Data FIFO

Data alignment

FIFO pointers

FIFO packing

FIFO Combine

Word mask register

Interrupts and DMA requests

FIFO request flag

FIFO warning flag

FIFO error flag

Sync error flag

Word start flag

Memory map and register definition

I2S Register Descriptions

I2S Memory Map

Version ID (VERID)

Parameter (PARAM)

SAI Transmit Control (TCSR)

SAI Transmit Configuration 1 (TCR1)

SAI Transmit Configuration 2 (TCR2)

SAI Transmit Configuration 3 (TCR3)

SAI Transmit Configuration 4 (TCR4)

SAI Transmit Configuration 5 (TCR5)

SAI Transmit Data (TDRa)

SAI Transmit FIFO (TFRa)

SAI Transmit Mask (TMR)

SAI Receive Control (RCSR)

SAI Receive Configuration 1 (RCR1)

SAI Receive Configuration 2 (RCR2)

SAI Receive Configuration 3 (RCR3)

SAI Receive Configuration 4 (RCR4)

SAI Receive Configuration 5 (RCR5)

SAI Receive Data (RDRa)

SAI Receive FIFO (RFRa)

SAI Receive Mask (RMR)

Chapter 38: Medium Quality Sound (MQS)

Chip-specific MQS information

Overview

Block Diagram

External Signals

Interface Signals

Programming Considerations

Usage Model

Chapter 39: Sony/Philips Digital Interface (SPDIF)

Chip-specific SPDIF information

Overview

External Signals

Clocks

Functional Description

SPDIF Receiver

Audio Data Reception

Application Note

Channel Status Reception

Channel Status Interrupt

User Bit Reception

Validity Flag Reception

SPDIF Receiver Interrupt Exception Definition

Standards Compliance

SPDIF PLOCK Detection and Rxclk Output

Measuring Frequency of SPDIF_RxClk

SPDIF Transmitter

Audio Data Transmission

Channel Status Transmission

Validity Flag Transmission

SPDIF Memory Map/Register Definition

SPDIF

SPDIF_SCR

SPDIF_SRCD

SPDIF_SRPC

SPDIF_SIE

SPDIF_SIS

SPDIF_SIC

SPDIF_SRL

SPDIF_SRR

SPDIF_SRCSH

SPDIF_SRCSL

SPDIF_SRU

SPDIF_SRQ

SPDIF_STL

SPDIF_STR

SPDIF_STCSCH

SPDIF_STCSCL

SPDIF_SRFM

SPDIF_STC

Chapter 40-42: Connectivity

Chapter 40: 10/100-Mbps Ethernet MAC (ENET)

Chip-specific ENET information

Introduction

Overview

Features

Ethernet MAC features

IP protocol performance optimization features

IEEE 1588 features

Block diagram

External Signals

Clocks

Memory map/register definition

ENETx

ENETx_EIR

ENETx_EIMR

ENETx_RDAR

ENETx_TDAR

ENETx_ECR

ENETx_MMFR

ENETx_MSCR

ENETx_MIBC

ENETx_RCR

ENETx_TCR

ENETx_PALR

ENETx_PAUR

ENETx_OPD

ENETx_TXIC

ENETx_RXIC

ENETx_IAUR

ENETx_IALR

ENETx_GAUR

ENETx_GALR

ENETx_TFWR

ENETx_RDSR

ENETx_TDSR

ENETx_MRBR

ENETx_RSFL

ENETx_RSEM

ENETx_RAEM

ENETx_RAFL

ENETx_TSEM

ENETx_TAEM

ENETx_TAFL

ENETx_TIPG

ENETx_FTRL

ENETx_TACC

ENETx_RACC

ENETx_RMON_T_DROP

ENETx_RMON_T_PACKETS

ENETx_RMON_T_BC_PKT

ENETx_RMON_T_MC_PKT

ENETx_RMON_T_CRC_ALIGN

ENETx_RMON_T_UNDERSIZE

ENETx_RMON_T_OVERSIZE

ENETx_RMON_T_FRAG

ENETx_RMON_T_JAB

ENETx_RMON_T_COL

ENETx_RMON_T_P64

ENETx_RMON_T_P65TO127

ENETx_RMON_T_P128TO255

ENETx_RMON_T_P256TO511

ENETx_RMON_T_P512TO1023

ENETx_RMON_T_P1024TO2047

ENETx_RMON_T_P_GTE2048

ENETx_RMON_T_OCTETS

ENETx_IEEE_T_DROP

ENETx_IEEE_T_FRAME_OK

ENETx_IEEE_T_1COL

ENETx_IEEE_T_MCOL

ENETx_IEEE_T_DEF

ENETx_IEEE_T_LCOL

ENETx_IEEE_T_EXCOL

ENETx_IEEE_T_MACERR

ENETx_IEEE_T_CSERR

ENETx_IEEE_T_SQE

ENETx_IEEE_T_FDXFC

ENETx_IEEE_T_OCTETS_OK

ENETx_RMON_R_PACKETS

ENETx_RMON_R_BC_PKT

ENETx_RMON_R_MC_PKT

ENETx_RMON_R_CRC_ALIGN

ENETx_RMON_R_UNDERSIZE

ENETx_RMON_R_OVERSIZE

ENETx_RMON_R_FRAG

ENETx_RMON_R_JAB

ENETx_RMON_R_RESVD_0

ENETx_RMON_R_P64

ENETx_RMON_R_P65TO127

ENETx_RMON_R_P128TO255

ENETx_RMON_R_P256TO511

ENETx_RMON_R_P512TO1023

ENETx_RMON_R_P1024TO2047

ENETx_RMON_R_P_GTE2048

ENETx_RMON_R_OCTETS

ENETx_IEEE_R_DROP

ENETx_IEEE_R_FRAME_OK

ENETx_IEEE_R_CRC

ENETx_IEEE_R_ALIGN

ENETx_IEEE_R_MACERR

ENETx_IEEE_R_FDXFC

ENETx_IEEE_R_OCTETS_OK

ENETx_ATCR

ENETx_ATVR

ENETx_ATOFF

ENETx_ATPER

ENETx_ATCOR

ENETx_ATINC

ENETx_ATSTMP

ENETx_TGSR

ENETx_TCSRn

ENETx_TCCRn

Functional description

Ethernet MAC frame formats

Pause Frames

Magic packets

IP and higher layers frame format

Ethernet types

IPv4 datagram format

IPv6 datagram format

Internet Control Message Protocol (ICMP) datagram format

User Datagram Protocol (UDP) datagram format

TCP datagram format

IEEE 1588 message formats

Transport encapsulation

UDP/IP

Native Ethernet (PTPv2)

PTP header

PTPv1 header

PTPv2 header

MAC receive

Collision detection in half-duplex mode

Preamble processing

MAC address check

Unicast address check

Multicast and unicast address resolution

Broadcast address reject

Miss-bit implementation

Frame length/type verification: payload length check

Frame length/type verification: frame length check

VLAN frames processing

Pause frame termination

CRC check

Frame padding removal

MAC transmit

Frame payload padding

MAC address insertion

CRC-32 generation

Inter-packet gap (IPG)

Collision detection and handling — half-duplex operation only

Full-duplex flow control operation

Remote device congestion

Local device/FIFO congestion

Magic packet detection

Sleep mode

Magic packet detection

Wakeup

IP accelerator functions

Checksum calculation

Additional padding processing

32-bit Ethernet payload alignment

Receive processing

Transmit processing

Received frame discard

IPv4 fragments

IPv6 support

Receive processing

Transmit processing

Resets and stop controls

Hardware reset

Soft reset

Hardware freeze

Graceful stop

Graceful transmit stop (GTS)

Graceful receive stop (GRS)

Graceful stop interrupt (GRA)

IEEE 1588 functions

Adjustable timer module

Adjustable timer implementation

Timer Synchronization for Multi-Port Implementations

Transmit timestamping

Receive timestamping

Time synchronization

Input Capture and Output Compare

Input capture

Output compare

DMA requests

FIFO thresholds

Receive FIFO

Transmit FIFO

Loopback options

Legacy buffer descriptors

Legacy receive buffer descriptor

Legacy transmit buffer descriptor

Enhanced buffer descriptors

Enhanced receive buffer descriptor

Enhanced transmit buffer descriptor

Client FIFO application interface

Data structure description

Data structure examples

Frame status

FIFO protection

Transmit FIFO underflow

Transmit FIFO overflow

Receive FIFO overflow

PHY management interface

MDIO clause 22 frame format

MDIO clause 45 frame format

MDIO clock generation

MDIO operation

Ethernet interfaces

RMII interface

MII Interface — transmit

Transmit with collision — half-duplex

MII interface — receive

Interrupt coalescence

Interrupt coalescence setup

Updating the frame count threshold on-the-fly

Updating the timer threshold on-the-fly

Chapter 41: Universal Serial Bus Controller (USB)

Chip-specific USB information

Overview

Features

Modes of Operation

Normal Mode

Low-Power Mode

External Signals

Functional Description

USB 2.0 Controller Core 0/1

Host Mode

Peripheral (Device) Mode

USB Power Control

Entering Low Power Suspend Mode

Wake-Up Events

Host Mode Events

Interrupts

USB Core Interrupts

USB Wake-Up Interrupts

USB Operation Model

Register Interface

Configuration, Control and Status Register Set

Identification Registers

OTG Operations

Host Data Structures

Periodic Frame List

Asynchronous List Queue Head Pointer

Isochronous (High-Speed) Transfer Descriptor (iTD)

Next Link Pointer

iTD Transaction Status and Control List

iTD Buffer Page Pointer List (Plus)

Split Transaction Isochronous Transfer Descriptor (siTD)

Next Link Pointer

siTD Endpoint Capabilities/Characteristics

siTD Transfer State

siTD Buffer Pointer List (plus)

siTD Back Link Pointer

Queue element transfer descriptor (qTD)

Next qTD Pointer

Alternate Next qTD Pointer

qTD Token

qTD Buffer Page Pointer List

Queue Head

Queue Head Horizontal Link Pointer

Queue Head Endpoint Capabilities/Characteristics

Transfer Overlay-Queue Head

Periodic Frame Span Traversal Node (FSTN)

FSTN Normal Path Pointer

FSTN Back Path Link Pointer

Host Operational Model

Host Controller Initialization

Port Routing and Control

Port Routing Control through EHCI Configured (CF) Bit

Port Routing Control through PortOwner and Disconnect Event

Example Port Routing State Machine

EHCI HC Owner

Companion HC Owner

Port Power

Port Reporting Over-Current

Suspend/Resume-Host Operational Model

Port Suspend/Resume

Schedule Traversal Rules

Example - Preserving Micro-Frame Integrity

Transaction Fit - A Best-Fit Approximation Algorithm

Periodic Schedule Frame Boundaries vs Bus Frame Boundaries

Periodic Schedule

Managing Isochronous Transfers Using iTDs

Host Controller Operational Model for iTDs

Software Operational Model for iTDs

Periodic scheduling threshold

Asynchronous Schedule

Adding Queue Heads to Asynchronous Schedule

Removing Queue Heads from Asynchronous Schedule

Empty Asynchronous Schedule Detection

Restarting Asynchronous Schedule Before EOF

Example Method for Restarting Asynchronous Schedule Traversal

Async Sched Not Active

Async Sched Active

Async Sched Sleeping

Example Derivation for AsyncSchedSleepTime

Asynchronous schedule traversal: Start Event

Reclamation Status Bit (USBSTS Register)

Operational Model for Nak Counter

Nak Count Reload Control

Wait for List Head

Do Reload

Wait for Start Event

Managing Control/Bulk/Interrupt Transfers through Queue Heads

Fetch Queue Head

Advance Queue

Execute Transaction

Interrupt Transfer Pre-condition Criteria

Asynchronous Transfer Pre-operations and Pre-condition Criteria

Transfer Type Independent Pre-operations

Halting a Queue Head

Asynchronous Schedule Park Mode

Write Back qTD

Follow Queue Head Horizontal Pointer

Buffer Pointer List Use for Data Streaming with qTDs

Adding Interrupt Queue Heads to the Periodic Schedule

Managing Transfer Complete Interrupts from Queue Heads

Ping Control

Split Transactions

Split Transactions for Asynchronous Transfers

Asynchronous - Do Start Split

Asynchronous - Do Complete Split

Split Transaction Interrupt

Split Transaction Scheduling Mechanisms for Interrupt

Host Controller Operational Model for FSTNs

Software Operational Model for FSTNs

Tracking Split Transaction Progress for Interrupt Transfers

Split Transaction Execution State Machine for Interrupt

Rebalancing the periodic schedule

Split Transaction Isochronous

Split Transaction Scheduling Mechanisms for Isochronous

Tracking Split Transaction Progress for Isochronous Transfers

Split Transaction Execution State Machine for Isochronous

Periodic Isochronous - Do Start Split

Periodic Isochronous - Do Complete Split

Complete-Split for Scheduling Boundary Cases 2a, 2b

Split Transaction for Isochronous - Processing Examples

Host Controller Pause

Port Test Modes -Host Operational Model

Interrupts-Host Operational Model

Transfer/Transaction Based Interrupts

Transaction Error

Serial Bus Babble

Data Buffer Error

USB Interrupt (Interrupt on Completion (IOC))

Short Packet

Host Controller Event Interrupts

Port Change Events

Frame List Rollover

Interrupt on Async Advance

Host System Error

EHCI Deviation

Embedded Transaction Translator Function

Capability Registers

Operational Registers

Discovery-EHCI Deviation

Data Structures

Operational Model

Micro- frame Pipeline

Split State Machines

Asynchronous Transaction Scheduling and Buffer Management

USB 2.0 - 11.17.3

USB 2.0 - 11.17.4

Periodic Transaction Scheduling and Buffer Management

USB 2.0 - 11.18.6.[1-2]

USB 2.0 - 11.18.[7-8]

Multiple Transaction Translators

Device Operation

USB_USBMODE Register

Non-Zero Fields the Register File

SOF Interrupt

Embedded Design Interface

Frame Adjust Register

Miscellaneous variations from EHCI

Programmable Physical Interface Behaviour

Discovery

Port Reset

Port Speed Detection

Port Test Mode

Device Data Structures

Endpoint Queue Head (dQH)

Endpoint Capabilities/Characteristics

Transfer Overlay-Endpoint Queue Head

Current dTD Pointer

Set-up Buffer

Endpoint Transfer Descriptor (dTD)

Device Operational Model

Device Controller Initialization

Port State and Control

Bus Reset

Suspend/Resume

Suspend

Resume

Managing Endpoints

Endpoint Initialization

Stalling

Data Toggle

Data Toggle Reset

Data Toggle Inhibit

Priming Transmit Endpoints

Priming Receive Endpoints

Operational Model For Packet Transfers

Interrupt/Bulk Endpoint Operational Model

Interrupt/Bulk Endpoint Bus Response Matrix

Control Endpoint Operation Model

Setup Phase

Data Phase

Status Phase

Control Endpoint Bus Response Matrix

Isochronous Endpoint Operational Model

Isochronous Pipe Synchronization

Isochronous Endpoint Bus Response Matrix

Managing Queue Heads

Queue Head Initialization

Operational Model For Setup Transfers

Managing Transfers with Transfer Descriptors

Software Link Pointers

Building a Transfer Descriptor

Executing A Transfer Descriptor

Transfer Completion

Flushing/De-priming an Endpoint

Device Error Matrix

Servicing Interrupts

High-Frequency Interrupts

Low-Frequency Interrupts

Error Interrupts

USB Non-Core Memory Map/Register Definition

USBNC

USBNC_USB_OTG1_CTRL

USBNC_USB_OTG2_CTRL

USBNC_USB_OTG1_PHY_CTRL_0

USBNC_USB_OTG2_PHY_CTRL_0

USB Core Memory Map/Register Definition

USB

USB_nID

USB_nHWGENERAL

USB_nHWHOST

USB_nHWDEVICE

USB_nHWTXBUF

USB_nHWRXBUF

USB_nGPTIMER0LD

USB_nGPTIMER0CTRL

USB_nGPTIMER1LD

USB_nGPTIMER1CTRL

USB_nSBUSCFG

USB_nCAPLENGTH

USB_nHCIVERSION

USB_nHCSPARAMS

USB_nHCCPARAMS

USB_nDCIVERSION

USB_nDCCPARAMS

USB_nUSBCMD