运放参数的详细解释——输入偏置电流 bI 和输入失调电流 osI

1、输入偏置电流 bI :实际的运放,会有电流流入(datasheet 中 bI 为负)或流出(datasheet

中 bI 为正)运放的输入端(与理想运放虚断的概念不一样),这两个输入端电流的平均值就

是输入偏置电流。

2、输入失调电流 osI :流入或流出运放输入端正极和负极偏置电流的差。

3、运放的输入级采用差分输入的双极型晶体管 Bipolar 时, bI 来源于输入级三极管的基极

电流。当采用场效应管 FET 时, bI 来源于差分输入端的一对 ESD 保护二极管的漏电流(栅

极电流很小,一般会在 fA 级)。

4、Bipolar 输入的运放输入偏置电流 bI 比较大,可达 uA 级。比较好的 CMOS 运放输入偏置

电流和输入失调电流可以做到小于 1pA 的目标。

5、要使 FET 输入偏置电流 bI 最小,要把共模电压设置在

CC V

V 处。

SS

2

6、输入偏置电流 bI 会流经外面的电阻网络,转化成运放的失调电压,再经过运放后到达运

放的输出端,造成运放的输入误差。

7、许多运放的输入失调电流会随着温度的变化而变化,甚至在 100℃的输入偏置电流 bI 是

25℃的几百倍,如果设计的系统在很宽的温度范围内工作,这一因素不得不考虑。

8、参数举例:

OPA642

当

VCM

0 时

V

bI =25uA

OPA842

当

VCM

0 时

V

bI =-35uA

osI =0.5uA

osI = 1 uA

�

运放参数的详细解释和分析——输入失调电压 osV 及温漂

1、输入失调电压 osV :当输入信号为 0 时,为了使运放的输出电压等于 0,必须在运放两个

输入端加一个小的电压,这个小电压就是 osV 。

2、运放的输入失调电压 osV 来源于运放差分输入级两个管子的不匹配。

3、输入失调电压 osV 会随着温度的变化而变化,即温漂。一大批运放的 osV 是符合正态分布

的。输入失调电压 osV 还随着时间的推移而变化,就是运放输入失调电压的长期漂移。

4、参数举例:

OPA642

Vos

5.1

mV

温漂 4uV/℃

OPA842

Vos

3.0

mV

温漂 4uV/℃

�

运放参数的详细解释和分析——运放噪声快速计算

1、运放构成的反向放大电路中,噪声主要来源于三个方面:

a:运放的输入电压噪声

ne

b:运放的输入电流噪声 ni

c:设置放大倍数的电阻 R1 和 Rf 的热噪声,可以通过经典公式算出来。很多情况下会成为

主要噪声来源。

2、运放的噪声带宽,datasheet 中给出的运放噪声参数一般为谱密度值如

1.1

nV /

Hz

,需

要对它在噪声带宽中进行积分才可以得到噪声的 RMS 电压值。

3、运放的输入电压噪声和输入电流噪声,与频率有关。在极低频率时(0.1Hz~10Hz)主要

是 1/f 噪声,以后主要是白噪声。

A:1/f 噪声。在低频条件下,噪声频谱密度会以 3dB/倍频程上升,功率频谱密度在此区域

内与频率成反比,所以电压和电流噪声频谱密度与频率的平方根成反比。因此,这种噪声通

常称为“1/f”噪声,或者使用“闪烁噪声”旧术语。这种噪声开始增加时的频率称为“1/f

转折频率”FC,该频率越小越好。最佳低频率、低噪声放大器的转折频率位于 1~10Hz 范围

内,而 JTET 器件和更为通用的运放则位于 1~100Hz 范围内。不过,超高速放大器的转折频

率相当高,可达数百 Hz,甚至 1~2kHz。

B:白噪声。指功率谱密度在整个频域内均匀分布的噪声。

4、参数举例:

OPA642

转折频率 1~10KHz

输入电压噪声密度

7.2

nV /

Hz

输入偏置电流噪声密度

8.2

pA/

Hz

OPA842

转折频率 10~100KHz

输入电压噪声密度

6.2

nV /

Hz

输入偏置电流噪声密度

7.2

pA/

Hz

�

运放参数的详细解释和分析——电源抑制比 DC-PSRR

1、电源抑制比 PSRR:当运放的电源电压发生变化时,会引起输入失调电压 osV 的变化,这

两个变化的比就是 PSRR。通常用 dB 表示:

PSRR

20

lg(

V

CC

V

ios

)

有些数据手册中,也会用失调电压对电源变化的比来表示,单位一般是 uV/V。

2、参数实例:

OPA642

OPA842

PSR=85dB

PSRR=90dB

when

VS

5.5~5.4

V

�

运发参数的详细解释和分析——电源抑制比 AC-PSRR

1、交流电源抑制比 AC-PSRR:实际的应用电路中,运放的电源电压可能是不变的,但是会

存在一定频率,一定幅度的纹波。PSRR 随电源交流频率的上升而下降,并且正负电源的

AC-PSRR 不同。

2、通常,运放的应用电路使用线性电源对运发供电,对运放的电源进行滤波。但某些情况

下,当使用开关电源时,其频率往往超过 100KHz,在这个频率点上,运放的 PSRR 能力下

降的非常快。

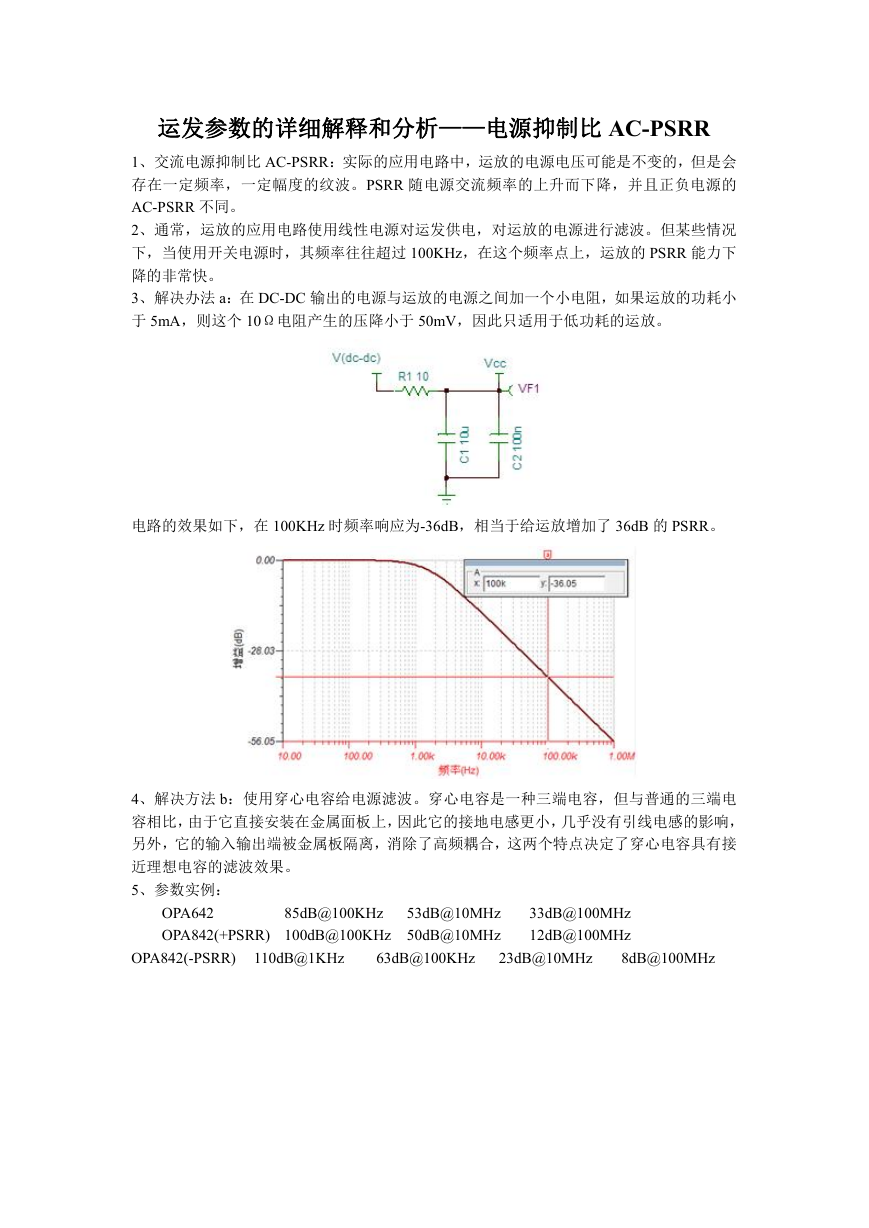

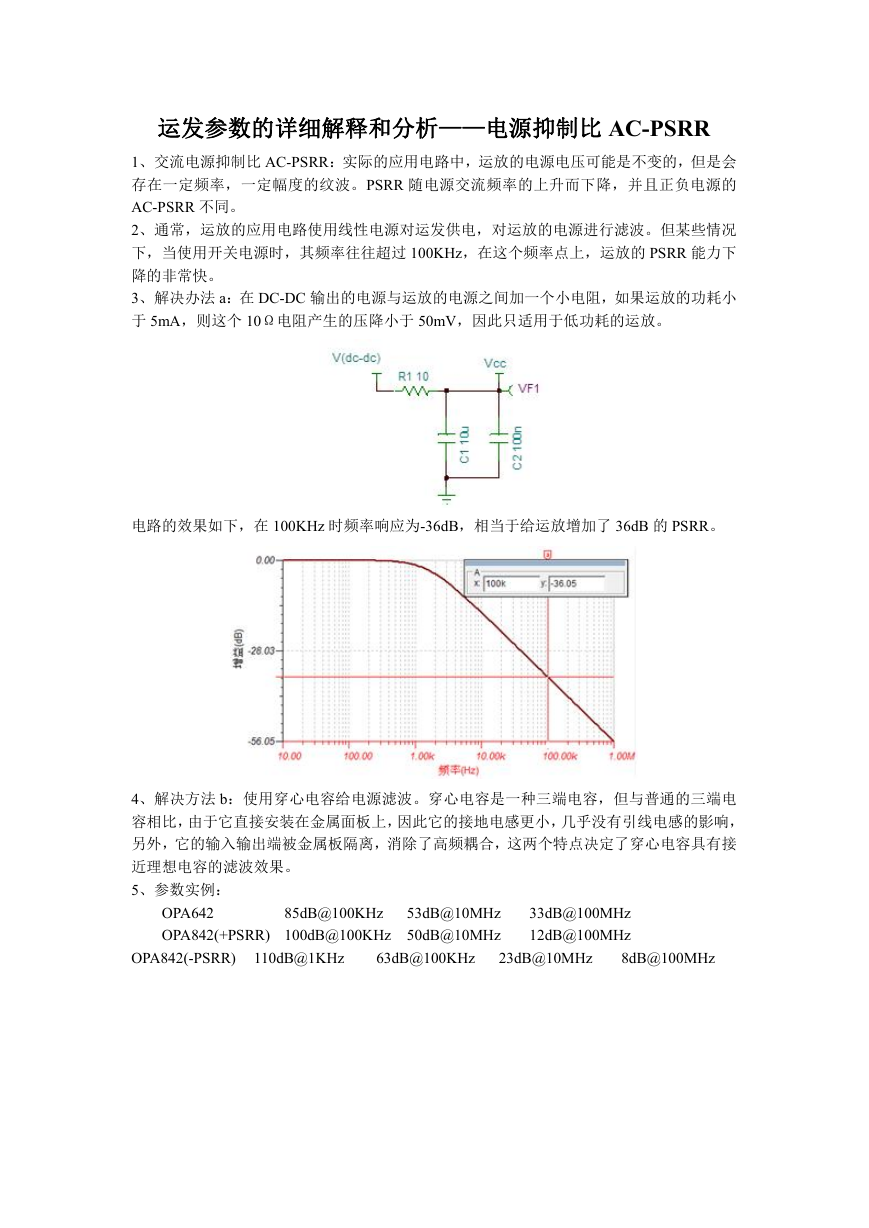

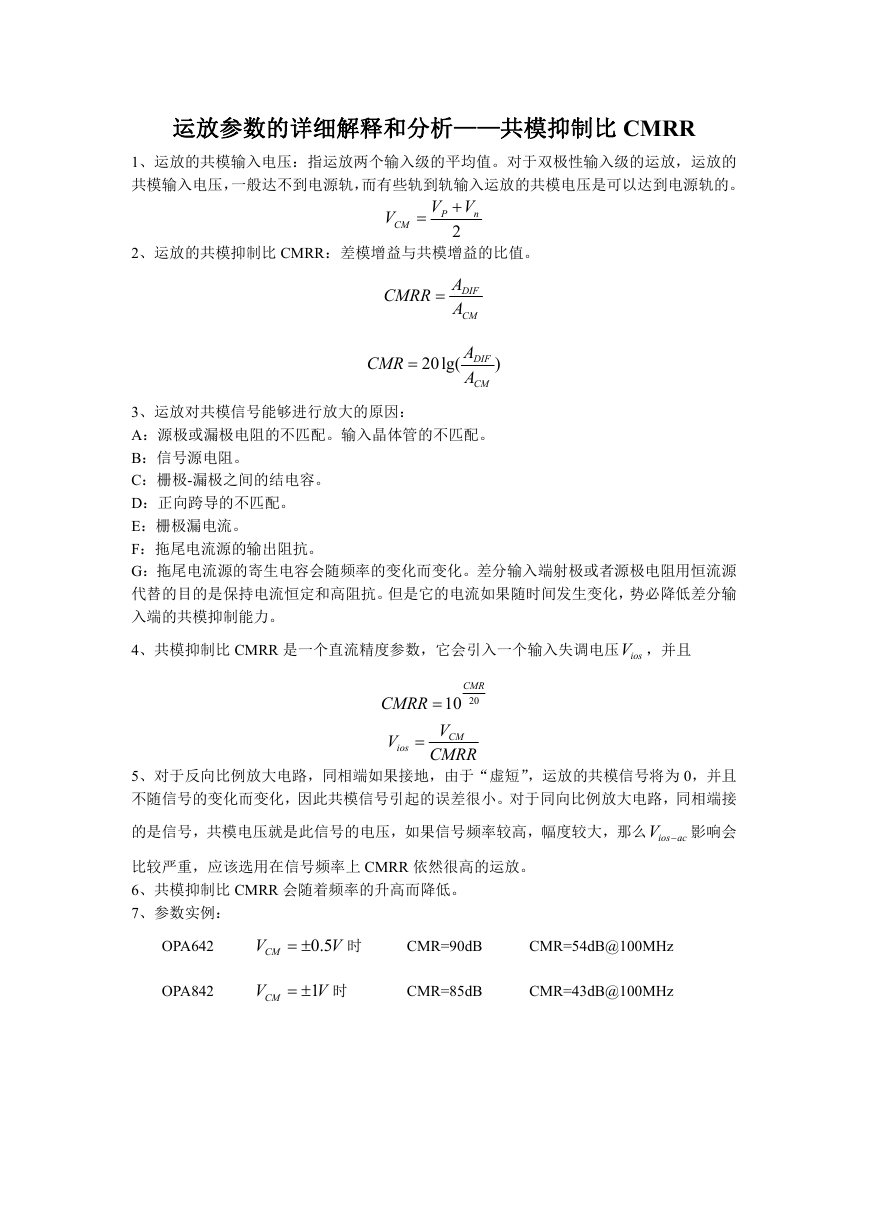

3、解决办法 a:在 DC-DC 输出的电源与运放的电源之间加一个小电阻,如果运放的功耗小

于 5mA,则这个 10Ω电阻产生的压降小于 50mV,因此只适用于低功耗的运放。

电路的效果如下,在 100KHz 时频率响应为-36dB,相当于给运放增加了 36dB 的 PSRR。

4、解决方法 b:使用穿心电容给电源滤波。穿心电容是一种三端电容,但与普通的三端电

容相比,由于它直接安装在金属面板上,因此它的接地电感更小,几乎没有引线电感的影响,

另外,它的输入输出端被金属板隔离,消除了高频耦合,这两个特点决定了穿心电容具有接

近理想电容的滤波效果。

5、参数实例:

85dB@100KHz

OPA642

OPA842(+PSRR) 100dB@100KHz

53dB@10MHz

50dB@10MHz

33dB@100MHz

12dB@100MHz

OPA842(-PSRR)

110dB@1KHz

63dB@100KHz

23dB@10MHz

8dB@100MHz

�

运放参数的详细解释和分析——共模抑制比 CMRR

1、运放的共模输入电压:指运放两个输入级的平均值。对于双极性输入级的运放,运放的

共模输入电压,一般达不到电源轨,而有些轨到轨输入运放的共模电压是可以达到电源轨的。

2、运放的共模抑制比 CMRR:差模增益与共模增益的比值。

V

P

V

CM

V

n

2

CMRR

A

DIF

A

CM

CMR

20

lg(

A

DIF

A

CM

)

3、运放对共模信号能够进行放大的原因:

A:源极或漏极电阻的不匹配。输入晶体管的不匹配。

B:信号源电阻。

C:栅极-漏极之间的结电容。

D:正向跨导的不匹配。

E:栅极漏电流。

F:拖尾电流源的输出阻抗。

G:拖尾电流源的寄生电容会随频率的变化而变化。差分输入端射极或者源极电阻用恒流源

代替的目的是保持电流恒定和高阻抗。但是它的电流如果随时间发生变化,势必降低差分输

入端的共模抑制能力。

4、共模抑制比 CMRR 是一个直流精度参数,它会引入一个输入失调电压 iosV ,并且

CMR

20

10

CMRR

V

CM

CMRR

V

ios

5、对于反向比例放大电路,同相端如果接地,由于“虚短”,运放的共模信号将为 0,并且

不随信号的变化而变化,因此共模信号引起的误差很小。对于同向比例放大电路,同相端接

的是信号,共模电压就是此信号的电压,如果信号频率较高,幅度较大,那么 ac

iosV 影响会

比较严重,应该选用在信号频率上 CMRR 依然很高的运放。

6、共模抑制比 CMRR 会随着频率的升高而降低。

7、参数实例:

OPA642

VCM

5.0

V

时

CMR=90dB

CMR=54dB@100MHz

OPA842

VCM

1

V

时

CMR=85dB

CMR=43dB@100MHz

�

运放参数的详细解释和分析——放大电路直流误差

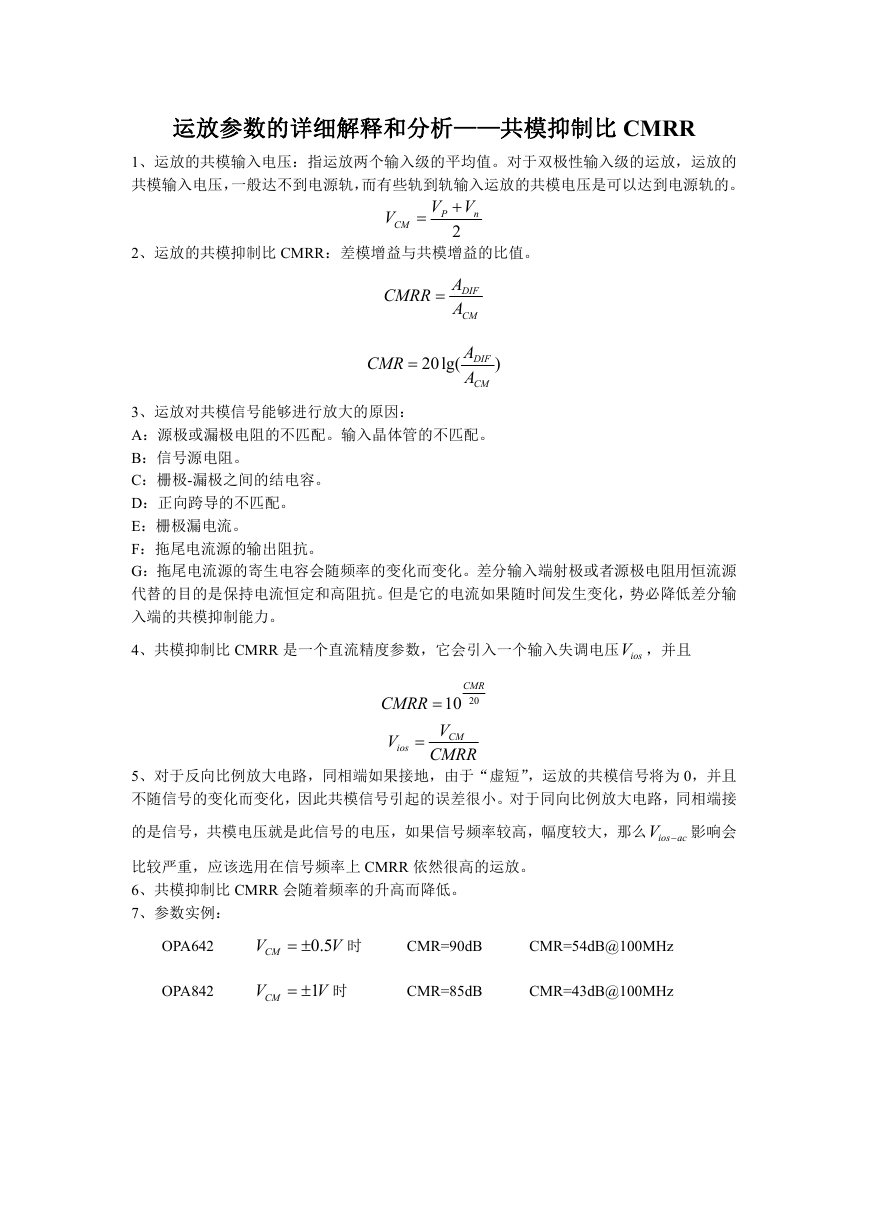

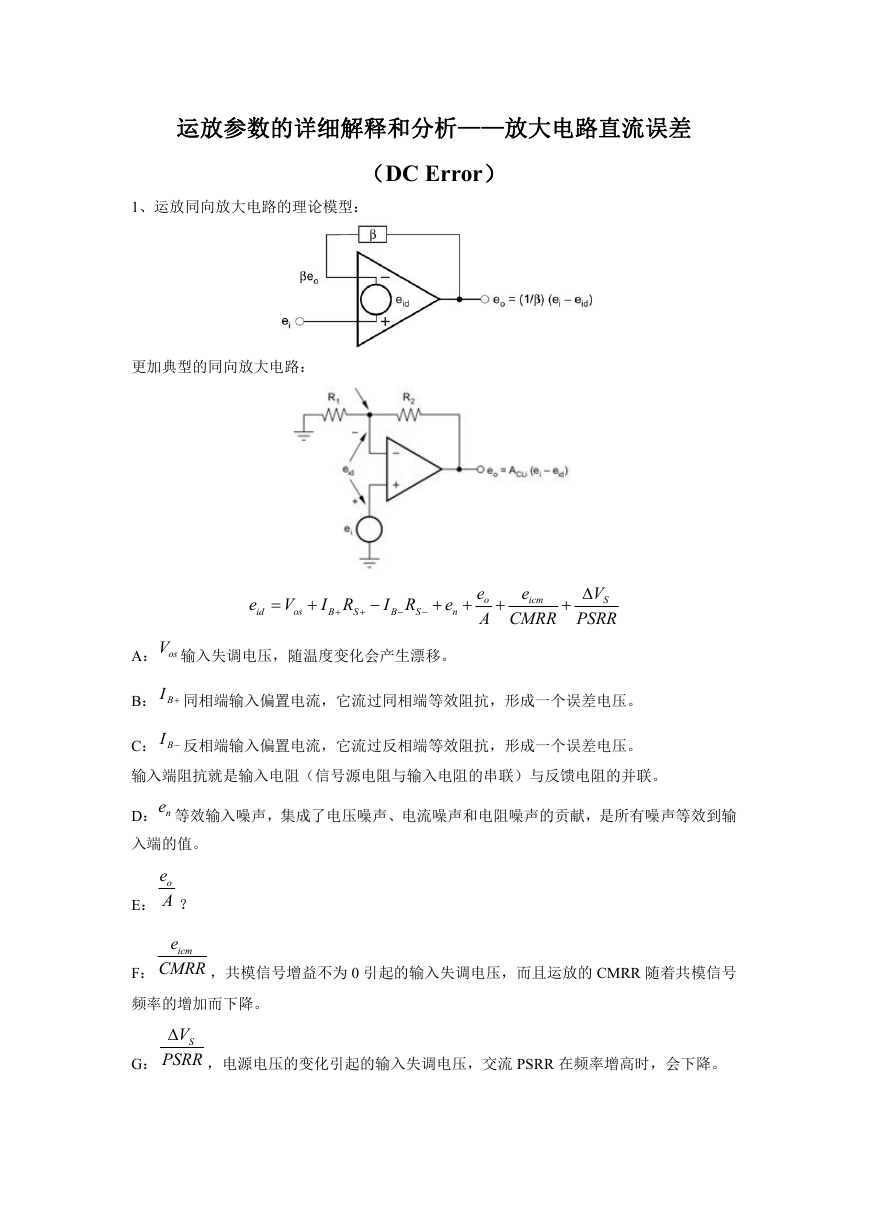

1、运放同向放大电路的理论模型:

(DC Error)

更加典型的同向放大电路:

e

id

V

os

RI

B

S

RI

B

S

e

n

e

o

A

e

icm

CMRR

V

S

PSRR

A: osV 输入失调电压,随温度变化会产生漂移。

B: BI 同相端输入偏置电流,它流过同相端等效阻抗,形成一个误差电压。

C: BI 反相端输入偏置电流,它流过反相端等效阻抗,形成一个误差电压。

输入端阻抗就是输入电阻(信号源电阻与输入电阻的串联)与反馈电阻的并联。

D: ne 等效输入噪声,集成了电压噪声、电流噪声和电阻噪声的贡献,是所有噪声等效到输

入端的值。

eo

E: A

?

eicm

F: CMRR

频率的增加而下降。

,共模信号增益不为 0 引起的输入失调电压,而且运放的 CMRR 随着共模信号

VS

G: PSRR

,电源电压的变化引起的输入失调电压,交流 PSRR 在频率增高时,会下降。

�

运算参数的详细解释和分析——输入阻抗和输入电容

1、对于电压反馈型运放,输入阻抗主要由输入级决定,一般双极型晶体管运放的共模输入

阻抗会大于 40MΩ,差模输入阻抗大于 200GΩ,对于 JFET 和 CMOS 输入级的运放,输入

阻抗更大,并且阻抗通常表现为电阻性。

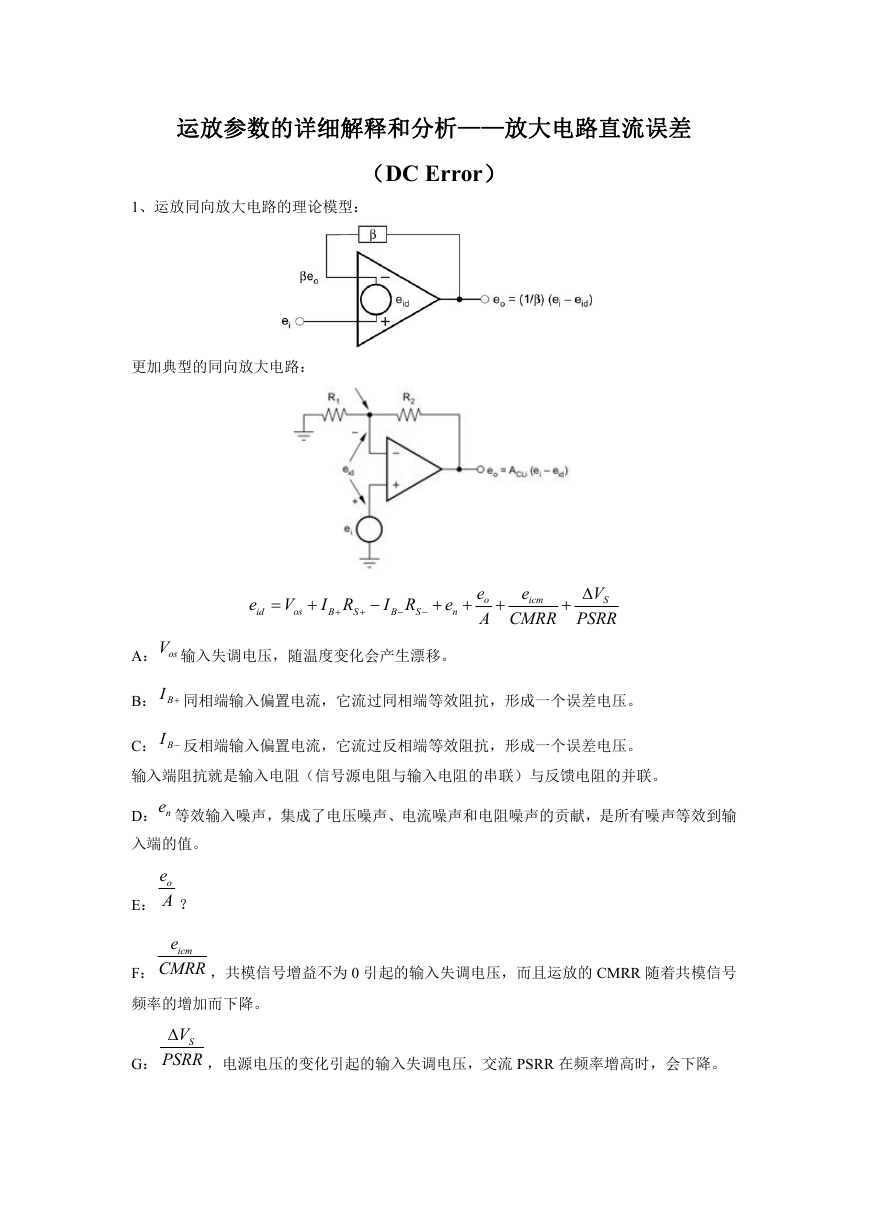

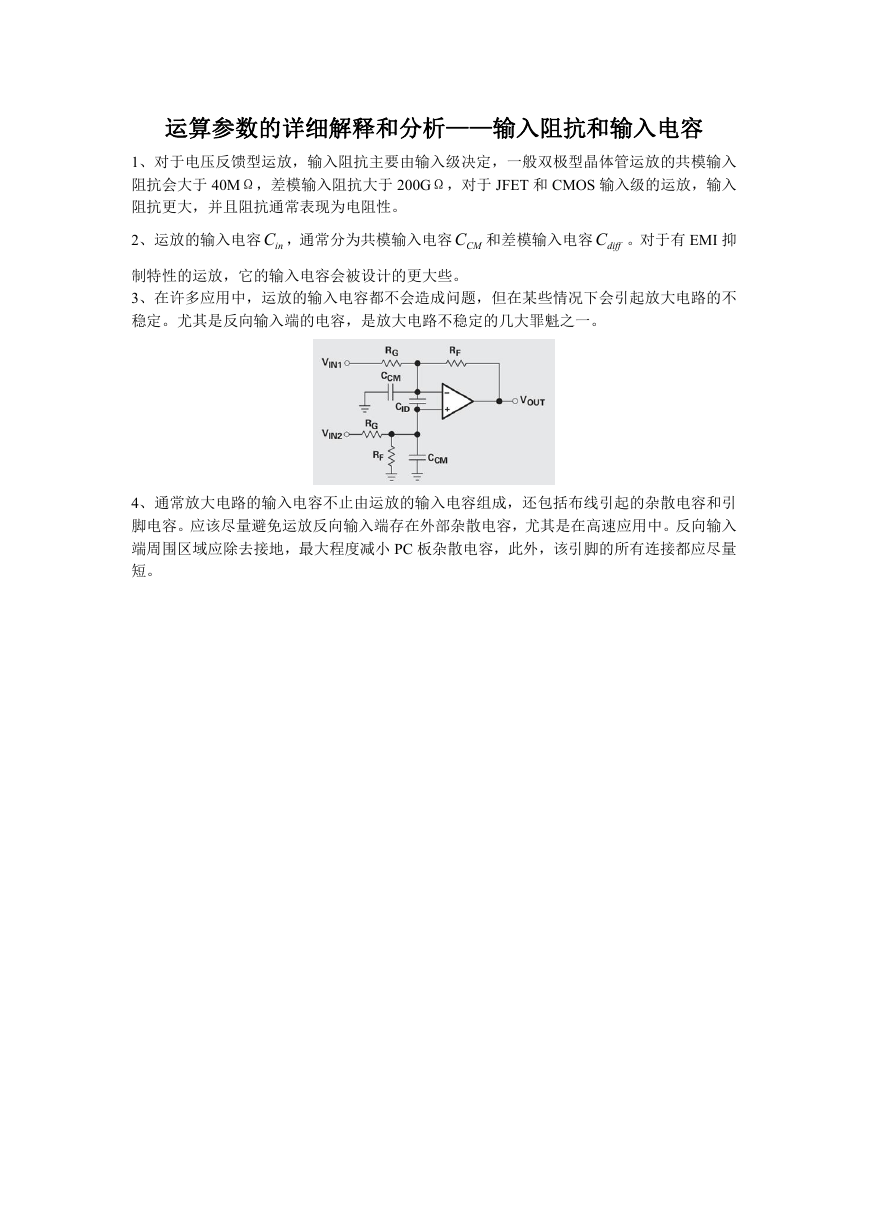

2、运放的输入电容 inC ,通常分为共模输入电容 CMC 和差模输入电容 diffC 。对于有 EMI 抑

制特性的运放,它的输入电容会被设计的更大些。

3、在许多应用中,运放的输入电容都不会造成问题,但在某些情况下会引起放大电路的不

稳定。尤其是反向输入端的电容,是放大电路不稳定的几大罪魁之一。

4、通常放大电路的输入电容不止由运放的输入电容组成,还包括布线引起的杂散电容和引

脚电容。应该尽量避免运放反向输入端存在外部杂散电容,尤其是在高速应用中。反向输入

端周围区域应除去接地,最大程度减小 PC 板杂散电容,此外,该引脚的所有连接都应尽量

短。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc