AN 575: PCI Express-DDR2 SDRAM

参考设计

引言

本应用手册将介绍在 Arria® II GX FPGA 硬件中实现专用 PCI Express 逻辑模块,内容包括:

Arria II GX 器件中 PCI Express MegaCore® 的硬核 IP 实现

DDR2 SDRAM 高性能控制器

PCI Express 协议

利用 Quartus® II 软件实现 PCI Express MegaCore

利用 ModelSim® 软件验证多 IP 模块

PCI Express 是一种点对点高速串行 I/O 接口,其为元件提供了极高效率的通信能力。该设计符合

《PCI Express 基本规范(2.0 修订版)》。

本设计在如下器件之间提供了一种接口样例:

使用 PCI Express 协议驱动 Arria II GX FPGA 指令的器件(Root Complex)

Arria II GX FPGA (endpoint)

外部 DDR2 SDRAM 存储器

Altera® PCI Express-DDR2 参考设计是连接 Altera PCI Express MegaCore 模块典型用户应用的一个

例子。

概述

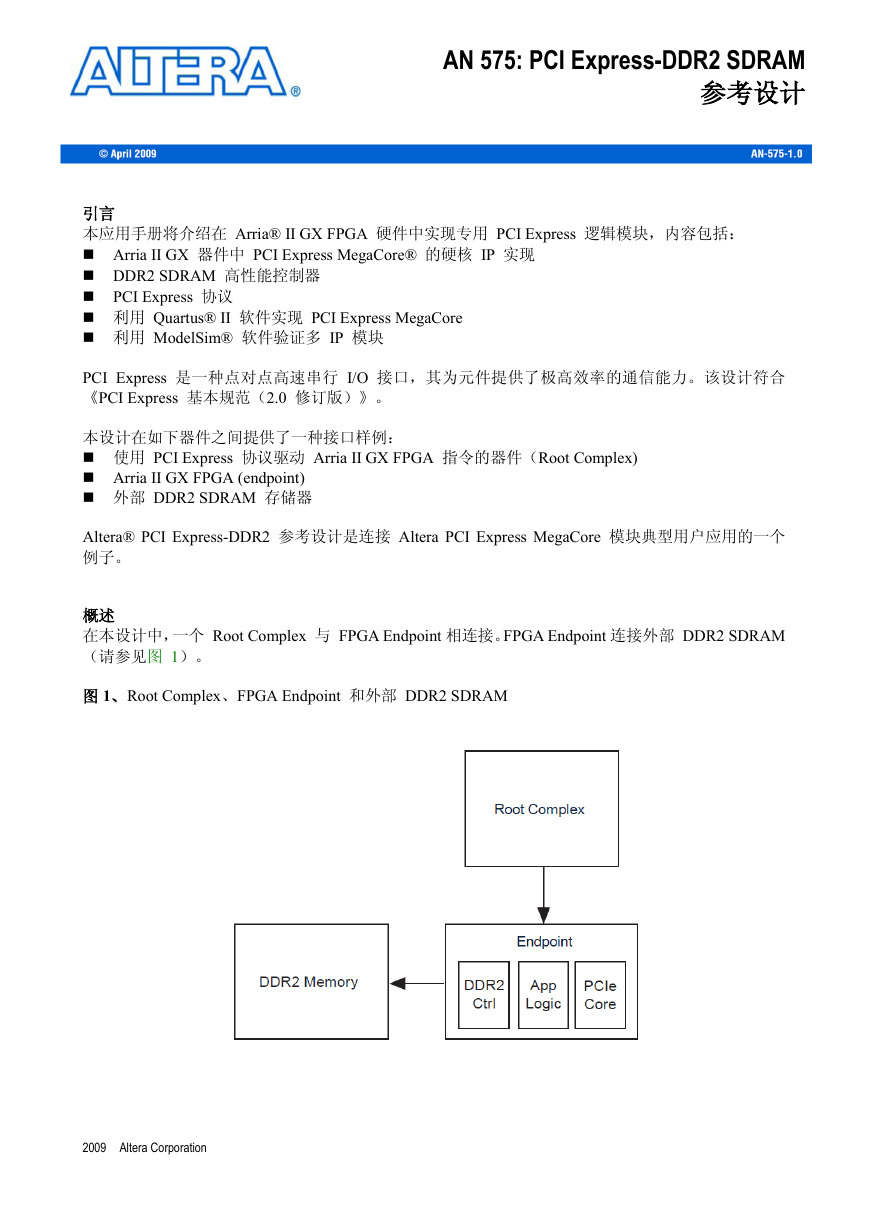

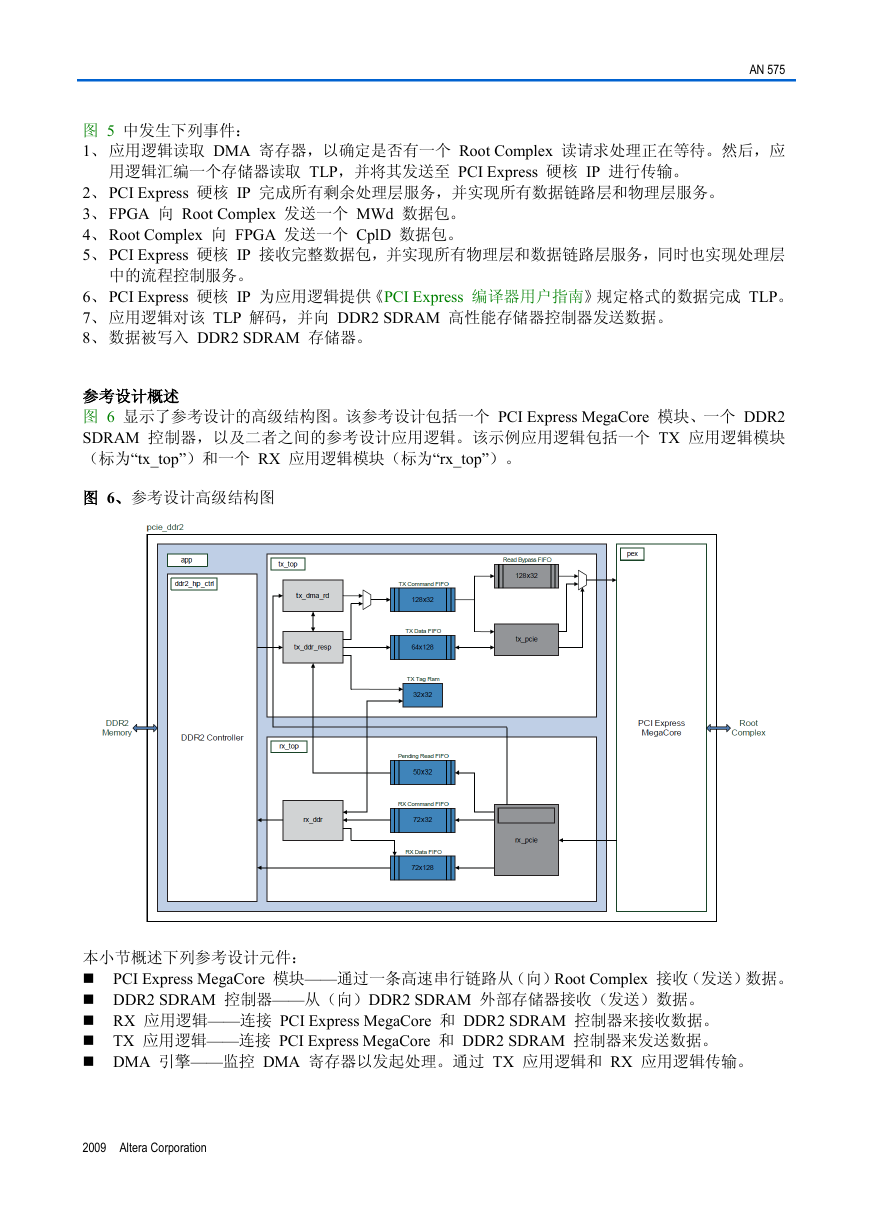

在本设计中,一个 Root Complex 与 FPGA Endpoint 相连接。FPGA Endpoint 连接外部 DDR2 SDRAM

(请参见图 1)。

图 1、Root Complex、FPGA Endpoint 和外部 DDR2 SDRAM

2009 Altera Corporation

�

AN 575

该参考设计在 FPGA 上实现 Endpoint,其包括如下模块:

连接 Root Complex 的一个 PCI Express MegaCore

连接 DDR2 SDRAM 存储器的 DDR2 SDRAM 高性能存储器控制器

连接 PCI Express MegaCore 和 DDR2 SDRAM 高性能存储器控制器的逻辑

Root Complex 在 PCI Express 链路上向 Endpoint 发出读写指令。Endpoint 也可以通过直接存储器访

问 (DMA) 读写来开始 Root Complex 读写。这是通过读写处理来实现的。

处理类型

从一个器件向另一个器件发送数据包时开始处理工作。一个数据包由报头和数据组成。报头包含处理

类型、所含数据以及其它数据包相关详细信息。数据就是元件之间传输的信息。本例中,组件为 Root

Complex、endpoint 和 DDR2 SDRAM。本例中的数据包为处理层数据包 (TLP)。

本参考设计将对下列 TLP 进行处理:

存储器读取请求 (MRd)

存储器写入请求 (MWr)

数据完成 (CplD)

发起器件可以向目标器件发送一个 MRd,该目标器件返回一个 CplD,其中包含请求的数据。发起器

件还可以发送一个包含数据的 MWr。

在 Root 端口和 FPGA Endpoint 之间的 PCI Express 链路上发起如下四种类型的处理。

Root Complex 发起的存储器写入处理

Root Complex 发起的存储器读取处理

Endpoint 发起的 DMA 写入处理

Endpoint 发起的 DMA 读取处理

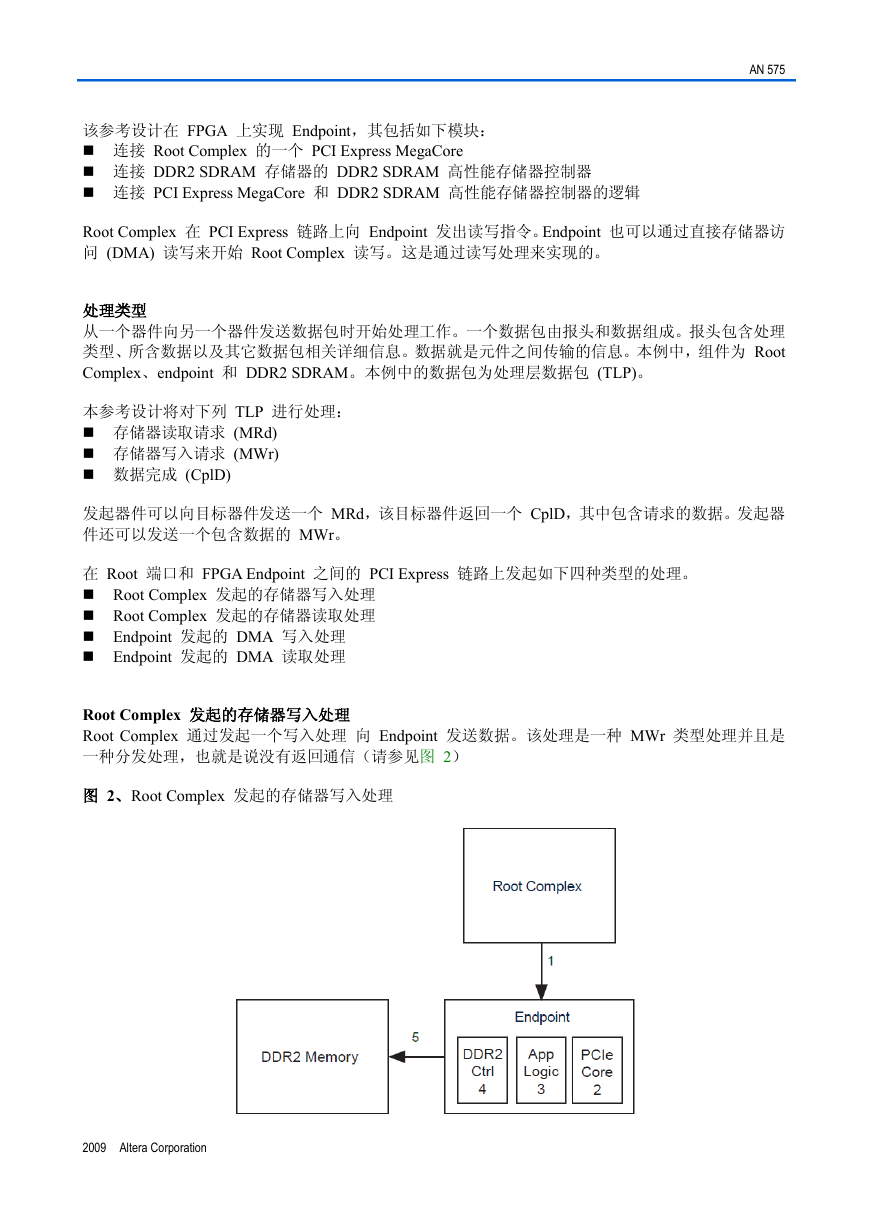

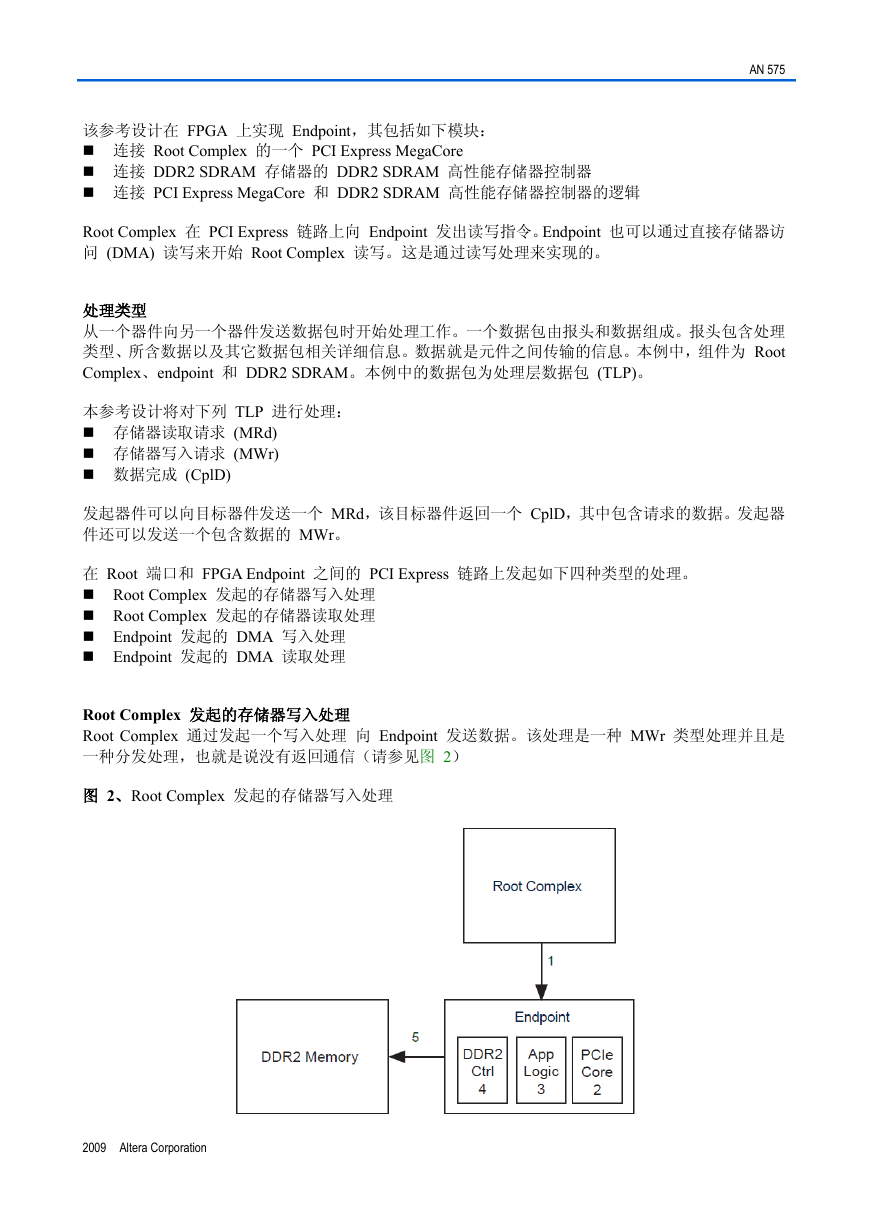

Root Complex 发起的存储器写入处理

Root Complex 通过发起一个写入处理 向 Endpoint 发送数据。该处理是一种 MWr 类型处理并且是

一种分发处理,也就是说没有返回通信(请参见图 2)

图 2、Root Complex 发起的存储器写入处理

2009 Altera Corporation

�

AN 575

图 2 中发生了下列事件:

1、 Root Complex 向 FPGA 发送 MWr 处理。

2、 PCI Express 硬核 IP 接收数据包,并实现所有物理层和数据链路层服务,同时还实现处理层中的

数据流控制服务。

3、 PCI Express 硬核 IP 为应用逻辑提供《PCI Express 编译器用户指南》规定格式的 TLP。

4、 应用逻辑对 TLP 解码,并向 DDR2 SDRAM 高性能存储器控制器发送数据。

5、 数据被写入 DDR2 SDRAM 存储器。

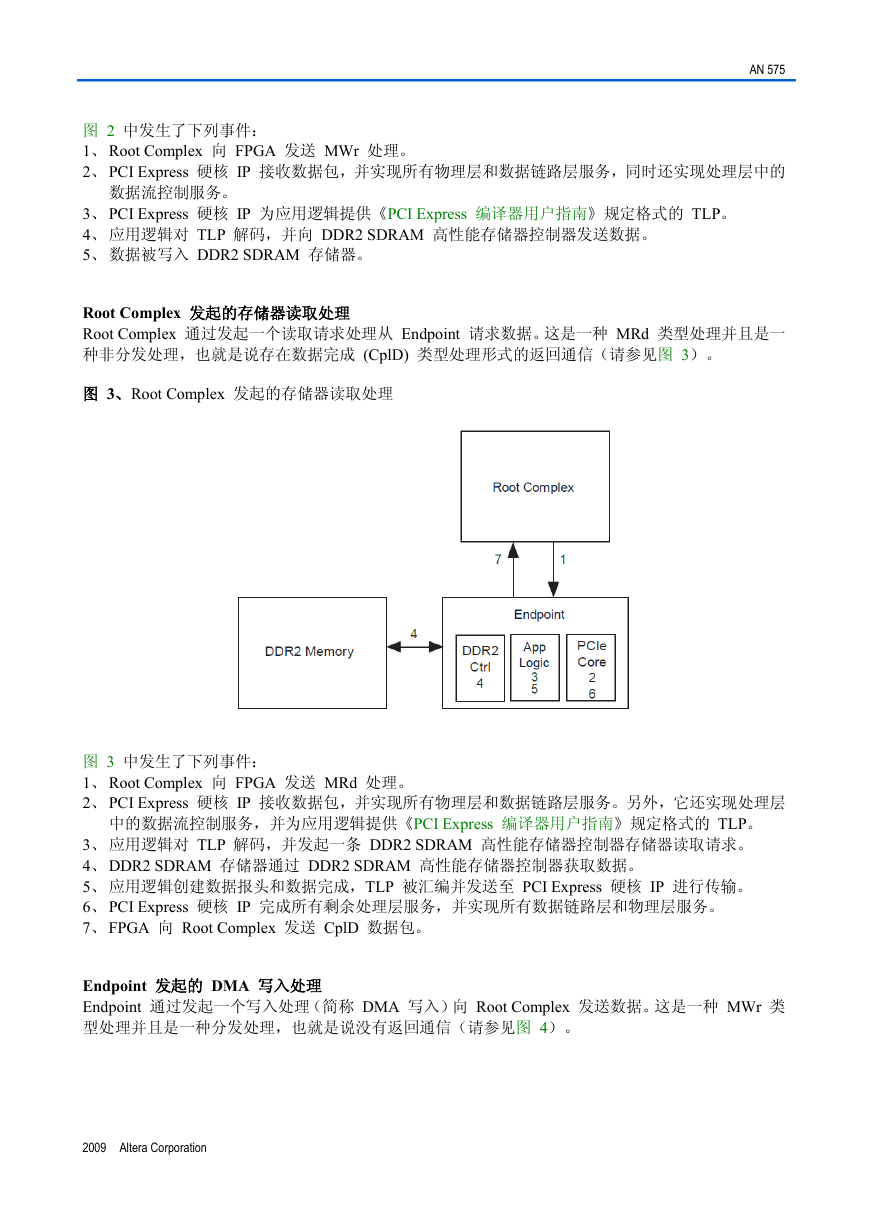

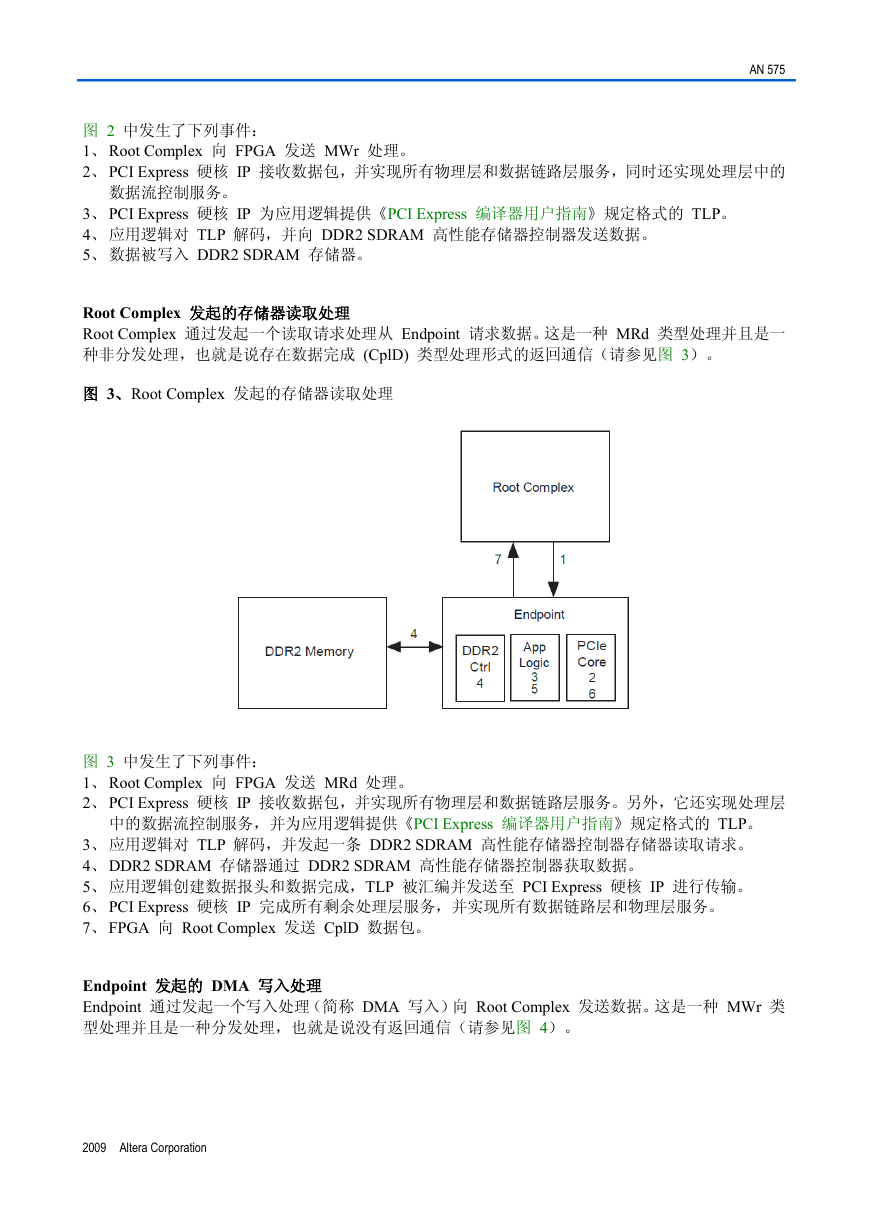

Root Complex 发起的存储器读取处理

Root Complex 通过发起一个读取请求处理从 Endpoint 请求数据。这是一种 MRd 类型处理并且是一

种非分发处理,也就是说存在数据完成 (CplD) 类型处理形式的返回通信(请参见图 3)。

图 3、Root Complex 发起的存储器读取处理

图 3 中发生了下列事件:

1、 Root Complex 向 FPGA 发送 MRd 处理。

2、 PCI Express 硬核 IP 接收数据包,并实现所有物理层和数据链路层服务。另外,它还实现处理层

中的数据流控制服务,并为应用逻辑提供《PCI Express 编译器用户指南》规定格式的 TLP。

3、 应用逻辑对 TLP 解码,并发起一条 DDR2 SDRAM 高性能存储器控制器存储器读取请求。

4、 DDR2 SDRAM 存储器通过 DDR2 SDRAM 高性能存储器控制器获取数据。

5、 应用逻辑创建数据报头和数据完成,TLP 被汇编并发送至 PCI Express 硬核 IP 进行传输。

6、 PCI Express 硬核 IP 完成所有剩余处理层服务,并实现所有数据链路层和物理层服务。

7、 FPGA 向 Root Complex 发送 CplD 数据包。

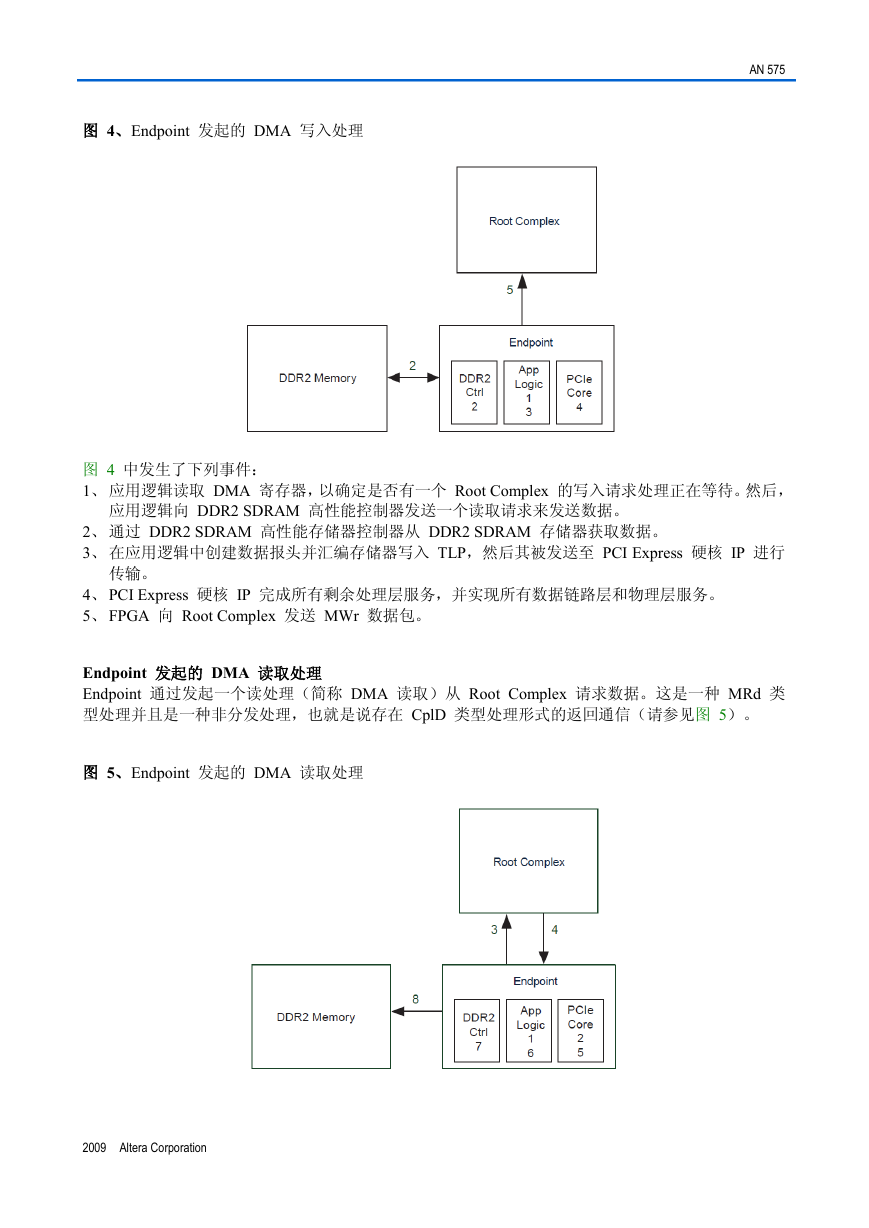

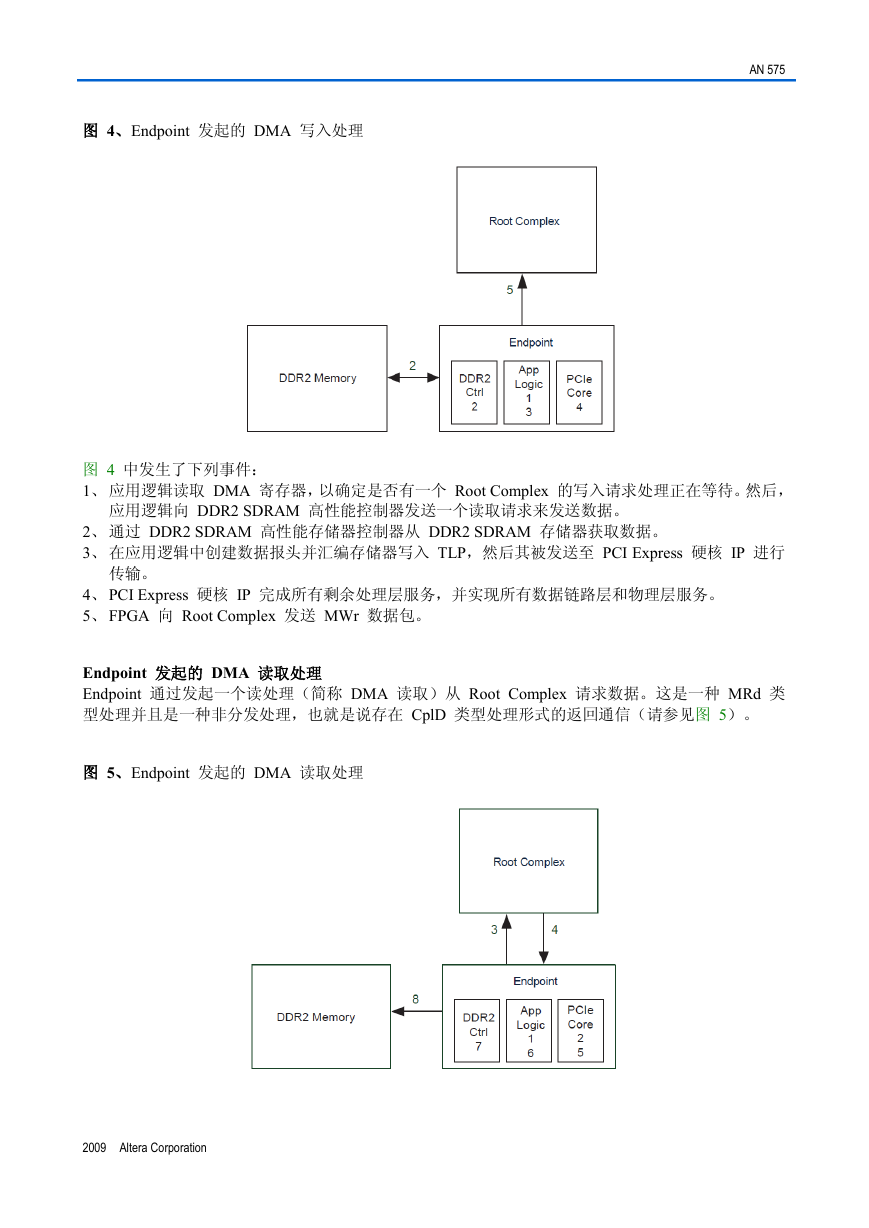

Endpoint 发起的 DMA 写入处理

Endpoint 通过发起一个写入处理(简称 DMA 写入)向 Root Complex 发送数据。这是一种 MWr 类

型处理并且是一种分发处理,也就是说没有返回通信(请参见图 4)。

2009 Altera Corporation

�

图 4、Endpoint 发起的 DMA 写入处理

AN 575

图 4 中发生了下列事件:

1、 应用逻辑读取 DMA 寄存器,以确定是否有一个 Root Complex 的写入请求处理正在等待。然后,

应用逻辑向 DDR2 SDRAM 高性能控制器发送一个读取请求来发送数据。

2、 通过 DDR2 SDRAM 高性能存储器控制器从 DDR2 SDRAM 存储器获取数据。

3、 在应用逻辑中创建数据报头并汇编存储器写入 TLP,然后其被发送至 PCI Express 硬核 IP 进行

传输。

4、 PCI Express 硬核 IP 完成所有剩余处理层服务,并实现所有数据链路层和物理层服务。

5、 FPGA 向 Root Complex 发送 MWr 数据包。

Endpoint 发起的 DMA 读取处理

Endpoint 通过发起一个读处理(简称 DMA 读取)从 Root Complex 请求数据。这是一种 MRd 类

型处理并且是一种非分发处理,也就是说存在 CplD 类型处理形式的返回通信(请参见图 5)。

图 5、Endpoint 发起的 DMA 读取处理

2009 Altera Corporation

�

图 5 中发生下列事件:

1、 应用逻辑读取 DMA 寄存器,以确定是否有一个 Root Complex 读请求处理正在等待。然后,应

用逻辑汇编一个存储器读取 TLP,并将其发送至 PCI Express 硬核 IP 进行传输。

AN 575

2、 PCI Express 硬核 IP 完成所有剩余处理层服务,并实现所有数据链路层和物理层服务。

3、 FPGA 向 Root Complex 发送一个 MWd 数据包。

4、 Root Complex 向 FPGA 发送一个 CplD 数据包。

5、 PCI Express 硬核 IP 接收完整数据包,并实现所有物理层和数据链路层服务,同时也实现处理层

中的流程控制服务。

6、 PCI Express 硬核 IP 为应用逻辑提供《PCI Express 编译器用户指南》规定格式的数据完成 TLP。

7、 应用逻辑对该 TLP 解码,并向 DDR2 SDRAM 高性能存储器控制器发送数据。

8、 数据被写入 DDR2 SDRAM 存储器。

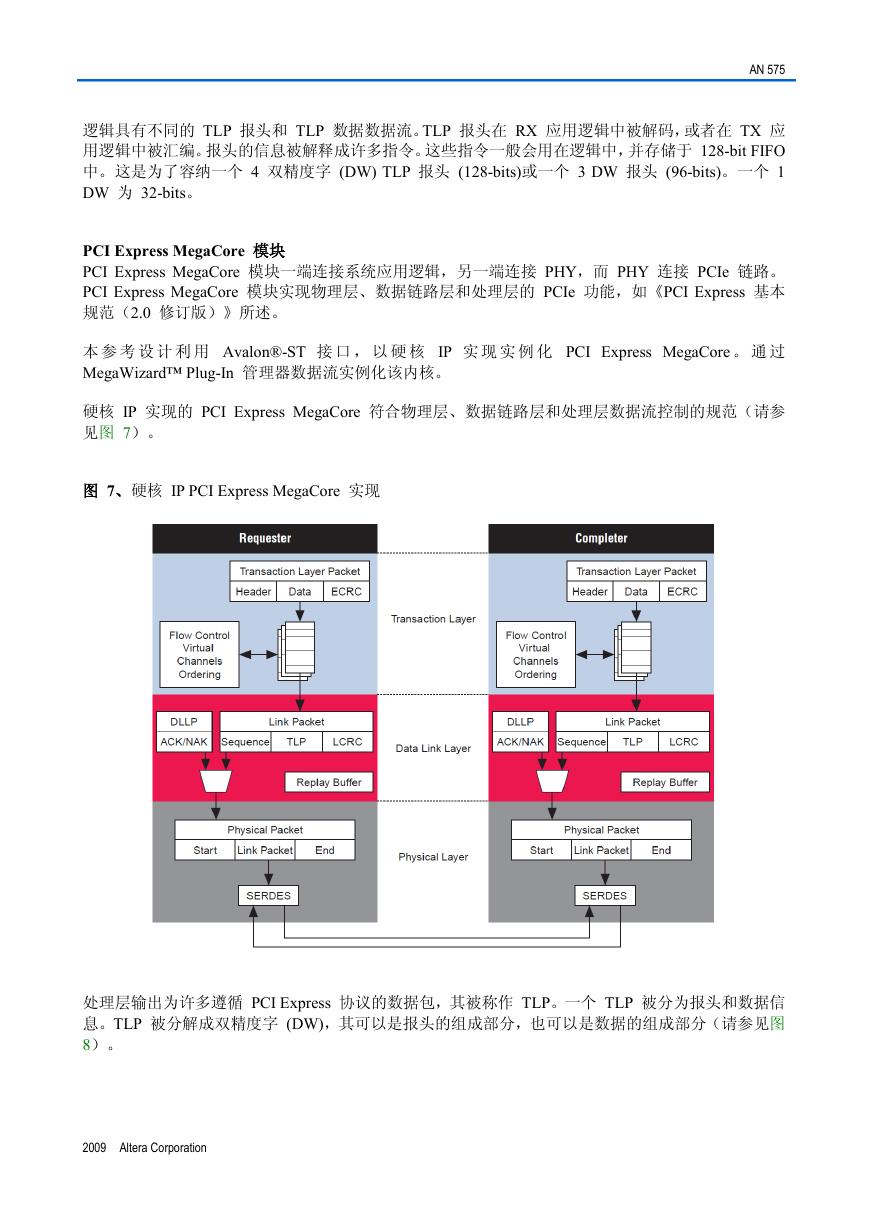

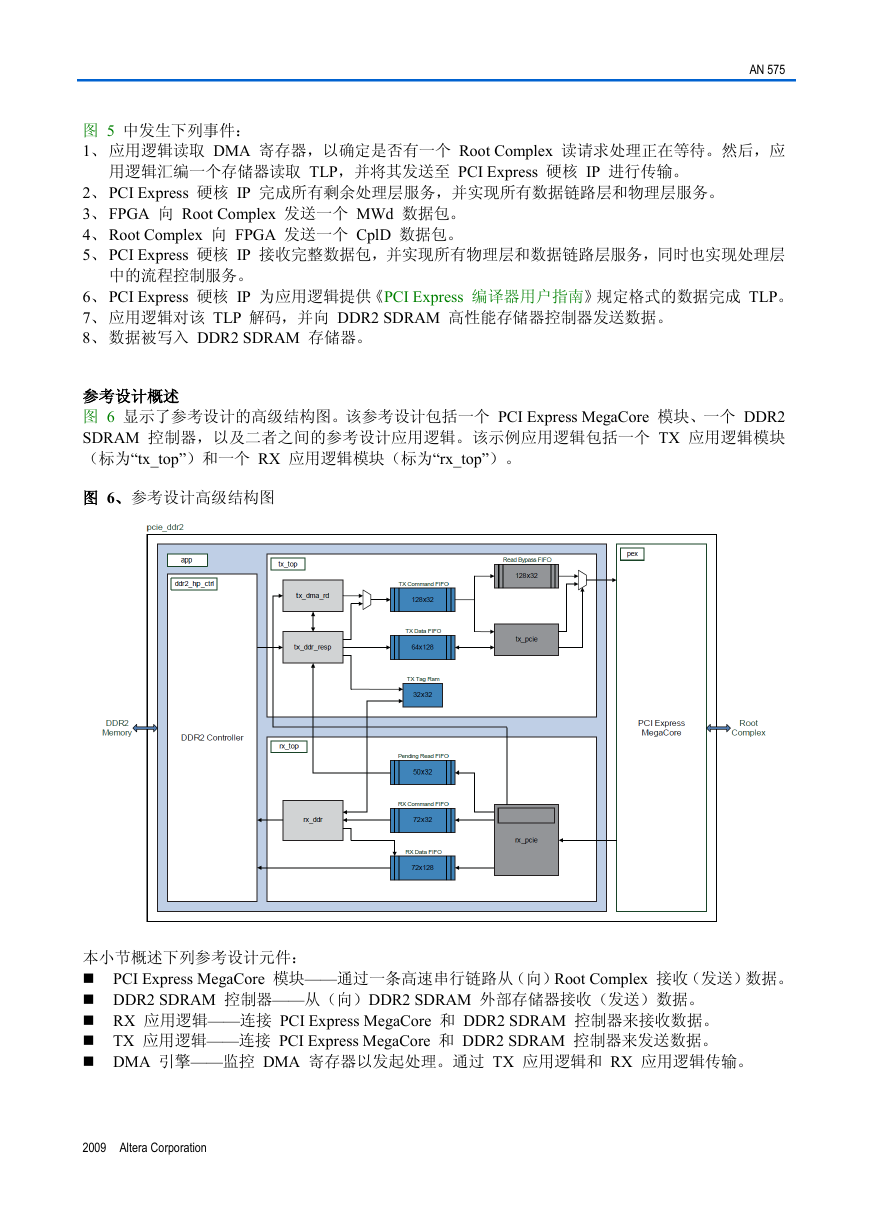

参考设计概述

图 6 显示了参考设计的高级结构图。该参考设计包括一个 PCI Express MegaCore 模块、一个 DDR2

SDRAM 控制器,以及二者之间的参考设计应用逻辑。该示例应用逻辑包括一个 TX 应用逻辑模块

(标为“tx_top”)和一个 RX 应用逻辑模块(标为“rx_top”)。

图 6、参考设计高级结构图

本小节概述下列参考设计元件:

PCI Express MegaCore 模块——通过一条高速串行链路从(向)Root Complex 接收(发送)数据。

DDR2 SDRAM 控制器——从(向)DDR2 SDRAM 外部存储器接收(发送)数据。

RX 应用逻辑——连接 PCI Express MegaCore 和 DDR2 SDRAM 控制器来接收数据。

TX 应用逻辑——连接 PCI Express MegaCore 和 DDR2 SDRAM 控制器来发送数据。

DMA 引擎——监控 DMA 寄存器以发起处理。通过 TX 应用逻辑和 RX 应用逻辑传输。

2009 Altera Corporation

�

AN 575

逻辑具有不同的 TLP 报头和 TLP 数据数据流。TLP 报头在 RX 应用逻辑中被解码,或者在 TX 应

用逻辑中被汇编。报头的信息被解释成许多指令。这些指令一般会用在逻辑中,并存储于 128-bit FIFO

中。这是为了容纳一个 4 双精度字 (DW) TLP 报头 (128-bits)或一个 3 DW 报头 (96-bits)。一个 1

DW 为 32-bits。

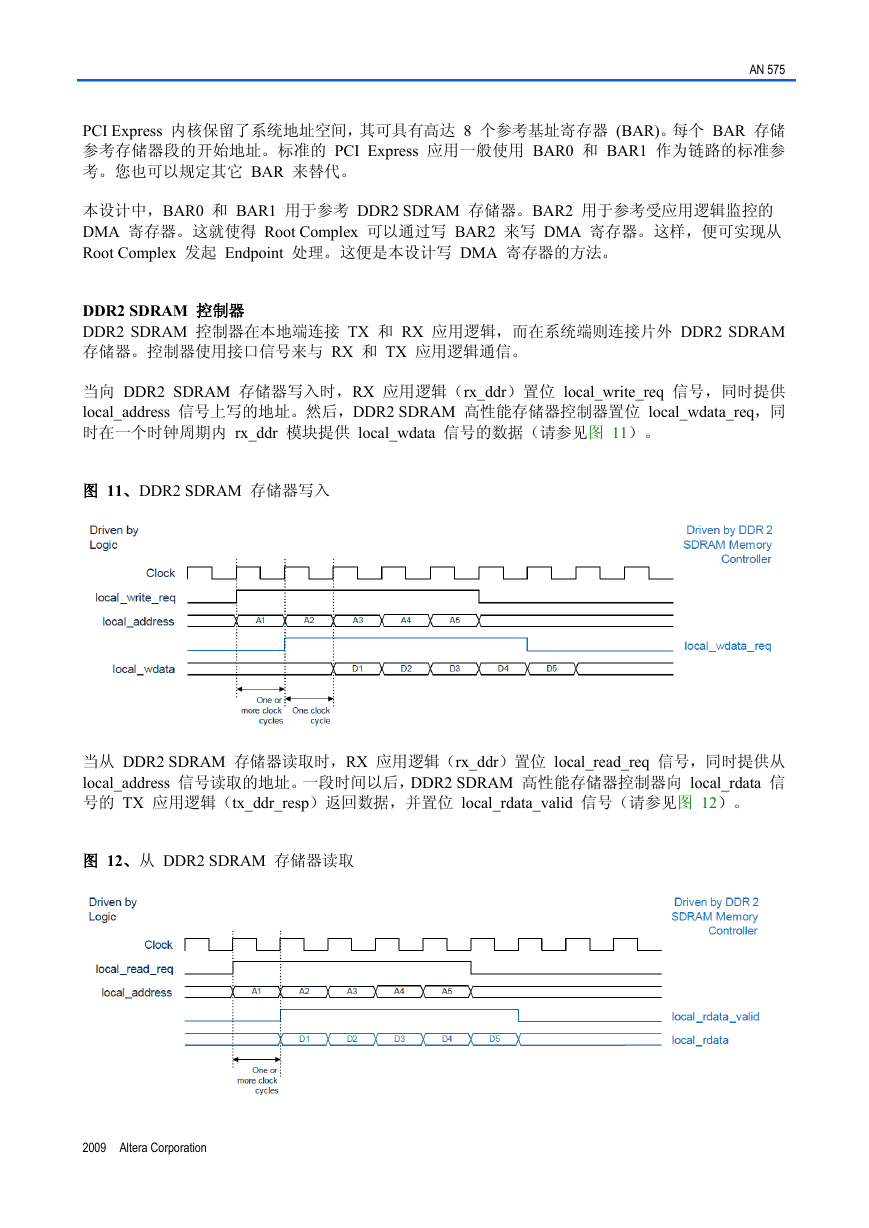

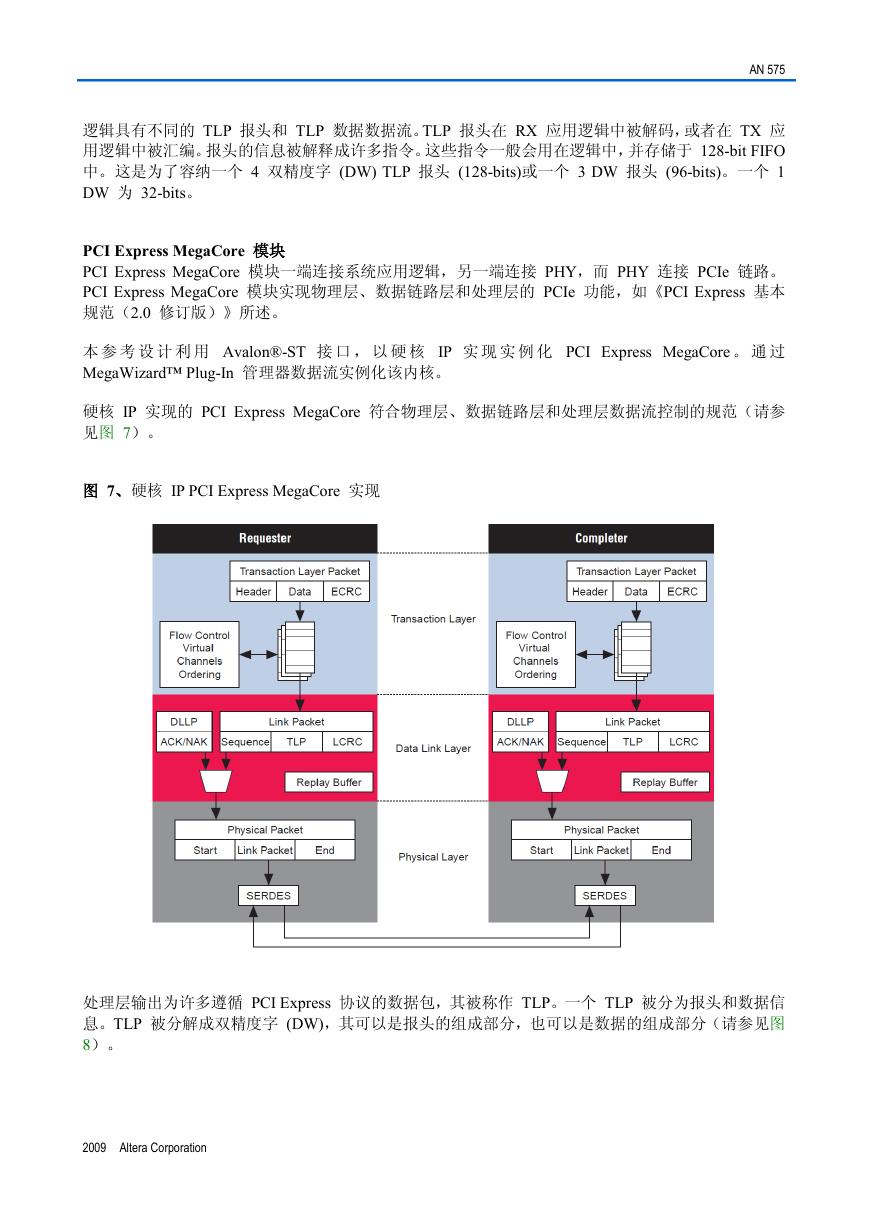

PCI Express MegaCore 模块

PCI Express MegaCore 模块一端连接系统应用逻辑,另一端连接 PHY,而 PHY 连接 PCIe 链路。

PCI Express MegaCore 模块实现物理层、数据链路层和处理层的 PCIe 功能,如《PCI Express 基本

规范(2.0 修订版)》所述。

本 参 考 设 计 利 用 Avalon®-ST 接 口 , 以硬 核 IP 实 现 实 例 化 PCI Express MegaCore 。 通 过

MegaWizard™ Plug-In 管理器数据流实例化该内核。

硬核 IP 实现的 PCI Express MegaCore 符合物理层、数据链路层和处理层数据流控制的规范(请参

见图 7)。

图 7、硬核 IP PCI Express MegaCore 实现

处理层输出为许多遵循 PCI Express 协议的数据包,其被称作 TLP。一个 TLP 被分为报头和数据信

息。TLP 被分解成双精度字 (DW),其可以是报头的组成部分,也可以是数据的组成部分(请参见图

8)。

2009 Altera Corporation

�

图 8、TLP 报头和数据信息

AN 575

TLP 可以有一个 3 DW 或 4 DW 报头。DW 长度字段的 TLP 报头规定了有效负载长度(请参见图

9)。

图 9、双精度字报头和有效负载长度

TLP 被传送至应用层,其在 FPGA 逻辑中实现。TLP 的形式如图 10 所示,其同时伴有控制信号。

TLP 信息存在于“数据”上。每个 TLP 开头都伴随一个数据包开始 (SOP)。数据包结束 (EOP) 标志

着 TLP 结束,在数据必须被计时且包含 TLP 信息的期间有效信号为高(请参见图 10)。

图 10、发送至应用层的 TLP

《PCI Express 基本规范(1.1 修订版)》第 2.1 节和《PCI Express 编译器用户指南》第 5 节分别

介绍了 TLP 的属性。

2009 Altera Corporation

�

AN 575

PCI Express 内核保留了系统地址空间,其可具有高达 8 个参考基址寄存器 (BAR)。每个 BAR 存储

参考存储器段的开始地址。标准的 PCI Express 应用一般使用 BAR0 和 BAR1 作为链路的标准参

考。您也可以规定其它 BAR 来替代。

本设计中,BAR0 和 BAR1 用于参考 DDR2 SDRAM 存储器。BAR2 用于参考受应用逻辑监控的

DMA 寄存器。这就使得 Root Complex 可以通过写 BAR2 来写 DMA 寄存器。这样,便可实现从

Root Complex 发起 Endpoint 处理。这便是本设计写 DMA 寄存器的方法。

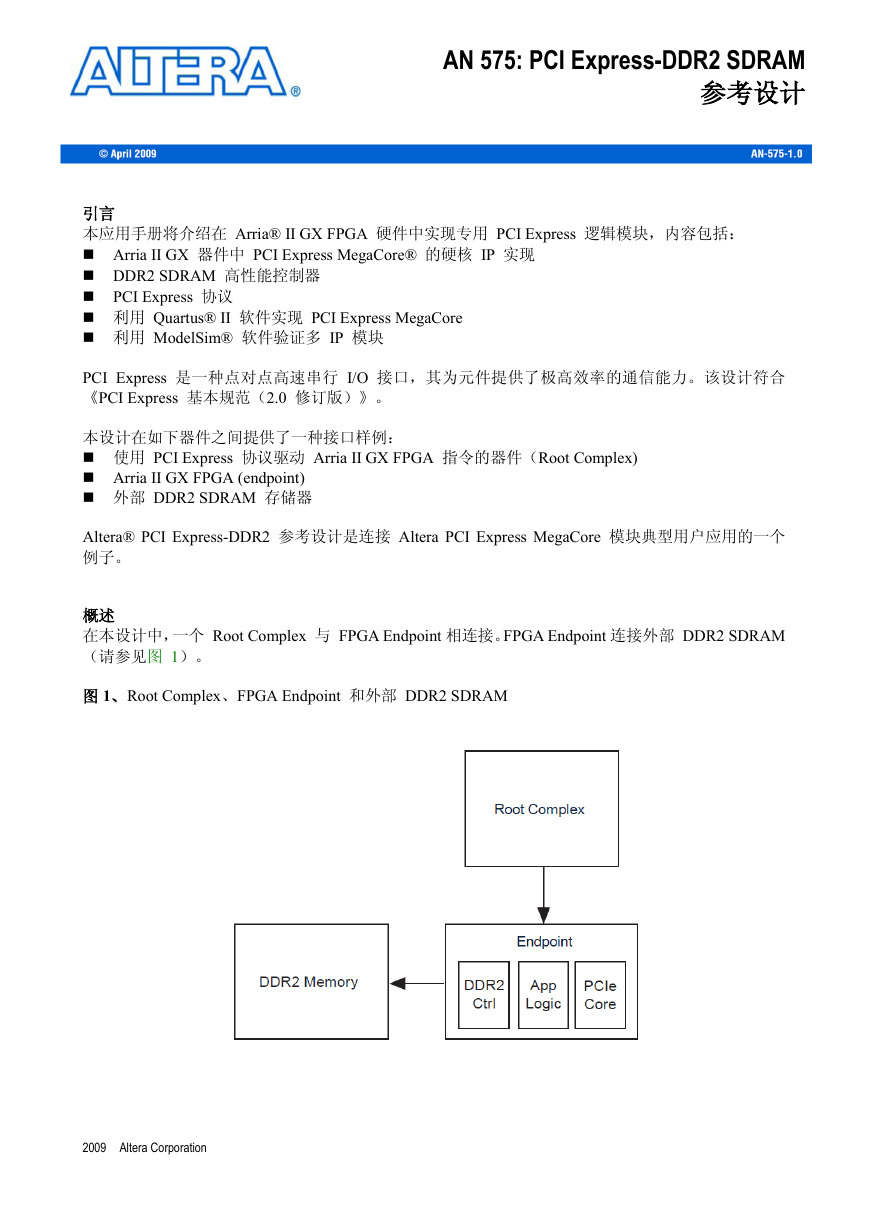

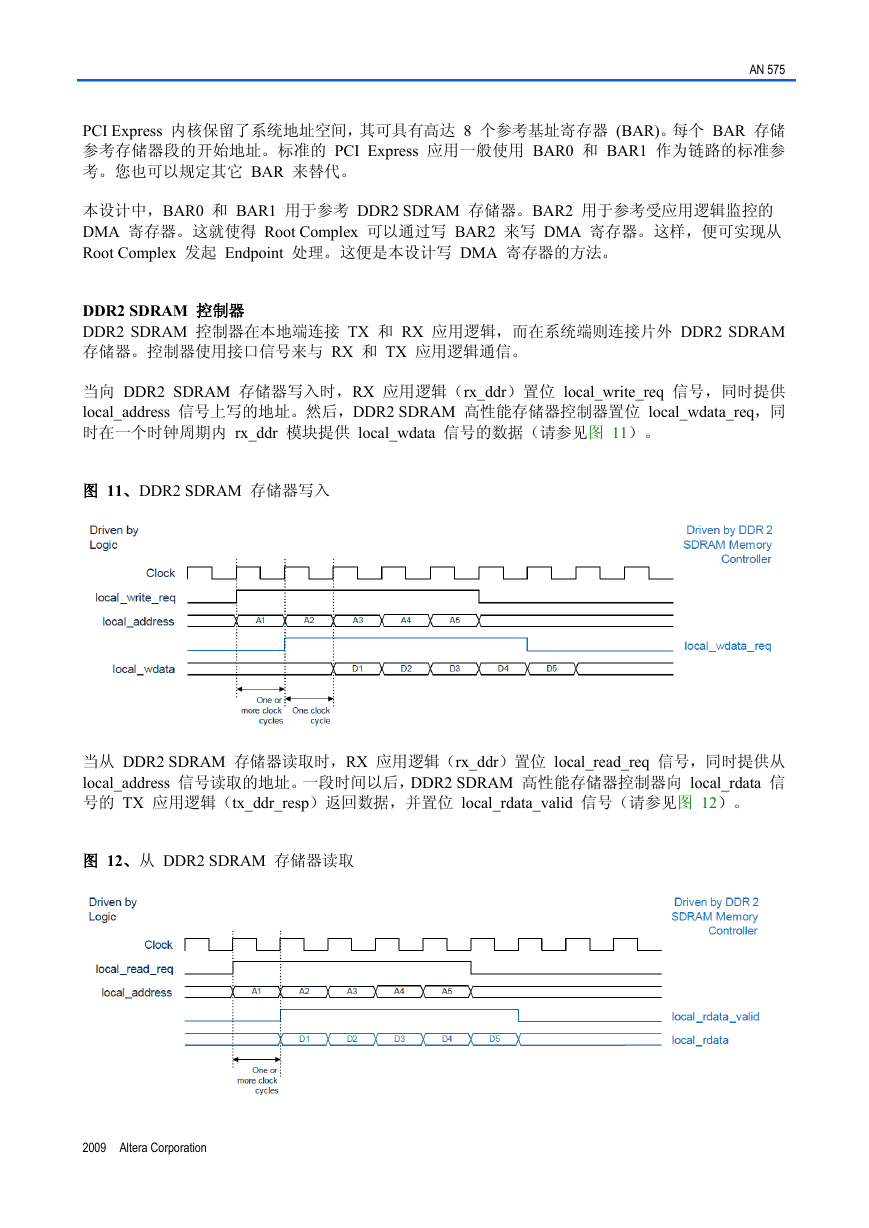

DDR2 SDRAM 控制器

DDR2 SDRAM 控制器在本地端连接 TX 和 RX 应用逻辑,而在系统端则连接片外 DDR2 SDRAM

存储器。控制器使用接口信号来与 RX 和 TX 应用逻辑通信。

当向 DDR2 SDRAM 存储器写入时,RX 应用逻辑(rx_ddr)置位 local_write_req 信号,同时提供

local_address 信号上写的地址。然后,DDR2 SDRAM 高性能存储器控制器置位 local_wdata_req,同

时在一个时钟周期内 rx_ddr 模块提供 local_wdata 信号的数据(请参见图 11)。

图 11、DDR2 SDRAM 存储器写入

当从 DDR2 SDRAM 存储器读取时,RX 应用逻辑(rx_ddr)置位 local_read_req 信号,同时提供从

local_address 信号读取的地址。一段时间以后,DDR2 SDRAM 高性能存储器控制器向 local_rdata 信

号的 TX 应用逻辑(tx_ddr_resp)返回数据,并置位 local_rdata_valid 信号(请参见图 12)。

图 12、从 DDR2 SDRAM 存储器读取

2009 Altera Corporation

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc