目 录

1.3

第 1 章:绪论............................................................................................................... 2

1.1 版图设计基础知识....................................................................................... 2

1.1.1 版图设计流程..................................................................................... 2

1.1.2 版图设计步骤..................................................................................... 2

1.1.3 版图设计规则及验证......................................................................... 3

1.2 标准单元版图的设计................................................................................... 4

1.2.1 标准单元库的定义............................................................................. 4

1.2.2 标准单元库用途................................................................................. 4

1.2.3 标准单元库设计流程......................................................................... 4

0.35um 工艺的设计规则............................................................................. 5

1.3.1 版图设计生成及建库技术................................................................. 5

第 2 章:D 触发器介绍............................................................................................... 6

2.1 D 触发器原理............................................................................................... 6

2.2 边沿 D 触发器............................................................................................. 7

2.2.1 边沿 D 触发器电路结构................................................................... 7

2.2.2 边沿 D 触发器工作原理.................................................................... 7

2.3 维持阻塞 D 触发器...................................................................................... 9

2.4 基于 TSPC 原理的 D 触发器.....................................................................12

第 3 章:0.35um 工艺基于 TSPC 原理的 D 触发器设计........................................13

3.1 动态 D 触发器电路图的设计步骤及电路图............................................ 13

3.2 动态 D 触发器版图的设计步骤及电路图................................................ 14

3.3 DRC 验证.................................................................................................... 15

第 4 章:课程设计总结............................................................................................. 16

参考文献..................................................................................................................... 17

�

第 1 章:绪论

1.1 版图设计基础知识

1.1.1 版图设计流程

版图设计是创建工程制图(网表)的精确的物理描述的过程,而这一物理描

述遵守由制造工艺、设计流程以及仿真显示为可行的性能要求所带来的一系列约

束。

1.1.2 版图设计步骤

1.首先,市场部通常会详细说明需要开发的产品。

2.下一步是规定设计的结构或者行为。电路设计工程师规定

芯片的结构来满足市场和/或 IDEA 功能需求。

3.系统仿真由一组工程师完成。这组工程师会对将要集成在

最终芯片中的各个单独模块进行定义和验证。

4.电路设计组完成所有的数字和模拟仿真,来验证电路的方

案和门的连通性,以及门的尺寸(为了满足时序规范)。这些组

需要和版图设计组进行交互,版图设计组会使电路适合芯片的版

图布局。

5.版图设计由版图设计工程师完成。他们的工作包括放置多

2

�

边形,对于所有的模块,利用电路组生成的电路图来实现晶体管、基底连线、连

线(使用 1 至 6 层金属)等。拿去大规模生产的最终设计是整个芯片的版图。

6.在第一块晶圆制造出来后,测试工程师组就要开始尝试测试芯片,首先,

他们将检查工艺参数是否在可以接受的允许误差范围内。下一步是使用工程测试

仪来测试芯片,以便于找出所有的违规,并尝试在现场解决这些问题。

7.在改正所有的错误(工艺上的和/或逻辑上的)后,芯片就要开始批量生产

并流入市场.

应当记住,这只是一个概念上的流程.在实际中,通过不同的设计阶段时,会有

很多的反复和设计上的迭代。

1.1.3 版图设计规则及验证

版图设计得好坏,其功能正确与否,必须通过验证工具才能确定。版图的验

证通常包括三大部分:设计规则检查(DRC)、电学规则检查(ERC)和版图与电路

图对照(LVS)。只有通过版图验证的芯片设计才进行制版和工艺流片。

设计规则的验证是版图与具体工艺的接口, 因此就显得尤为重要, Cadence

中进行版图验证的工具主要有 dracula 和 diva。Dracula 为独立的验证工具, 不仅

可以进行设计规则验证(DRC) , 而且可以完成电学规则验证(ERC)、版图与电路

验证(LV S)、寄生参数提取(L PE) 等一系列验证工作, 功能强于 Diva。通过 C IW

窗口中的 Export→Stream 菜单, 将版图转变成 GDS2 格式文件*.gds, 并存到运

行目录下。在创建了规则文件之后, 就可以使用 PDRACULA 预处理工具对其进

行编译。首先, 检查规则文件中的语法错误, 通过后方可对规则文件进行编译,

并将结果存为可执行文件进行 jxrun.com 或 jxsub.com, 这个可执行文件包含了

提交 Dracula 任务的命令。在进行验证操作过程中用到的库都应位于当前运行目

录或由路径指定链接到该运行目录。如果库不位于当前运行目录, 则由 Pdracula

建立一个从库到运行目录的链接, 并将其加入上述可执行文件 jxrun.com 中, 经

jxrun.con 执行后产生的错误文件(*.DA T )。打开要验证单元的版图界面, 点击

file 下的 D racula

Interact ive, DRC, LV S, L PE 等窗口弹出在菜单栏上, 在

DRC 菜单下的 setup 中, 给出错误文件的路径, 即可将错误报告与 Virtuoso 的图

形界面结合起来, 根据错误层的提示, 在图中直接修改即可。

根据错误报告的提示, 修改版图的步骤为:

3

�

(1) 将错误文件导入 Virtuoso 界面。

(2) 找到错误层, 根据错误提示进行修改。

(3) 更新 gds II, 编译规则文件, 进行 DRC 验证, 重复上述(1) , (2) 操作, 直

至版图完全通过 DRC 验证。有一类错误比较隐蔽, 称为 offgrid 错误。这类错误

是因为位置位于最小栅格的内部造成的, 这样的版图在制版中因分辨率的限制

会对尺寸四舍五入, 造成数据的失真, 甚至可能违反设计规则, 故必须修改。在

最高层的 offgrid 错误易于修改, 移动该层或线使其位于栅格边界上,在底层的错

误要 descend 数层后, 修改 instance 才可完成。

1.2 标准单元版图的设计

1.2.1 标准单元库的定义

整套的标准单元库包括版图库、符号库、电路逻辑库等。包含了组合逻辑、

时序逻辑、功能单元和特殊类型单元。是集成电路芯片后端设计过程中的基础部

分。一般每个工艺厂商在每个工艺下都会提供相应的标准单元。

1.2.2 标准单元库用途

标准单元库用来为布局布线工具提供支持,导出以下文档用来进行支持:

GDSII 文件:包含了单元的版图信息,用来合成最终的全芯片版图;

LEF 文件:本文件是 SOC ENCOUNTER 环境下用于进行布局布线的文件,

该文件为布局布线工具提供了工艺信息和各个单元的几何特性;

时序文件:时序文件用于 Design Complier 及其他数字综合工具进行门级综

合,用于 SOC ENCOUNTER 等布局布线工具进行时序优化和调节。

电路逻辑和符号库:用于进行大规模的芯片电路设计。

1.2.3 标准单元库设计流程

标准单元库的设计主要包括电路设计和版图设计记忆文档的提取。其中电路

设计环节要确定库容量的确定和时序曲线的优化,在这一设计中要最终确定所需

的单元类型和驱动能力,电路设计完毕后进行版图的设计,往往通过全定制的人

工设计进行。不过也有一些自动化的工具进行,如 CELLERITY 和 CLIP。

4

�

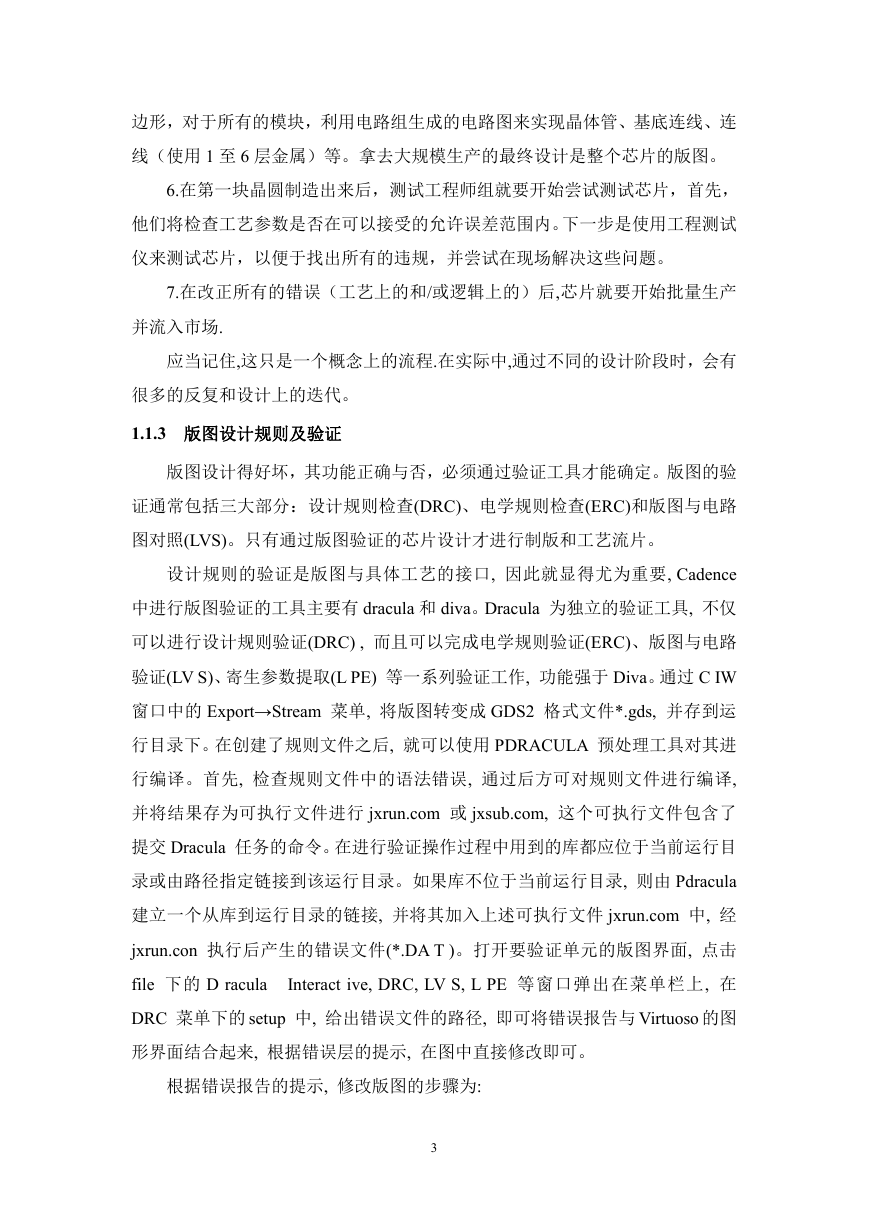

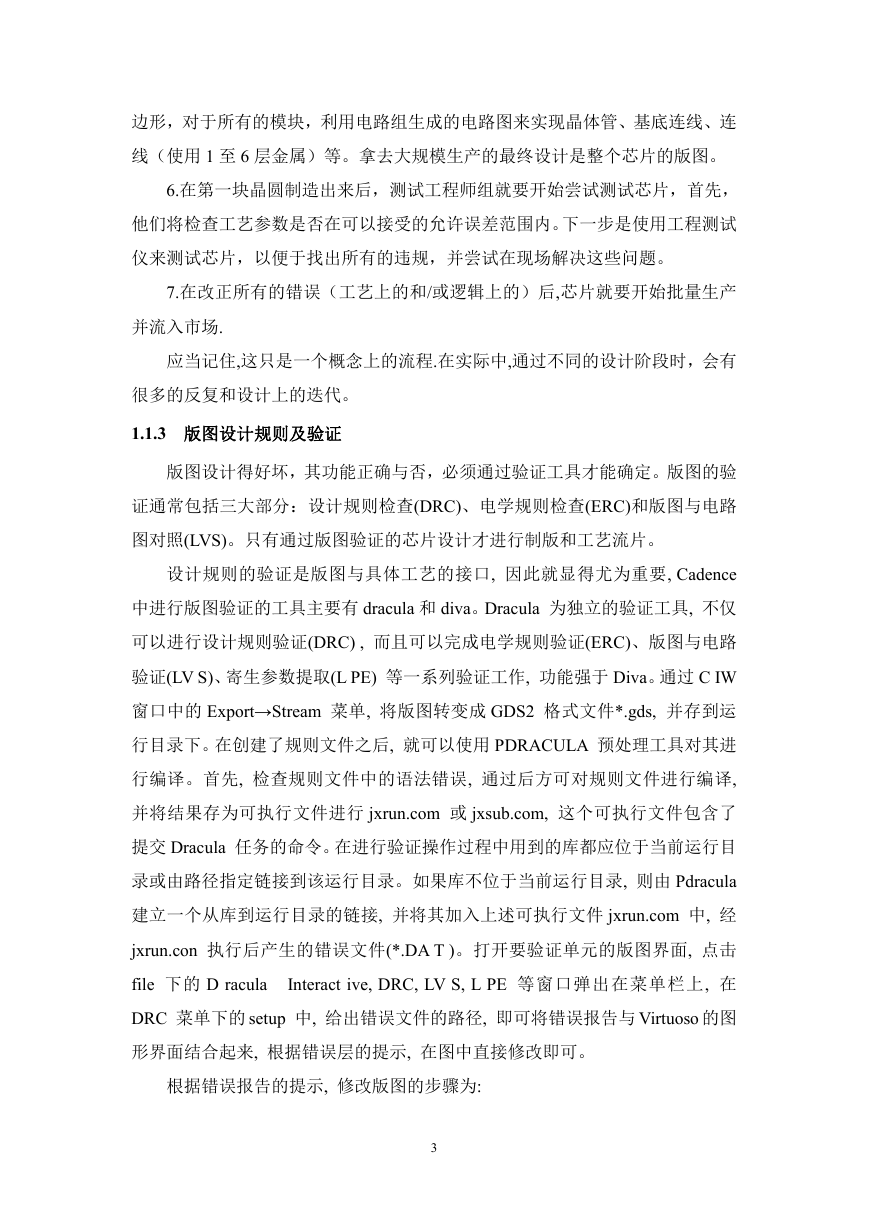

1.3 0.35um 工艺的设计规则

电路设计师一般都希望电路设计得尽量紧凑, 而工艺设计师却希望工艺成品

率高, 设计规则是对他们满意的折衷。设计规则是良好的规范文献,它列出了元

件(导体、有源区、电阻器等)

的最小宽度,相邻部件之间所允

许的最小间距,必要的重叠与给

定的工艺相配合的其它尺寸。人

们把设计过程抽象成若干易于处

理的概念性版图层次,这些层次

代表将线路转换成芯片时所必需

的掩膜图形。下面就以 0.35um N

阱硅栅工艺为例来介绍有关层次

的概念。不同层次的名称、含义

及其图形标记参见右图。

1.3.1 版图设计生成及建库技术

单元库中的每个标准单元具有相同的高度,而宽度则视单元的复杂程度而有

所不同,这样才能在综合布局布线时连成一个整体。标准单元的版图除了电源、

地线的端口可以从两侧水平引出之外,其它端口都排列在相对的上下两边。这样,

布局时从水平方向上可以方便地使所有标准单元排列得很整齐。互连线则被放置

在单元行之间的水平布线通道和单元行两端的垂直布线通道区内。对所有单元一

般要遵循下面的规则:

1)每一个逻辑 Pin 必须包括至少有一个端口的物理描述,每个端口必须至

少有一个物理几何尺寸。

2)属于一个单元的所有对象必须在单元边界里面。

3)在一些技术中,电源和地伸出边缘或者在边界外边。

4)Pin 的边缘和 Blockage 必须至少是到单元边界最小距离的一半。

5)让单元尺寸最小并不一定是要使芯片面积最小。最好是通过稍微增加芯

片面积来优化布局而不是在脑子中一直不考虑布局而一味地减小单元的面积。由

于 0.35um 标准单元库是要标准单元在单个单元行中具有相同的高度,设计时可

5

�

以使电源共享。电源共享可以通过减少通道的数量来减少芯片的面积。

第 2 章:D 触发器介绍

触发器是能够存储一位二进制信息的基本单元。

触发器特点有 1.有两个能够保持的稳定状态,分别用来表示逻辑 0 和逻辑 1。

2. 在适当输入信号作用下,可从一种状态翻转到另一种状态;在输入信号取消

后,能将获得的新状态保存下来。把触发器按触发方式分:可分为电位触发方式、

主从触发方式及边沿触发方式。按逻辑功能分:可分为 R-S 触发器、D 触发器、

J-K 触发器和 T 触发器。

2.1 D 触发器原理

触 发 器 是 一 种 时 钟 控 制 的 记 忆 器 件 , 触 发 器 具 有 一 个 控 制 输 入 讯 号

(CLOCK)。CLOCK 讯号使触发器只在特定时刻才按输入讯号改变输出状态。若

触发器只在时钟 CLOCK 由 L 到 H (H 到 L) 的转换时刻才接收输入,则称这种

触发器是上升沿 (下降沿) 触发的。

触发器可用来储存一位的数据。通过将若干个触发器连接在一起可储存多位

元的数据,它们可用来表示时序器的状态、计数器的值、电脑记忆体中的 ASCII

码或其他资料。

D 触发器是最常用的触发

器之一。对于上升沿触发 D 触

发 器 来 说 , 其 输 出 Q 只 在

CLOCK 由 L 到 H 的转换时刻

才会跟随输入 D 的状态而变

化,其他时候 Q 则维持不变。

上图显示了上升沿触发 D 触发器的时序图。

6

�

SET 和 RESET 是 D 触发器中额外两个可以屏蔽时钟操作的输入。D 触发器

正常工作情况下,SET 和 RESET 均必须设为 1。

2.2 边沿 D 触发器

负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在

CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状况出错。而边

沿触发器允许在 CP 触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的

时间大大缩短,受干扰的可能性就降低了。边沿 D 触发器也称为维持-阻塞边沿

D 触发器。

2.2.1 边沿 D 触发器电路结构

该触发器由 6 个与非门组成,其中 G1 和 G2 构成基本 RS 触发器。

2.2.2 边沿 D 触发器工作原理

SD 和 RD 接至基本 RS 触发器的输入端,它们分别是预置和清零端,低电

平有效。当 SD=0 且 RD=1 时,不论输入端 D 为何种状况,都会使 Q=1,Q=0,即

触发器置 1;当 SD=1 且 RD=0 时,触发器的状况为 0,SD 和 RD 通常又称为直接

置 1 和置 0 端。我们设它们均已加入了高电平,不影响电路的工作。工作过程如

下:

1.CP=0 时,与非门 G3 和 G4 封锁,其输出 Q3=Q4=1,触发器的状况不变。同时,

由于 Q3 至 Q5 和 Q4 至 Q6 的反馈信号将这两个门打开,因此可接收输入信号 D,

Q5=D,Q6=Q5=D。

2.当 CP 由 0 变 1 时触发器翻转。这时 G3 和 G4 打开,它们的输入 Q3 和 Q4 的

状况由 G5 和 G6 的输出状况决定。Q3=Q5=D,Q4=Q6=D。由基本 RS 触发器的

7

�

逻辑功能可知,Q=D。

3.触发器翻转后,在 CP=1 时输入信号被封锁。这是因为 G3 和 G4 打开后,它们

的输出 Q3 和 Q4 的状况是互补的,即必定有一个是 0,若 Q3 为 0,则经 G3 输出

至 G5 输入的反馈线将 G5 封锁,即封锁了 D 通往基本 RS 触发器的路径;该反

馈线起到了使触发器维持在 0 状况和阻止触发器变为 1 状况的作用,故该反馈线

称为置 0 维持线,置 1 阻塞线。Q4 为 0 时,将 G3 和 G6 封锁,D 端通往基本 RS

触发器的路径也被封锁。Q4 输出端至 G6 反馈线起到使触发器维持在 1 状况的

作用,称作置 1 维持线;Q4 输出至 G3 输入的反馈线起到阻止触发器置 0 的作

用,称为置 0 阻塞线。因此,该触发器常称为维持-阻塞触发器。总之,该触发器

是在 CP 正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,

三步都是在正跳沿后完成,所以有边沿触发器之称。与主从触发器相比,同工艺

的边沿触发器有更强的抗干扰能力和更高的工作速度。

2.2.3 边沿 D 触发器功能描述

2.2.3.1 状况转移真值表

2.2.3.2 特征方程

Qn+1=D

2.2.3.3 状况转移图

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc