文档标题:EZ-USB® FX3™/FX3S™硬件设计指南和原理图检查表

AN70707

作者: Rizwan Afridi、Hussein Osman

相关项目:无

相关部件系列: CYUSB3014、CYUSB3035

软件版本:N/A

相关应用手册:无

AN88725 文档介绍了,开发人员需要考虑的 EZ-USB® FX3™/FX3S™硬件设计及其关键项目的建议。赛普拉斯 EZ-

USB FX3 是新一代的 USB 3.0 外设控制器。它可提供高度集成和灵活的特性,因此开发人员可以在任何系统中添加

USB 3.0 功能。除非另有说明,所有推荐的内容都应用于 FX3 和 FX3S。

目录

简介

简介 ................................................................................... 1

供电系统 ............................................................................ 2

概述 .............................................................................. 3

功耗模式 ....................................................................... 4

器件的电源去耦 ............................................................ 4

电涌注意事项和供电设计 .............................................. 4

时钟 ................................................................................... 6

晶振 .............................................................................. 6

时钟 .............................................................................. 7

看门狗定时器 ................................................................ 7

GPIF II 接口 ....................................................................... 7

I2C 接口 ............................................................................. 7

低性能外设(LPP) .......................................................... 8

JTAG ............................................................................ 8

I2S................................................................................. 8

SPI 和 UART ................................................................ 8

引导 ................................................................................... 8

EMI 和 ESD 注意事项 ........................................................ 9

FX3 器件封装尺寸 ............................................................. 9

电气设计注意事项.............................................................. 9

USB 3.0 SuperSpeed 的设计指南 ................................ 9

附录 A — PCB 布局提示 .................................................. 18

赛普拉斯 EZ-USB® FX3 是新一代 USB 3.0 外设控制器,可

提供集成和灵活的功能。FX3 具有一个可进行完全配置的

并行通用可编程接口 GPIF II,它能够与任何处理器、ASIC

或 FPGA 连接。它可轻松无缝地同多种常用接口建立连

接,如异步 SRAM、异步和同步地址数据复用式接口,以

及并行 ATA。FX3 包含一个嵌入式 32 位 ARM926EJ-S 微

处理器,它具有强大的数据处理能力,并可用于构建定制应

用。本产品采用了一种架构,使从 GPIF II 到 USB 接口的

数据传输速度可达 375 MB/秒。

通过集成的 USB2.0 OTG 控制器可以使能某些应用,其中

FX3 具有两个作用。例如,EZ-USB FX3 可以作为 OTG 主

机控制 MSC 设备和作为 HID 设备使用。FX3 具有大小为

512 KB 或 256KB 的片上 SRAM,用于存储代码和数据。

EZ-USB FX3 还具有可连接至 UART、SPI、I2C 和 I2S 等

串行外设的接口。FX3 带有应用开发工具。软件开发工具

包中带有应用示例,从而能够加快产品的上市时间。

除了上述功能外,FX3S 还集成了存储控制器,并可支持 2

个独立的大容量存储器。它支持 SD 3.0 和 eMMC 4.41 存

储卡。并且这些端口还支持 SDIO 功能。 FX3 和 FX3S 特

性的区别如表 1 所示。

为了成功地将这个高吞吐量的管道添加到系统内,开发者必

须在设计过程中考虑多个关键因素。由于 EZ-USB FX3 器

件的封装和高性能特性,您需要遵照指南中所要求的走线宽

度、多层板以及其他布局注意事项,以确保系统正常运行。

有 关 EZ-USB FX3 DVK 的 参 考 原 理 图 , 请 查 看

CYUSB3KIT-001 EZ-USB® FX3™ 中 介 绍 的 内 容 。 如 需

EZ-USB FX3S DVK 原理图,请与 fx3@cypress.com 取得

联络。

www.cypress.com

文档编号:001-88725 版本**

1

�

EZ-USB® FX3/FX3S™硬件设计指南和原理图的检查表

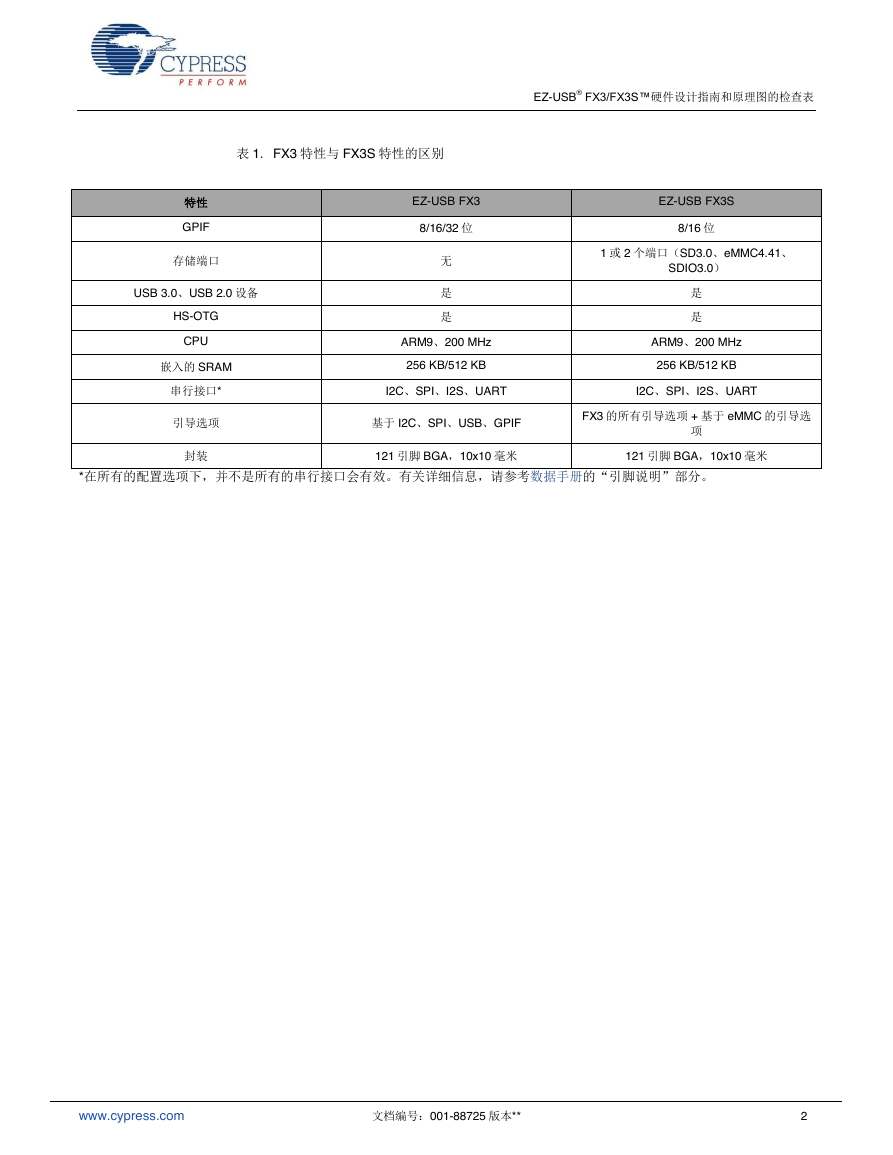

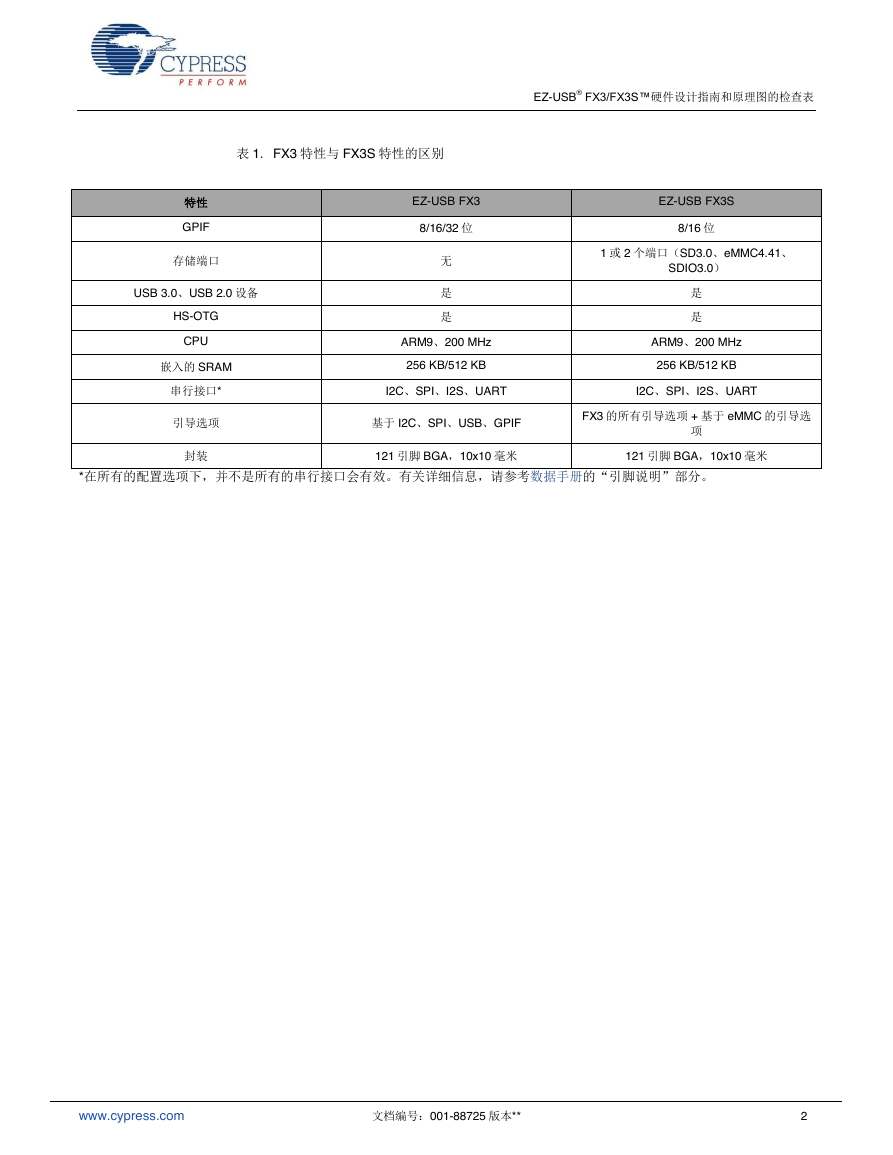

表 1. FX3 特性与 FX3S 特性的区别

特性

GPIF

存储端口

USB 3.0、USB 2.0 设备

HS-OTG

CPU

嵌入的 SRAM

串行接口*

引导选项

封装

EZ-USB FX3

8/16/32 位

无

是

是

ARM9、200 MHz

256 KB/512 KB

EZ-USB FX3S

8/16 位

1 或 2 个端口(SD3.0、eMMC4.41、

SDIO3.0)

是

是

ARM9、200 MHz

256 KB/512 KB

I2C、SPI、I2S、UART

I2C、SPI、I2S、UART

基于 I2C、SPI、USB、GPIF

FX3 的所有引导选项 + 基于 eMMC 的引导选

项

121 引脚 BGA,10x10 毫米

121 引脚 BGA,10x10 毫米

*在所有的配置选项下,并不是所有的串行接口会有效。有关详细信息,请参考数据手册的“引脚说明”部分。

www.cypress.com

文档编号:001-88725 版本**

2

�

供电系统

EZ-USB® FX3/FX3S™硬件设计指南和原理图的检查表

概述

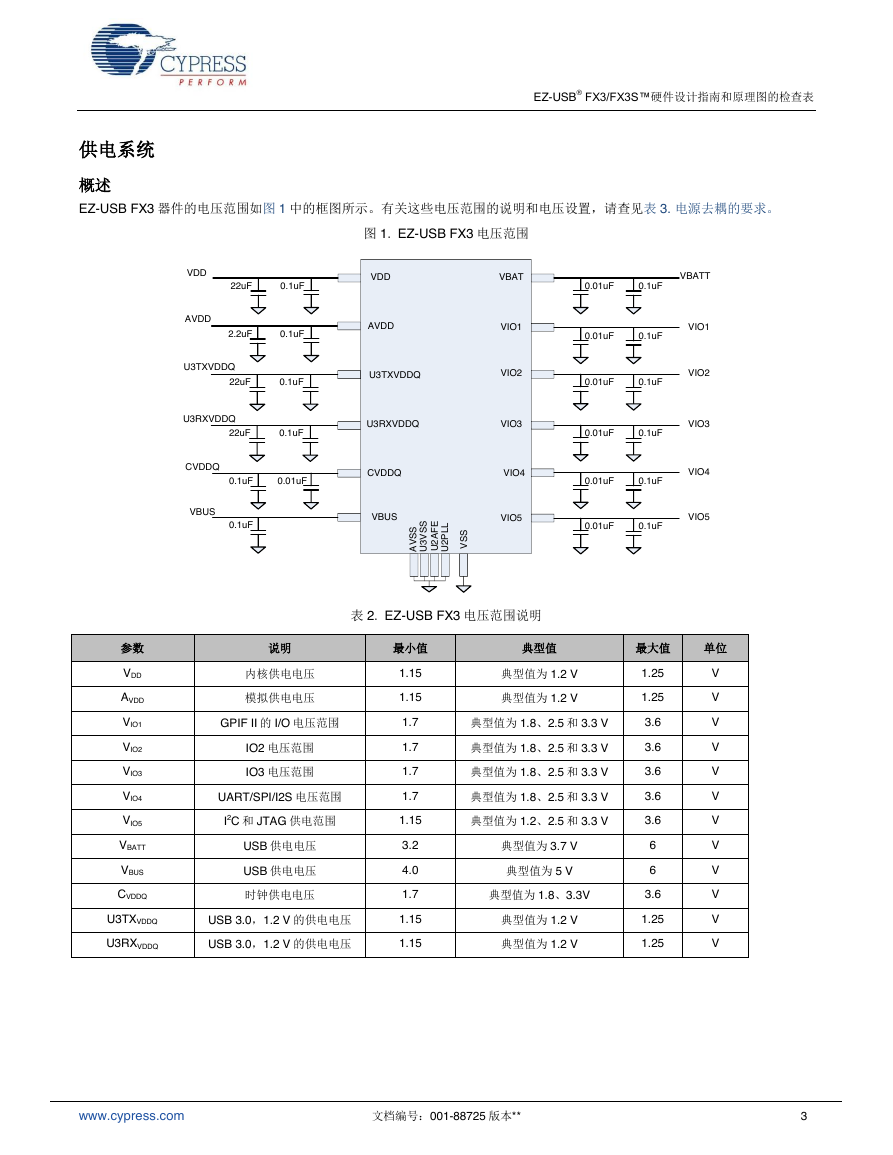

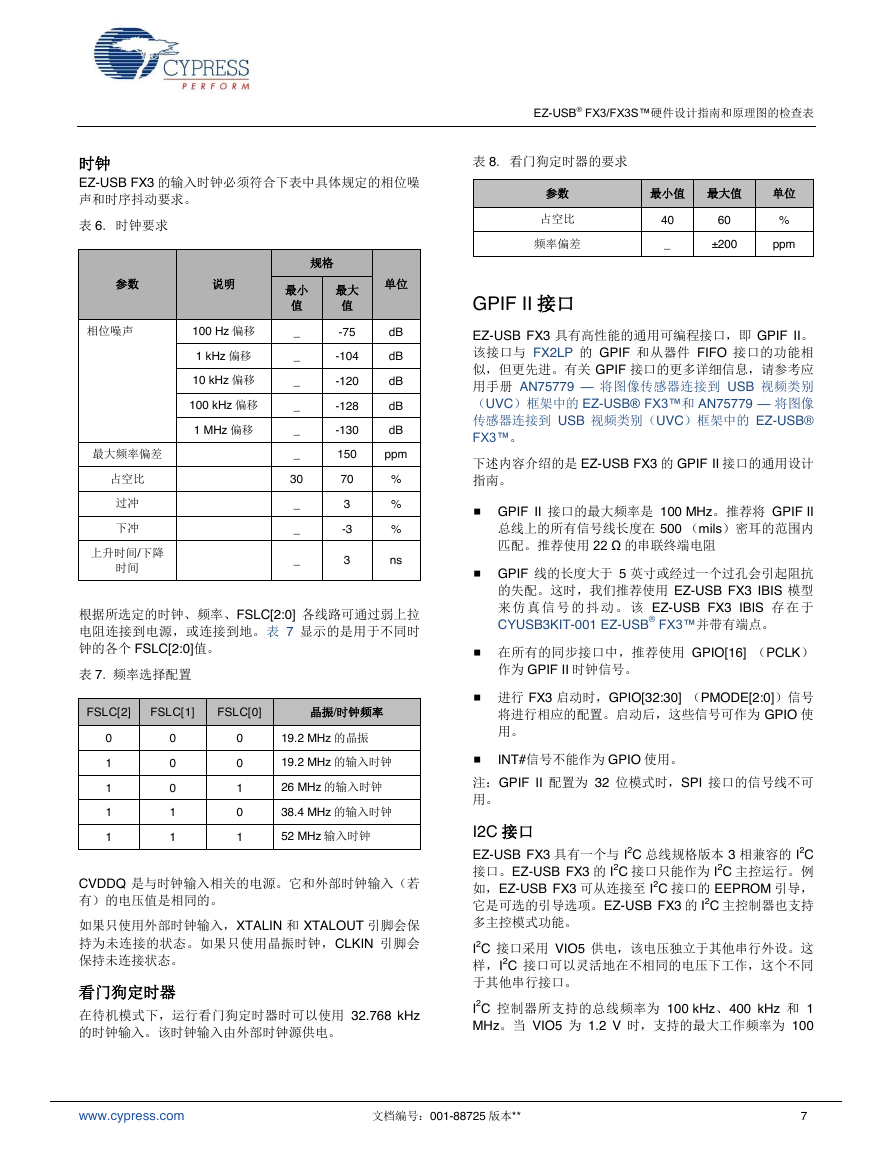

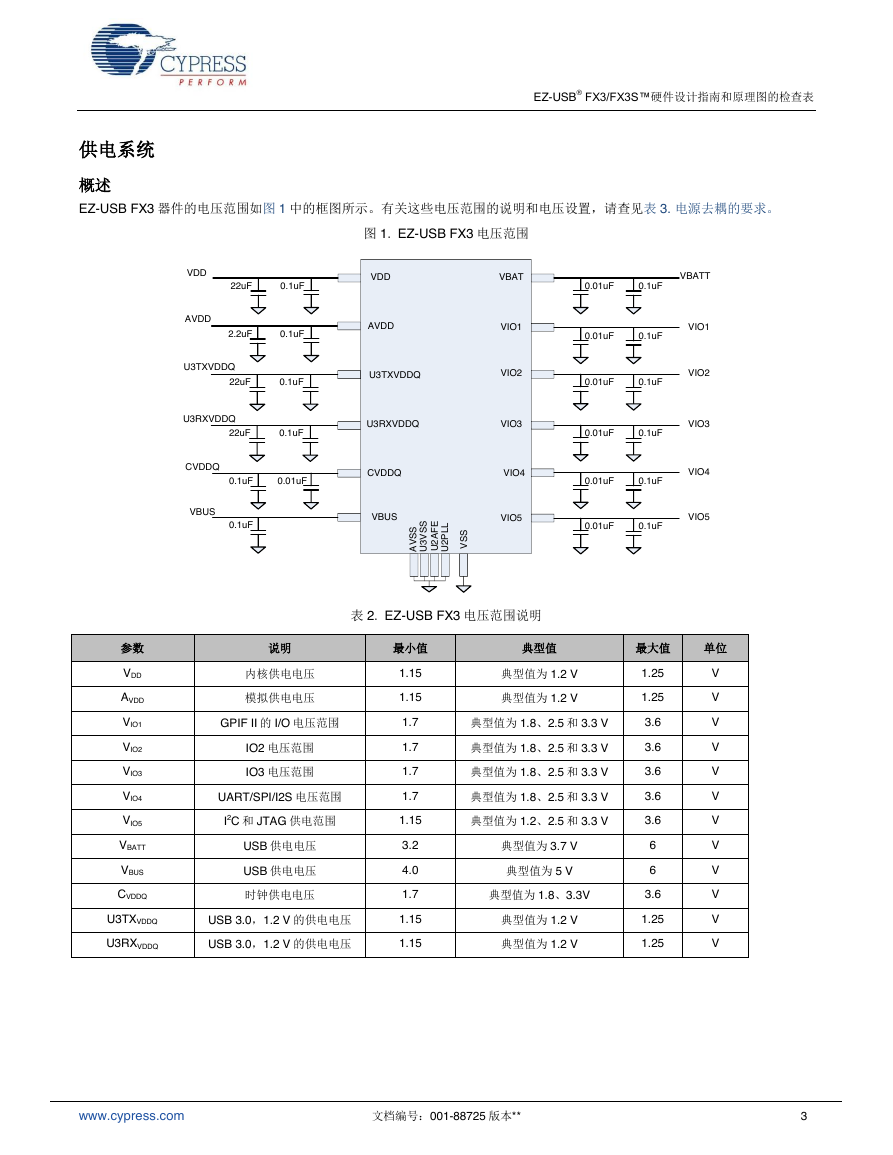

EZ-USB FX3 器件的电压范围如图 1 中的框图所示。有关这些电压范围的说明和电压设置,请查见表 3. 电源去耦的要求。

图 1. EZ-USB FX3 电压范围

表 2. EZ-USB FX3 电压范围说明

说明

最小值

典型值

最大值

单位

内核供电电压

模拟供电电压

GPIF II 的 I/O 电压范围

IO2 电压范围

IO3 电压范围

UART/SPI/I2S 电压范围

1.15

1.15

1.7

1.7

1.7

1.7

典型值为 1.2 V

典型值为 1.2 V

典型值为 1.8、2.5 和 3.3 V

典型值为 1.8、2.5 和 3.3 V

典型值为 1.8、2.5 和 3.3 V

典型值为 1.8、2.5 和 3.3 V

I2C 和 JTAG 供电范围

1.15

典型值为 1.2、2.5 和 3.3 V

1.25

1.25

3.6

3.6

3.6

3.6

3.6

6

6

3.6

1.25

1.25

V

V

V

V

V

V

V

V

V

V

V

V

参数

VDD

AVDD

VIO1

VIO2

VIO3

VIO4

VIO5

VBATT

VBUS

CVDDQ

USB 供电电压

USB 供电电压

时钟供电电压

3.2

4.0

1.7

1.15

1.15

典型值为 3.7 V

典型值为 5 V

典型值为 1.8、3.3V

典型值为 1.2 V

典型值为 1.2 V

U3TXVDDQ

USB 3.0,1.2 V 的供电电压

U3RXVDDQ

USB 3.0,1.2 V 的供电电压

www.cypress.com

文档编号:001-88725 版本**

3

VBATVIO1VIO2VIO3VIO4VIO5VDDU3RXVDDQVBATT0.01uF0.1uFVIO10.01uF0.1uFVIO20.01uF0.1uFVIO30.01uF0.1uFVIO40.01uF0.1uFVIO50.01uF0.1uFVDD0.1uF22uFU3RXVDDQ0.1uF22uFVSSCVDDQ0.01uF0.1uFCVDDQAVDDAVDD0.1uF2.2uFU3TXVDDQU3TXVDDQ0.1uF22uFVBUS0.1uFVBUSAVSSU2AFEU3VSSU2PLL�

EZ-USB® FX3/FX3S™硬件设计指南和原理图的检查表

功耗模式

EZ-USB FX3 支持下列各功耗模式:

正常模式:全功能工作模式。在此模式下,内部 CPU

时钟和内部 PLL 都被使能。

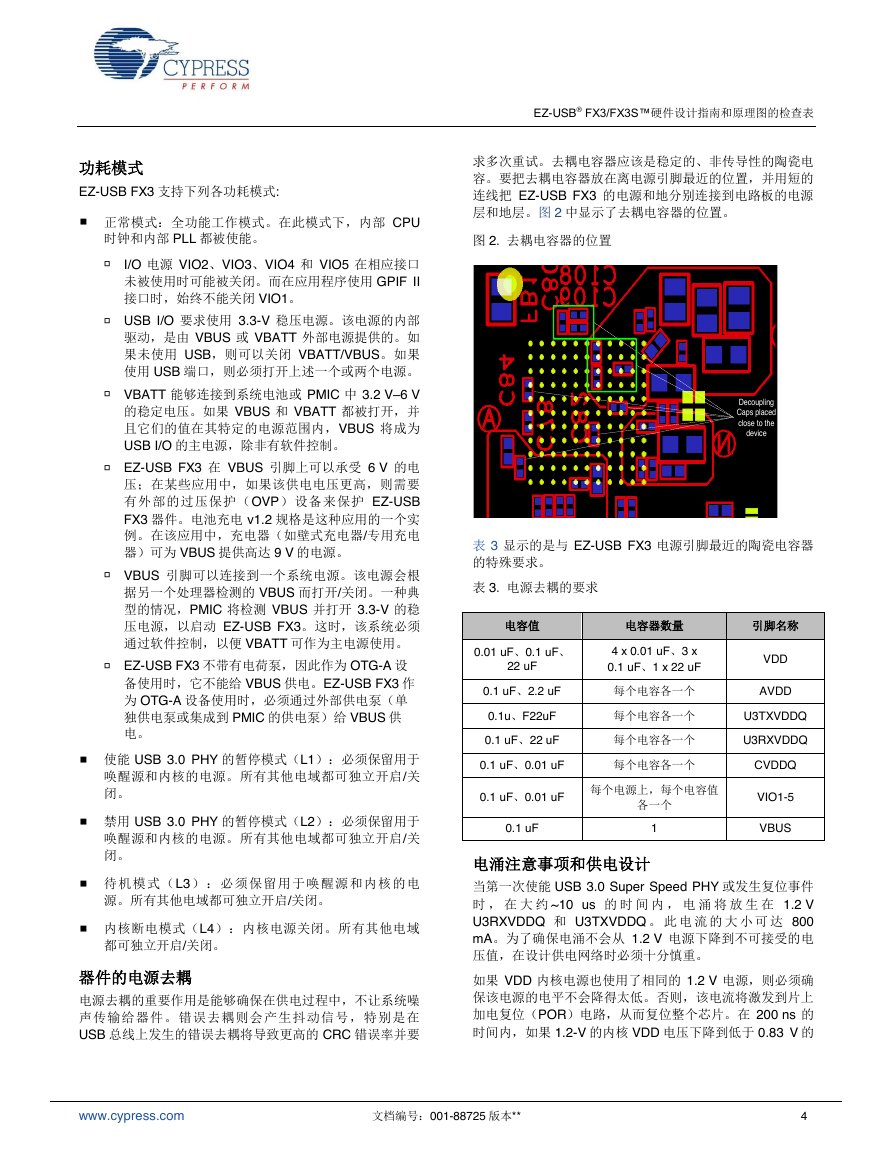

求多次重试。去耦电容器应该是稳定的、非传导性的陶瓷电

容。要把去耦电容器放在离电源引脚最近的位置,并用短的

连线把 EZ-USB FX3 的电源和地分别连接到电路板的电源

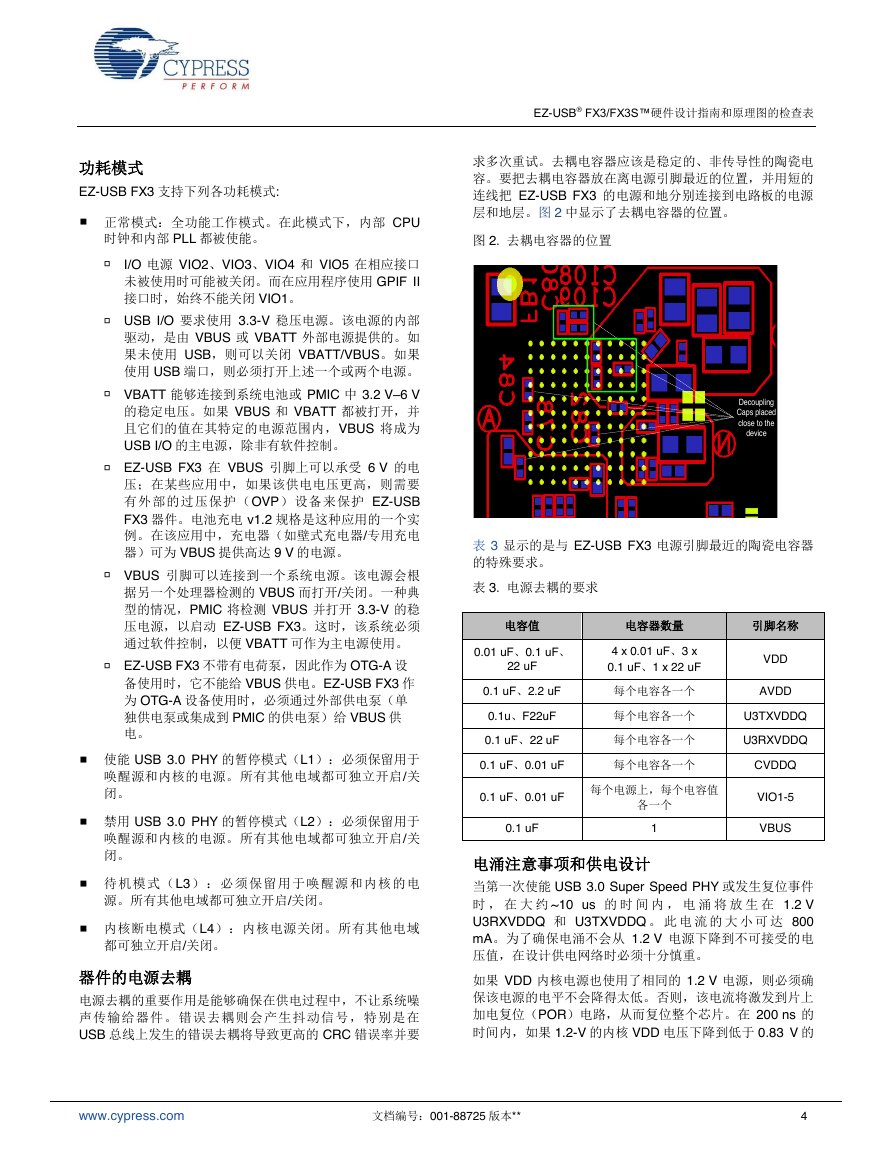

层和地层。图 2 中显示了去耦电容器的位置。

图 2. 去耦电容器的位置

I/O 电源 VIO2、VIO3、VIO4 和 VIO5 在相应接口

未被使用时可能被关闭。而在应用程序使用 GPIF II

接口时,始终不能关闭 VIO1。

USB I/O 要求使用 3.3-V 稳压电源。该电源的内部

驱动,是由 VBUS 或 VBATT 外部电源提供的。如

果未使用 USB,则可以关闭 VBATT/VBUS。如果

使用 USB 端口,则必须打开上述一个或两个电源。

VBATT 能够连接到系统电池或 PMIC 中 3.2 V–6 V

的稳定电压。如果 VBUS 和 VBATT 都被打开,并

且它们的值在其特定的电源范围内,VBUS 将成为

USB I/O 的主电源,除非有软件控制。

EZ-USB FX3 在 VBUS 引脚上可以承受 6 V 的电

压;在某些应用中,如果该供电电压更高,则需要

有外部的过压保护(OVP)设备来保护 EZ-USB

FX3 器件。电池充电 v1.2 规格是这种应用的一个实

例。在该应用中,充电器(如壁式充电器/专用充电

器)可为 VBUS 提供高达 9 V 的电源。

VBUS 引脚可以连接到一个系统电源。该电源会根

据另一个处理器检测的 VBUS 而打开/关闭。一种典

型的情况,PMIC 将检测 VBUS 并打开 3.3-V 的稳

压电源,以启动 EZ-USB FX3。这时,该系统必须

通过软件控制,以便 VBATT 可作为主电源使用。

EZ-USB FX3 不带有电荷泵,因此作为 OTG-A 设

备使用时,它不能给 VBUS 供电。EZ-USB FX3 作

为 OTG-A 设备使用时,必须通过外部供电泵(单

独供电泵或集成到 PMIC 的供电泵)给 VBUS 供

电。

使能 USB 3.0 PHY 的暂停模式(L1):必须保留用于

唤醒源和内核的电源。所有其他电域都可独立开启/关

闭。

禁用 USB 3.0 PHY 的暂停模式(L2):必须保留用于

唤醒源和内核的电源。所有其他电域都可独立开启/关

闭。

待机模式(L3):必须保留用于唤醒源和内核的电

源。所有其他电域都可独立开启/关闭。

内核断电模式(L4):内核电源关闭。所有其他电域

都可独立开启/关闭。

器件的电源去耦

电源去耦的重要作用是能够确保在供电过程中,不让系统噪

声传输给器件。错误去耦则会产生抖动信号,特别是在

USB 总线上发生的错误去耦将导致更高的 CRC 错误率并要

表 3 显示的是与 EZ-USB FX3 电源引脚最近的陶瓷电容器

的特殊要求。

表 3. 电源去耦的要求

电容值

电容器数量

引脚名称

0.01 uF、0.1 uF、

22 uF

4 x 0.01 uF、3 x

0.1 uF、1 x 22 uF

VDD

0.1 uF、2.2 uF

每个电容各一个

AVDD

0.1u、F22uF

每个电容各一个

U3TXVDDQ

0.1 uF、22 uF

每个电容各一个

U3RXVDDQ

0.1 uF、0.01 uF

每个电容各一个

CVDDQ

0.1 uF、0.01 uF

0.1 uF

每个电源上,每个电容值

各一个

1

VIO1-5

VBUS

电涌注意事项和供电设计

当第一次使能 USB 3.0 Super Speed PHY 或发生复位事件

时 , 在 大 约 ~10 us 的 时 间 内 , 电 涌 将 放 生 在 1.2 V

U3RXVDDQ 和 U3TXVDDQ 。 此 电 流 的 大 小 可 达 800

mA。为了确保电涌不会从 1.2 V 电源下降到不可接受的电

压值,在设计供电网络时必须十分慎重。

如果 VDD 内核电源也使用了相同的 1.2 V 电源,则必须确

保该电源的电平不会降得太低。否则,该电流将激发到片上

加电复位(POR)电路,从而复位整个芯片。在 200 ns 的

时间内,如果 1.2-V 的内核 VDD 电压下降到低于 0.83 V 的

www.cypress.com

文档编号:001-88725 版本**

4

Decoupling Caps placed close to the device�

值,则 POR 电路将被破坏。必须设计 1.2-V 电源网络,以

便在发生涌入事件时,VDD 不会低于 0.83 V。为了达到此

目的,需要结合使用去耦电容器(如数据手册中所指定)、

电感器扼流圈和电压调节器的输出阻抗。

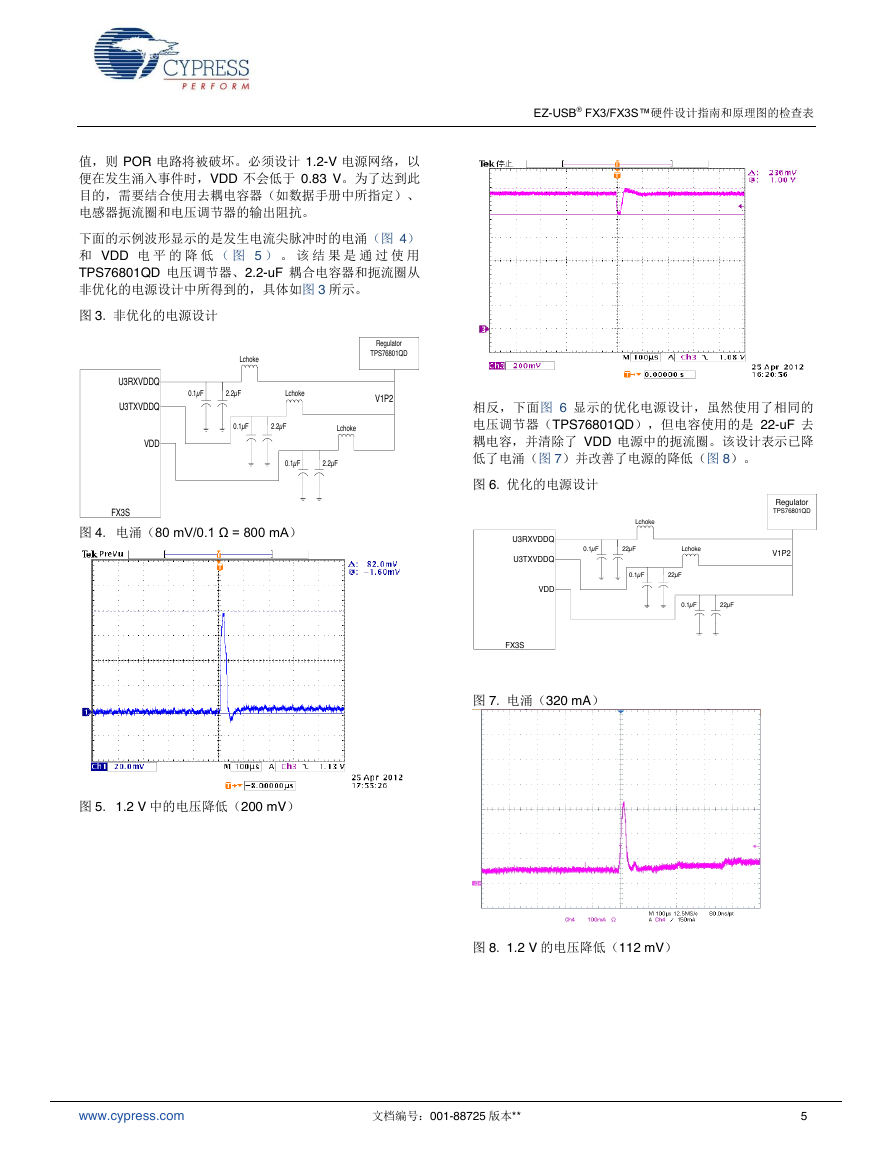

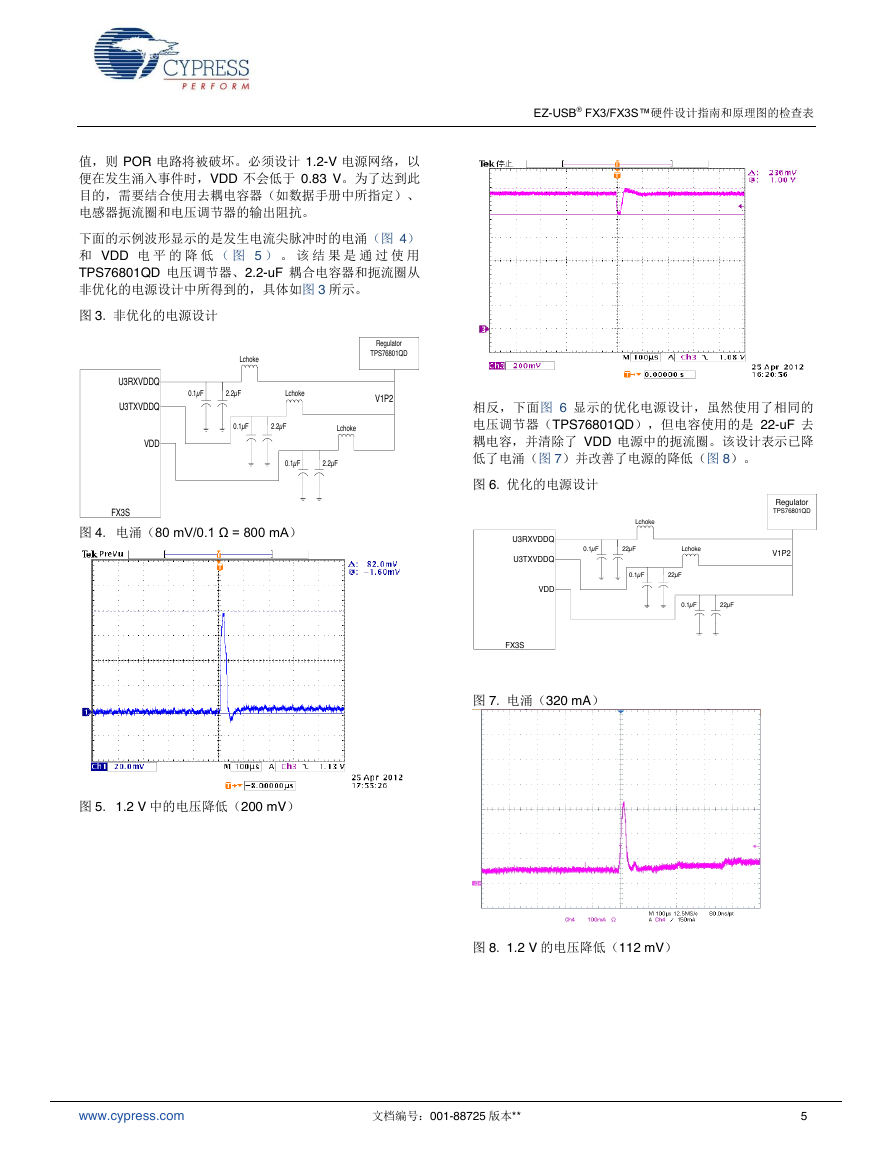

下面的示例波形显示的是发生电流尖脉冲时的电涌(图 4)

和 VDD 电 平 的 降 低 ( 图 5 ) 。 该 结 果 是 通 过 使 用

TPS76801QD 电压调节器、2.2-uF 耦合电容器和扼流圈从

非优化的电源设计中所得到的,具体如图 3 所示。

图 3. 非优化的电源设计

EZ-USB® FX3/FX3S™硬件设计指南和原理图的检查表

相反,下面图 6 显示的优化电源设计,虽然使用了相同的

电压调节器(TPS76801QD),但电容使用的是 22-uF 去

耦电容,并清除了 VDD 电源中的扼流圈。该设计表示已降

低了电涌(图 7)并改善了电源的降低(图 8)。

图 6. 优化的电源设计

图 4. 电涌(80 mV/0.1 Ω = 800 mA)

图 7. 电涌(320 mA)

图 5. 1.2 V 中的电压降低(200 mV)

图 8. 1.2 V 的电压降低(112 mV)

www.cypress.com

文档编号:001-88725 版本**

5

U3RXVDDQU3TXVDDQVDDFX3S0.1µF2.2µF0.1µF2.2µF0.1µF2.2µFLchokeLchokeLchokeRegulator TPS76801QD V1P2U3RXVDDQU3TXVDDQVDDFX3S0.1µF22µF0.1µF22µF0.1µF22µFLchokeLchokeRegulator TPS76801QD V1P2�

EZ-USB® FX3/FX3S™硬件设计指南和原理图的检查表

公式 1. 晶振的驱动电平

可以兼容的晶振的驱动电平不能超过该晶振的功率限制。可

以 兼 容 的 晶 振 的 示 例 如 表 5 所 示 。 请 注 意 , 只 有

NX3225SA 符合 EZ-USB FX3 的特性,其他晶振通过使用

公式 1 作为示例。

表 5. 晶振选择

数据手册

中 R1 的

最大值

(欧姆)

CL

eqv

(pF)

C0

(pF)

估算值

40

80

50

50

40

6

6

6

6

6

3

3

3

3

3

使用公式

1

(uW)

的驱动电

平

82

171

107

107

82

最大驱动

电平

(Spec)

uW

100

300

200

200

100

器件

Epson FA-

H20

ITTI I16

NX2520SA

NX3225SA

Saronix-FL

用户可以选择具有相同规格的任何电压调节器。

时钟

EZ-USB FX3 器件使用频率为 19.2-MHz 的晶振或 19.2

MHz、26 MHz、38.4 MHz 或 52 MHz 的任何时钟作为时钟

源。

晶振

晶振连接如图 9 所示。

图 9. 晶振电流

表 4 显示的是 19.2-MHz 晶振的要求。

表 4. 晶振要求

参数

容差

温度范围

负载电容

驱动电平

规格

±100

-40 到 85

12

使用公式 1

单位

ppm

°F

pF

mW

该晶振的功耗由 XTAL-OUT 引脚的驱动电平(在 EZ-USB

FX3 器 件 中 , 该 电 平 为 1.32 V ) 、 所 需 的 频 率

(19.2 MHz)以及晶振的等效电阻来确定。

www.cypress.com

文档编号:001-88725 版本**

6

�

EZ-USB® FX3/FX3S™硬件设计指南和原理图的检查表

时钟

EZ-USB FX3 的输入时钟必须符合下表中具体规定的相位噪

声和时序抖动要求。

表 6. 时钟要求

表 8. 看门狗定时器的要求

参数

占空比

频率偏差

最小值 最大值

单位

40

_

60

%

±200

ppm

规格

参数

说明

相位噪声

100 Hz 偏移

1 kHz 偏移

10 kHz 偏移

100 kHz 偏移

1 MHz 偏移

最大频率偏差

占空比

过冲

下冲

上升时间/下降

时间

最小

值

_

_

_

_

_

_

30

_

_

_

最大

值

-75

-104

-120

-128

-130

单位

dB

dB

dB

dB

dB

150

ppm

70

3

-3

%

%

%

3

ns

根据所选定的时钟、频率、FSLC[2:0] 各线路可通过弱上拉

电阻连接到电源,或连接到地。表 7 显示的是用于不同时

钟的各个 FSLC[2:0]值。

表 7. 频率选择配置

FSLC[2]

FSLC[1]

FSLC[0]

晶振/时钟频率

0

0

0

1

1

0

0

1

0

1

19.2 MHz 的晶振

19.2 MHz 的输入时钟

26 MHz 的输入时钟

38.4 MHz 的输入时钟

52 MHz 输入时钟

0

1

1

1

1

CVDDQ 是与时钟输入相关的电源。它和外部时钟输入(若

有)的电压值是相同的。

如果只使用外部时钟输入,XTALIN 和 XTALOUT 引脚会保

持为未连接的状态。如果只使用晶振时钟,CLKIN 引脚会

保持未连接状态。

看门狗定时器

在待机模式下,运行看门狗定时器时可以使用 32.768 kHz

的时钟输入。该时钟输入由外部时钟源供电。

GPIF II 接口

EZ-USB FX3 具有高性能的通用可编程接口,即 GPIF II。

该接口与 FX2LP 的 GPIF 和从器件 FIFO 接口的功能相

似,但更先进。有关 GPIF 接口的更多详细信息,请参考应

用手册 AN75779 — 将图像传感器连接到 USB 视频类别

(UVC)框架中的 EZ-USB® FX3™和 AN75779 — 将图像

传感器连接到 USB 视频类别(UVC)框架中的 EZ-USB®

FX3™。

下述内容介绍的是 EZ-USB FX3 的 GPIF II 接口的通用设计

指南。

GPIF II 接口的最大频率是 100 MHz。推荐将 GPIF II

总线上的所有信号线长度在 500 (mils)密耳的范围内

匹配。推荐使用 22 Ω 的串联终端电阻

GPIF 线的长度大于 5 英寸或经过一个过孔会引起阻抗

的失配。这时,我们推荐使用 EZ-USB FX3 IBIS 模型

来 仿 真 信 号 的 抖 动 。 该 EZ-USB FX3 IBIS 存 在 于

CYUSB3KIT-001 EZ-USB® FX3™并带有端点。

在所有的同步接口中,推荐使用 GPIO[16] (PCLK)

作为 GPIF II 时钟信号。

进行 FX3 启动时,GPIO[32:30] (PMODE[2:0])信号

将进行相应的配置。启动后,这些信号可作为 GPIO 使

用。

INT#信号不能作为 GPIO 使用。

注:GPIF II 配置为 32 位模式时,SPI 接口的信号线不可

用。

I2C 接口

EZ-USB FX3 具有一个与 I2C 总线规格版本 3 相兼容的 I2C

接口。EZ-USB FX3 的 I2C 接口只能作为 I2C 主控运行。例

如,EZ-USB FX3 可从连接至 I2C 接口的 EEPROM 引导,

它是可选的引导选项。EZ-USB FX3 的 I2C 主控制器也支持

多主控模式功能。

I2C 接口采用 VIO5 供电,该电压独立于其他串行外设。这

样,I2C 接口可以灵活地在不相同的电压下工作,这个不同

于其他串行接口。

I2C 控制器所支持的总线频率为 100 kHz、400 kHz 和 1

MHz。当 VIO5 为 1.2 V 时,支持的最大工作频率为 100

www.cypress.com

文档编号:001-88725 版本**

7

�

EZ-USB® FX3/FX3S™硬件设计指南和原理图的检查表

kHz。当 VIO5 为 1.8 V、2.5 V 或 3.3 V 时,支持的工作频

率为 400 kHz 和 1 MHz。

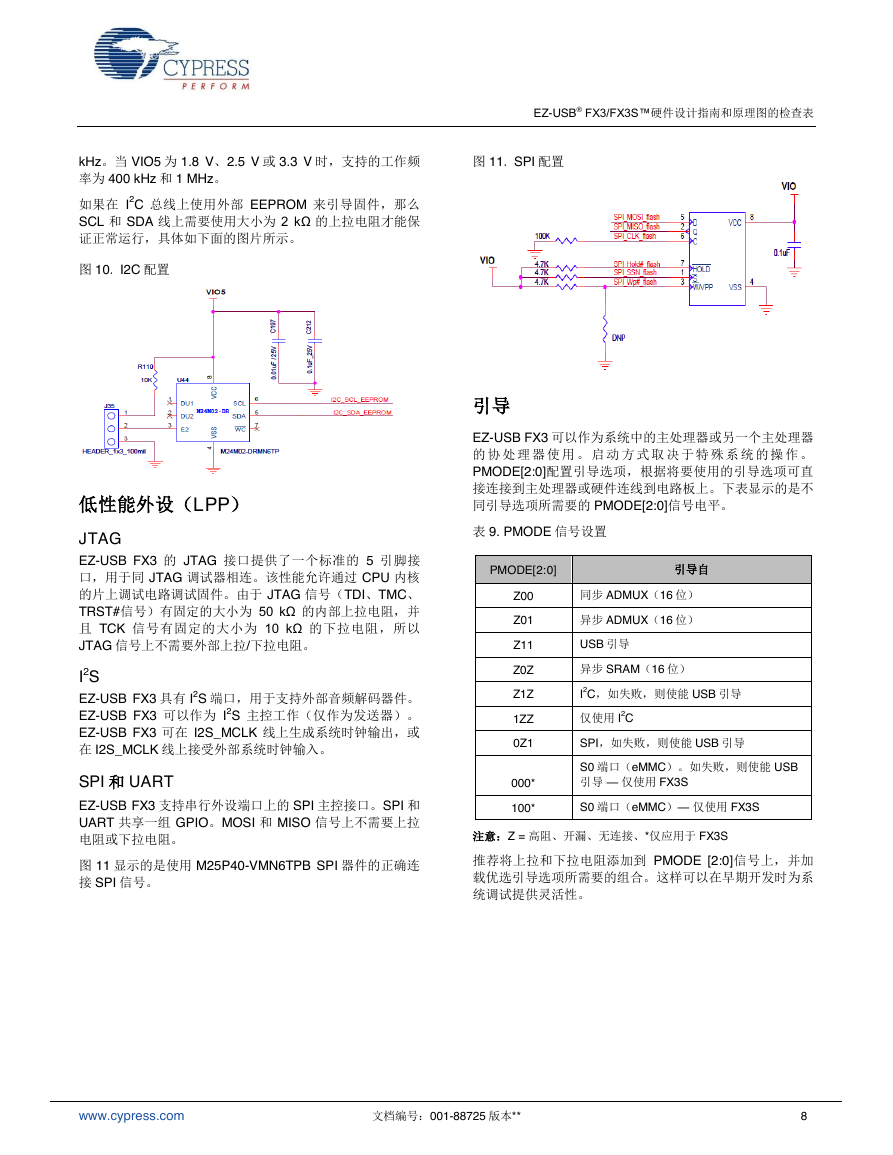

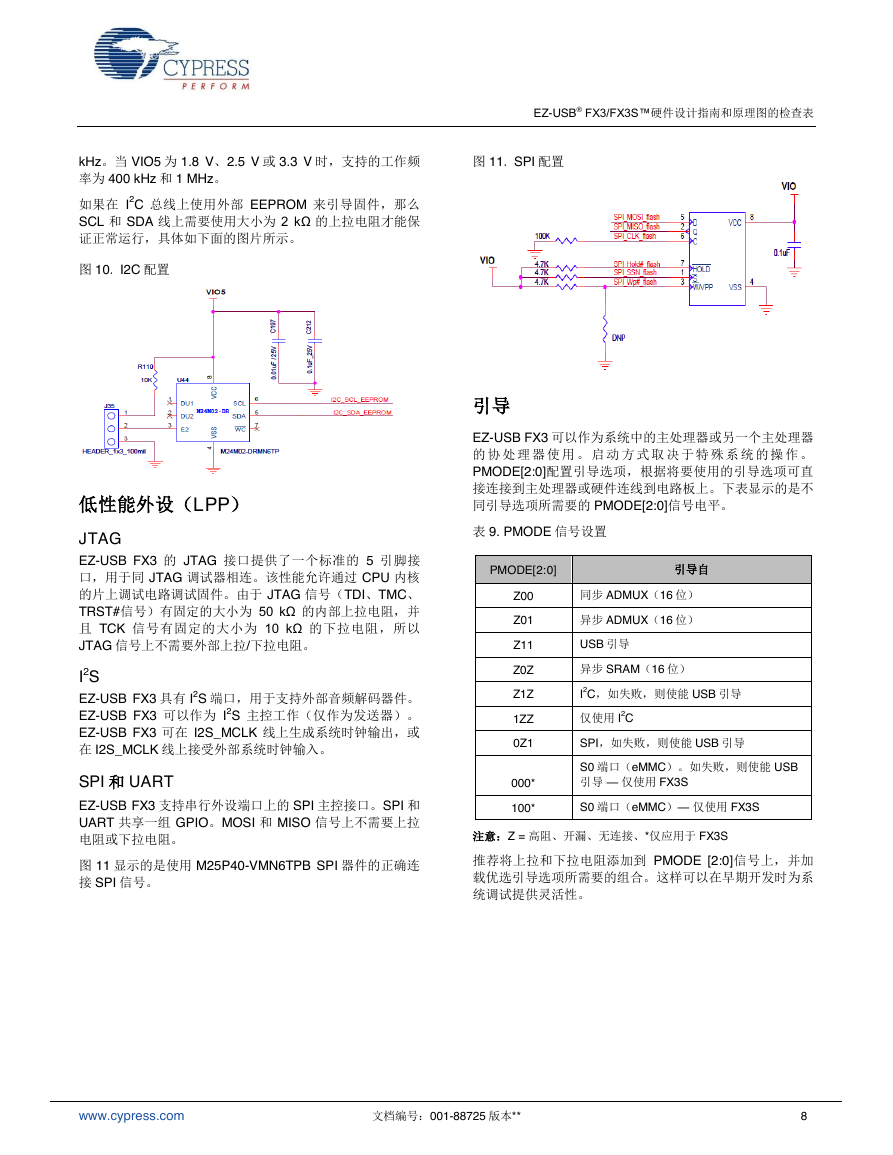

图 11. SPI 配置

如果在 I2C 总线上使用外部 EEPROM 来引导固件,那么

SCL 和 SDA 线上需要使用大小为 2 kΩ 的上拉电阻才能保

证正常运行,具体如下面的图片所示。

图 10. I2C 配置

引导

EZ-USB FX3 可以作为系统中的主处理器或另一个主处理器

的 协 处 理 器 使 用 。 启 动 方 式 取 决 于 特 殊 系 统 的 操 作 。

PMODE[2:0]配置引导选项,根据将要使用的引导选项可直

接连接到主处理器或硬件连线到电路板上。下表显示的是不

同引导选项所需要的 PMODE[2:0]信号电平。

低性能外设(LPP)

JTAG

EZ-USB FX3 的 JTAG 接口提供了一个标准的 5 引脚接

口,用于同 JTAG 调试器相连。该性能允许通过 CPU 内核

的片上调试电路调试固件。由于 JTAG 信号(TDI、TMC、

TRST#信号)有固定的大小为 50 kΩ 的内部上拉电阻,并

且 TCK 信号有固定的大小为 10 kΩ 的下拉电阻,所以

JTAG 信号上不需要外部上拉/下拉电阻。

I2S

EZ-USB FX3 具有 I2S 端口,用于支持外部音频解码器件。

EZ-USB FX3 可以作为 I2S 主控工作(仅作为发送器)。

EZ-USB FX3 可在 I2S_MCLK 线上生成系统时钟输出,或

在 I2S_MCLK 线上接受外部系统时钟输入。

SPI 和 UART

EZ-USB FX3 支持串行外设端口上的 SPI 主控接口。SPI 和

UART 共享一组 GPIO。MOSI 和 MISO 信号上不需要上拉

电阻或下拉电阻。

图 11 显示的是使用 M25P40-VMN6TPB SPI 器件的正确连

接 SPI 信号。

表 9. PMODE 信号设置

PMODE[2:0]

引导自

Z00

Z01

Z11

Z0Z

Z1Z

1ZZ

0Z1

000*

100*

同步 ADMUX(16 位)

异步 ADMUX(16 位)

USB 引导

异步 SRAM(16 位)

I2C,如失败,则使能 USB 引导

仅使用 I2C

SPI,如失败,则使能 USB 引导

S0 端口(eMMC)。如失败,则使能 USB

引导 — 仅使用 FX3S

S0 端口(eMMC)— 仅使用 FX3S

注意:Z = 高阻、开漏、无连接、*仅应用于 FX3S

推荐将上拉和下拉电阻添加到 PMODE [2:0]信号上,并加

载优选引导选项所需要的组合。这样可以在早期开发时为系

统调试提供灵活性。

www.cypress.com

文档编号:001-88725 版本**

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc