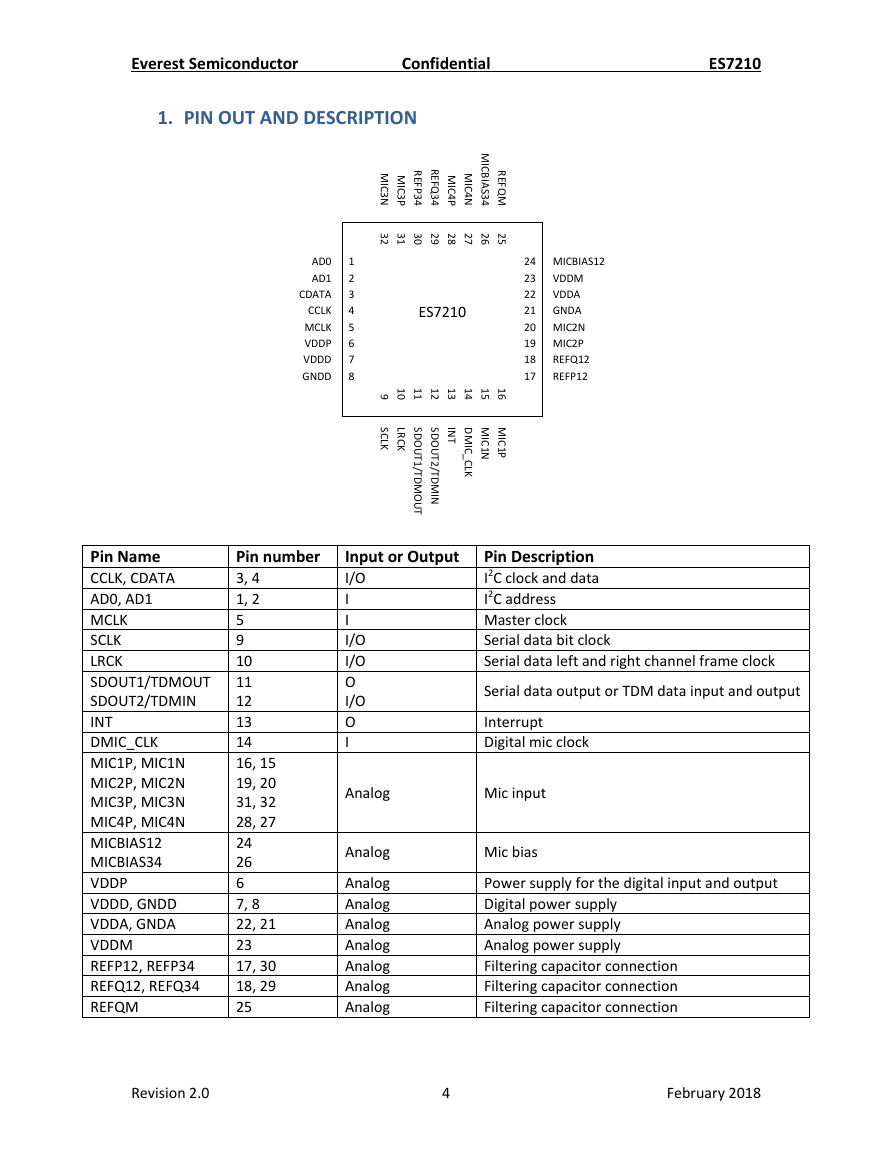

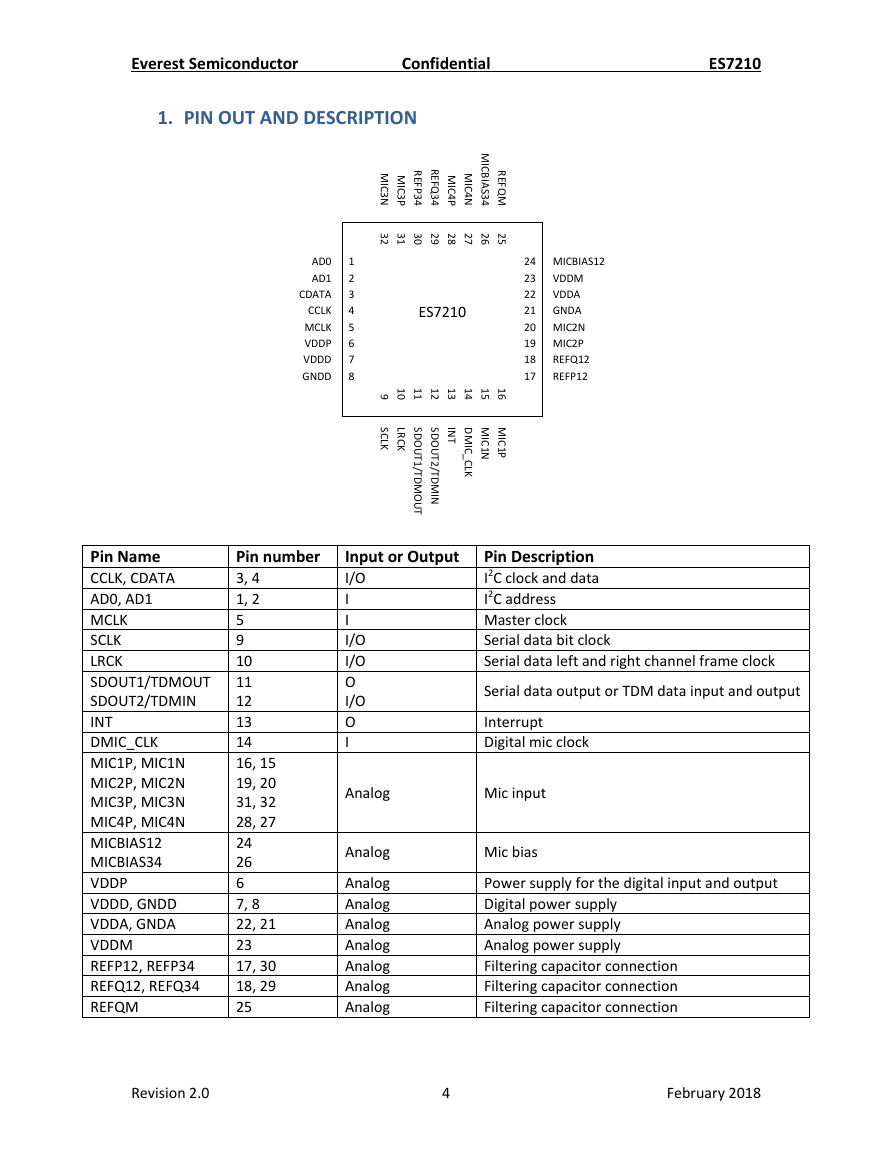

1. Pin Out and Description

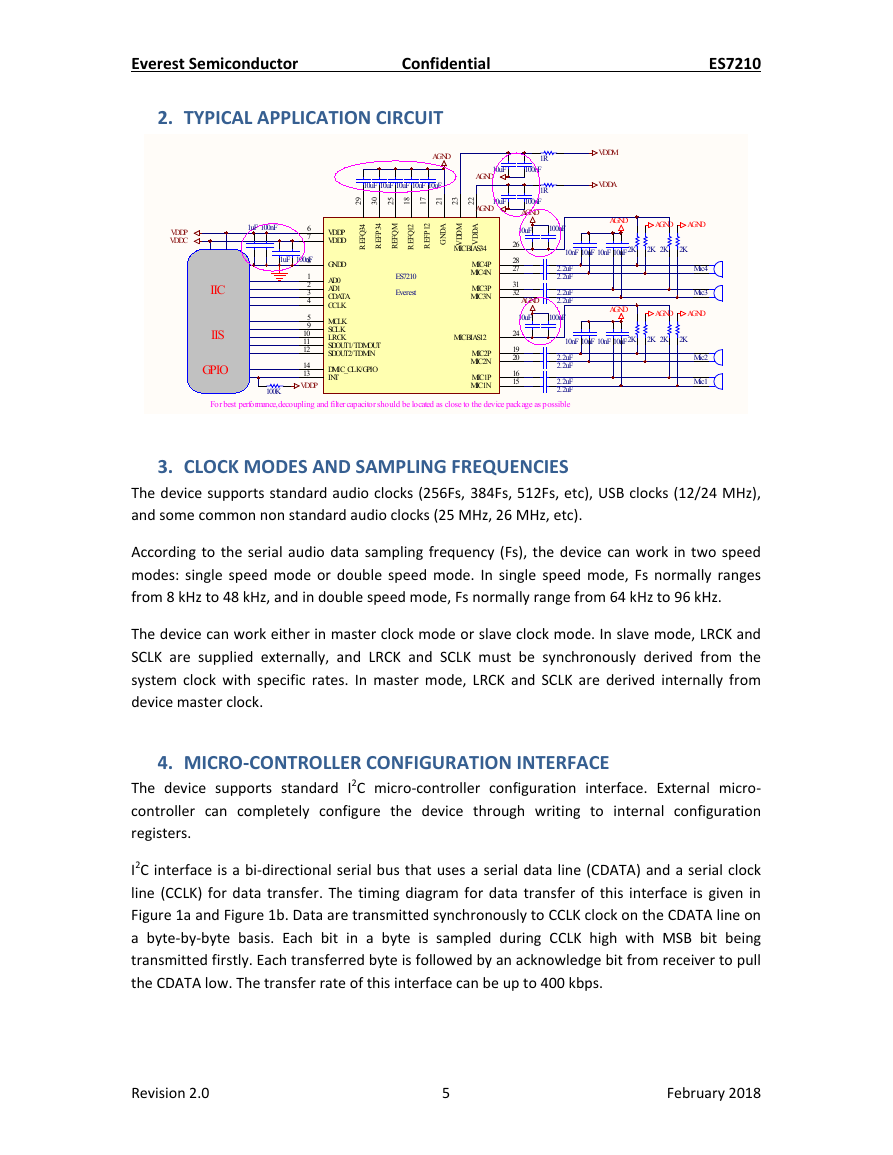

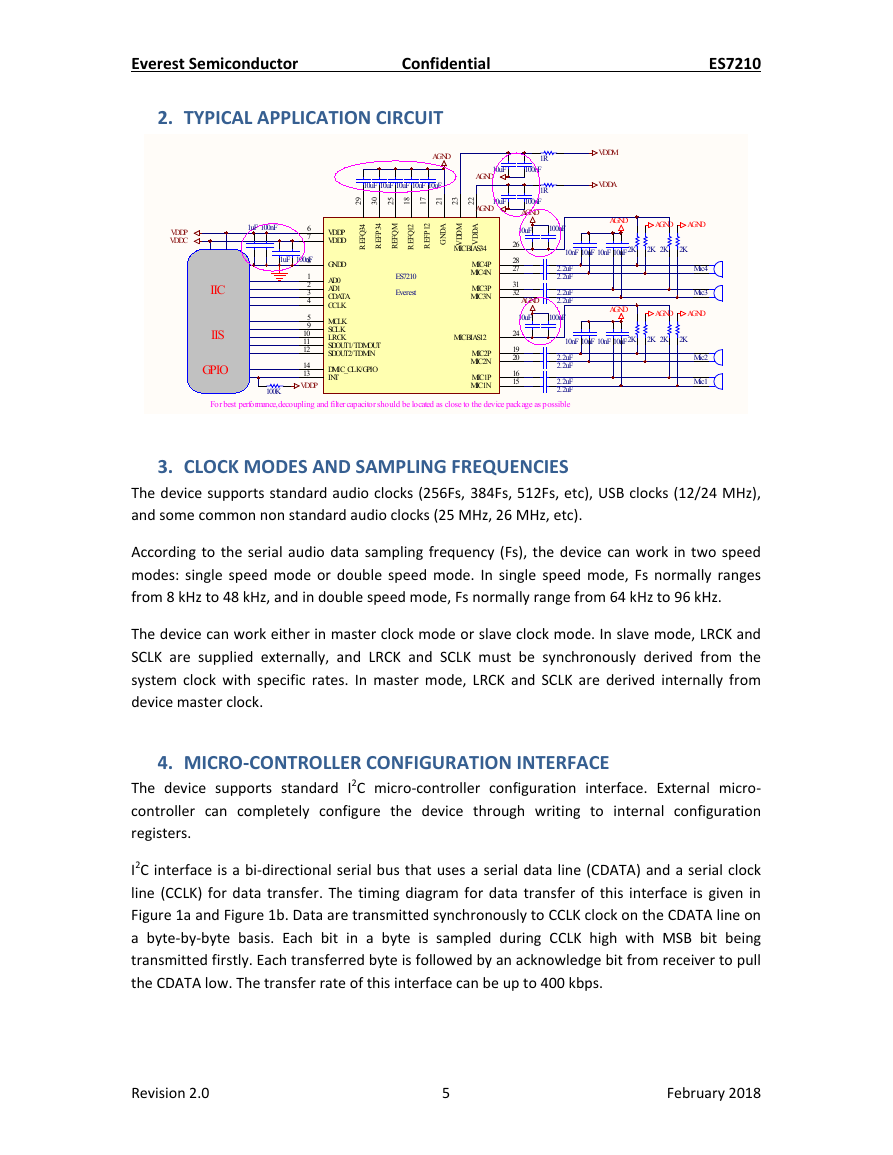

2. typical APPLICATION CIRCUIT

3. Clock Modes and Sampling Frequencies

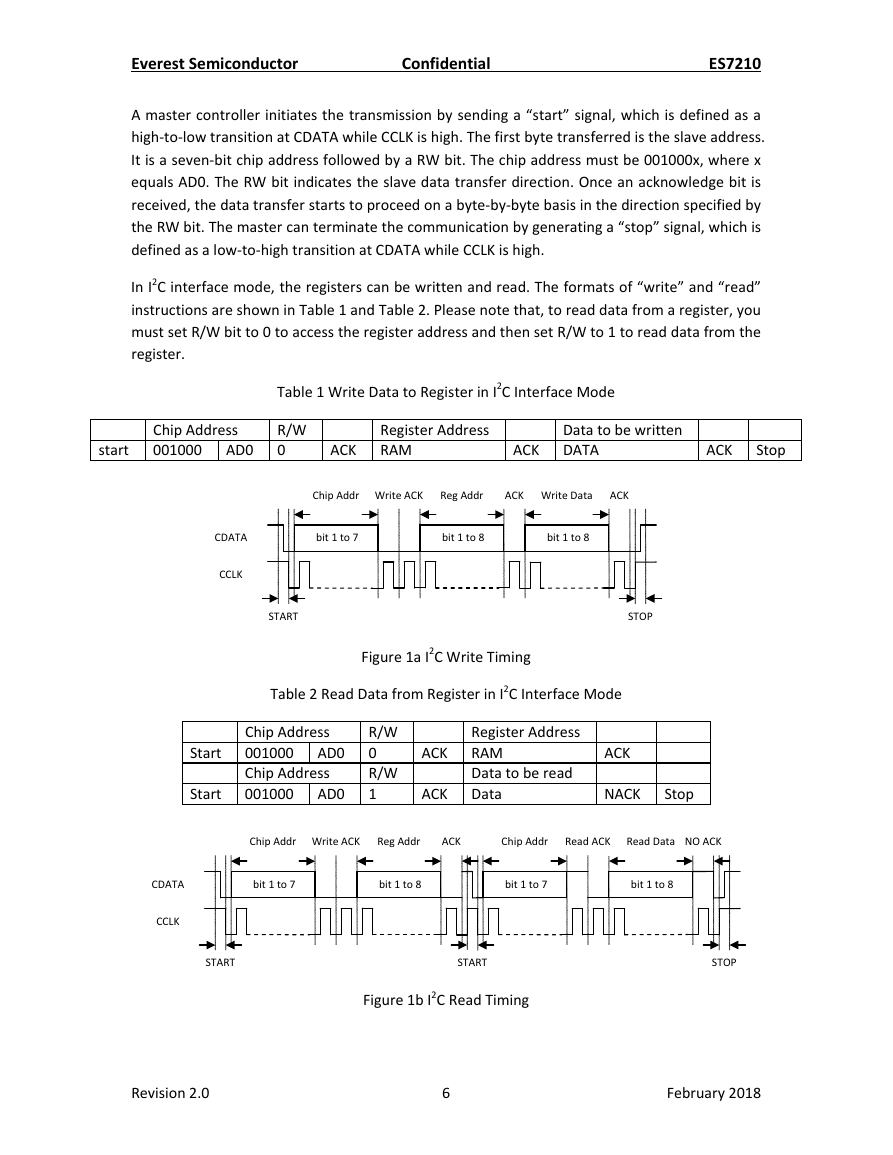

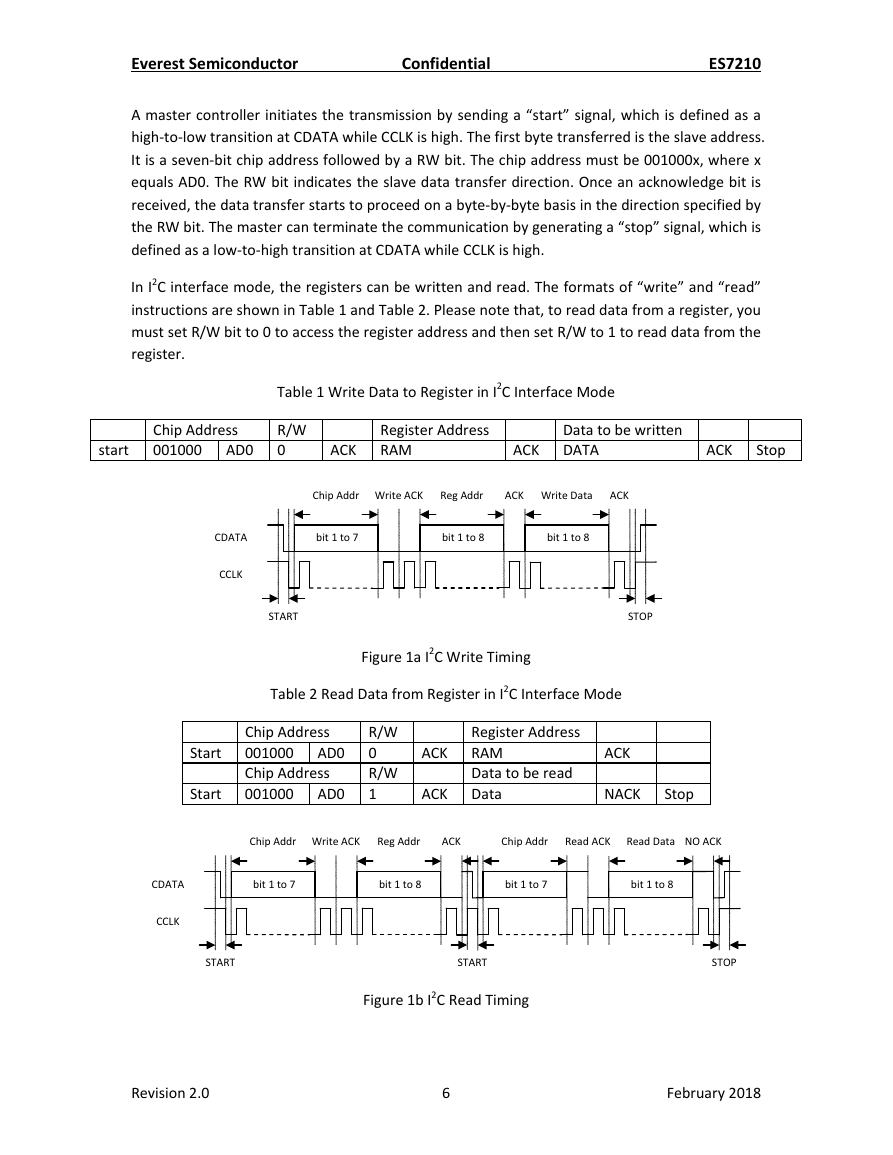

4. Micro-controller configuration Interface

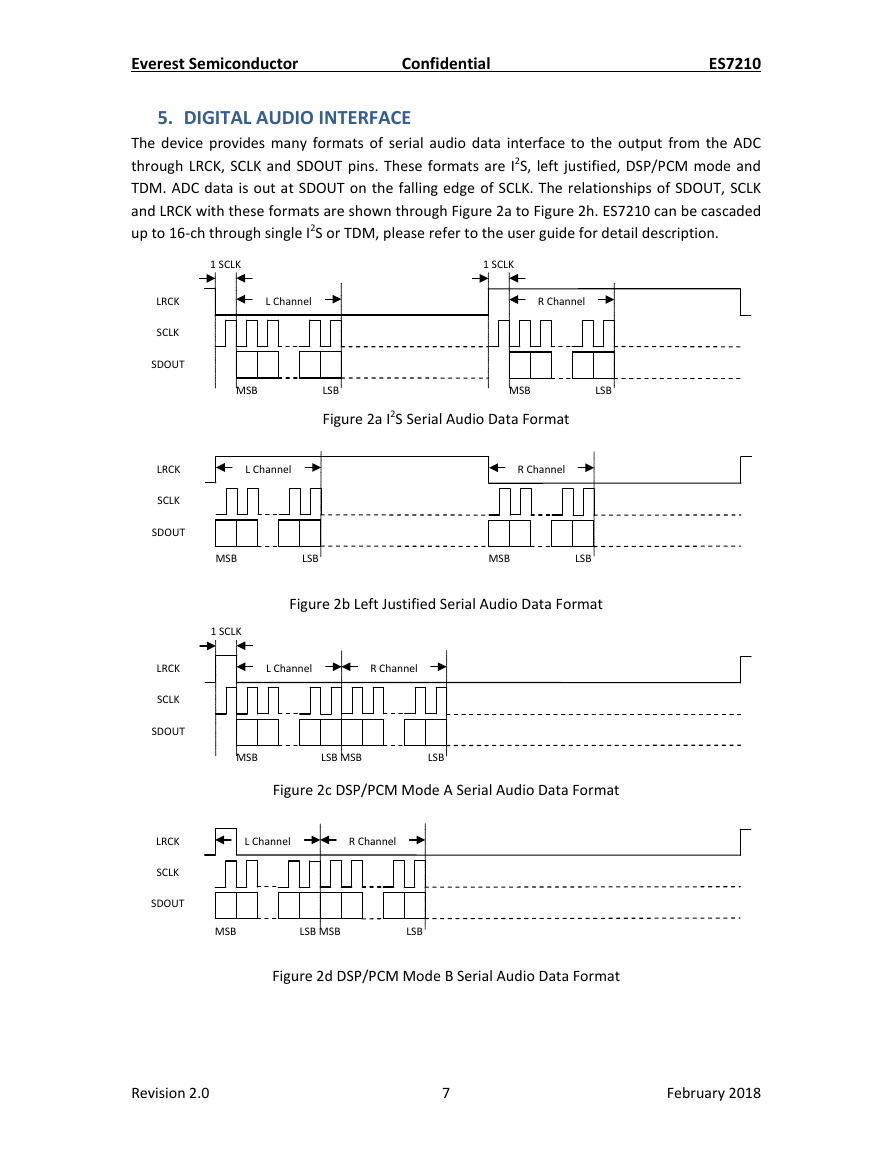

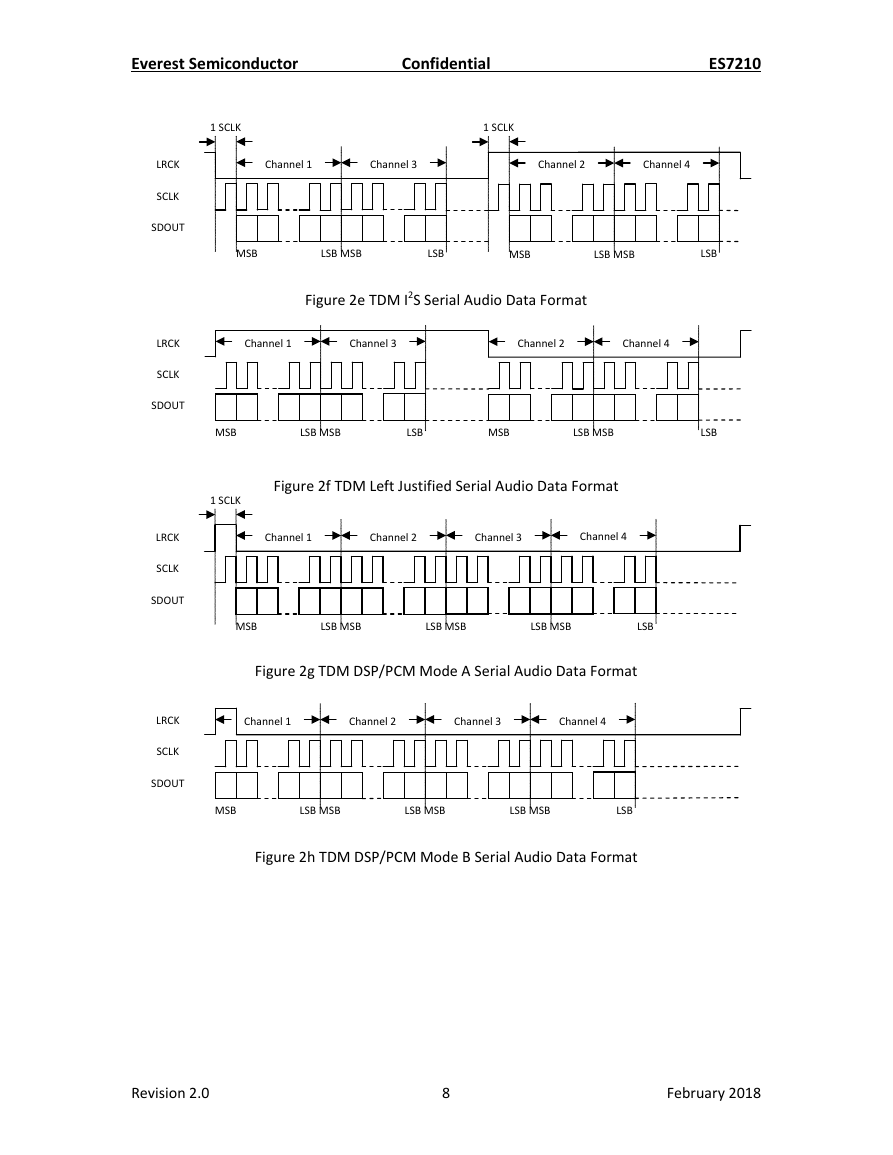

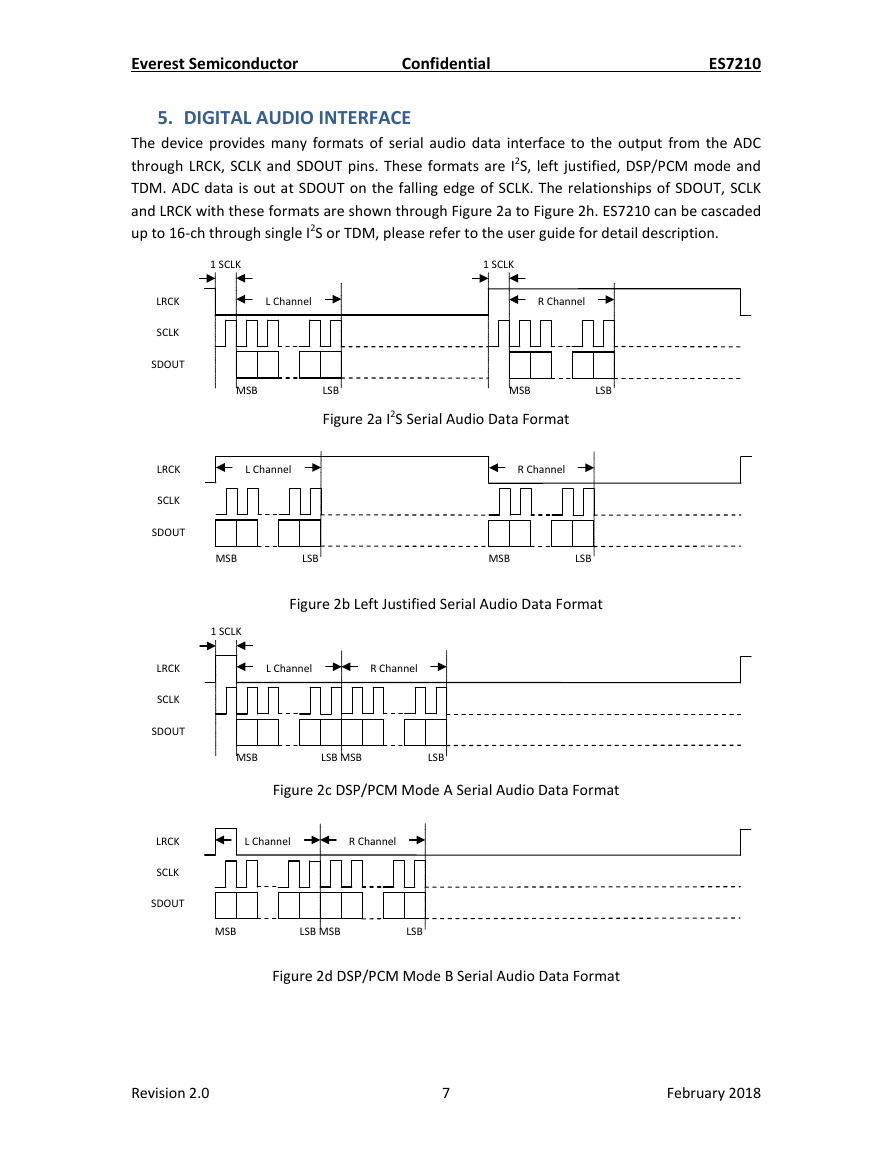

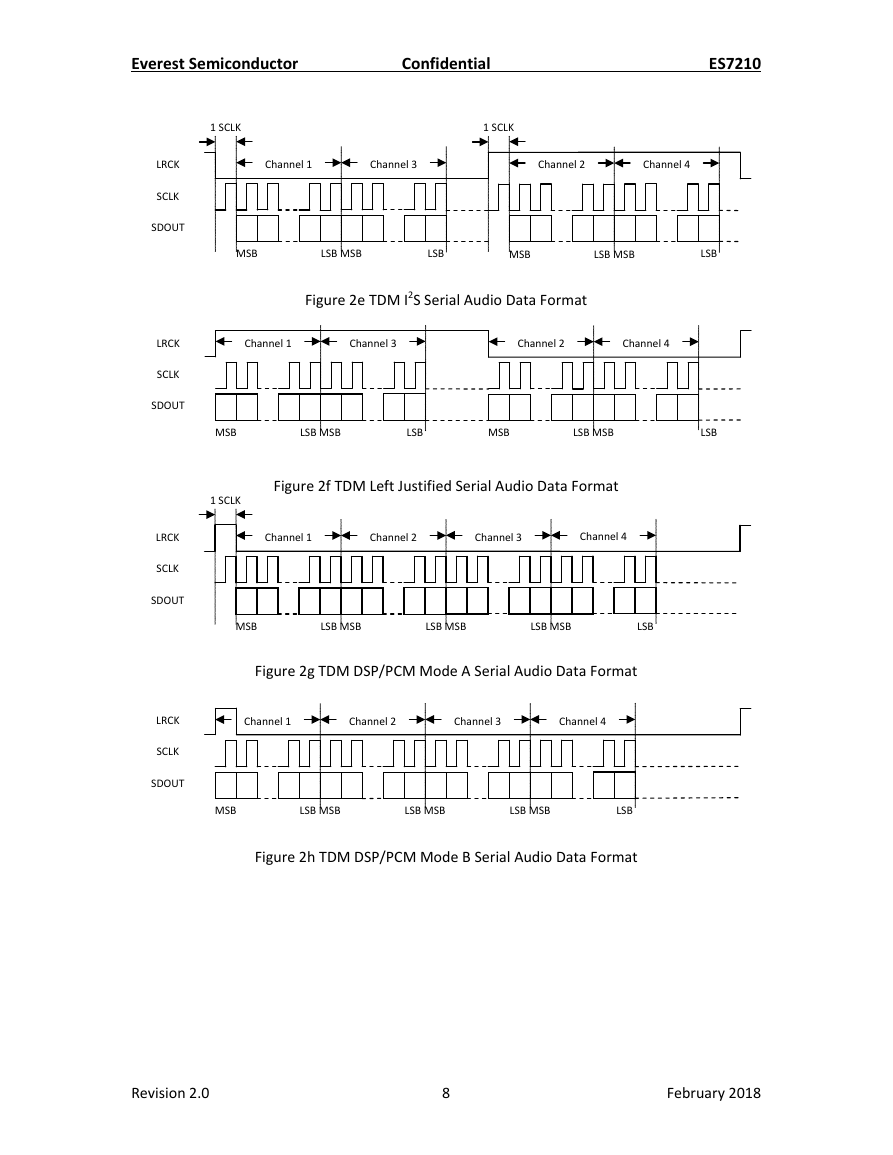

5. Digital Audio Interface

6. ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings

Recommended Operating Conditions

ADC Analog and Filter Characteristics and Specifications

Power Consumption Characteristics

Serial Audio Port Switching Specifications

I2C Switching Specifications

7. Configuration Register Definition

Register 0x00 – Reset control, Default 00110010

Register 0x01 – clock off, Default 00100000

Register 0x02 – main clock control, Default 00000010

Register 0x03 – Master clock control, Default 00000100

Register 0x04 – Master LRCK divider 1, Default 00000001

Register 0x05 – master lrck divider 0, Default 00000000

Register 0x06 – power down, Default 00000000

Register 0x07 – adc osr config, Default 00100000

Register 0x08 – mode config, Default 00010000

Register 0x09 – time control 0 for chip initialization, Default 01000000

Register 0x0A – time control 1 for chip initialization, Default 01000000

Register 0x0B – chip status, Default 00000000

Register 0x0C – interrupt control, Default 00000000

Register 0x0D – misc. control, Default 00001001

Register 0x10 – dmic control, Default 00000000

Register 0x11 – sdp interface config 1, Default 00000000

Register 0x12 – sdp interface config 2, Default 00000000

Register 0x13 – adc automute control, Default 00000000

Register 0x14 – adc34 mute control, Default 00000000

Register 0x15 – adc12 mute control, Default 00000000

Register 0x16 – alc select, Default 00000000

Register 0x17 – alc common config 1, Default 00000000

Register 0x18 – adc34 ALC level, Default 11110111

Register 0x19 – adc12 ALC level, Default 11110111

Register 0x1a – alc common config2, Default 00000000

Register 0x1b – adc4 max gain, Default 10111111

Register 0x1c – adc3 max gain, Default 10111111

Register 0x1d – adc2 max gain, Default 10111111

Register 0x1e – adc1 max gain, Default 10111111

Register 0x20 – adc34 hpf2, Default 00100110

Register 0x21 – adc34 hpf1, Default 00100110

Register 0x22 – ADc12 hpf1, Default 00000110

Register 0x23 – ADC12 HPF2, Default 00100110

Register 0x24 to 3x37 – EQ COEFficients automaticlly generated by matlab

Register 0x3d – CHIP ID1, Default 01110010

Register 0x3e – CHIP ID0, Default 00010000

Register 0x3f – chip VERSION, Default 00000000

Register 0x40 – ANALOG SYSTEM, Default 10000000

Register 0x41 – MIC1/2 BIAS, Default 01110001

Register 0x42 – MIC3/4 BIAS, Default 01110001

Register 0x43 – MIC1 GAIN, Default 00000000

Register 0x44 – MIC2 GAIN, Default 00000000

Register 0x45 – MIC3 GAIN, Default 00000000

Register 0x46 – MIC4 GAIN, Default 00000000

Register 0x47 – MIC1 LOW POWER, Default 00000000

Register 0x48 – MIC2 LOW POWER, Default 00000000

Register 0x49 – MIC3 LOW POWER, Default 00000000

Register 0x4a – MIC4 LOW POWER, Default 00000000

Register 0x4b – MIC1/2 POWER DOWN, Default 11111111

Register 0x4c – MIC3/4 POWER DOWN, Default 11111111

8. Package

9. CORPORATe INFORMATION

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc