Xilinx ISE 与 Modelsim 联合调试平台搭建

版本:V1.0

邮箱:648636762@qq.com

安装环境:Windows 7(X64),Xilinx ISE Design Suite 14.4(D:\Xilinx\14.4),Modelsim

10.1b(D:\modeltech_10.1b)。对于版本的选择,建议采用较新的版本进行配套,Modelsim10.1b

采用 32 位或者 64 位均可,这里我采用 32 位版本。

Xilinx ISE 与 Modelsim 的安装顺序随意。

首先安装 Xilinx_ISE_DS_14.4_P.49d.3.0,安装大约需要 20G 左右的硬盘空间,所以安

装路径建议选择非系统盘进行安装,其他设置均按默认操作即可,以实验室四核电脑作为例

子,安装过程大概需要持续一个小时,请耐心等待。

Note:安装过程中请关闭所以的杀毒软件和防火墙,并拔出除鼠标外的其他 USB 设备

以加快安装速度。

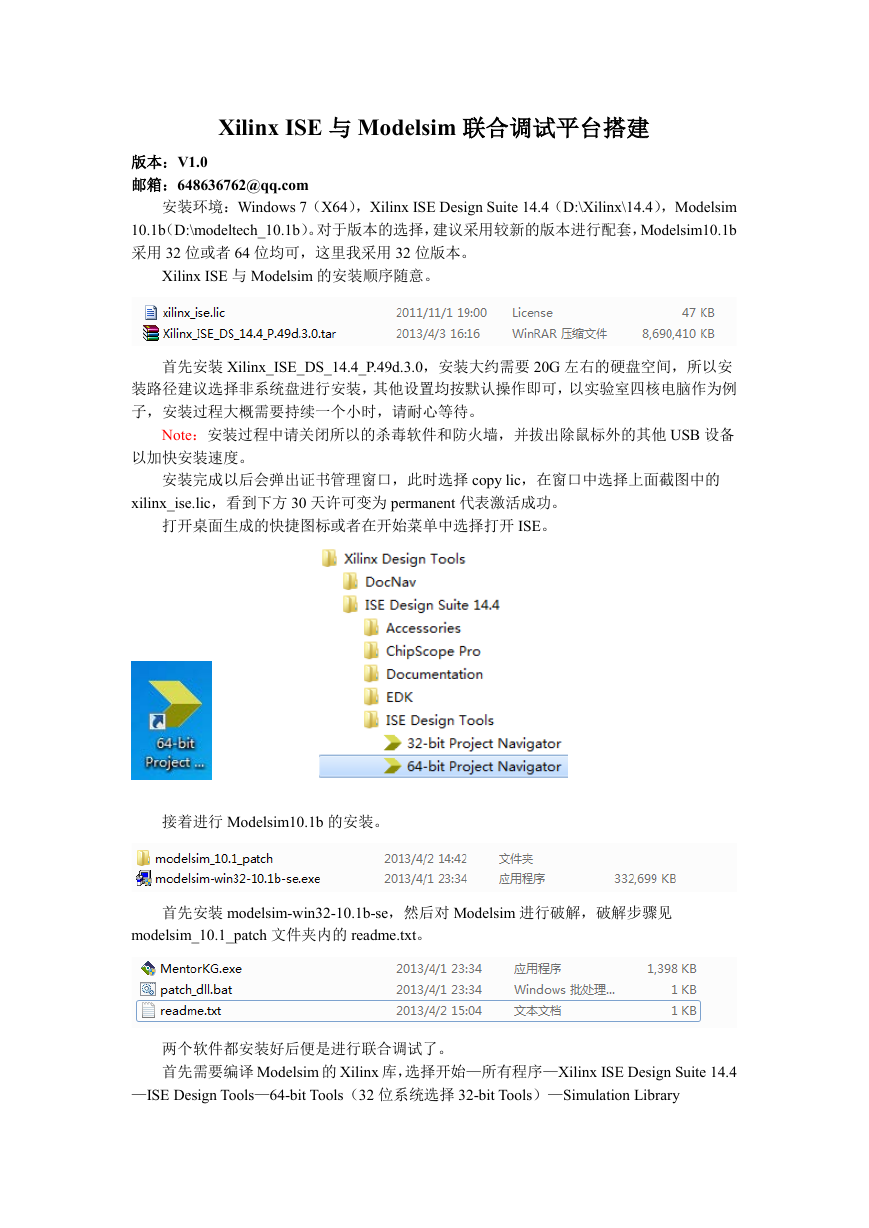

安装完成以后会弹出证书管理窗口,此时选择 copy lic,在窗口中选择上面截图中的

xilinx_ise.lic,看到下方 30 天许可变为 permanent 代表激活成功。

打开桌面生成的快捷图标或者在开始菜单中选择打开 ISE。

接着进行 Modelsim10.1b 的安装。

首先安装 modelsim-win32-10.1b-se,然后对 Modelsim 进行破解,破解步骤见

modelsim_10.1_patch 文件夹内的 readme.txt。

两个软件都安装好后便是进行联合调试了。

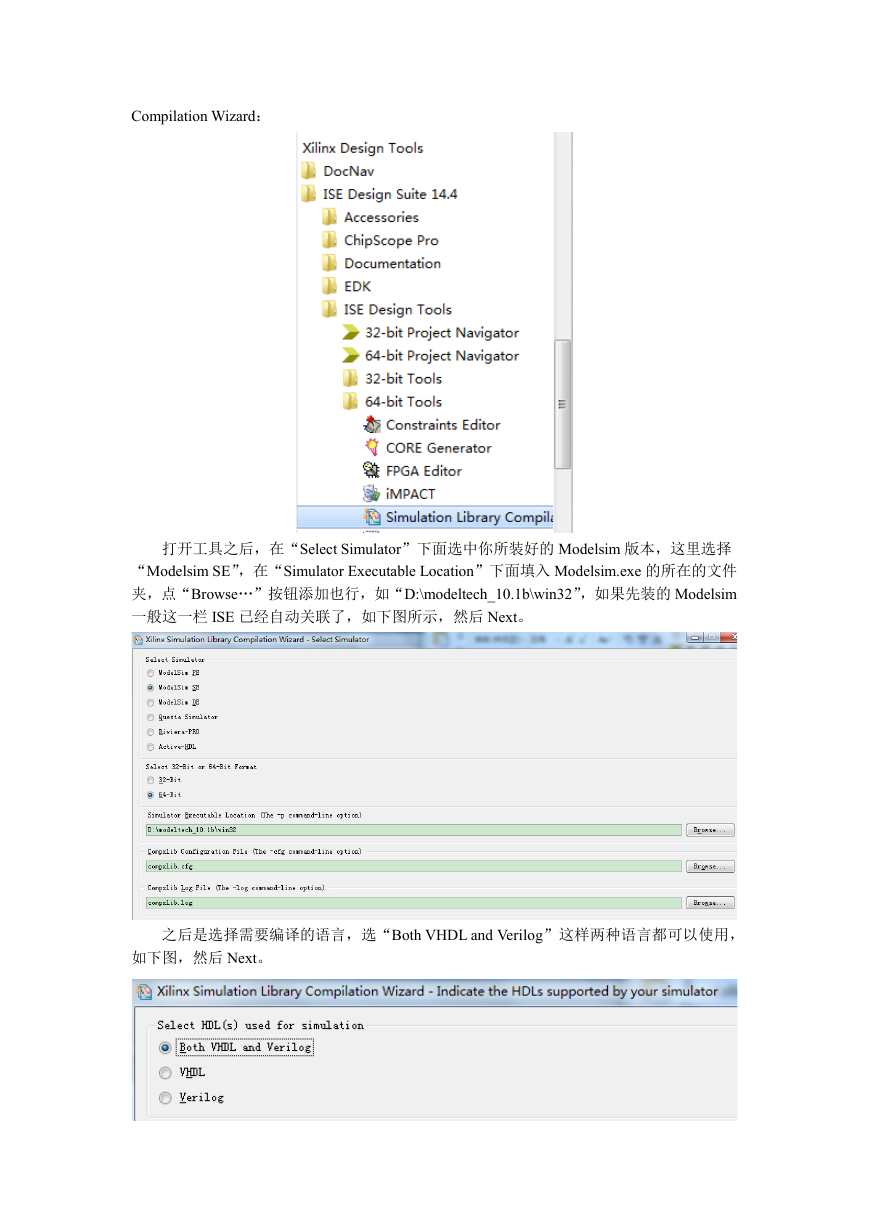

首先需要编译 Modelsim 的 Xilinx 库,选择开始—所有程序—Xilinx ISE Design Suite 14.4

—ISE Design Tools—64-bit Tools(32 位系统选择 32-bit Tools)—Simulation Library

�

Compilation Wizard:

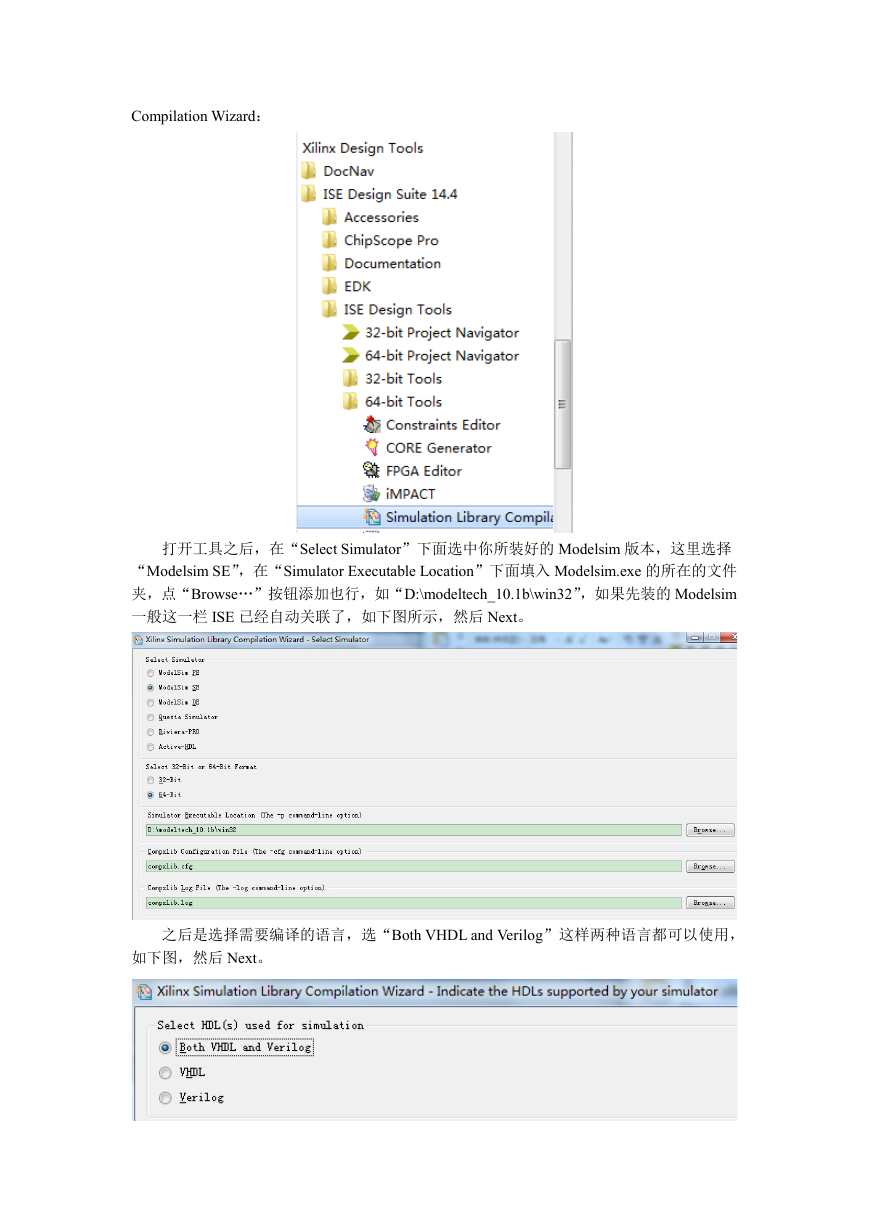

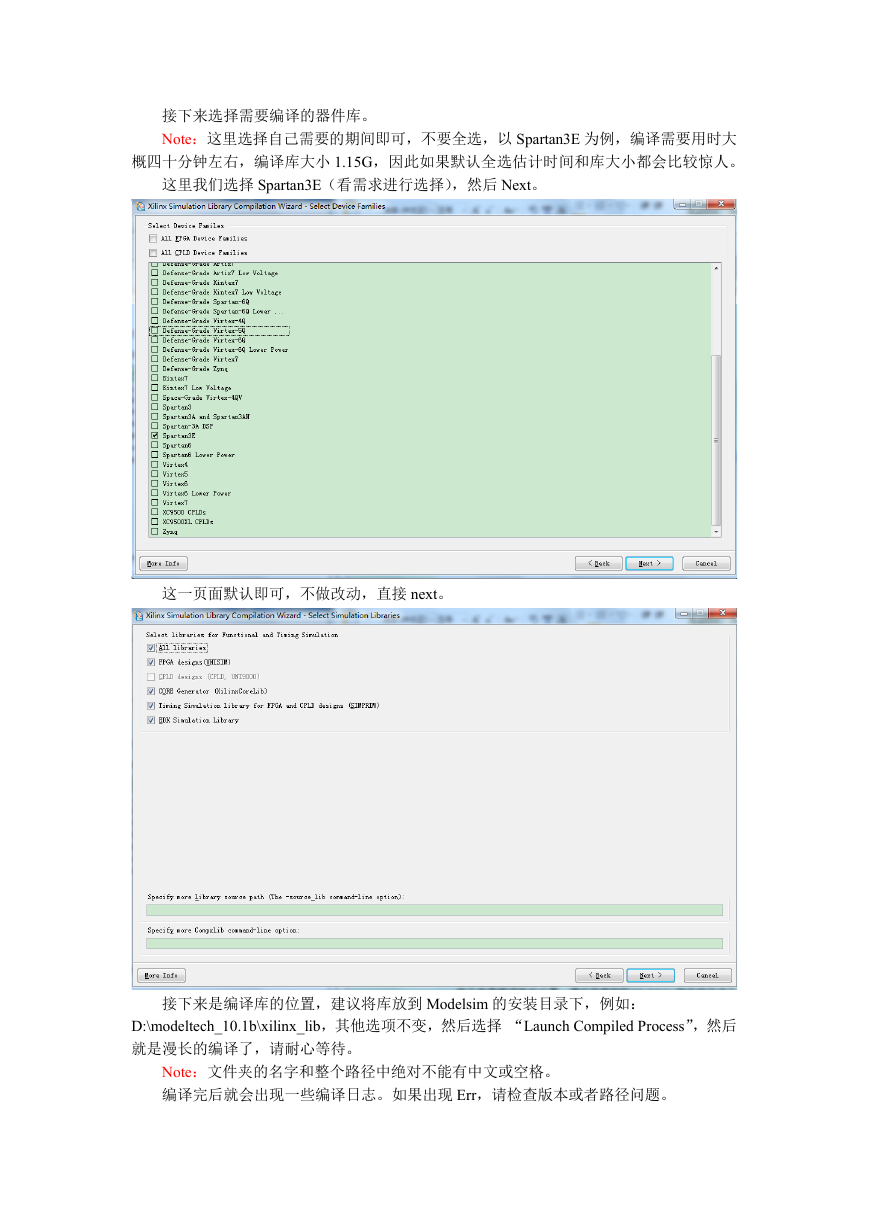

打开工具之后,在“Select Simulator”下面选中你所装好的 Modelsim 版本,这里选择

“Modelsim SE”,在“Simulator Executable Location”下面填入 Modelsim.exe 的所在的文件

夹,点“Browse…”按钮添加也行,如“D:\modeltech_10.1b\win32”,如果先装的 Modelsim

一般这一栏 ISE 已经自动关联了,如下图所示,然后 Next。

之后是选择需要编译的语言,选“Both VHDL and Verilog”这样两种语言都可以使用,

如下图,然后 Next。

�

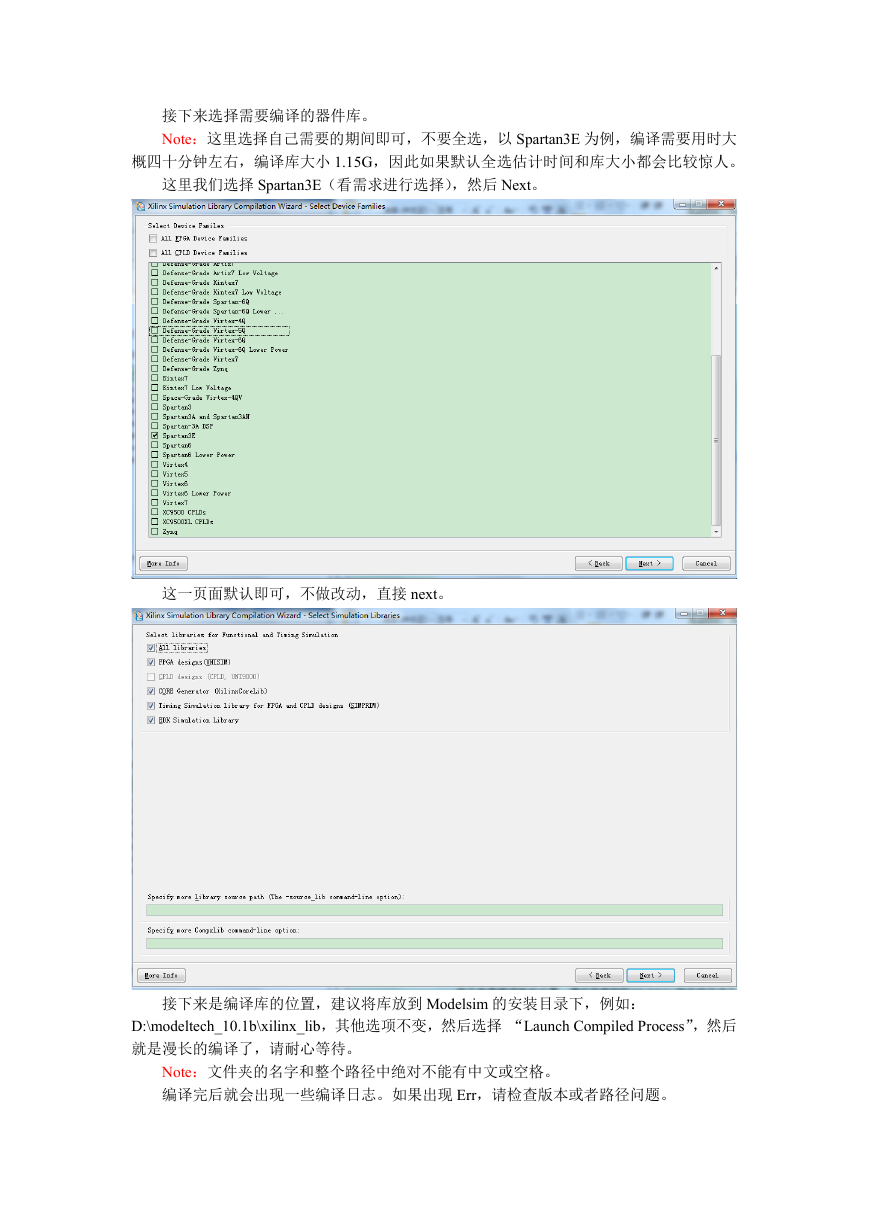

接下来选择需要编译的器件库。

Note:这里选择自己需要的期间即可,不要全选,以 Spartan3E 为例,编译需要用时大

概四十分钟左右,编译库大小 1.15G,因此如果默认全选估计时间和库大小都会比较惊人。

这里我们选择 Spartan3E(看需求进行选择),然后 Next。

这一页面默认即可,不做改动,直接 next。

接下来是编译库的位置,建议将库放到 Modelsim 的安装目录下,例如:

D:\modeltech_10.1b\xilinx_lib,其他选项不变,然后选择 “Launch Compiled Process”,然后

就是漫长的编译了,请耐心等待。

Note:文件夹的名字和整个路径中绝对不能有中文或空格。

编译完后就会出现一些编译日志。如果出现 Err,请检查版本或者路径问题。

�

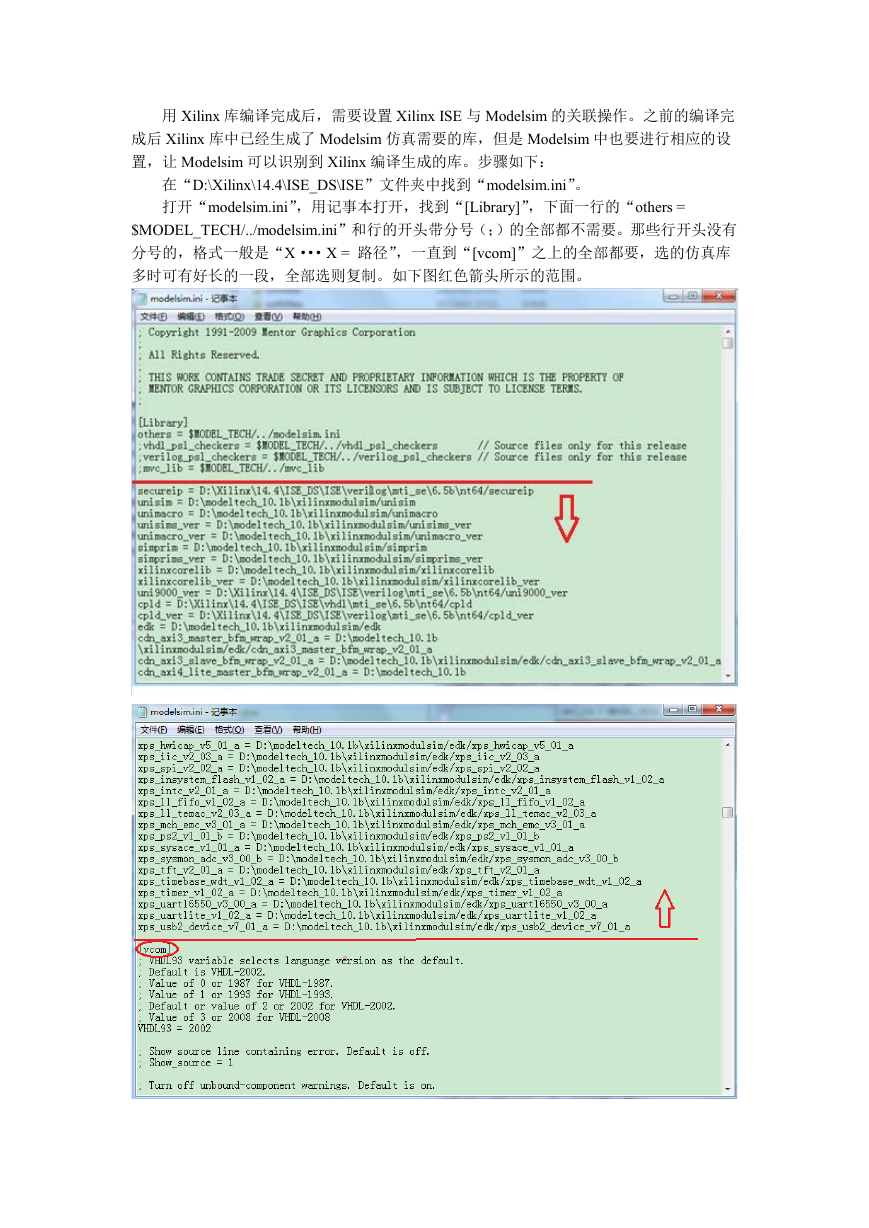

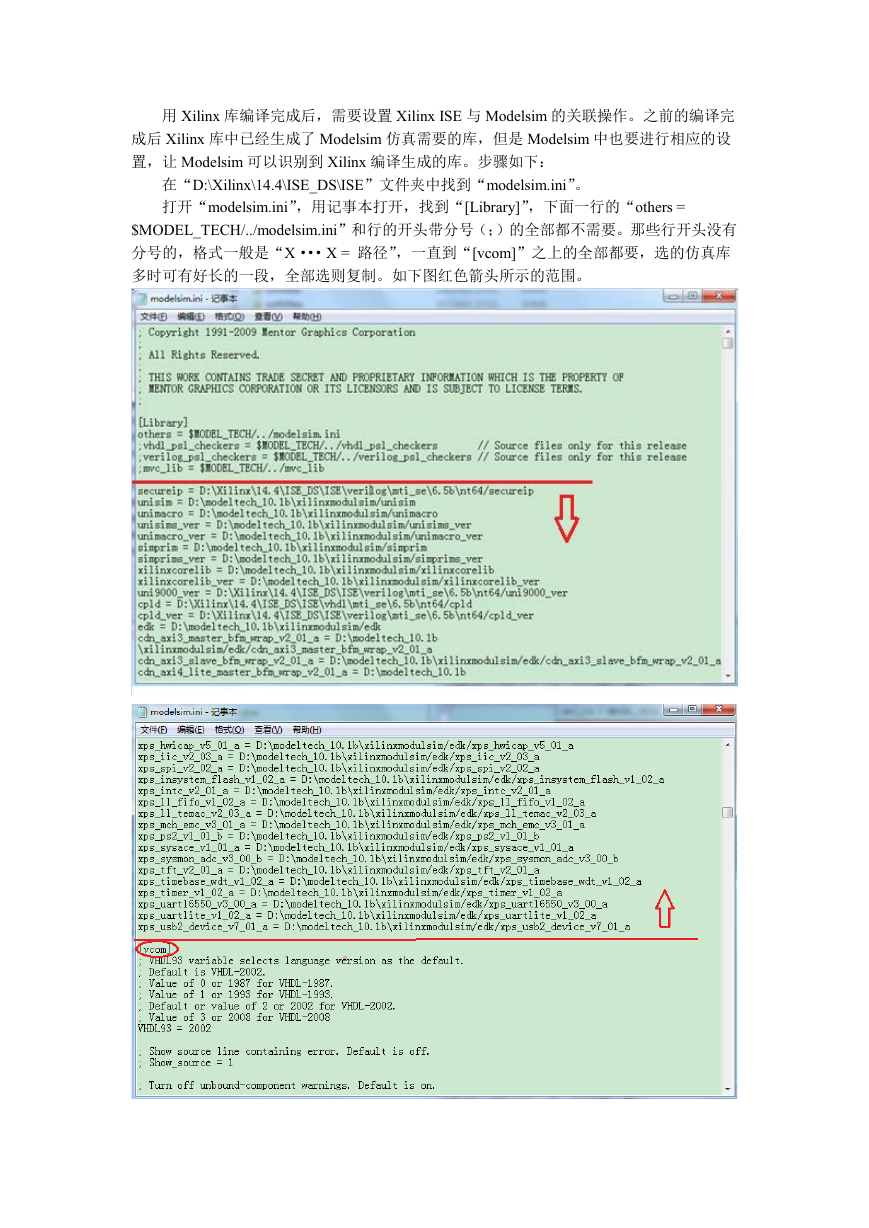

用 Xilinx 库编译完成后,需要设置 Xilinx ISE 与 Modelsim 的关联操作。之前的编译完

成后 Xilinx 库中已经生成了 Modelsim 仿真需要的库,但是 Modelsim 中也要进行相应的设

置,让 Modelsim 可以识别到 Xilinx 编译生成的库。步骤如下:

在“D:\Xilinx\14.4\ISE_DS\ISE”文件夹中找到“modelsim.ini”。

打开“modelsim.ini”,用记事本打开,找到“[Library]”,下面一行的“others =

$MODEL_TECH/../modelsim.ini”和行的开头带分号(;)的全部都不需要。那些行开头没有

分号的,格式一般是“X···X = 路径”,一直到“[vcom]”之上的全部都要,选的仿真库

多时可有好长的一段,全部选则复制。如下图红色箭头所示的范围。

�

然后在 Modelsim 的安装目录下,例如“D:\modeltech_10.1b”,找到“modelsim.ini”,(右

键选择属性,去掉只读。

Note:如果打开后很乱的话,建议不要使用记事本打开,可以选择写字板,或者使用其

他文本编辑工具。

打开后,同样是找到“[Library]”,在它的下面粘贴上刚刚复制的所有内容,如下图红

线位置。注意,行开头不要有分号,注意不要覆盖原有内容。只要在“[Library]”和“[vcom]”

之间粘贴就行,然后保存,设置文件属性为只读。

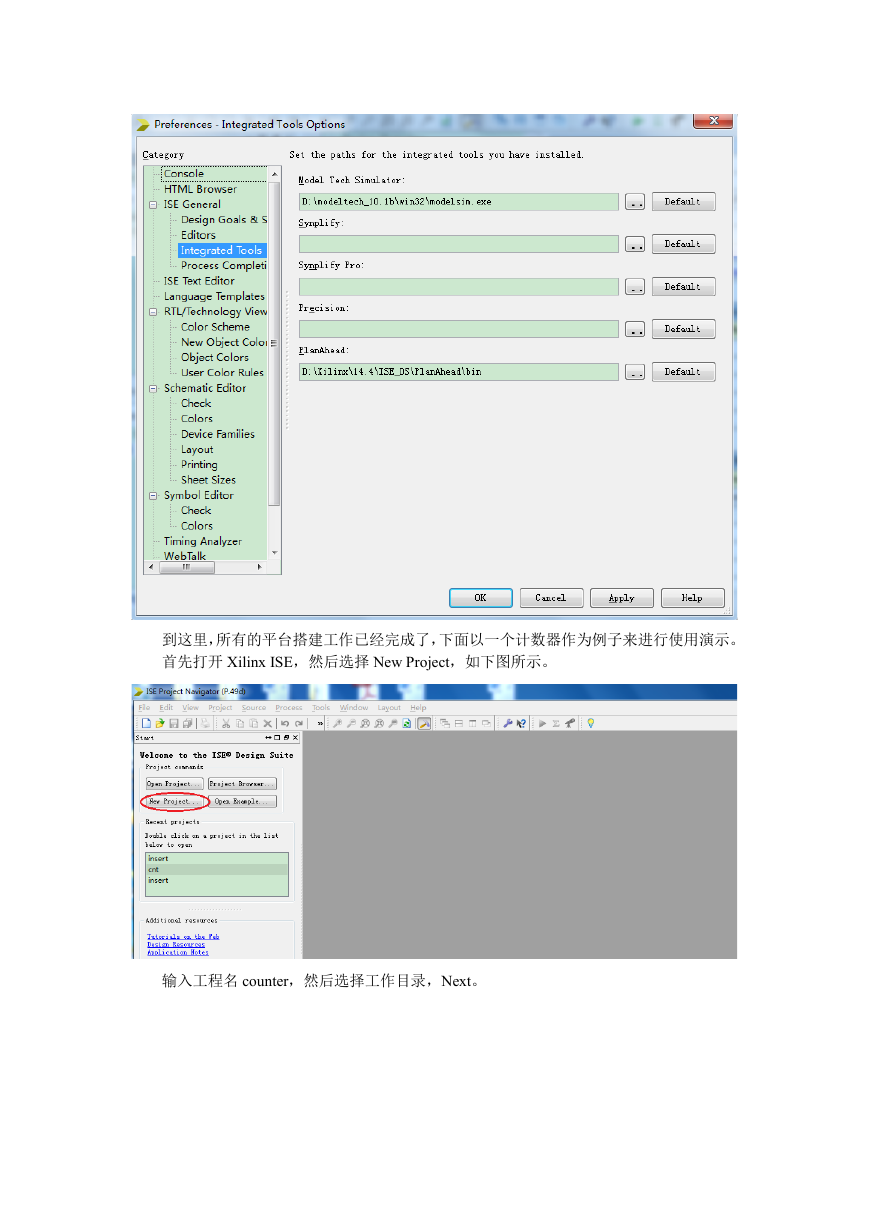

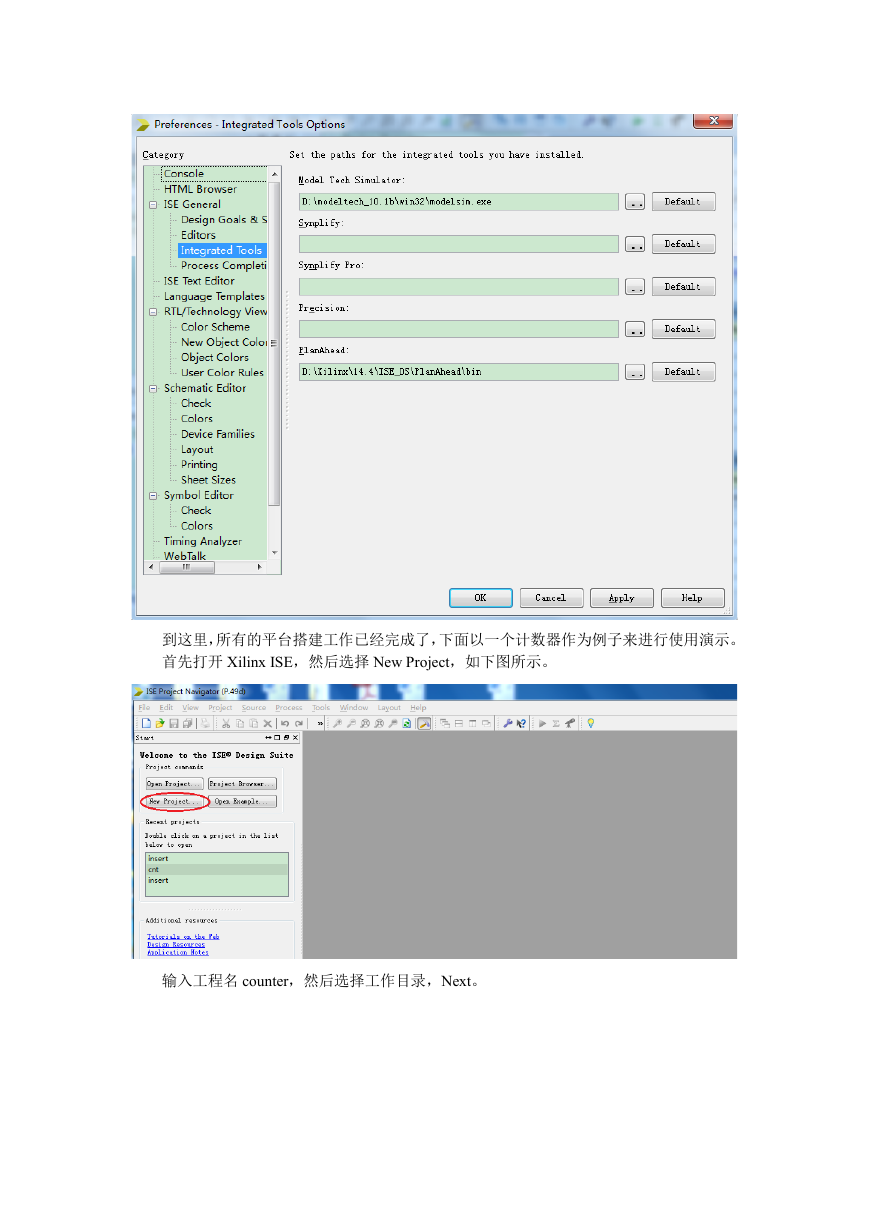

之后打开 Xilinx ISE,选择“Edit—Preferences”调出 Preferences 设置窗口,在左边的

“Category”下选中“ISE General—Integrated Tools”。在 Integrated Tools 项设置中,右边的

“Model Tech Simulator:”下面填入 Modelsim.exe 的文件路径,或者点旁边的“..”按键选

中 Modelsim.exe,例如:“D:\modeltech_10.1b\win32\modelsim.exe”,如下图。

�

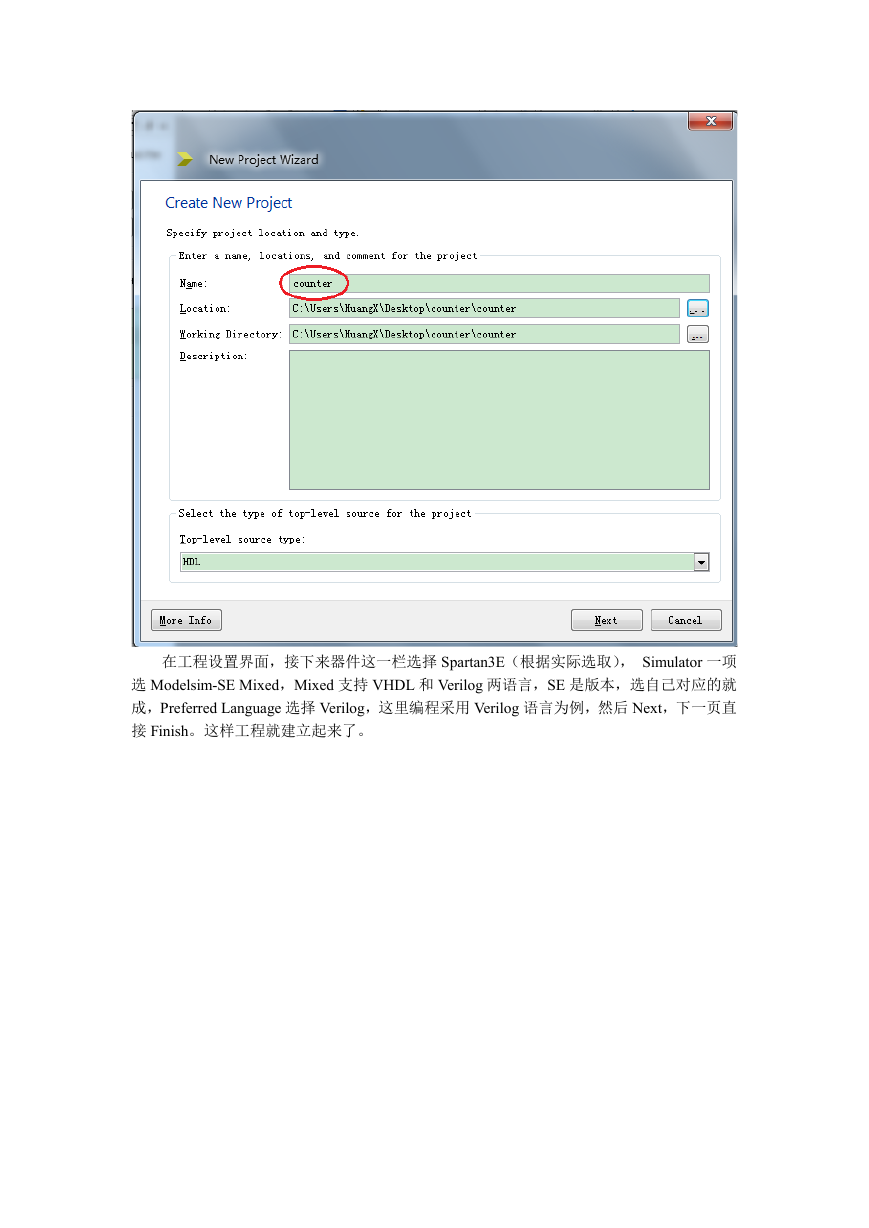

到这里,所有的平台搭建工作已经完成了,下面以一个计数器作为例子来进行使用演示。

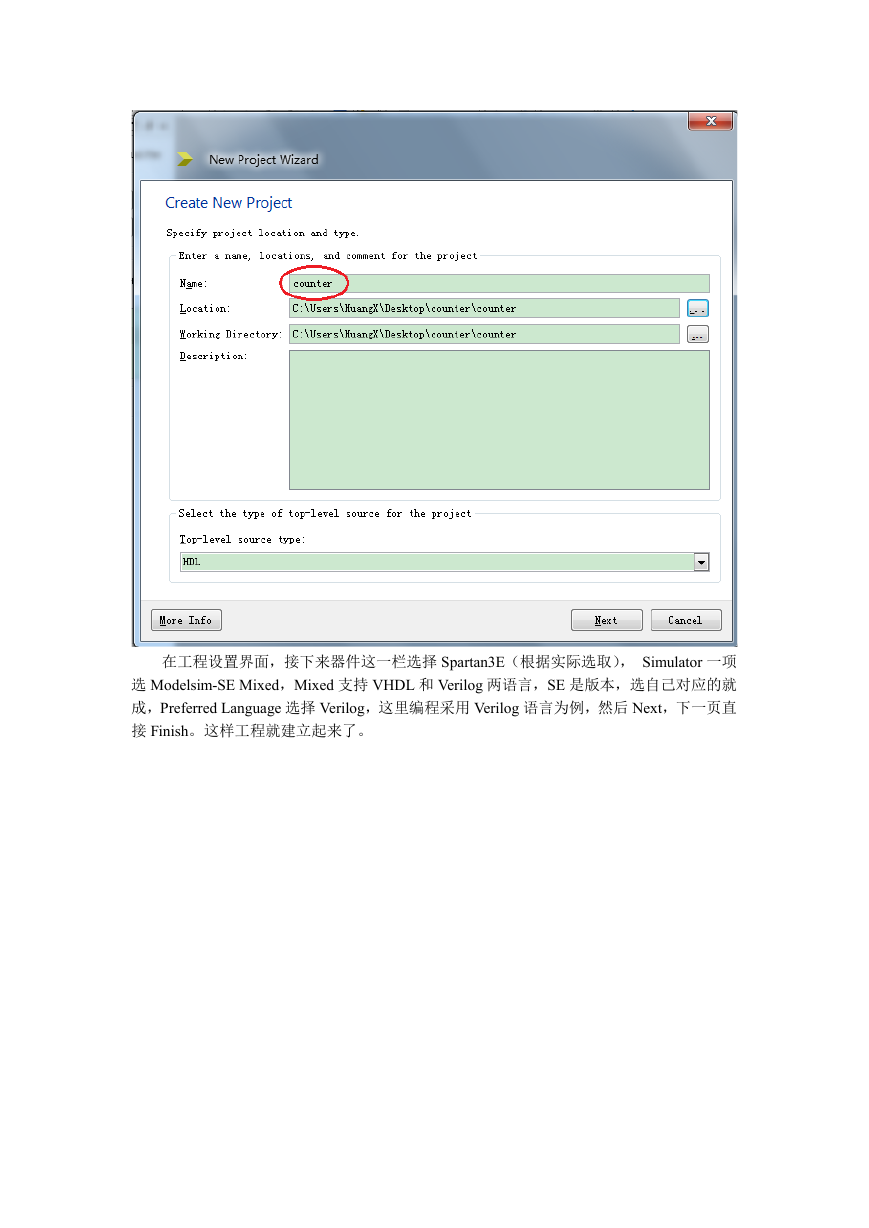

首先打开 Xilinx ISE,然后选择 New Project,如下图所示。

输入工程名 counter,然后选择工作目录,Next。

�

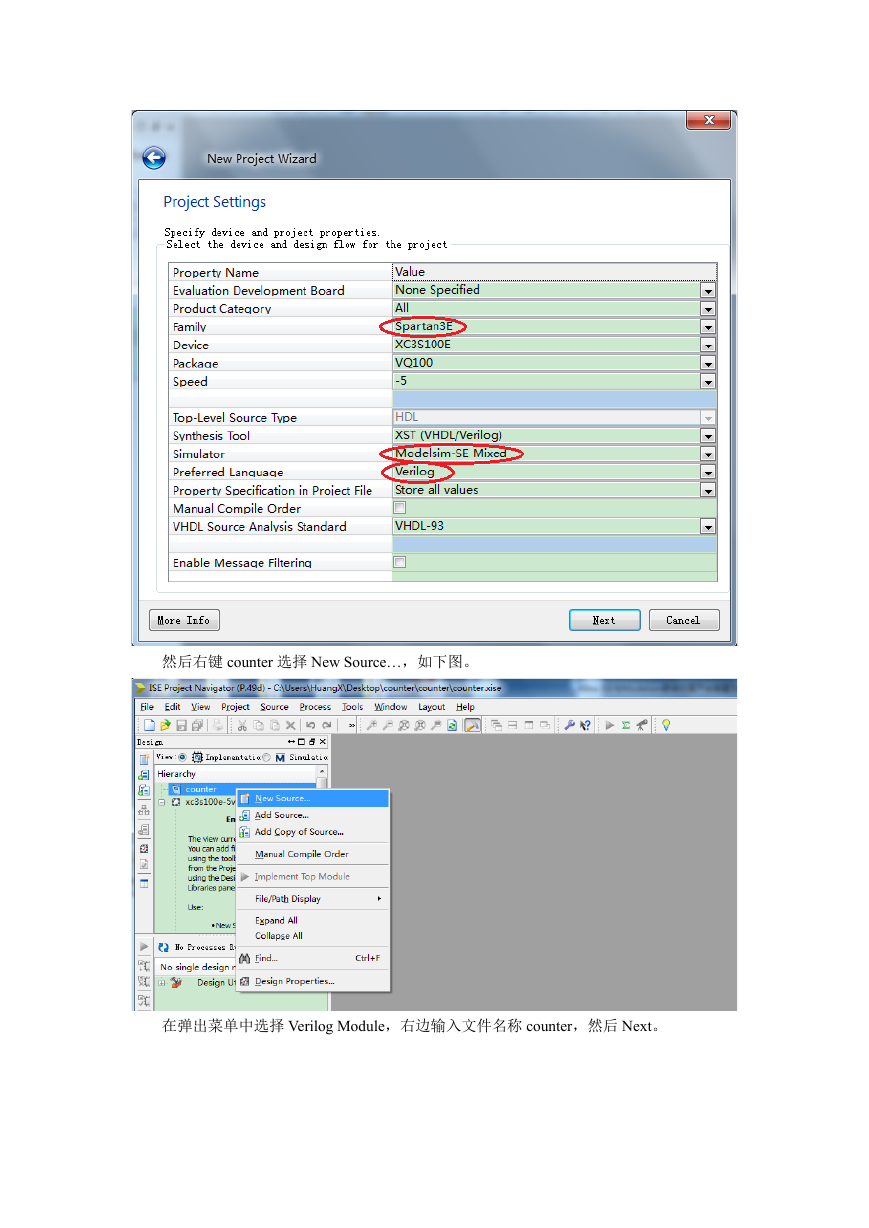

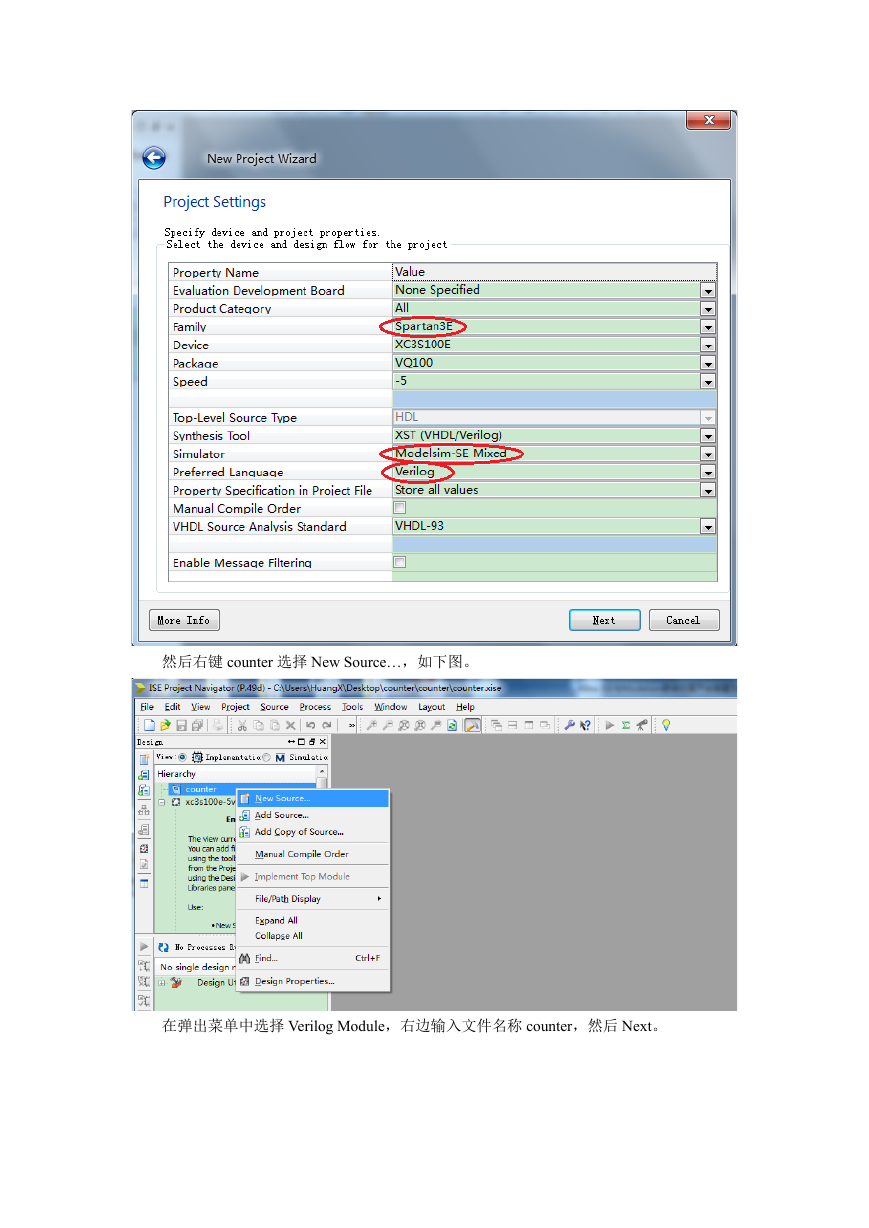

在工程设置界面,接下来器件这一栏选择 Spartan3E(根据实际选取), Simulator 一项

选 Modelsim-SE Mixed,Mixed 支持 VHDL 和 Verilog 两语言,SE 是版本,选自己对应的就

成,Preferred Language 选择 Verilog,这里编程采用 Verilog 语言为例,然后 Next,下一页直

接 Finish。这样工程就建立起来了。

�

然后右键 counter 选择 New Source…,如下图。

在弹出菜单中选择 Verilog Module,右边输入文件名称 counter,然后 Next。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc