5.4. 4Mb/s 速率

5.4.1.4PPM 数据编码解说

脉冲位置调制(PPM)编码靠定义一个数据符号持续时间之后细分持续时间到一套等价

的时间片——称作“chip”来实现。在 PPM 方式中,各个时间片的位置在一个数据符号之

内代表一种可能的位组合。每个 chip 有 ct 的持续时间:ct 由下面的表达式确定:

Ct=Dt/Base

在这个表达式中 Base 代表脉冲位置的号码,或 chips 在每个数据符号中。Base 在 irda

ppm 4.0Mb/s 的系统中被定义为 4,这种调制方式的结果称作“四脉冲位置调制(4PPM)”。

Irda PPM 系统的数据率定义为 4Mb/s。Ct 和 Dt 最后的值如下:

Dt=500ns

Ct=125ns

下图为一个数据符号段和它在 4PPM 方式下被标注上 chip 持续时间

因为在 4PPM 的每个符号中有四个独立的 chip 位置,一个 chip 是逻辑 1 其他所有的都

是逻辑 0 的情况下有四个独立的符号存在。我们定义只有这四种独立的符号为 4PPM 中合

法的数据符号(DD)。每个 DD 代表两位的净数据,或者一个“数据比特对”。这样一字节

的净数据能够依次被四个 DDs 代表。下面的表格定义了 chip 样式代表的为 4PPM 定义的四

种独立的 DDs。

逻辑 1 代表发送 LED 发光一 chip 的持续时间的时间段,而逻辑 0 呢就代表 LED 关断一 chip

持续时间的时间段。为传输而编码的数据 LSB 先编码完。下面的例子展示了为了传输数据

编码之后变化的数据字节将被 DD 代表。在这些例子中传输时间从左边到右边增加,这样距

左边最远的 chips 和符号最先传输。

�

5.4.2 PPM 数据包格式

数据包综述

下面的数据包格式是为 4.0Mb/s PPM 数据包定义的:

在这个数据包格式中,净数据像上面描述的 4PPM 编码方式编码,编码符号在 DD 段。

最大的数据包长度是像低速情况下一样协商解决。报头段被接收器使用来建立相位锁定。

在 PA 期间,接收器开始查询起始标志(STA)用以建立符号同步,如果 STA 正确接收,接

收器便可以开始解释 DD 段的数据符号。接收器持续接收并解释数据直到识别到结束标志

(STO)。STO 表示一个帧的结束。PA,STA,FCS 段和 STO 段的 Chip 模式和符号定义如下。

只有包含全部定义的格式的完整数据包才能能保证被接收器解码(注意,低速率时,

information 区域可能长度为零)。

4PPM 数据编码上面只定义了合法的净数据符号。其他所有的 4chip 组合在解码时被定

义为非法的符号。这些非法符号中的一些被使用来定义 PA,STA,FCS 段和 STO 段因为他们

不是数据。

5.4.2.2 报头段定义

报头段(PA)精确地重复传输 3 次下面的符号串,在 PA 段,传输时间从左到右增大,

这样左边的 chip 和符号先被传输。

�

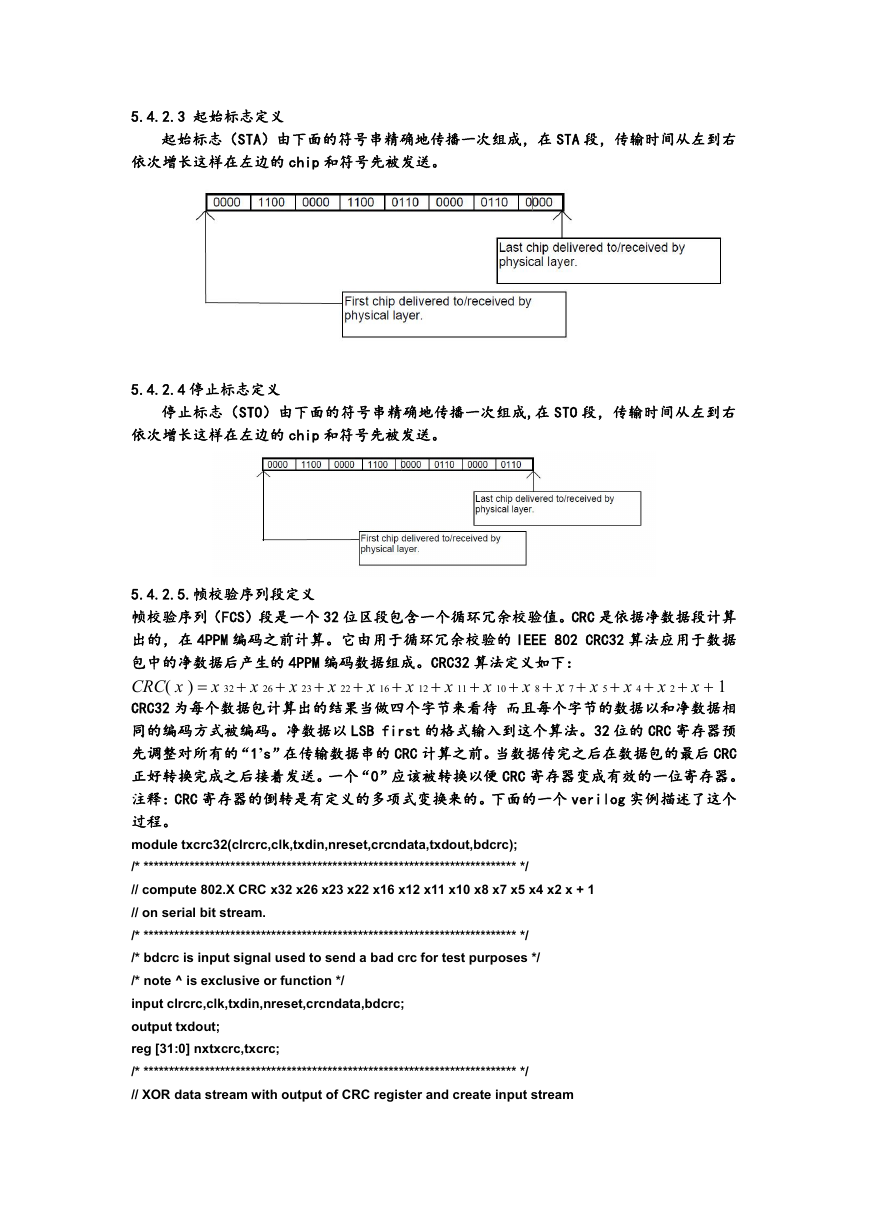

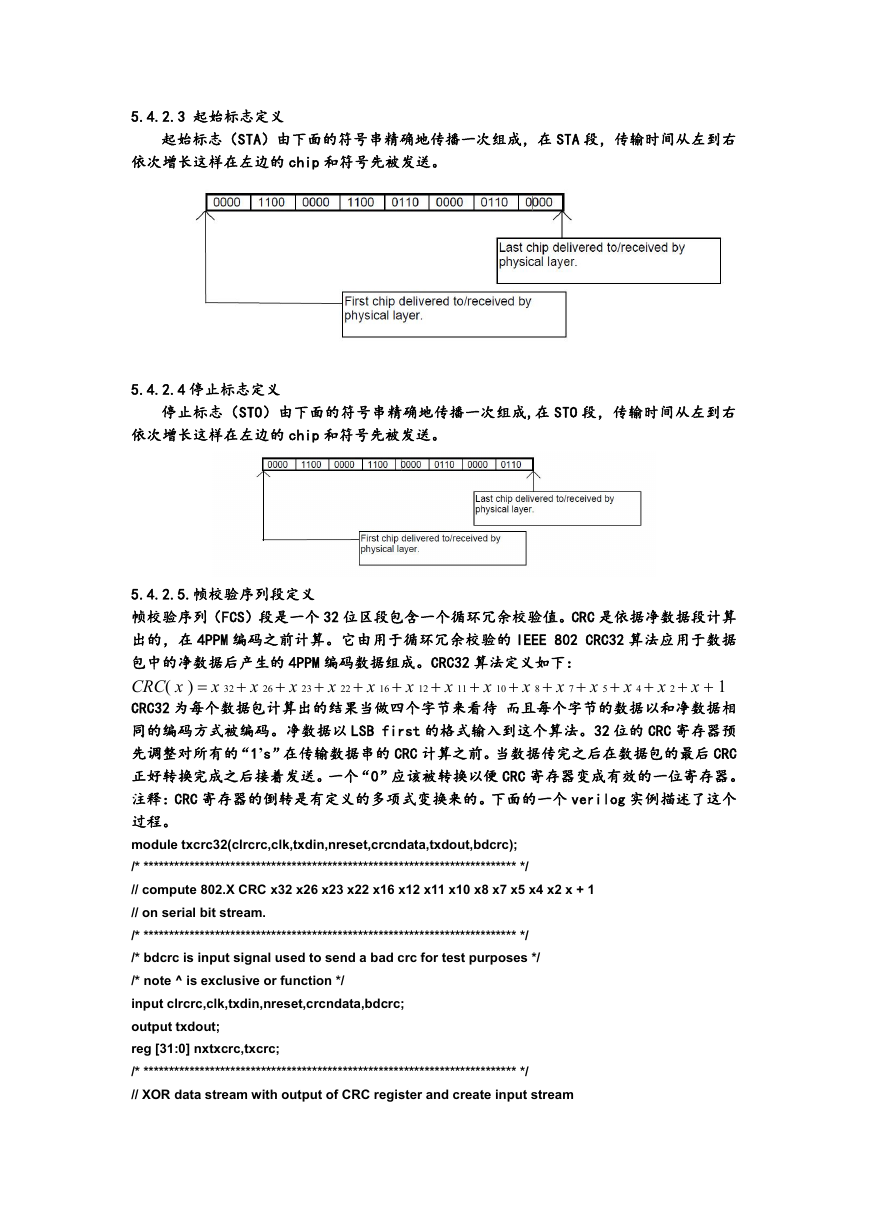

5.4.2.3 起始标志定义

起始标志(STA)由下面的符号串精确地传播一次组成,在 STA 段,传输时间从左到右

依次增长这样在左边的 chip 和符号先被发送。

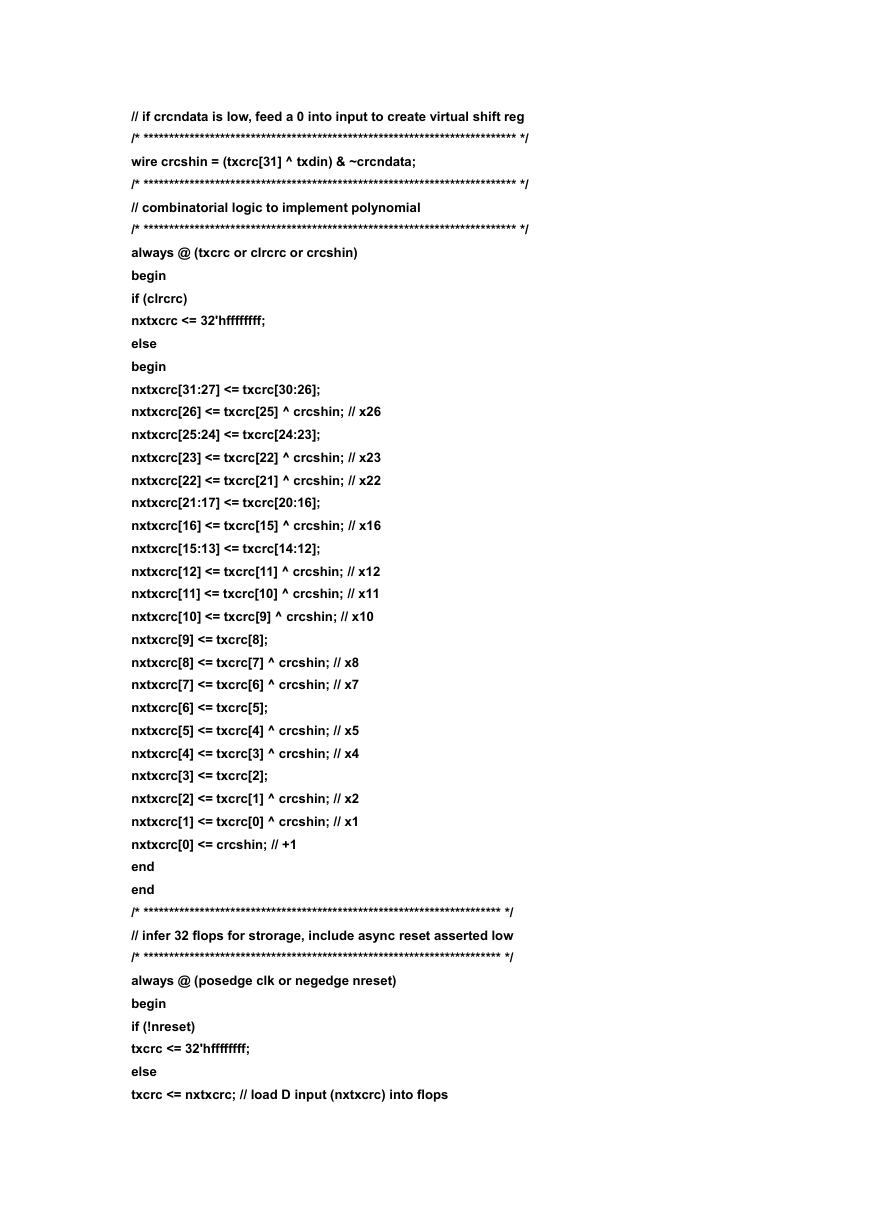

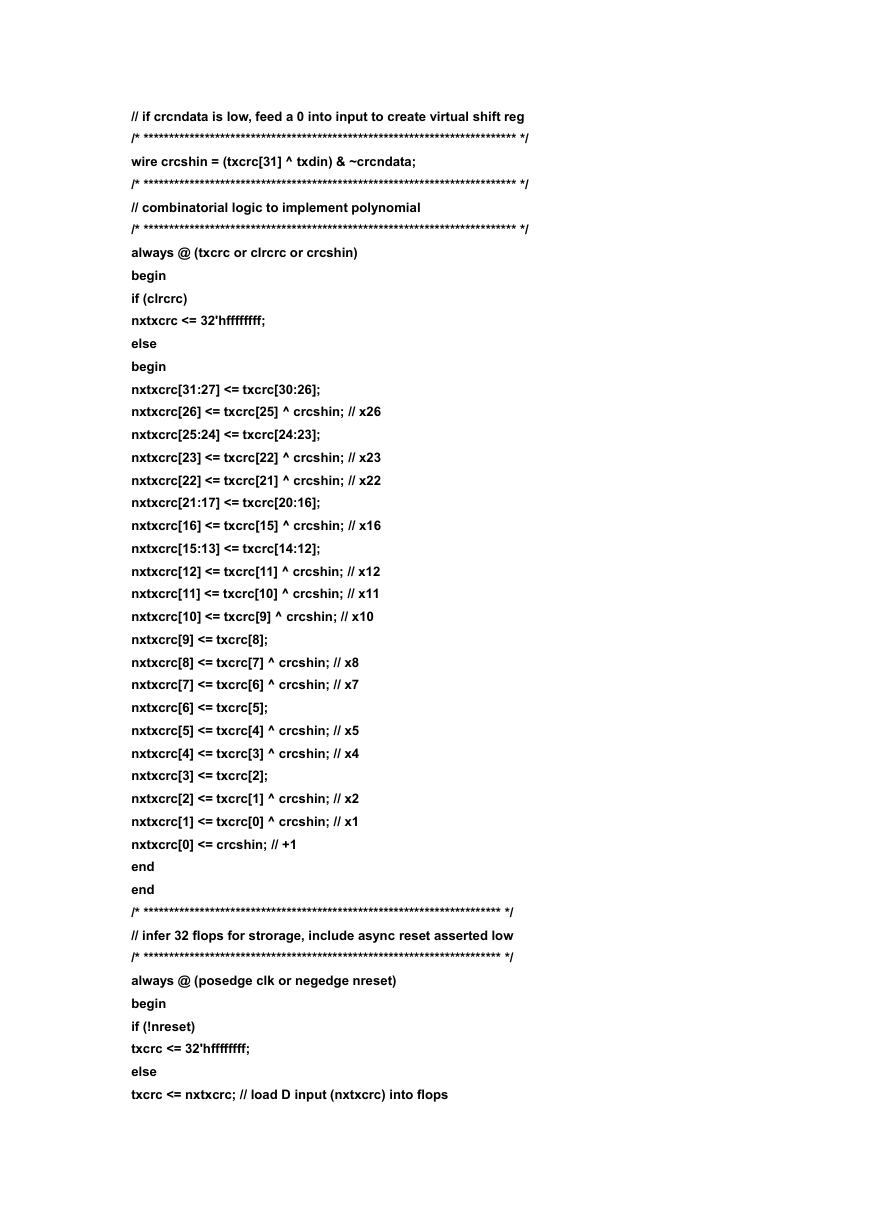

5.4.2.4 停止标志定义

停止标志(STO)由下面的符号串精确地传播一次组成,在 STO 段,传输时间从左到右

依次增长这样在左边的 chip 和符号先被发送。

5.4.2.5.帧校验序列段定义

帧校验序列(FCS)段是一个 32 位区段包含一个循环冗余校验值。CRC 是依据净数据段计算

出的,在 4PPM 编码之前计算。它由用于循环冗余校验的 IEEE 802 CRC32 算法应用于数据

包中的净数据后产生的 4PPM 编码数据组成。CRC32 算法定义如下:

CRC( x ) x 32 x 26 x 23 x 22 x 16 x 12 x 11 x 10 x 8 x 7 x 5 x 4 x 2 x 1

CRC32 为每个数据包计算出的结果当做四个字节来看待 而且每个字节的数据以和净数据相

同的编码方式被编码。净数据以 LSB first 的格式输入到这个算法。32 位的 CRC 寄存器预

先调整对所有的“1’s”在传输数据串的 CRC 计算之前。当数据传完之后在数据包的最后 CRC

正好转换完成之后接着发送。一个“0”应该被转换以便 CRC 寄存器变成有效的一位寄存器。

注释:CRC 寄存器的倒转是有定义的多项式变换来的。下面的一个 verilog 实例描述了这个

过程。

module txcrc32(clrcrc,clk,txdin,nreset,crcndata,txdout,bdcrc);

/* ************************************************************************* */

// compute 802.X CRC x32 x26 x23 x22 x16 x12 x11 x10 x8 x7 x5 x4 x2 x + 1

// on serial bit stream.

/* ************************************************************************* */

/* bdcrc is input signal used to send a bad crc for test purposes */

/* note ^ is exclusive or function */

input clrcrc,clk,txdin,nreset,crcndata,bdcrc;

output txdout;

reg [31:0] nxtxcrc,txcrc;

/* ************************************************************************* */

// XOR data stream with output of CRC register and create input stream

�

// if crcndata is low, feed a 0 into input to create virtual shift reg

/* ************************************************************************* */

wire crcshin = (txcrc[31] ^ txdin) & ~crcndata;

/* ************************************************************************* */

// combinatorial logic to implement polynomial

/* ************************************************************************* */

always @ (txcrc or clrcrc or crcshin)

begin

if (clrcrc)

nxtxcrc <= 32'hffffffff;

else

begin

nxtxcrc[31:27] <= txcrc[30:26];

nxtxcrc[26] <= txcrc[25] ^ crcshin; // x26

nxtxcrc[25:24] <= txcrc[24:23];

nxtxcrc[23] <= txcrc[22] ^ crcshin; // x23

nxtxcrc[22] <= txcrc[21] ^ crcshin; // x22

nxtxcrc[21:17] <= txcrc[20:16];

nxtxcrc[16] <= txcrc[15] ^ crcshin; // x16

nxtxcrc[15:13] <= txcrc[14:12];

nxtxcrc[12] <= txcrc[11] ^ crcshin; // x12

nxtxcrc[11] <= txcrc[10] ^ crcshin; // x11

nxtxcrc[10] <= txcrc[9] ^ crcshin; // x10

nxtxcrc[9] <= txcrc[8];

nxtxcrc[8] <= txcrc[7] ^ crcshin; // x8

nxtxcrc[7] <= txcrc[6] ^ crcshin; // x7

nxtxcrc[6] <= txcrc[5];

nxtxcrc[5] <= txcrc[4] ^ crcshin; // x5

nxtxcrc[4] <= txcrc[3] ^ crcshin; // x4

nxtxcrc[3] <= txcrc[2];

nxtxcrc[2] <= txcrc[1] ^ crcshin; // x2

nxtxcrc[1] <= txcrc[0] ^ crcshin; // x1

nxtxcrc[0] <= crcshin; // +1

end

end

/* ********************************************************************** */

// infer 32 flops for strorage, include async reset asserted low

/* ********************************************************************** */

always @ (posedge clk or negedge nreset)

begin

if (!nreset)

txcrc <= 32'hffffffff;

else

txcrc <= nxtxcrc; // load D input (nxtxcrc) into flops

�

end

/* ********************************************************************** */

// normally crc is inverted as it is sent out

// input signal badcrc is asserted to append bad CRC to packet for

// testing, this is an implied mux with control signal crcndata

// if crcndata = 0 , the data is passed by unchanged, if = 1 then

// the crc register is inverted and transmitted.

/* ********************************************************************** */

wire txdout = (crcndata) ? (~txcrc[31] ^ bdcrc) : txdin; // don't invert

// if bdcrc is 1

endmodule

/* ********************************************************************** */

下面展示了CRC计算以及在编码完成后结果将会怎样被代表以供发送。CRC计算的结果

(txcrc[31 - 0])通过下面的表格列出,当DD段的内容是X’1B’ 和X’A4’, X’1B’是

DD段的第一个字节,如果这四字节的CRC被看成净数据被接收,结果6字节排序是X’1B’, X’

A4’, X’94’,X’BE’, X’54’ and X’39’

5.4.3 数据包丢弃

接收器可能不接收像PPM数据包格式部分所定义的那样具有有效的STA, DD, FCS, 和STO段

的数据包。PA段在接收数据包是不需要很正规。所有其他的数据包被丢弃不管。任何数据

包可能丢弃在任何时间在有一个有效的STA,但是在通过两个或更多重复发送非法的符号

�

“0000”在发送一个完整的STO标志之前将被丢弃。在一个有效的STA被接收到有任何不是

STO段的非法符号任何数据包可能被丢弃在任何时间。

5.4.4连续的数据包传输

连续或brick-walled数据包是被允许的,但是每个数据包必须完整(i.e., containing

PA, STA, DD and STO fields),下面举例说明了brick-walled数据包。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc