关于在FPGA上跑通RISC-V的调研

软件所智能软件中心PLCT实验室 张爱珩 实习生

2020/02/11

�

目 录

01 FPGA开发简介

02 实现RISC-V所需硬件资源

03 实现RISC-V所需工作

04 实现RISC-V成功案例

�

01 FPGA开发简介

什么是FPGA

• FPGA是现场可编程门阵列,英文全称为 Field Programmable Gate Array。

• 通过软件的手段去改变和配置器件内部连接结构和逻辑单元以完成指定设计功能的所有数字集成电路。

与传统数字专用芯片的不同:

FPGA的优点优势:

• 由多个独立、可灵活相连的逻辑单元组成

• 这些逻辑资源之间的连接方式由一个或多个可

编程的连接矩阵来决定

• 可编程

• 灵活性高

• 高密度

• 可重新配置

• 开发周期短

参考资料:

[1] 顾长怡. 基于FPGA与RISC-V的嵌入式系统设计[M].北京:清华大学出版社,2020.

[2] https://wenku.baidu.com/view/4b00548b900ef12d2af90242a8956bec0975a5a9.html

�

01 FPGA开发简介

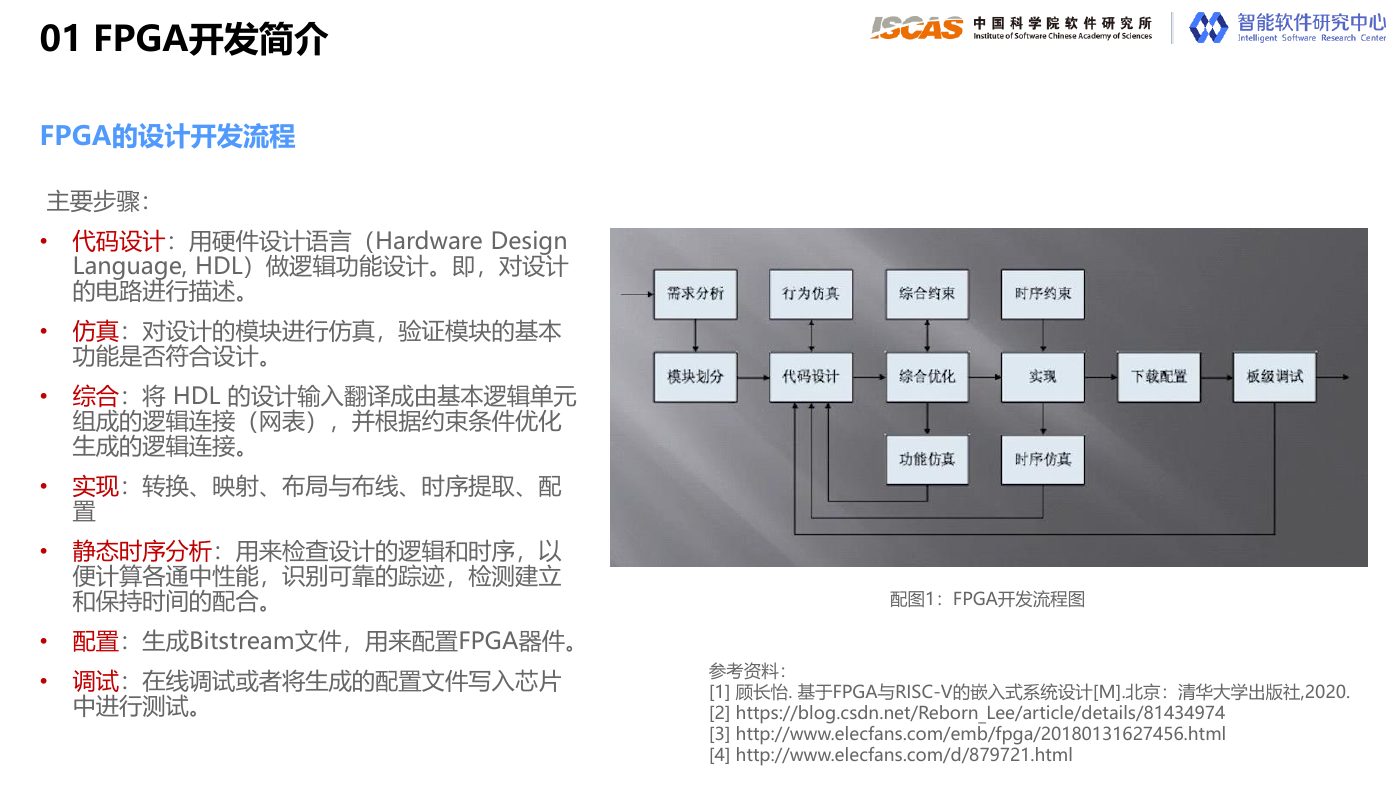

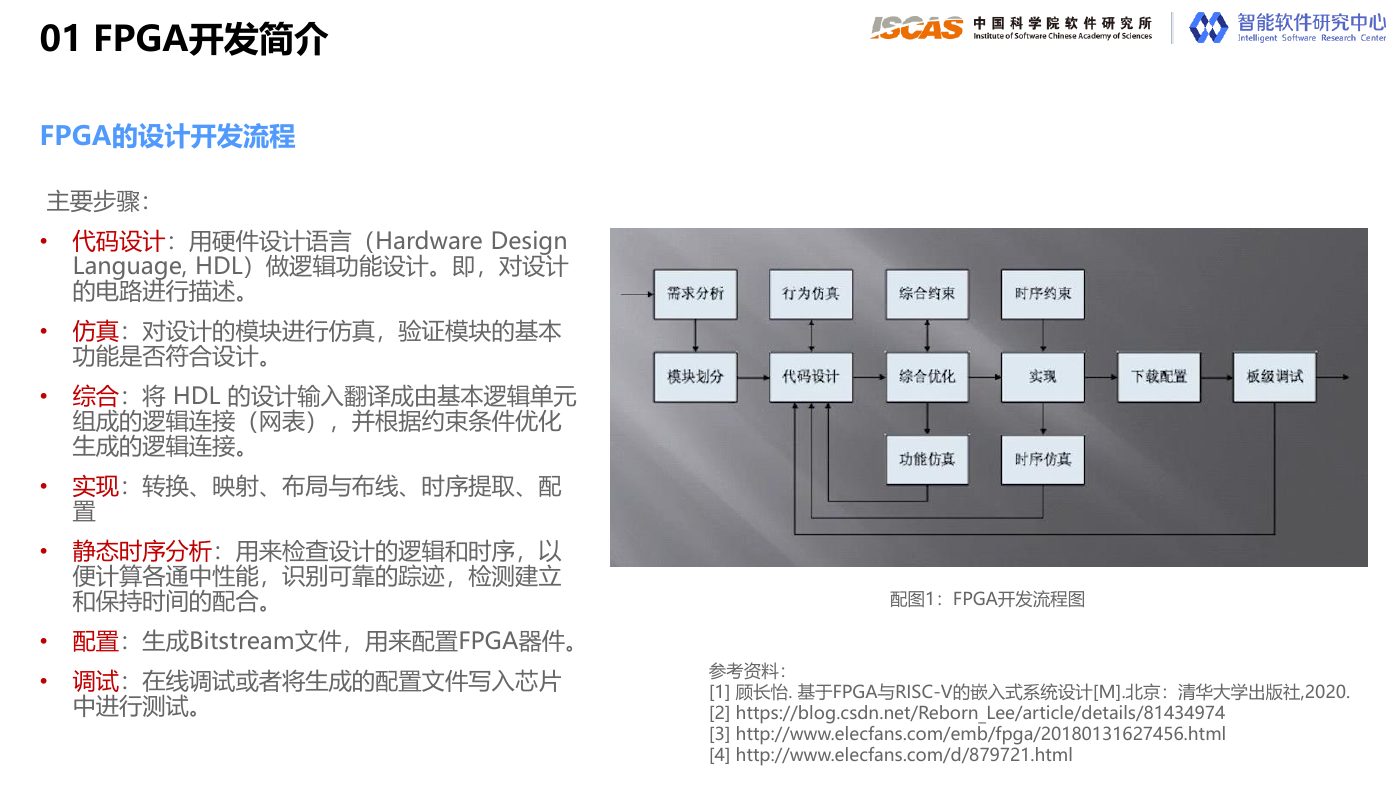

FPGA的设计开发流程

主要步骤:

• 代码设计:用硬件设计语言(Hardware Design

Language, HDL)做逻辑功能设计。即,对设计

的电路进行描述。

• 仿真:对设计的模块进行仿真,验证模块的基本

功能是否符合设计。

• 综合:将 HDL 的设计输入翻译成由基本逻辑单元

组成的逻辑连接(网表),并根据约束条件优化

生成的逻辑连接。

• 实现:转换、映射、布局与布线、时序提取、配

置

• 静态时序分析:用来检查设计的逻辑和时序,以

便计算各通中性能,识别可靠的踪迹,检测建立

和保持时间的配合。

• 配置:生成Bitstream文件,用来配置FPGA器件。

• 调试:在线调试或者将生成的配置文件写入芯片

中进行测试。

配图1:FPGA开发流程图

参考资料:

[1] 顾长怡. 基于FPGA与RISC-V的嵌入式系统设计[M].北京:清华大学出版社,2020.

[2] https://blog.csdn.net/Reborn_Lee/article/details/81434974

[3] http://www.elecfans.com/emb/fpga/20180131627456.html

[4] http://www.elecfans.com/d/879721.html

�

02 实现RISC-V所需硬件资源

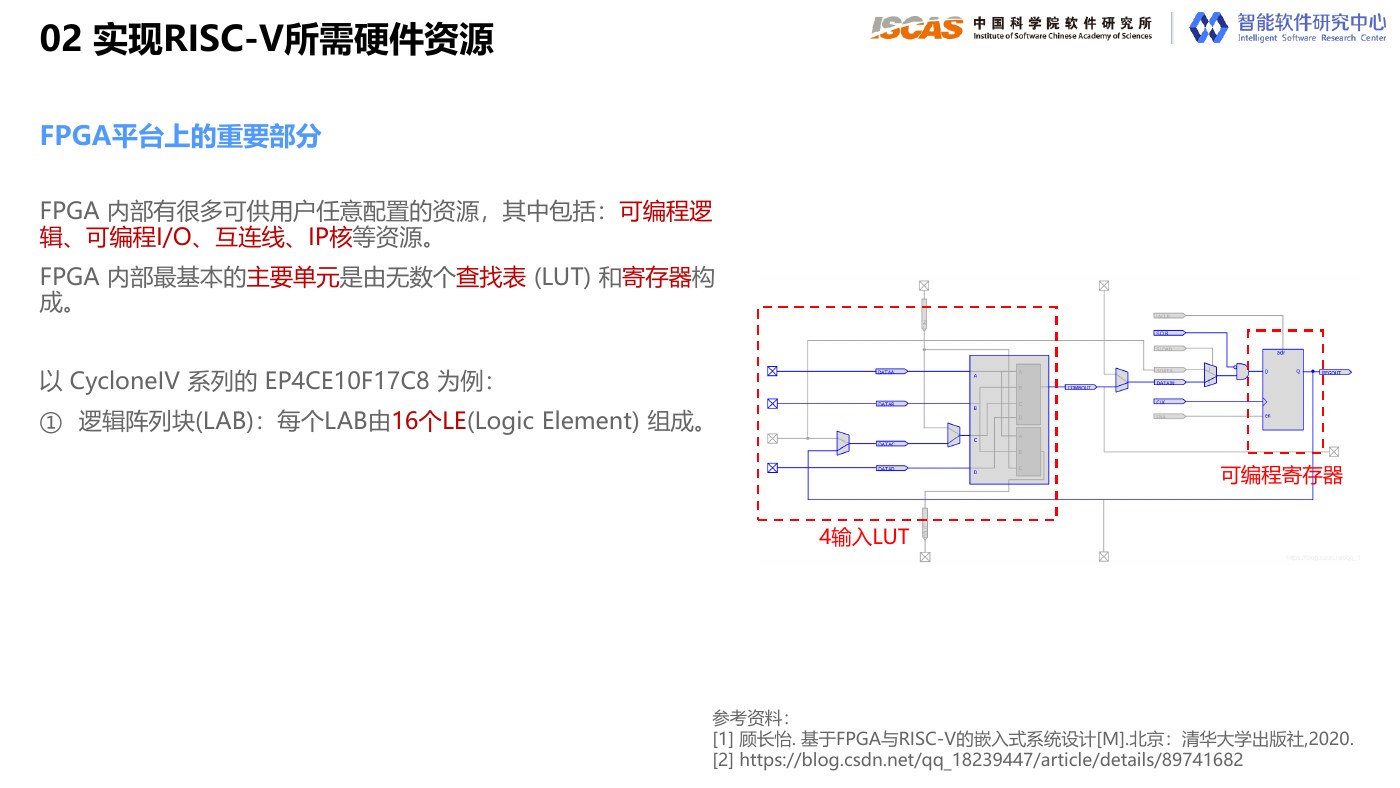

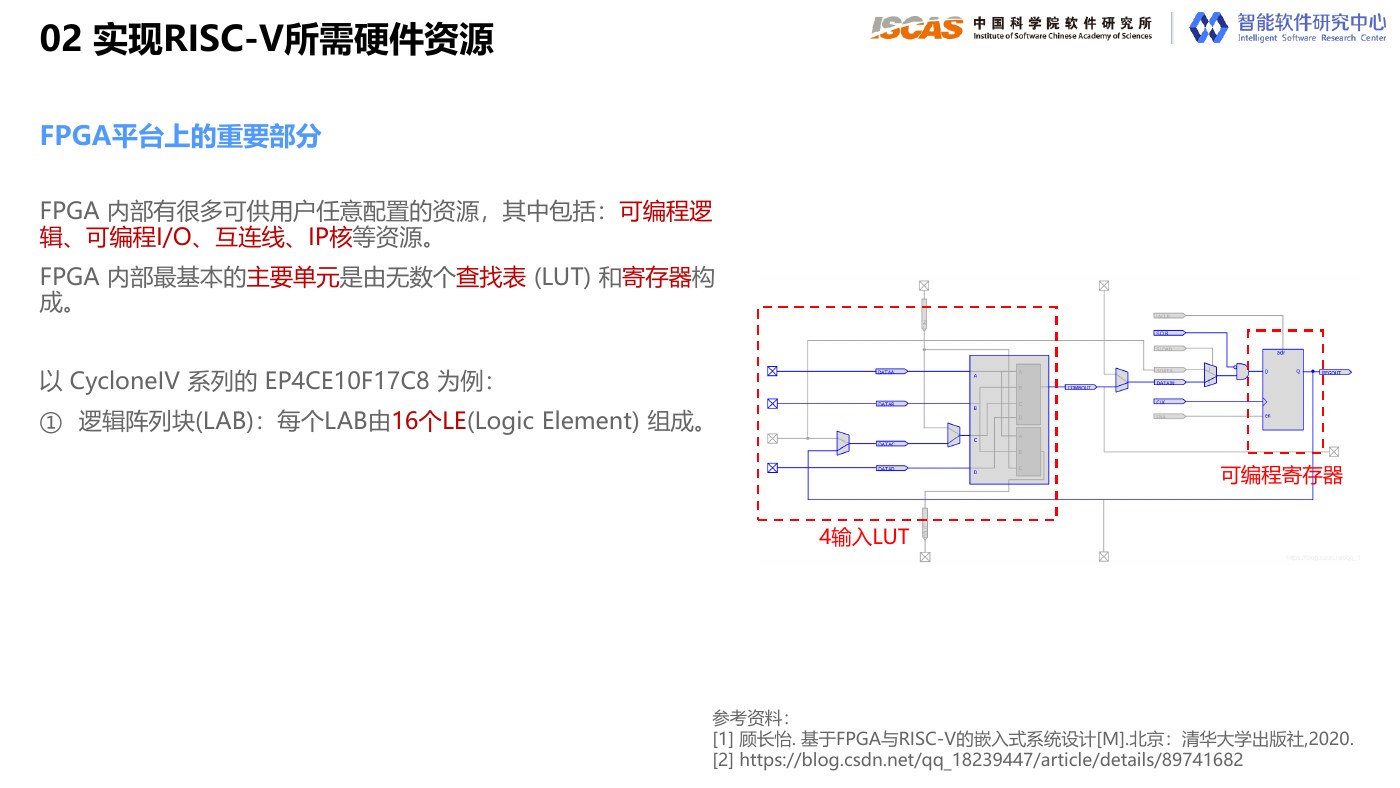

FPGA平台上的重要部分

FPGA 内部有很多可供用户任意配置的资源,其中包括:可编程逻

辑、可编程I/O、互连线、IP核等资源。

FPGA 内部最基本的主要单元是由无数个查找表 (LUT) 和寄存器构

成。

以 CycloneIV 系列的 EP4CE10F17C8 为例:

① 逻辑阵列块(LAB):每个LAB由16个LE(Logic Element) 组成。

4输入LUT

可编程寄存器

参考资料:

[1] 顾长怡. 基于FPGA与RISC-V的嵌入式系统设计[M].北京:清华大学出版社,2020.

[2] https://blog.csdn.net/qq_18239447/article/details/89741682

�

02 实现RISC-V所需硬件资源

FPGA平台上的重要部分

FPGA 内部有很多可供用户任意配置的资源,其中包括:可编程逻

辑、可编程I/O、互连线、IP核等资源。

FPGA 内部最基本的主要单元是由无数个查找表 (LUT) 和寄存器构

成。

以 CycloneIV 系列的 EP4CE10F17C8 为例:

① 逻辑阵列块(LAB):每个LAB由16个LE(Logic Element) 组成。

② 用户可编程I/O (IOE)

参考资料:

[1] 顾长怡. 基于FPGA与RISC-V的嵌入式系统设计[M].北京:清华大学出版社,2020.

[2] https://blog.csdn.net/qq_18239447/article/details/89741682

�

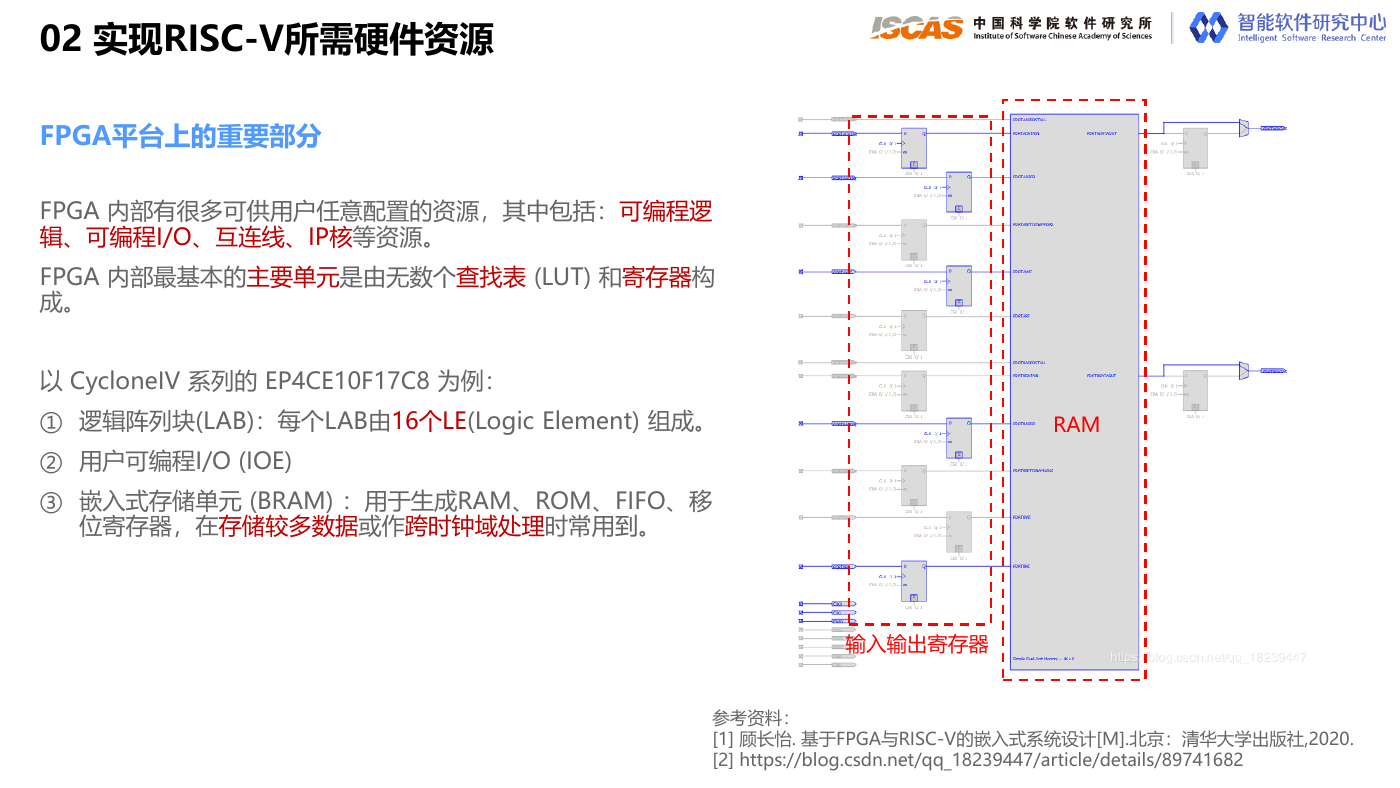

02 实现RISC-V所需硬件资源

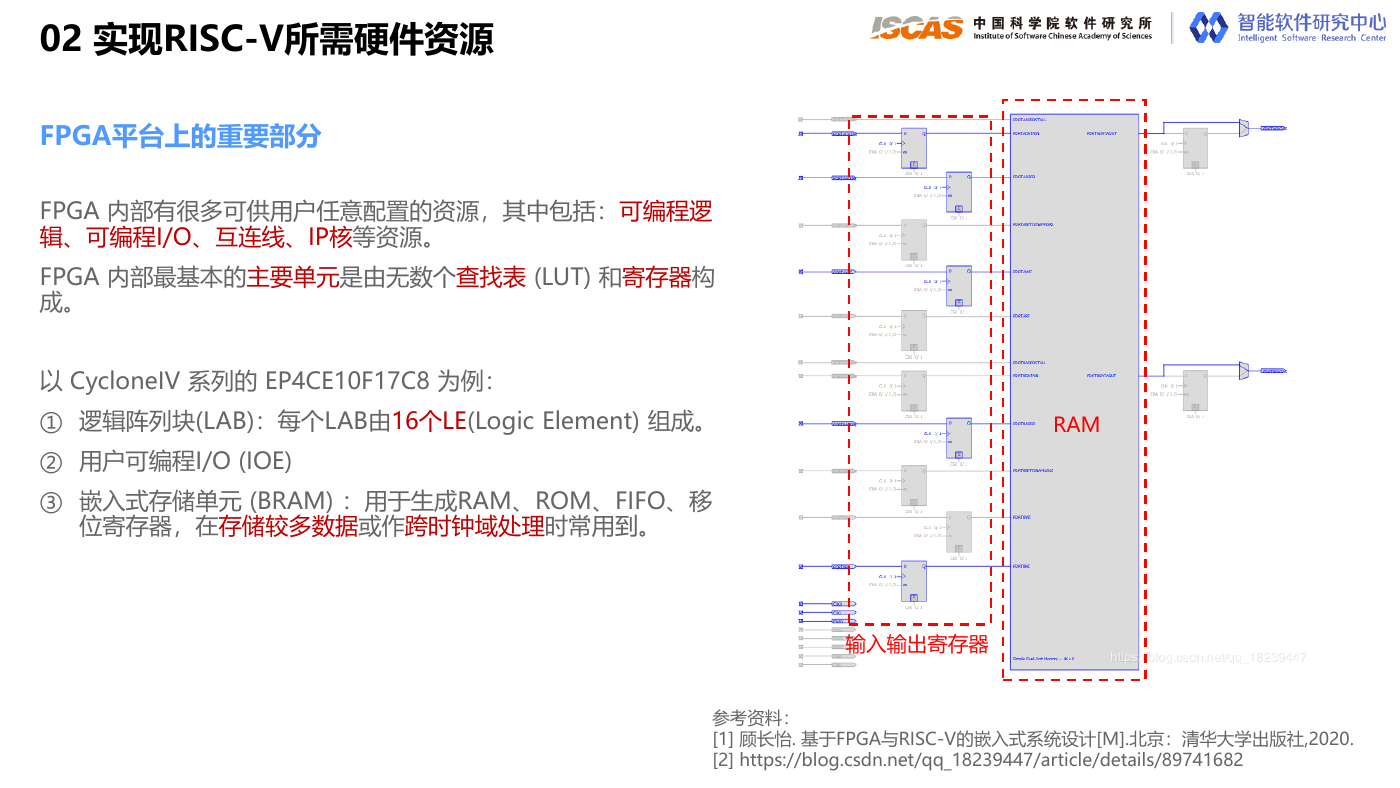

FPGA平台上的重要部分

FPGA 内部有很多可供用户任意配置的资源,其中包括:可编程逻

辑、可编程I/O、互连线、IP核等资源。

FPGA 内部最基本的主要单元是由无数个查找表 (LUT) 和寄存器构

成。

以 CycloneIV 系列的 EP4CE10F17C8 为例:

① 逻辑阵列块(LAB):每个LAB由16个LE(Logic Element) 组成。

RAM

② 用户可编程I/O (IOE)

③ 嵌入式存储单元 (BRAM) :用于生成RAM、ROM、FIFO、移

位寄存器,在存储较多数据或作跨时钟域处理时常用到。

输入输出寄存器

参考资料:

[1] 顾长怡. 基于FPGA与RISC-V的嵌入式系统设计[M].北京:清华大学出版社,2020.

[2] https://blog.csdn.net/qq_18239447/article/details/89741682

�

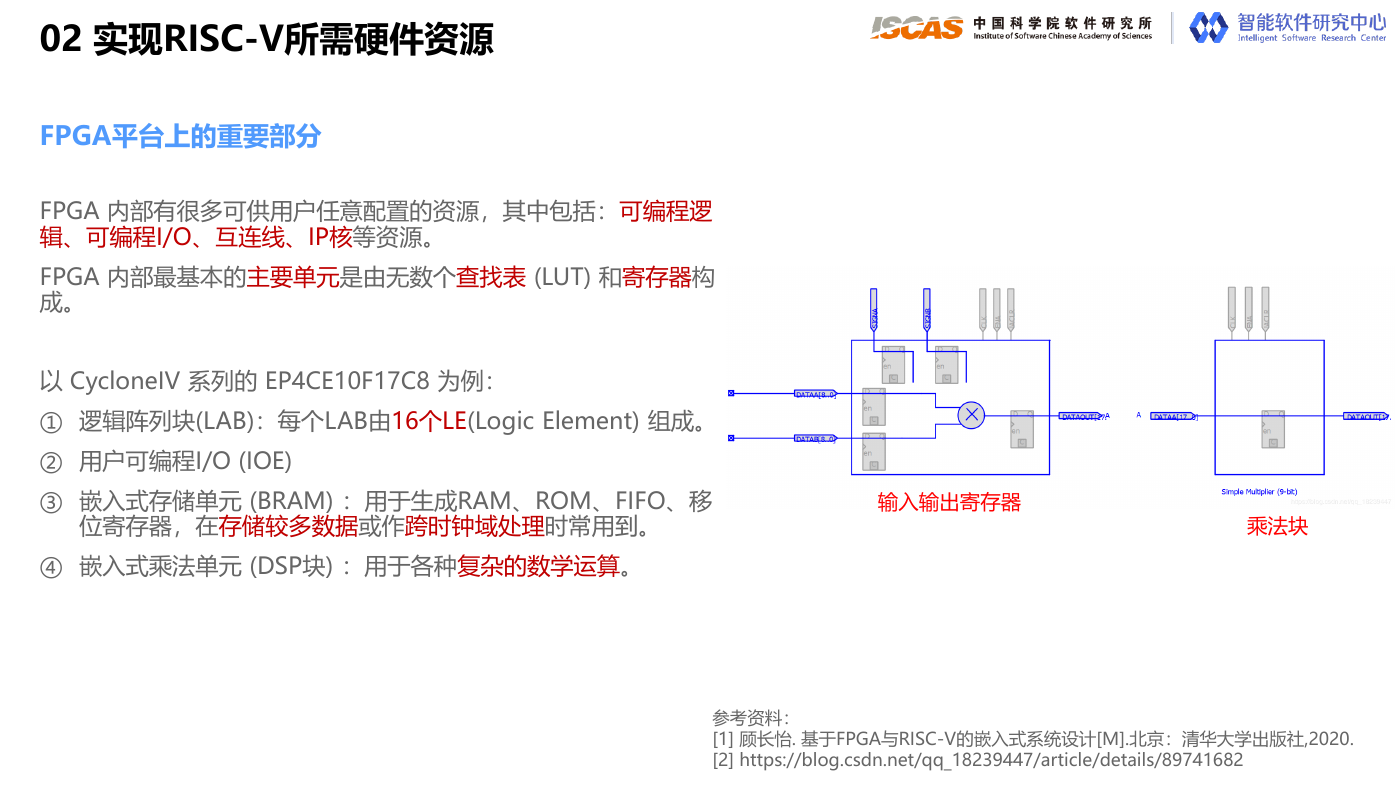

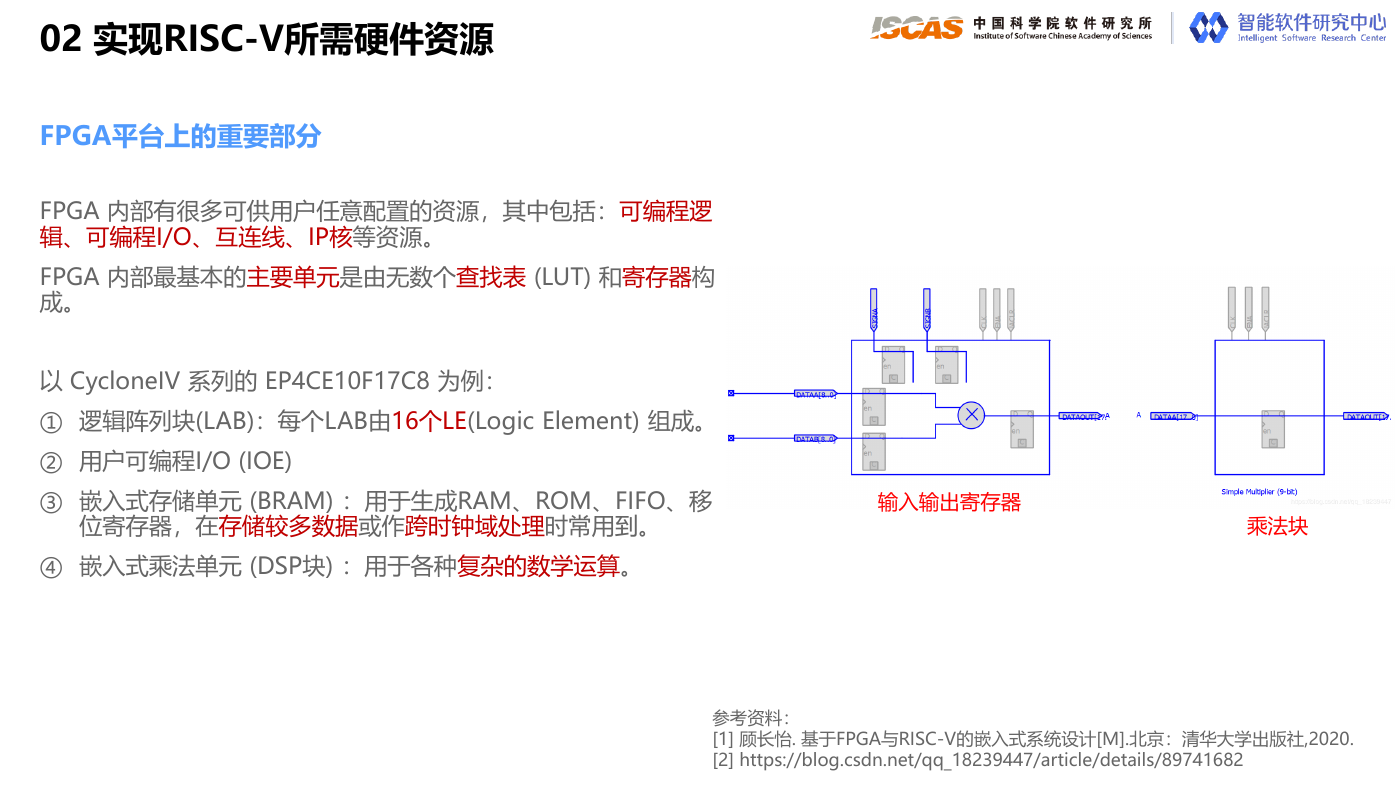

02 实现RISC-V所需硬件资源

FPGA平台上的重要部分

FPGA 内部有很多可供用户任意配置的资源,其中包括:可编程逻

辑、可编程I/O、互连线、IP核等资源。

FPGA 内部最基本的主要单元是由无数个查找表 (LUT) 和寄存器构

成。

以 CycloneIV 系列的 EP4CE10F17C8 为例:

① 逻辑阵列块(LAB):每个LAB由16个LE(Logic Element) 组成。

② 用户可编程I/O (IOE)

③ 嵌入式存储单元 (BRAM) :用于生成RAM、ROM、FIFO、移

位寄存器,在存储较多数据或作跨时钟域处理时常用到。

④ 嵌入式乘法单元 (DSP块) :用于各种复杂的数学运算。

输入输出寄存器

乘法块

参考资料:

[1] 顾长怡. 基于FPGA与RISC-V的嵌入式系统设计[M].北京:清华大学出版社,2020.

[2] https://blog.csdn.net/qq_18239447/article/details/89741682

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc