1.引言

随着集成电路和计算机技术的飞速发展,EDA 技术应运而生,它是一种高级、快速、

有效的电子设计自动化技术。EDA 将大量的电路功能集成到一个芯片中,并且可以由用户

自行设计逻辑功能,提高了系统的集成度和可靠性。运用 EDA 技术可以方便、快捷设计电

路系统。

本文基于 EDA 系统,在 Quartus II7.2 软件平台上,完成了汽车尾灯电路的设计。采用

VHDL 硬件描述语言描述汽车尾灯电路,完成对电路的功能仿真。在设计过程中,重点探讨

了汽车尾灯电路的设计思路和功能模块划分,通过分析仿真波形表明设计的汽车尾灯电路完

成了预期的功能。

2.汽车尾灯控制器的设计过程

2.1 设计内容

选用合适的可编程逻辑器件及外围电子元器件,设计一个汽车尾灯控制器,利用 EDA

软件(QUARTUS Ⅱ)进行编译及仿真,设计输入可采用 VHDL 硬件描述语言输入法和原

理图输入法,并下载到 EDA 实验开发系统,连接外围电路,完成实际测试。

2.2 设计要求

(1)汽车尾部左右两侧各有多盏指示灯。

(2)汽车正常行驶时指示灯都不亮。

(3)汽车右转弯时,右侧的一盏指示灯亮。

(4)汽车左转弯时,左侧的一盏指示灯亮。

(5)汽车刹车时,左右两侧的一盏指示灯同时亮。

(6)汽车在夜间行驶时,左右两侧有指示灯同时一直亮,供照明使用。

设计参数

2.3 汽车尾灯控制器的工作原理

尾部指示灯数

4

汽车尾灯控制器就是一个状态机的实例。当汽车正常行驶时所有指示灯都不亮;当汽车

向右转弯时,汽车右侧的指示灯 ldright 亮;当汽车向左侧转弯时,汽车左侧的指示灯 ldleft

亮;当汽车刹车时,汽车右侧的指示灯 ldbrake1 和汽车左侧的指示灯 ldbrake2 同时亮;当汽

车在夜间行驶时,汽车右侧的指示灯 ldnight1 和汽车左侧的指示灯 ldnight2 同时一直亮;当

于大雾天行驶时右侧指示灯 ldfoggy1 和左侧指示灯 ldfoggy2 同时亮。

通过设置系统的输入信号:系统时钟信号 clk,汽车左转弯控制信号 left,汽车右转弯控

制信号 right,刹车信号 brake,夜间行驶信号 night,雾灯信号 foggy 和系统的输出信号:汽

车左侧 4 盏指示灯 ldleft,dbrake1,dnight1,dfoggy1 和汽车右侧 4 盏指示灯 ldright,ldbrake2,

ldnight2,ldfoggy2 实现以上功能。

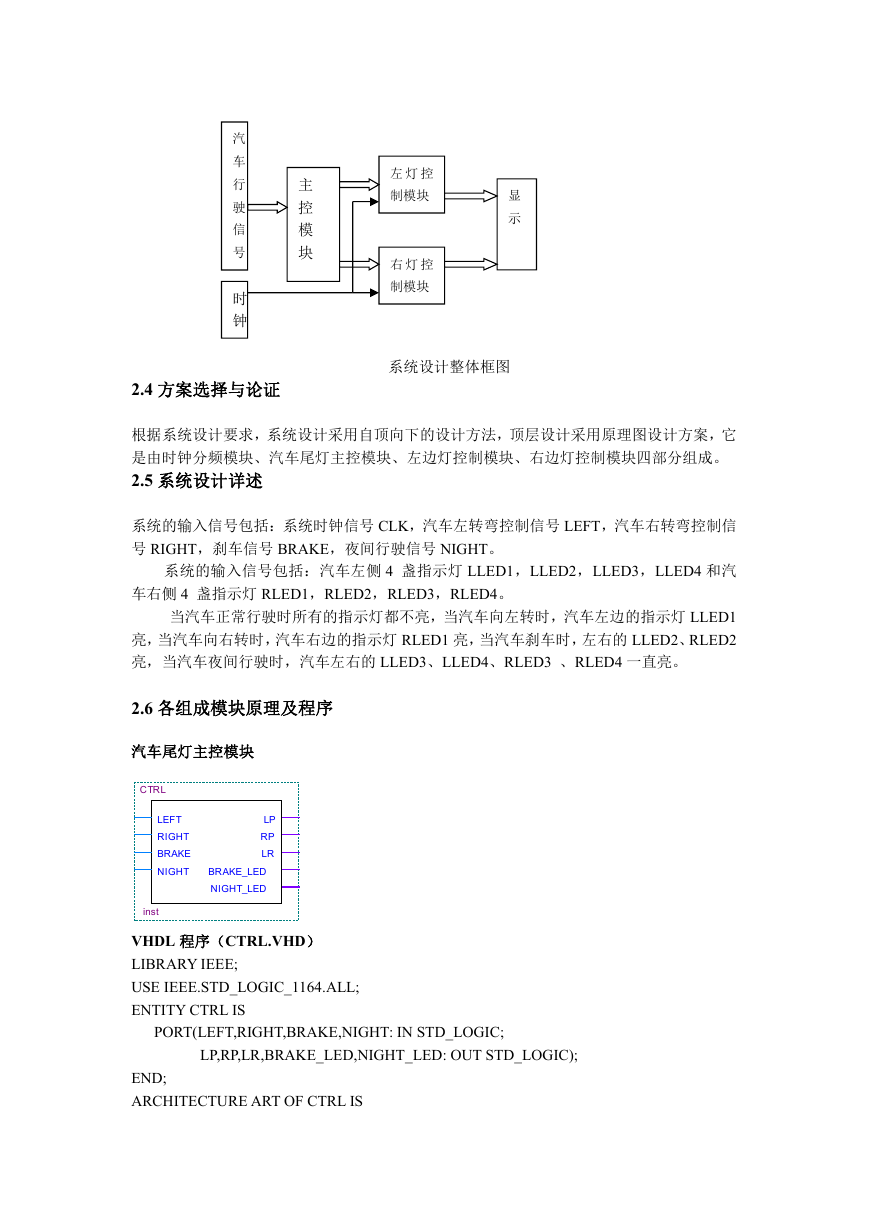

系统的整体组装设计原理如图所示:

�

汽

车

行

驶

信

号

时

钟

主

控

模

块

左 灯 控

制模块

右 灯 控

制模块

显

示

2.4 方案选择与论证

系统设计整体框图

根据系统设计要求,系统设计采用自顶向下的设计方法,顶层设计采用原理图设计方案,它

是由时钟分频模块、汽车尾灯主控模块、左边灯控制模块、右边灯控制模块四部分组成。

2.5 系统设计详述

系统的输入信号包括:系统时钟信号 CLK,汽车左转弯控制信号 LEFT,汽车右转弯控制信

号 RIGHT,刹车信号 BRAKE,夜间行驶信号 NIGHT。

系统的输入信号包括:汽车左侧 4 盏指示灯 LLED1,LLED2,LLED3,LLED4 和汽

车右侧 4 盏指示灯 RLED1,RLED2,RLED3,RLED4。

当汽车正常行驶时所有的指示灯都不亮,当汽车向左转时,汽车左边的指示灯 LLED1

亮,当汽车向右转时,汽车右边的指示灯 RLED1 亮,当汽车刹车时,左右的 LLED2、RLED2

亮,当汽车夜间行驶时,汽车左右的 LLED3、LLED4、RLED3 、RLED4 一直亮。

2.6 各组成模块原理及程序

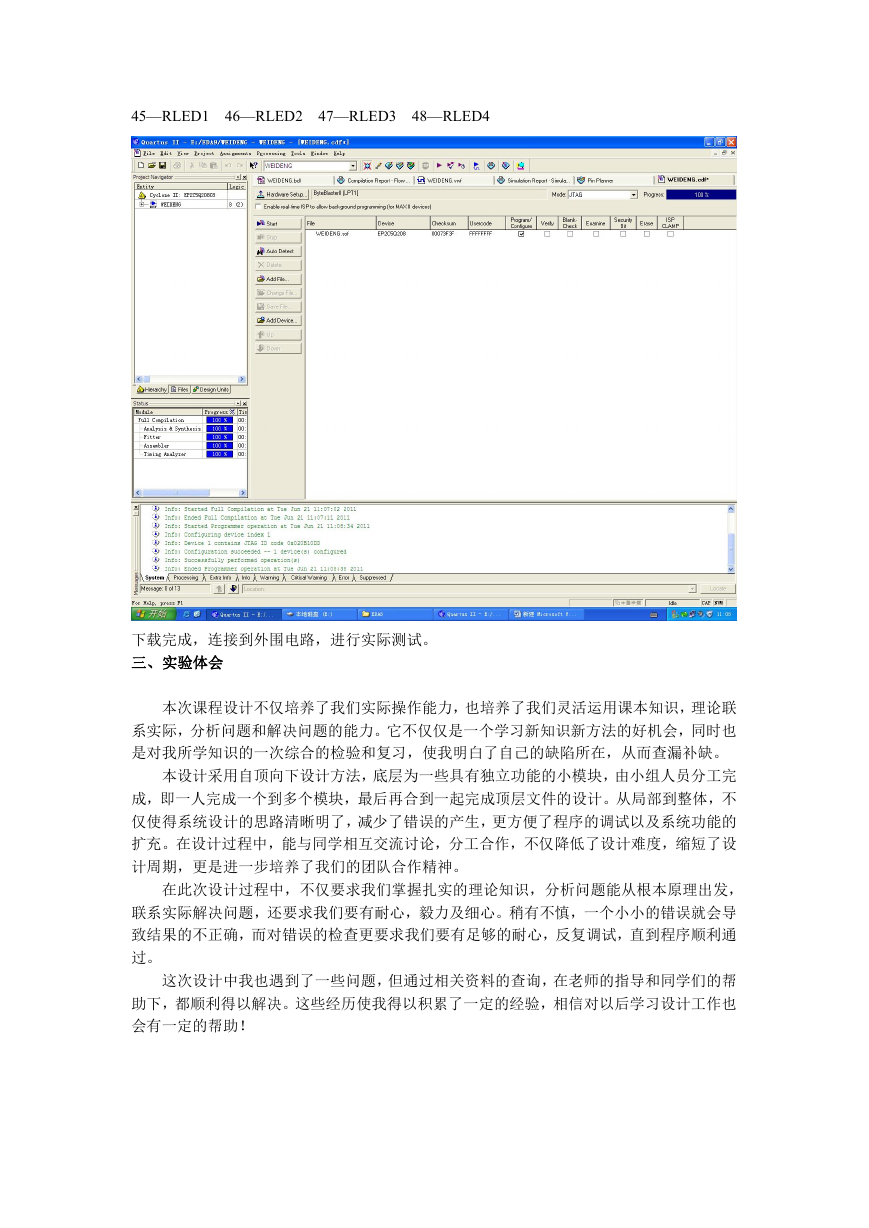

汽车尾灯主控模块

CTRL

LEFT

RIGHT

BRAKE

NIGHT

inst

LP

RP

LR

BRAKE_LED

NIGHT_LED

VHDL 程序(CTRL.VHD)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CTRL IS

PORT(LEFT,RIGHT,BRAKE,NIGHT: IN STD_LOGIC;

LP,RP,LR,BRAKE_LED,NIGHT_LED: OUT STD_LOGIC);

END;

ARCHITECTURE ART OF CTRL IS

�

BEGIN

NIGHT_LED<=NIGHT;

BRAKE_LED<=BRAKE;

PROCESS(LEFT,RIGHT)

VARIABLE TEMP:STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN

TEMP:=LEFT&RIGHT;

CASE TEMP IS

WHEN "00"=>LP<='0';RP<='0';LR<='0';

WHEN "01"=>LP<='0';RP<='1';LR<='0';

WHEN "10"=>LP<='1';RP<='0';LR<='0';

WHEN OTHERS =>LP<='0';RP<='0';LR<='1';

END CASE ;

END PROCESS;

END ART;

功能:以 LEFT、RIGHT、BRAKE、NIGHT 为输入端口,高电平有效,LP、RP、LR、

BRAKE_LED、NIGHT_LED 为输出端口。将 NIGHT 端的信号给 NIGHT_LED,将 BRAKE

的信号给 BRAKE_LED,用 CASE 语句来控制 LP(左灯输入)、RP(右灯输入)、LR(左

右同时输入),LEFT 为高电平时,左模块工作,当 RIGHT 为高电平时,右模块工作,当

LR 为高电平时,左右灯都没有信号输入。从而实现对左右控制模块的控制。

左边灯控制模块

LC

CLK

LP

LR

BRAKE

NIGHT

inst1

LEDL

LEDB

LEDN1

LEDN2

VHDL 程序(LC.VHD)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LC IS

PORT(CLK,LP,LR,BRAKE,NIGHT:IN STD_LOGIC;

LEDL,LEDB,LEDN1, LEDN2:OUT STD_LOGIC);

END;

ARCHITECTURE ART OF LC IS

BEGIN

LEDB<=BRAKE;

LEDN1<=NIGHT;

LEDN2<=NIGHT;

PROCESS(CLK,LP,LR)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF(LR='0') THEN

IF(LP='0')THEN

LEDL<='0';

ELSE

LEDL<='1';

�

END IF;

ELSE

LEDL<='0';

END IF;

END IF;

END PROCESS;

END ART;

功能:以 CLK、LP、LR、BRAKE、NIGHT 为输入端口, 高电平有效, LEDL、LEDB、LEDN1、

LEDN2 为输出端口。将 BRAKE 信号 给 LEDB 端口,NIGHT 信号分别给 LEDN1、LEDN2,

当 CLK 的上升沿到来时,如果 LR、LP 都同时为低电平时,LEDL 端口输出低电平,当 LR

为低电平 LP 为高电平时,LEDL 输出高电平,当 LR 为高电平时,LEDL 端口输出低电平。

通过 LEDL、LEDB、LEDN1、LEDN2 的电平信号来控制汽车左边的尾灯。

右边灯控制模块

RC

CLK

RP

LR

BRAKE

NIGHT

inst2

LEDR

LEDB

LEDN1

LEDN2

VHDL 程序(RC.VHD)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY RC IS

PORT(CLK,RP,LR,BRAKE,NIGHT:IN STD_LOGIC;

LEDR,LEDB,LEDN1, LEDN2:OUT STD_LOGIC);

END ART;

功能: 以 CLK、RP、LR、BRAKE、NIGHT 为输入端口, 高电平有效, LEDR、LEDB、LEDN1、

LEDN2 为输出端口。将 BRAKE 信号 给 LEDB 端口,NIGHT 信号分别给 LEDN1、LEDN2,

END;

ARCHITECTURE ART OF RC IS

BEGIN

LEDB<=BRAKE;

LEDN1<=NIGHT;

LEDN2<=NIGHT;

PROCESS(CLK,RP,LR)

BEGIN

IF CLK'EVENT AND CLK='1'THEN

IF (LR='0') THEN

IF (RP='0') THEN

LEDR<='0';

ELSE

LEDR<='1';

END IF;

ELSE

LEDR<='0';

END IF;

END IF;

END PROCESS;

�

当 CLK 的上升沿到来时,如果 LR、RP 都同时为低电平时,LEDL 端口输出低电平,当 LR

为低电平 RP 为高电平时,LEDL 输出高电平,当 LR 为高电平时,LEDL 端口输出低电平。

通过 LEDL、LEDB、LEDN1、LEDN2 的电平信号来控制汽车右边的尾灯。

时钟分频模块

SZ

CLK

CP

inst3

VHDL 程序(SZ.VHD)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY SZ IS

PORT(CLK:IN STD_LOGIC;

CP:OUT STD_LOGIC);

END;

ARCHITECTURE ART OF SZ IS

SIGNAL COUNT:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS(CLK)

BEGIN

IF CLK'EVENT AND CLK = '1' THEN

COUNT<= COUNT + 1;

END IF;

END PROCESS;

CP<= COUNT(3);

END ART;

功能:这块的功能是对左右两边的 LLED1、RLED1 的闪烁时间间隔,以 CLK 为输入信号,

CP 为输出信号,在程序中定义一个八位节点信号 COUNT 来放计数值,当 CLK 的上升沿到

来时就开始计数,最后将 COUNT(3)给 CP,实现对 CLK 的八分频。再将 CP 的电平信号分

别和 LEDL、LEDR 电平与,最后用输出的电平来控制汽车左右的 LLED1、RLED1,实现

左右转的指示功能。

�

CLK

INPUT

VCC

LEFT

RIGHT

BRAKE

NIGHT

INPUT

VCC

INPUT

VCC

INPUT

VCC

INPUT

VCC

CTRL

LEFT

RIGHT

BRAKE

NIGHT

inst

LP

RP

LR

BRAKE_LED

NIGHT_LED

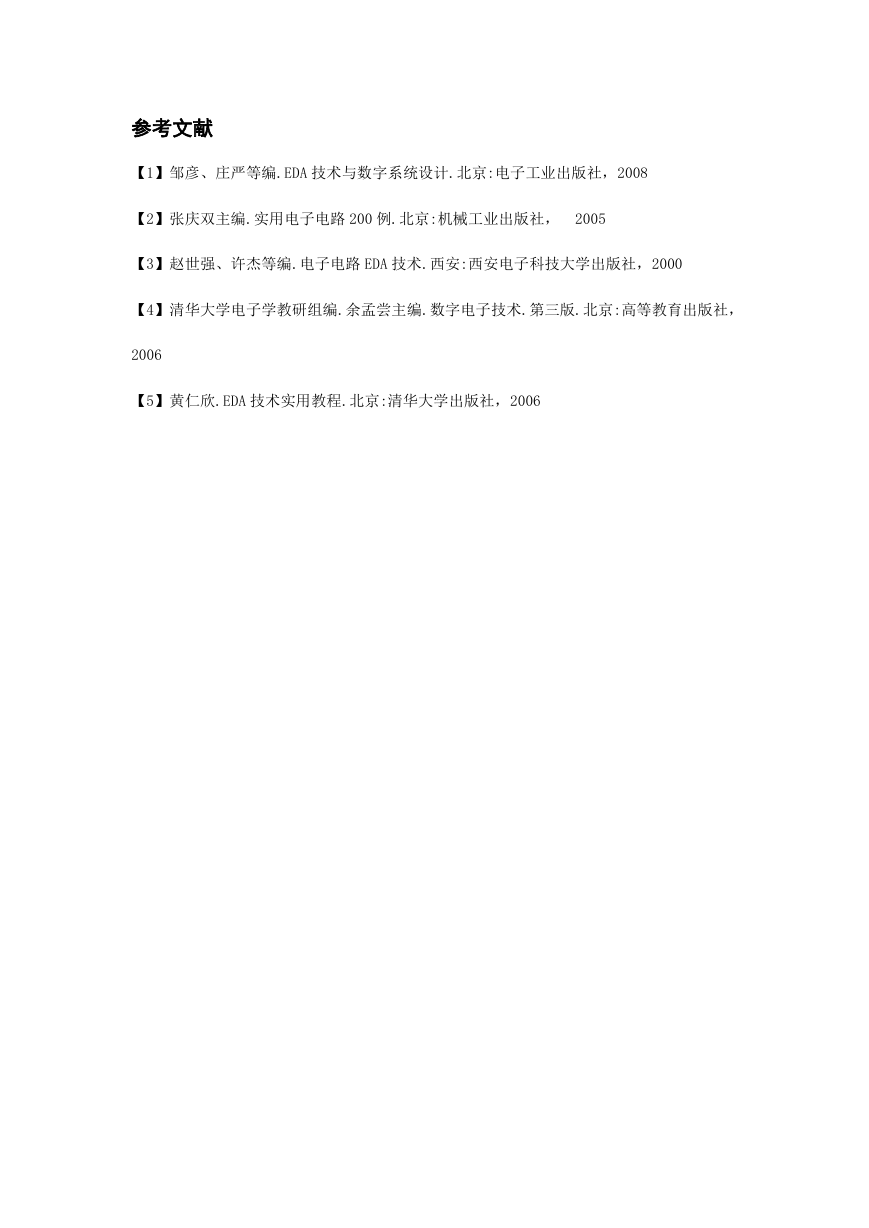

原理图

LC

CLK

LP

LR

BRAKE

NIGHT

LEDL

LEDB

LEDN1

LEDN2

inst1

SZ

CLK

CP

inst3

RC

CLK

RP

LR

BRAKE

NIGHT

inst2

LEDR

LEDB

LEDN1

LEDN2

AND2

inst9

OUTPUT

LLED1

OUTPUT

OUTPUT

LLED2

LLED3

OUTPUT

LLED4

AND2

inst10

OUTPUT

RLED1

OUTPUT

RLED2

OUTPUT

RLED3

OUTPUT

RLED4

仿真波形图

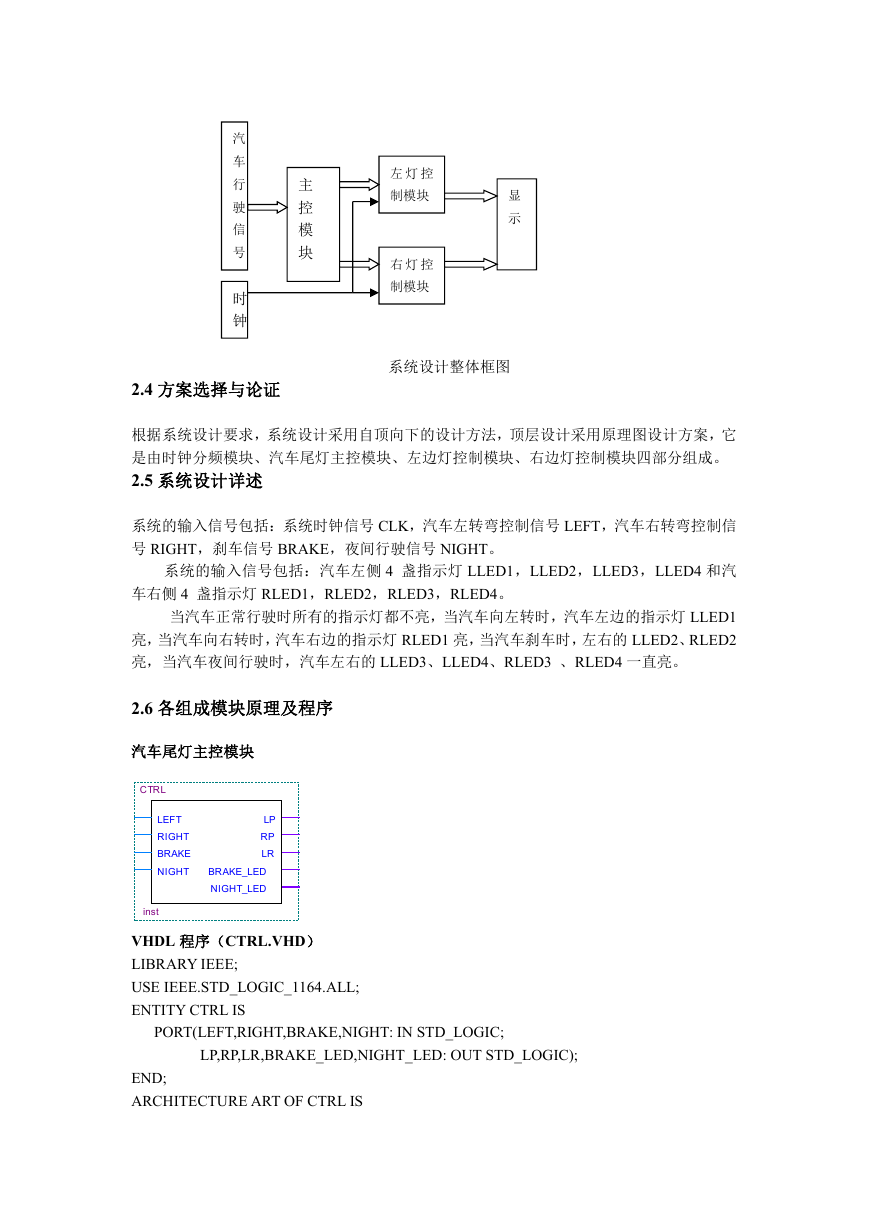

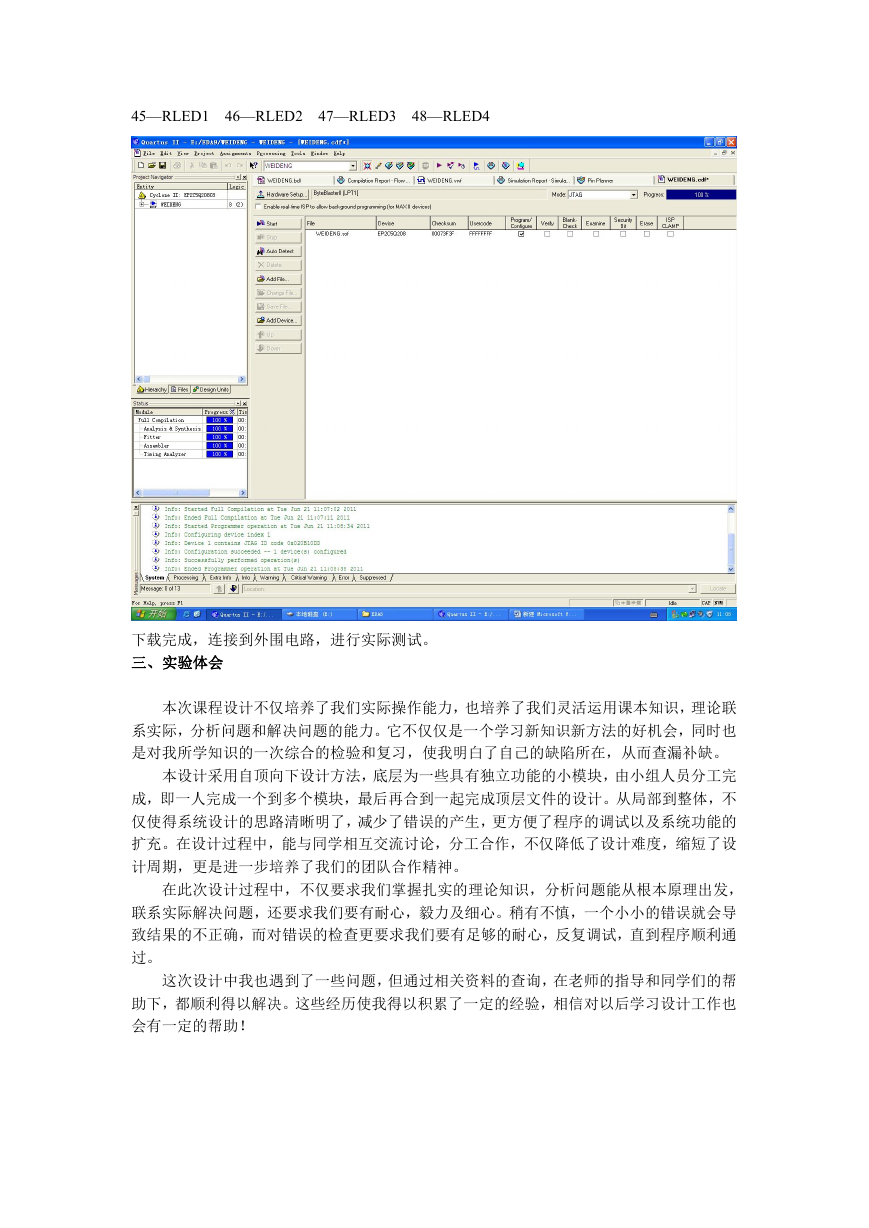

EP2C5Q208C8 管脚

33—CLK

40—LLED1

44—LLED4

34—LEFT 35—RIGHT 36—BRAKE 39—NIGHT

41—LLED2

43—LLED3

�

45—RLED1

46—RLED2

47—RLED3

48—RLED4

下载完成,连接到外围电路,进行实际测试。

三、实验体会

本次课程设计不仅培养了我们实际操作能力,也培养了我们灵活运用课本知识,理论联

系实际,分析问题和解决问题的能力。它不仅仅是一个学习新知识新方法的好机会,同时也

是对我所学知识的一次综合的检验和复习,使我明白了自己的缺陷所在,从而查漏补缺。

本设计采用自顶向下设计方法,底层为一些具有独立功能的小模块,由小组人员分工完

成,即一人完成一个到多个模块,最后再合到一起完成顶层文件的设计。从局部到整体,不

仅使得系统设计的思路清晰明了,减少了错误的产生,更方便了程序的调试以及系统功能的

扩充。在设计过程中,能与同学相互交流讨论,分工合作,不仅降低了设计难度,缩短了设

计周期,更是进一步培养了我们的团队合作精神。

在此次设计过程中,不仅要求我们掌握扎实的理论知识,分析问题能从根本原理出发,

联系实际解决问题,还要求我们要有耐心,毅力及细心。稍有不慎,一个小小的错误就会导

致结果的不正确,而对错误的检查更要求我们要有足够的耐心,反复调试,直到程序顺利通

过。

这次设计中我也遇到了一些问题,但通过相关资料的查询,在老师的指导和同学们的帮

助下,都顺利得以解决。这些经历使我得以积累了一定的经验,相信对以后学习设计工作也

会有一定的帮助!

�

参考文献

【1】邹彦、庄严等编.EDA 技术与数字系统设计.北京:电子工业出版社,2008

【2】张庆双主编.实用电子电路 200 例.北京:机械工业出版社, 2005

【3】赵世强、许杰等编.电子电路 EDA 技术.西安:西安电子科技大学出版社,2000

【4】清华大学电子学教研组编.余孟尝主编.数字电子技术.第三版.北京:高等教育出版社,

2006

【5】黄仁欣.EDA 技术实用教程.北京:清华大学出版社,2006

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc