FFT MegaCore Function User Guide

FFT MegaCore Function

User Guide

101 Innovation Drive

San Jose, CA 95134

www.altera.com

UG-FFT-11.1

Subscribe

�

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

November 2011 Altera Corporation

FFT MegaCore Function

User Guide

�

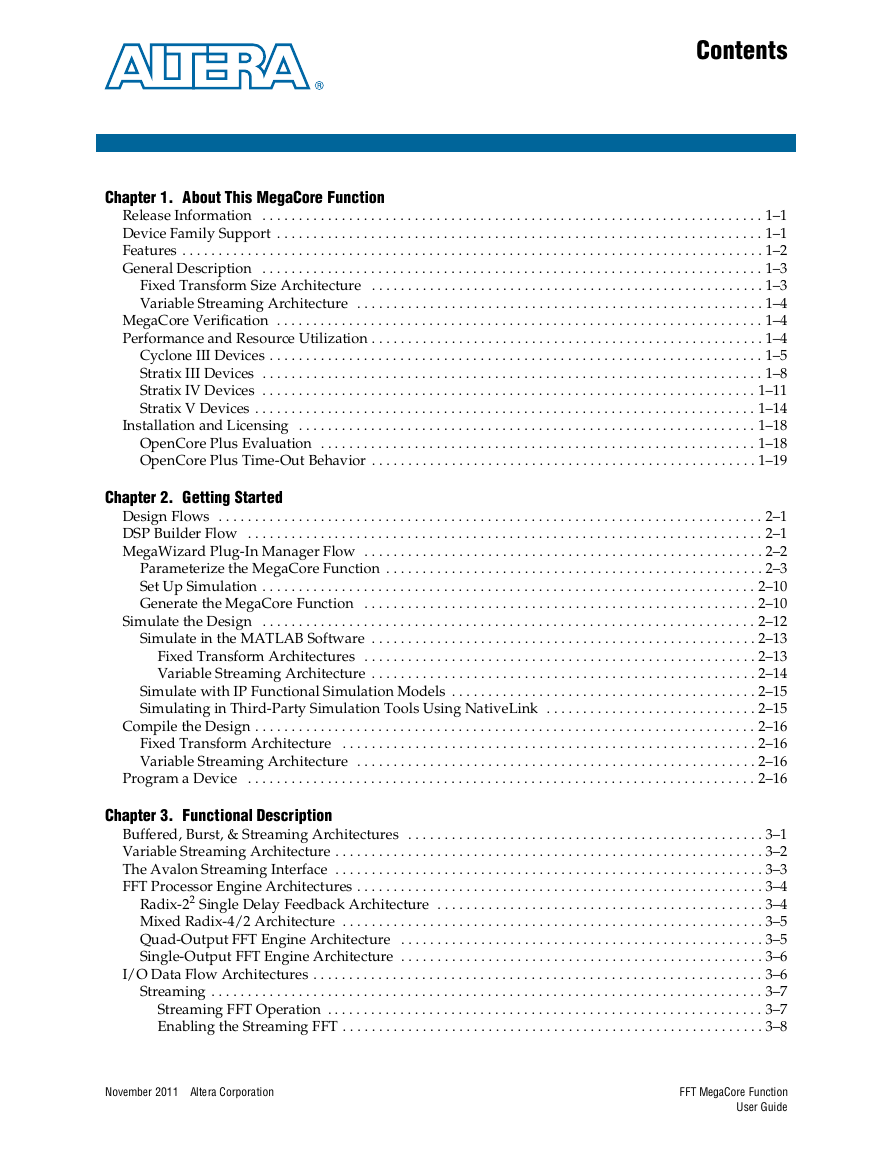

Contents

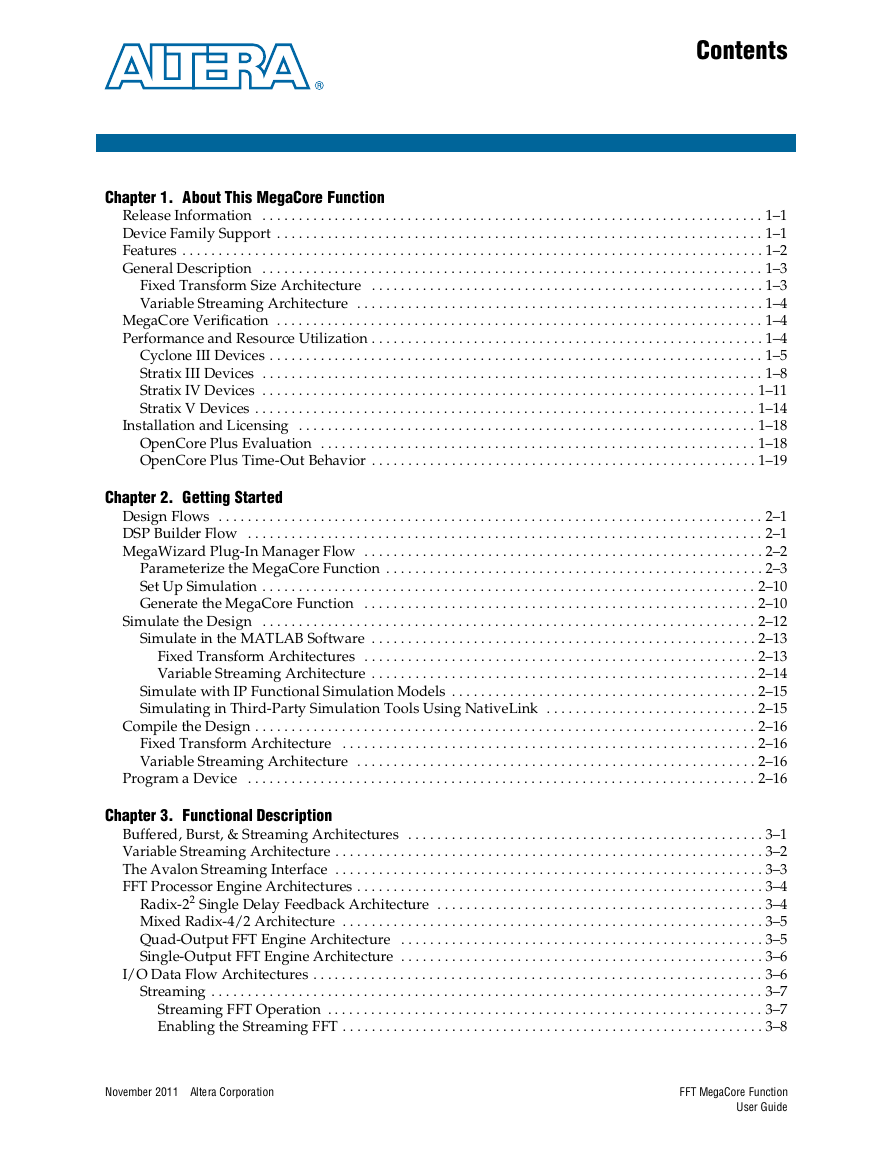

Chapter 1. About This MegaCore Function

Release Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

Device Family Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–2

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

Fixed Transform Size Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

Variable Streaming Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–4

MegaCore Verification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–4

Performance and Resource Utilization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–4

Cyclone III Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–5

Stratix III Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–8

Stratix IV Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–11

Stratix V Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–14

Installation and Licensing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–18

OpenCore Plus Evaluation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–18

OpenCore Plus Time-Out Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–19

Chapter 2. Getting Started

Design Flows . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

DSP Builder Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

MegaWizard Plug-In Manager Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

Parameterize the MegaCore Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

Set Up Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–10

Generate the MegaCore Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–10

Simulate the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–12

Simulate in the MATLAB Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–13

Fixed Transform Architectures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–13

Variable Streaming Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–14

Simulate with IP Functional Simulation Models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–15

Simulating in Third-Party Simulation Tools Using NativeLink . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–15

Compile the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–16

Fixed Transform Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–16

Variable Streaming Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–16

Program a Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–16

Chapter 3. Functional Description

Buffered, Burst, & Streaming Architectures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

Variable Streaming Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

The Avalon Streaming Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

FFT Processor Engine Architectures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Radix-22 Single Delay Feedback Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Mixed Radix-4/2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

Quad-Output FFT Engine Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

Single-Output FFT Engine Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–6

I/O Data Flow Architectures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–6

Streaming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

Streaming FFT Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

Enabling the Streaming FFT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–8

November 2011 Altera Corporation

FFT MegaCore Function

User Guide

�

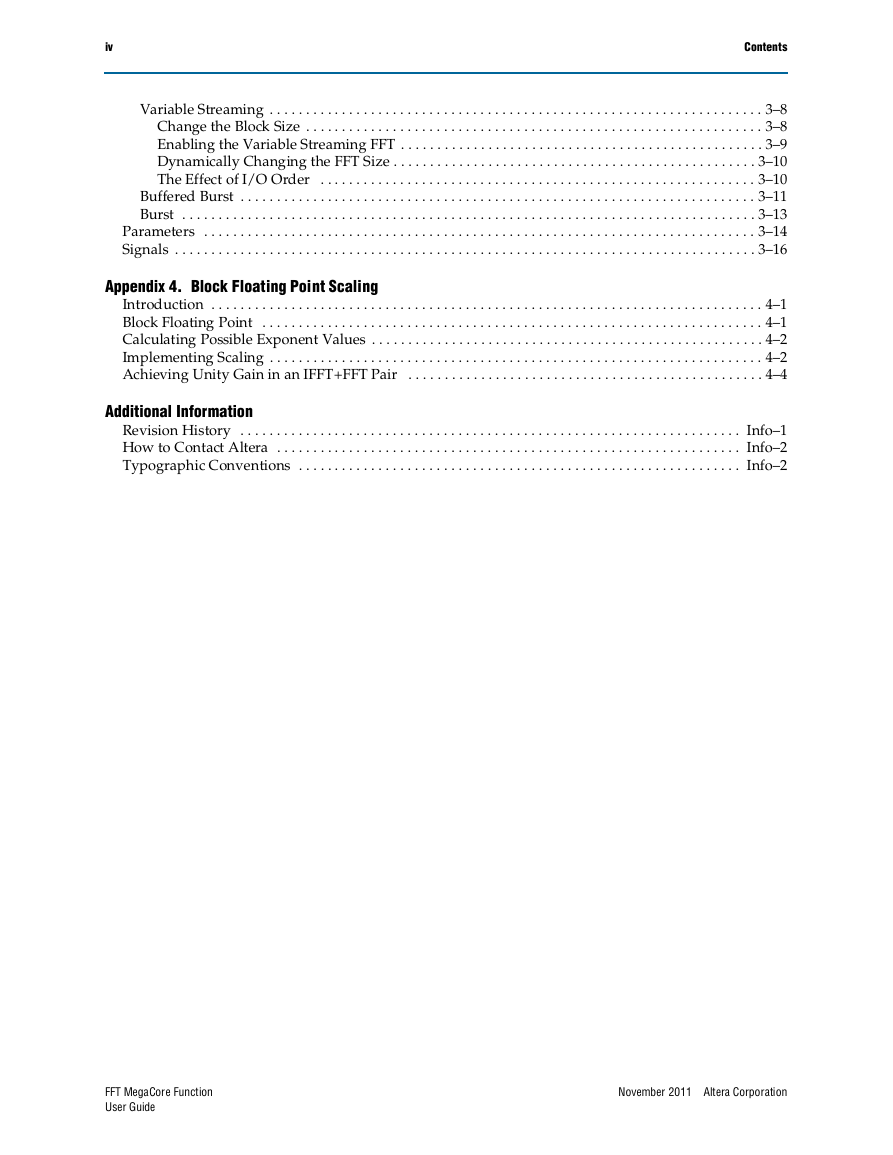

iv

Contents

Variable Streaming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–8

Change the Block Size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–8

Enabling the Variable Streaming FFT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–9

Dynamically Changing the FFT Size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–10

The Effect of I/O Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–10

Buffered Burst . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

Burst . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–13

Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–14

Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–16

Appendix 4. Block Floating Point Scaling

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–1

Block Floating Point . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–1

Calculating Possible Exponent Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–2

Implementing Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–2

Achieving Unity Gain in an IFFT+FFT Pair . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–4

Additional Information

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–2

Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–2

FFT MegaCore Function

User Guide

November 2011 Altera Corporation

�

1. About This MegaCore Function

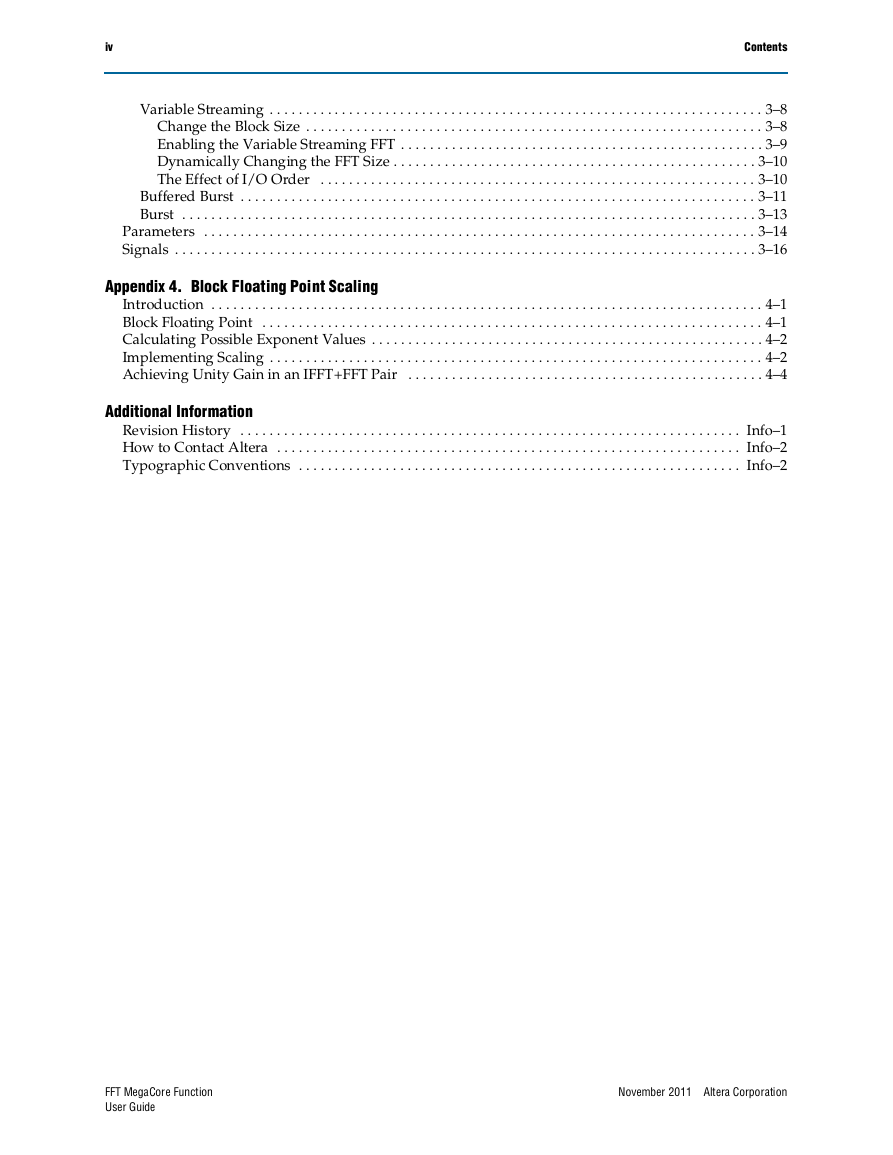

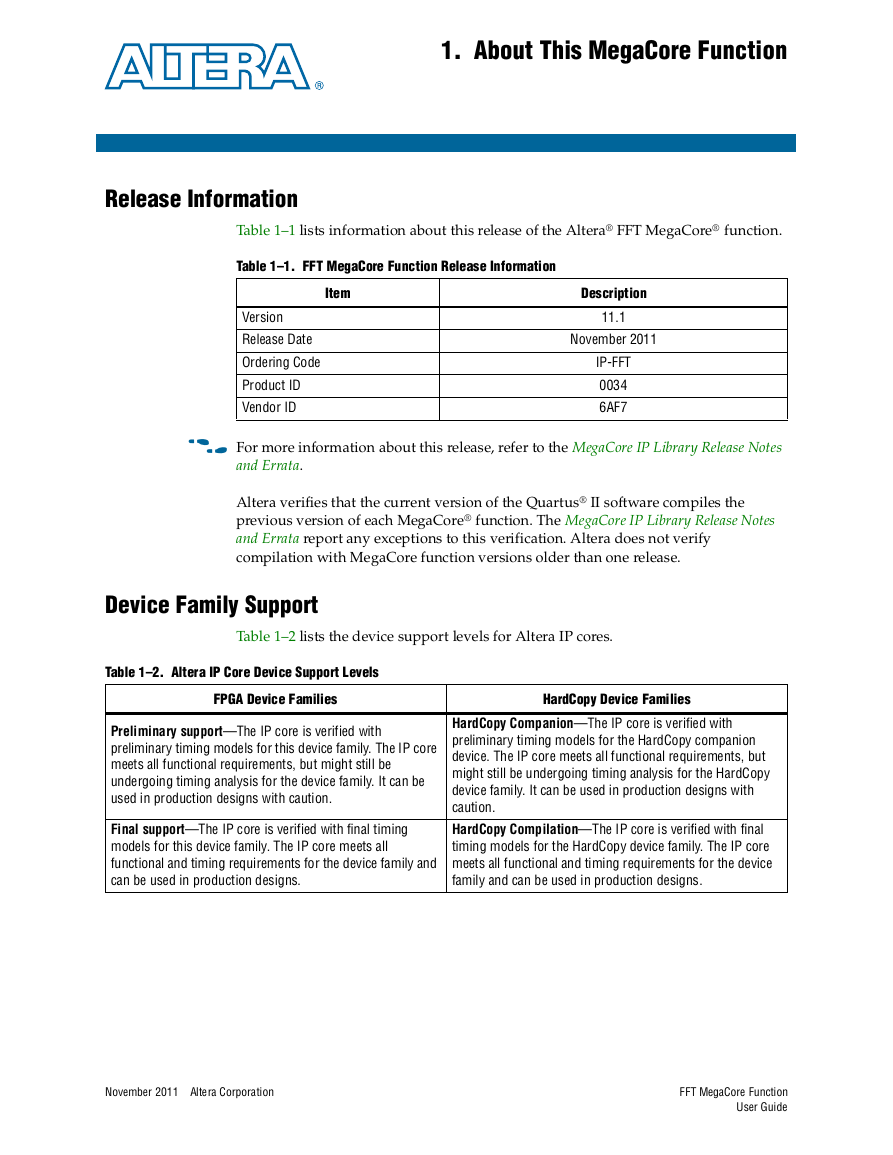

Release Information

Table 1–1 lists information about this release of the Altera® FFT MegaCore® function.

Table 1–1. FFT MegaCore Function Release Information

Item

Version

Release Date

Ordering Code

Product ID

Vendor ID

Description

11.1

November 2011

IP-FFT

0034

6AF7

f For more information about this release, refer to the MegaCore IP Library Release Notes

and Errata.

Altera verifies that the current version of the Quartus® II software compiles the

previous version of each MegaCore® function. The MegaCore IP Library Release Notes

and Errata report any exceptions to this verification. Altera does not verify

compilation with MegaCore function versions older than one release.

Device Family Support

Table 1–2 lists the device support levels for Altera IP cores.

Table 1–2. Altera IP Core Device Support Levels

FPGA Device Families

HardCopy Device Families

Preliminary support—The IP core is verified with

preliminary timing models for this device family. The IP core

meets all functional requirements, but might still be

undergoing timing analysis for the device family. It can be

used in production designs with caution.

Final support—The IP core is verified with final timing

models for this device family. The IP core meets all

functional and timing requirements for the device family and

can be used in production designs.

HardCopy Companion—The IP core is verified with

preliminary timing models for the HardCopy companion

device. The IP core meets all functional requirements, but

might still be undergoing timing analysis for the HardCopy

device family. It can be used in production designs with

caution.

HardCopy Compilation—The IP core is verified with final

timing models for the HardCopy device family. The IP core

meets all functional and timing requirements for the device

family and can be used in production designs.

November 2011 Altera Corporation

FFT MegaCore Function

User Guide

�

1–2

Chapter 1: About This MegaCore Function

Features

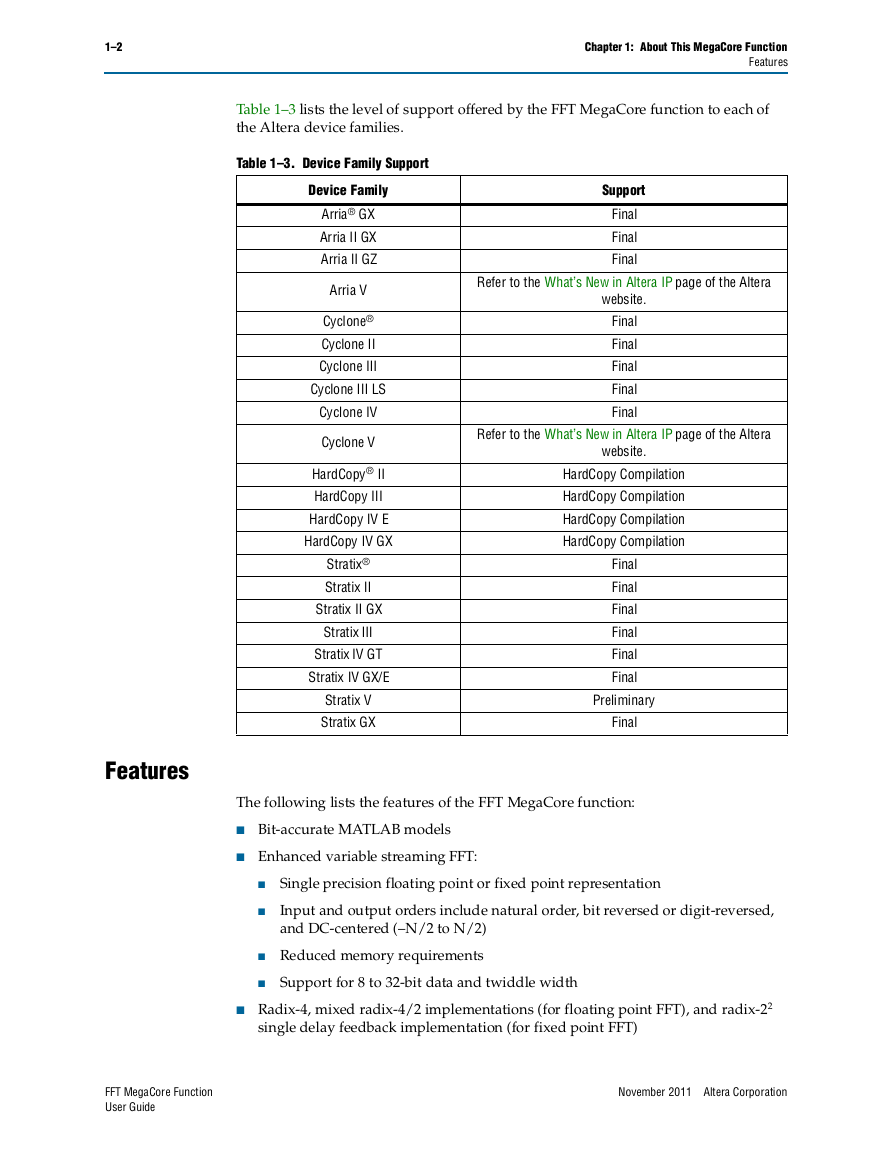

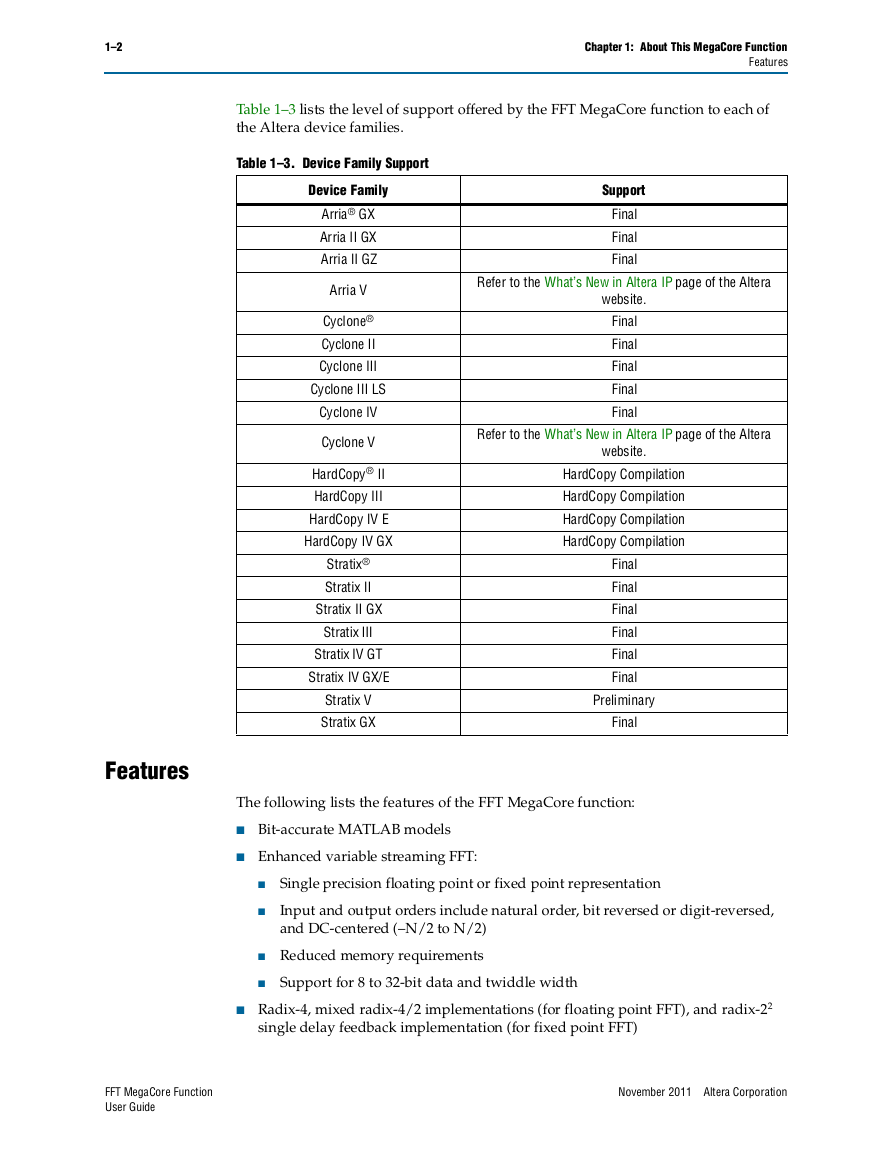

Table 1–3 lists the level of support offered by the FFT MegaCore function to each of

the Altera device families.

Table 1–3. Device Family Support

Device Family

Arria® GX

Arria II GX

Arria II GZ

Arria V

Cyclone®

Cyclone II

Cyclone III

Cyclone III LS

Cyclone IV

Cyclone V

HardCopy® II

HardCopy III

HardCopy IV E

HardCopy IV GX

Stratix®

Stratix II

Stratix II GX

Stratix III

Stratix IV GT

Stratix IV GX/E

Stratix V

Stratix GX

Support

Final

Final

Final

Refer to the What’s New in Altera IP page of the Altera

website.

Final

Final

Final

Final

Final

Refer to the What’s New in Altera IP page of the Altera

website.

HardCopy Compilation

HardCopy Compilation

HardCopy Compilation

HardCopy Compilation

Final

Final

Final

Final

Final

Final

Preliminary

Final

Features

The following lists the features of the FFT MegaCore function:

■ Bit-accurate MATLAB models

■ Enhanced variable streaming FFT:

■ Single precision floating point or fixed point representation

■

Input and output orders include natural order, bit reversed or digit-reversed,

and DC-centered (–N/2 to N/2)

■ Reduced memory requirements

■ Support for 8 to 32-bit data and twiddle width

■ Radix-4, mixed radix-4/2 implementations (for floating point FFT), and radix-22

single delay feedback implementation (for fixed point FFT)

FFT MegaCore Function

User Guide

November 2011 Altera Corporation

�

Chapter 1: About This MegaCore Function

General Description

1–3

■ Block floating-point architecture—maintains the maximum dynamic range of data

during processing (not for variable streaming)

■ Uses embedded memory

■ Maximum system clock frequency more than 300 MHz

■ Optimized to use Stratix series DSP blocks and TriMatrix™ memory

architecture

■ High throughput quad-output radix 4 FFT engine

■ Support for multiple single-output and quad-output engines in parallel

■ Multiple I/O data flow modes: streaming, buffered burst, and burst

■ User control over optimization in DSP blocks or in speed in Stratix V devices, for

streaming, buffered burst, and burst modes and for variable streaming fixed point

mode

■ Avalon® Streaming (Avalon-ST) compliant input and output interfaces

■ Parameterization-specific VHDL and Verilog HDL testbench generation

■ Transform direction (FFT/IFFT) specifiable on a per-block basis

■ Easy-to-use IP Toolbench interface

■ IP functional simulation models for use in Altera-supported VHDL and Verilog

HDL simulators

■ DSP Builder ready

f For more information about Avalon-ST interfaces, refer to the Avalon Interface

Specifications.

General Description

The FFT MegaCore function is a high performance, highly-parameterizable Fast

Fourier transform (FFT) processor. The FFT MegaCore function implements a

complex FFT or inverse FFT (IFFT) for high-performance applications.

The FFT MegaCore function implements the following architectures:

■ Fixed transform size architecture

■ Variable streaming architecture

Fixed Transform Size Architecture

The fixed transform architecture FFT implements a radix-2/4 decimation-in-

frequency (DIF) FFT fixed-transform size algorithm for transform lengths of 2m where

6 m 16. This architecture uses block-floating point representations to achieve the

best trade-off between maximum signal-to-noise ratio (SNR) and minimum size

requirements.

November 2011 Altera Corporation

FFT MegaCore Function

User Guide

�

1–4

Chapter 1: About This MegaCore Function

MegaCore Verification

The fixed transform architecture accepts as an input a two’s complement format

complex data vector of length N, where N is the desired transform length in natural

order; the function outputs the transform-domain complex vector in natural order. An

accumulated block exponent is output to indicate any data scaling that has occurred

during the transform to maintain precision and maximize the internal signal-to-noise

ratio. Transform direction is specifiable on a per-block basis via an input port.

Variable Streaming Architecture

The variable streaming architecture FFT implements two different types of

architecture. The variable streaming FFT variations implement either a radix-22 single

delay feedback architecture, using a fixed-point representation, or a mixed radix-4/2

architecture, using a single precision floating point representation. After you select

your architecture type, you can configure your FFT variation during runtime to

perform the FFT algorithm for transform lengths of 2m where 3 m 18.

The fixed-point representation grows the data widths naturally from input through to

output thereby maintaining a high SNR at the output. The single precision floating

point representation allows a large dynamic range of values to be represented while

maintaining a high SNR at the output.

f For more information about radix-22 single delay feedback architecture, refer to S. He

and M. Torkelson, A New Approach to Pipeline FFT Processor, Department of Applied

Electronics, Lund University, IPPS 1996.

The order of the input data vector of size N can be natural, bit- or digit-reversed, or

–N/2 to N/2 (DC-centered). The fixed-point representation supports a natural,

bit-reversed, or DC-centered order and the floating point representation supports a

natural, digit-reversed, or DC-centered order. The architecture outputs the

transform-domain complex vector in natural, bit-reversed, or digit-reversed order.

The transform direction is specifiable on a per-block basis using an input port.

MegaCore Verification

Before releasing a version of the FFT MegaCore function, Altera runs comprehensive

regression tests to verify its quality and correctness.

Custom variations of the FFT MegaCore function are generated to exercise its various

parameter options, and the resulting simulation models are thoroughly simulated

with the results verified against master simulation models.

Performance and Resource Utilization

Performance varies depending on the FFT engine architecture and I/O data flow. All

data represents the geometric mean of a three seed Quartus II synthesis sweep.

1 Cyclone III devices use combinational look-up tables (LUTs) and logic registers;

Stratix III devices use combinational adaptive look-up tables (ALUTs) and logic

registers.

FFT MegaCore Function

User Guide

November 2011 Altera Corporation

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc