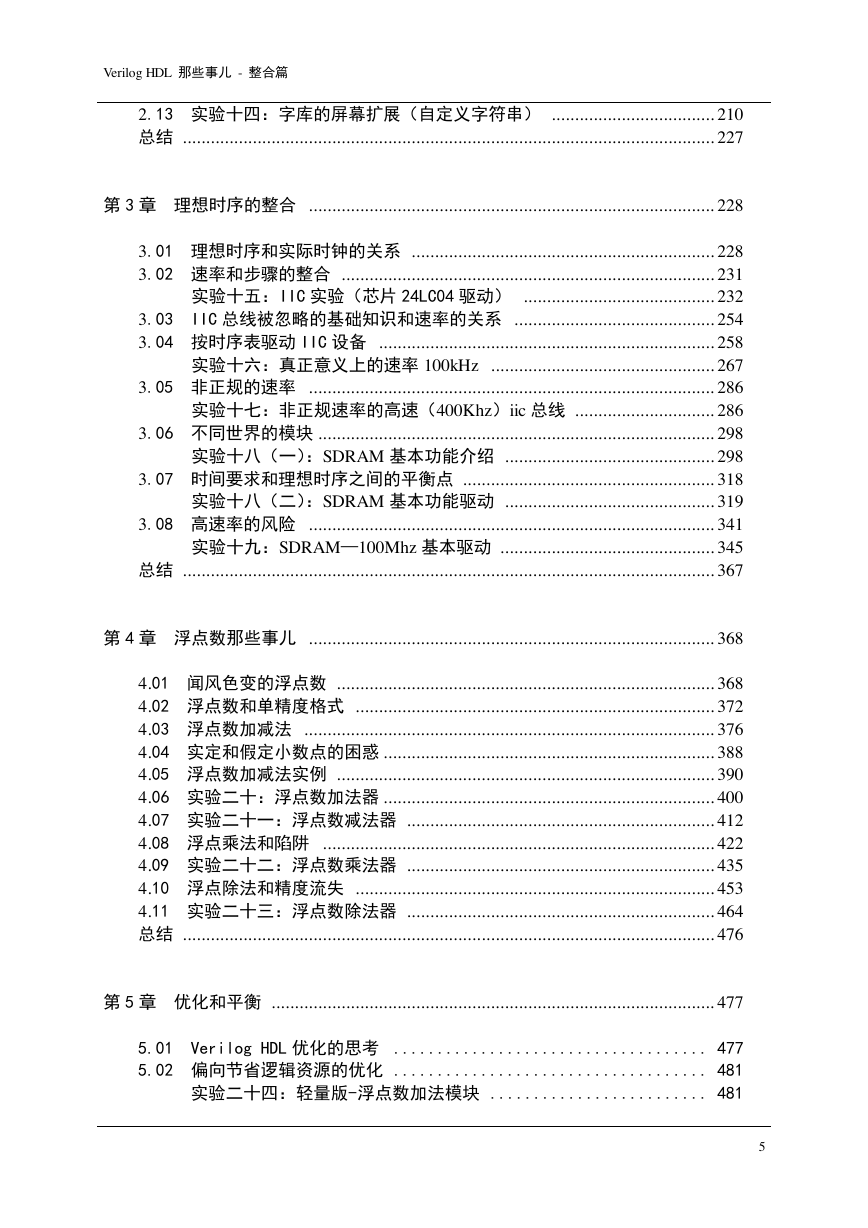

目录

第一章 整合的概念

1.1源码上的整合

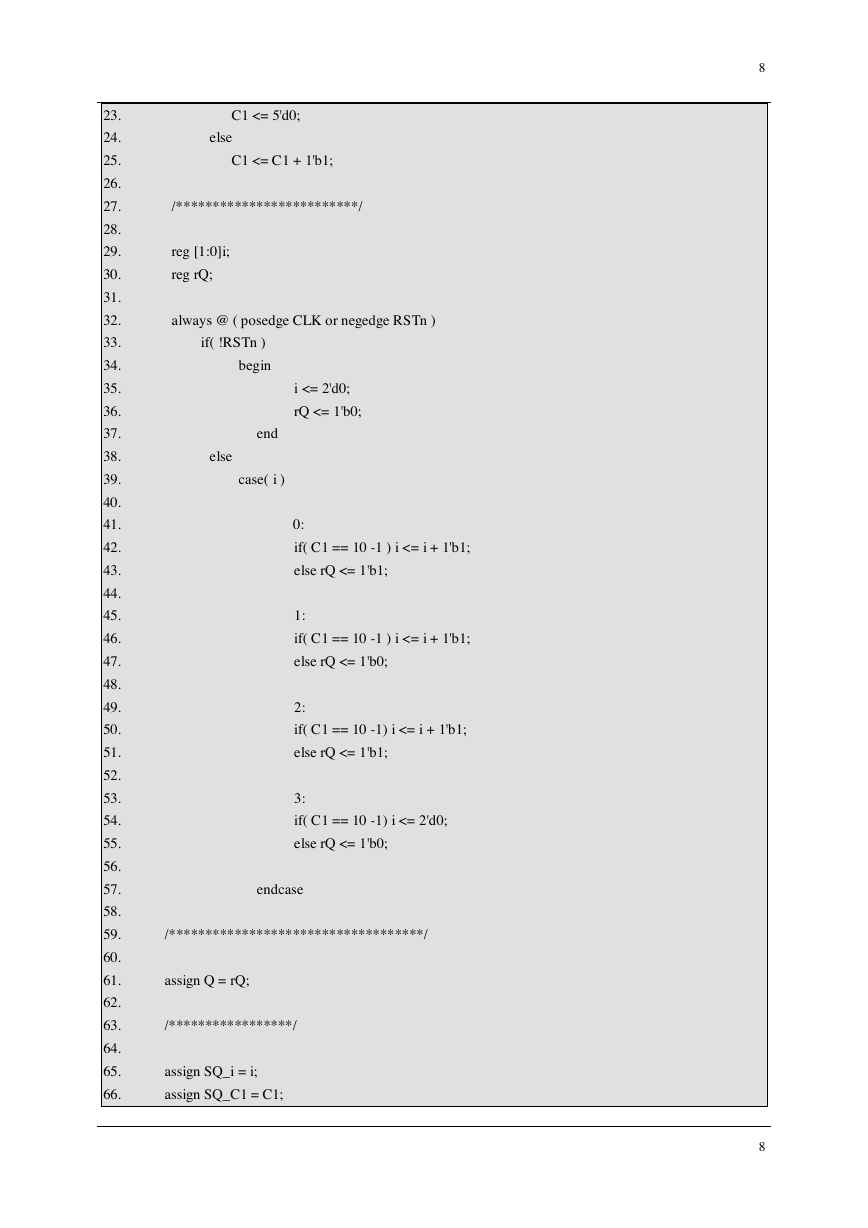

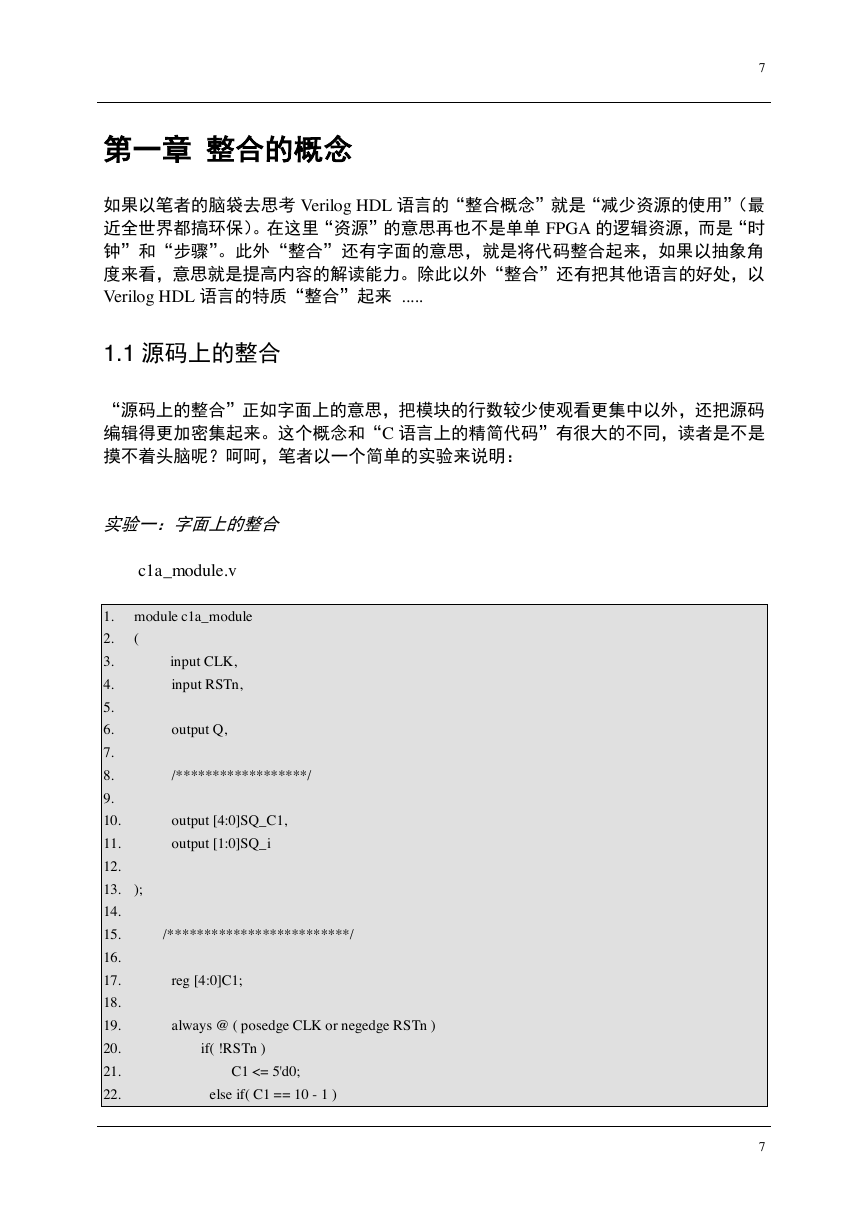

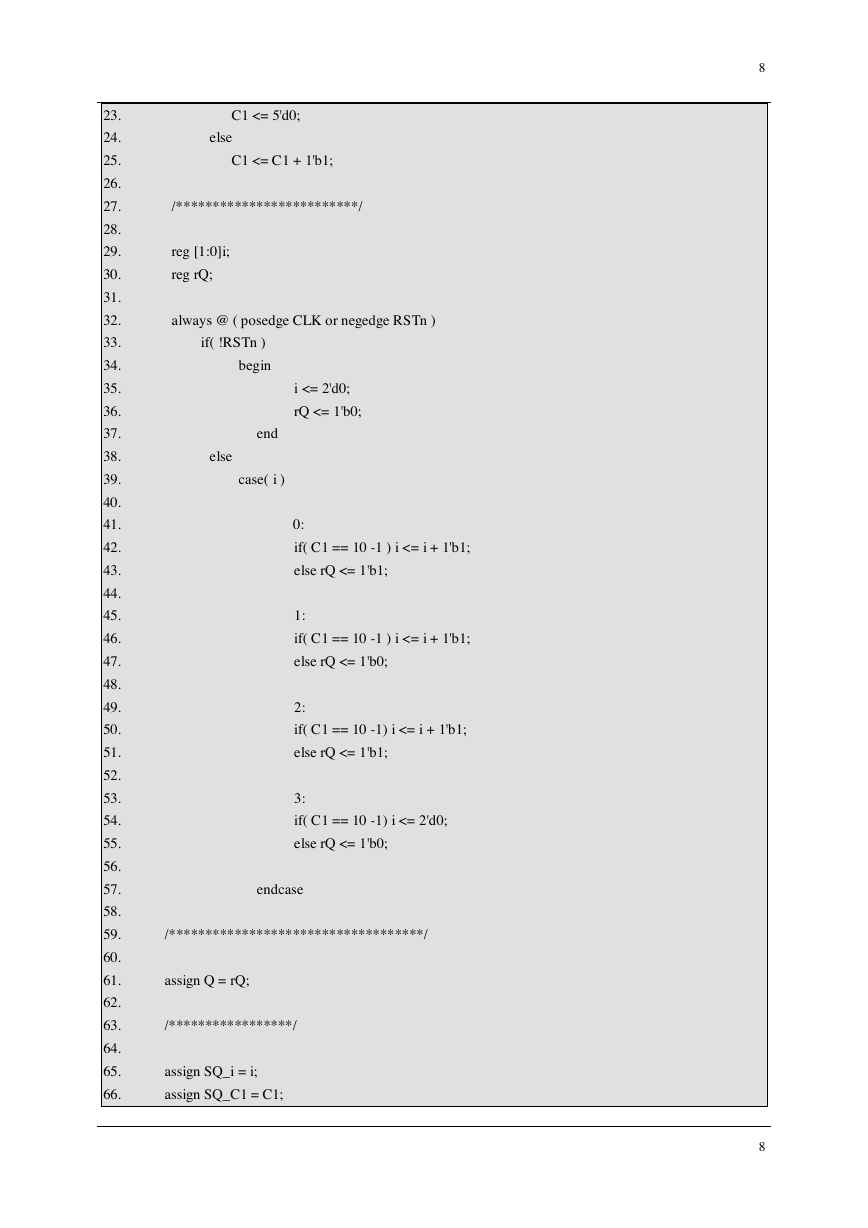

实验一:字面上的整合

c1a_module.v

clb_module.v

1.2 时钟和步骤的定义

1.3 有效的使用资源(资源上的整合)

实验二:资源上的整合

c2a_module.v

c2a_module.vt

仿真结果:

c2b_module.v

c2b_module.vt

仿真结果:

1.4 循环保留和循环操作

1.5 把C语言的好处(循环)整合进来

1.6 把C语言的好处(嵌入循环)整合进来

1.7 把C语言的好处(动作的关系)整合进来

1.8 步骤的循环和时序的循环之间的区别

1.9 实验三 :串口发送模块

tx_module.v

tx_module.vt

仿真结果:

1.10实验四 :串口发送模块2

tx_module2.v

tx_module2.vt

仿真结果:

1.11 模块之间调用的延迟

实验五:被延迟的数据

rom_module.v

control_module.v

exp5_env.v

exp5_env.vt

仿真结果:

1.12 同步数据的几个想法

实验六:加上过路寄存器

exp06_env.v

exp6_env.vt

仿真结果:

实验七:用循环操作来同步数据

control_module.v

exp7_env.vt

仿真结果:

总结:

第二章 - 时钟化和信号的长度

2.1 一个时钟一块数据的概念

2.2 信号时钟化

2.3 深入了解“模块的沟通”

2.4 电平检测模块的整合(即时事件在时序上的不和谐)

实验八:电平检测模块

detect_module.v

detect_module.vt

仿真结果:

exp2_4a.vt

2.5电平检测模块的整合(即时事件在模块沟通上的不和谐)

2.6 实验九:串口接收模块

rx_module.v

exp09_env.v

exp09_env.vt

仿真结果:

2.7 不同执行模式的“定时器和计数器”

exp2_7a.vt

exp2_7b.vt

2.8 计算N个长度的工具

2.9 实验十:重新设计vga模块

sync_module.v

rom_module.v

vga_module.v

2.10 主动设计的概念和模块的语言

实验十一:两个小屏幕

vga_control_module2.v

vga_module.v

2.11 实验十二:皮卡丘的HP血条

ram_module1.v

screen_control_module.v

screen_interface1.v

screen_system.v

2.12实验十三:我的小小字库

格式化

字库模块(rom模块)说明

字符

命令

ziku_control_module1.v

vga_control_module3.v

screen_interface2.v

demo_control_module.v

screen_system.v

2.13 实验十四:字库的屏幕扩张 (自定义字符串)

vga_control_module4.v

ziku_control_module2.v

screen_interface3.v

string_generate_module.v

screen_system.v

总结:

第三章 理想时序的整合

3.1 理想时钟和实际时钟的关系

3.2 速率和步骤的整合

实验十五:IIC实验(芯片—24LC04驱动)

iic_func_module.v

exp15_demo.v

3.3 iic总线被忽略的基础知识和速率的关系。

3.4 按时序表驱动iic设备。

实验十六:真正意义上的速率100Khz

iic_func_module.v

exp16_demo.v

iic_func_module.vt

仿真结果:

3.5 非正规的速率

实验十七:非正规速率的高速(400Khz)iic总线

iic_func_module.v

exp17_demo.v

3.6 不同世界的模块

实验十八(一) SDRAM基本功能介绍

SDRAM初始化:

定时自动刷新:

写一字操作:

读一字数据操作:

3.7 时间要求与理想时序之间的平衡点

实验十八(二)SDRAM基本功能驱动

sdram_init_module.v

iic_func_module.v

sdram_ctrl_module.v

sdram_module.v

sdram_demo.v

3.8 高速率的风险

实验十九 :SDRAM—100Mhz基本驱动

sdram_initial_module.v

sdram_func_module.v

sdram_control_module.v

sdram_module3.v

sdram_demo3.v

总结:

第四章 浮点数那些事儿

4.1 闻风色变的浮点数

4.2 浮点数和单精度格式

4.3浮点数加减法

4.4 实定和假定小数点的困惑

4.5 浮点数加减法实例

4.6 实验二十:浮点数加法器

float_add_module.v

float_add_module.vt

仿真结果:

4.7 实验二十一:浮点数减法器

float_sub_module.v

float_sub_module.vt

4.8 浮点乘法和陷阱

4.9 实验二十二:浮点数乘法器

float_multi_module.v

float_multi_module.vt

仿真结果:

4.10 浮点除法和精度流失

4.11 实验二十三:浮点数除法模块

float_divide_module.v

float_divide_module.vt

仿真结果:

总结:

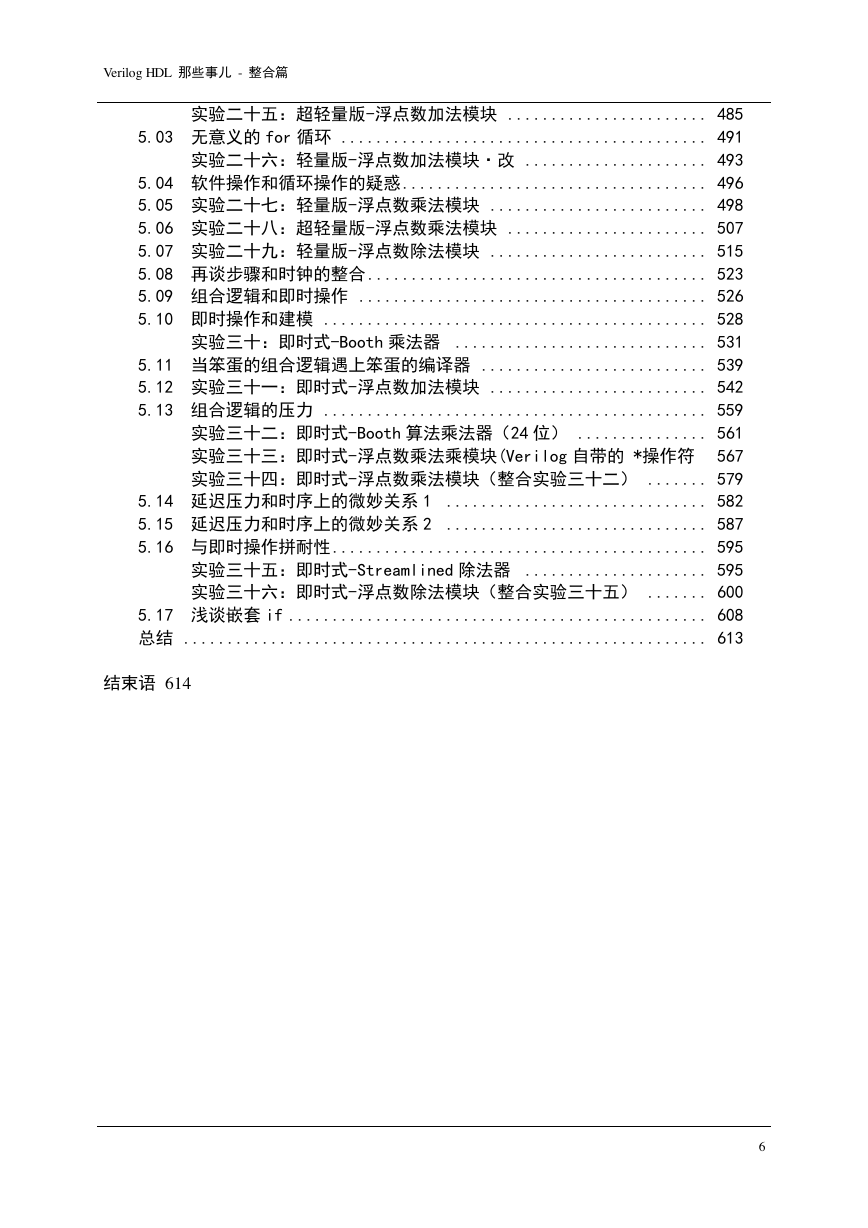

第五章 优化和平衡

5.1 Verilog HDL优化的思考

5.2 偏向节省逻辑资源的优化

实验二十四:轻量版-浮点数加法模块

float_add_module_light.v

实验二十五:超轻量版-浮点数加法模块

float_add_module_light2.v

5.3 无意义的for循环

实验二十六:轻量版-浮点数加法模块 改

float_add_module_light2.v

仿真结果:

5.4 软件操作和循环操作的疑惑

5.5 实验二十七:轻量版-浮点数乘法模块

booth_multiplier_module_2.v

float_multi_module_light2.v

仿真结果:

5.6实验二十八:超轻量版-浮点数乘法模块

booth_multiplier_module_2.v

float_multiplier_module_light2.v

仿真结果:

5.7 实验二十九:轻量版-浮点数除法模块

streamlined_divider_module.v

float_divide_module_light.v

仿真结果:

5.8 再谈步骤和时钟的整合

5.9 组合逻辑和即时操作

5.10 即时操作和建模

实验三十:即时式Booth乘法器

immediate_booth_multiplier_module.v

immediate_booth_multiplier_module.vt

仿真结果:

5.11 当笨蛋的组合逻辑遇上笨蛋的编译器

5.12 实验三十一:即时式-浮点数加法模块

immediate_float_add_module.v

immediate_float_add_module.vt

仿真结果:

5.13 组合逻辑的压力

实验三十二:即时式-Booth算法乘法器(24位)

immediate_booth_multiplier_module.v

immediate_booth_multiplier_module.vt

实验三十三:即时式-浮点数乘法模块(Verilog 自带的 *操作符)

immediate_float_multi_module.v

immediate_float_multi_module.vt

仿真结果:

实验三十四:即时式-浮点数乘法模块(整合实验三十二)

immediate_float_multi_module.v

5.14 延迟压力和时序上的微妙关系1

5.15 延迟压力和时序上的微妙关系2

5.16 与即时操作拼耐性

实验三十五:即时式-Streamlined除法器

immediate_divide_module.v

实验三十六:即时式-浮点数除法模块 ( 整合实验三十五 )

immediate_float_divide_module.v

immediate_float_divide_module.v

仿真结果:

5.17 浅谈嵌套 if

总结:

结束语

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc