EDA 电子闹钟设计

学校:福建师范大学

学院:数学与计算机科学学院

专业:电子信息科学与技术

姓名:花和尚-------2009 级

学号:01001010

01000011 01001011

一、闹钟实现的基本功能要求。

(1)、实现调整时间,闹钟时间。

(2)、二十四小时进制。

(3)、在能在 1602 LCD 显示器上显示 调整的时间及显

示时间。

(4)、到达设定的时间能能输出一千 HZ 的脉冲

(5)、在调整时 能在相应的位置闪烁

二、闹钟的基本结构

(1)、三个按键(复位,选择调整位置,调整信号)

(2)、六个模块(消除抖动,分频,时间计时,闹钟时间

设定,译码控制,LCD1602 驱动)

(3)、四个输入信号,五个输出信号,顶层文件如图。

1

�

三、 基本操作

加电后下载程序,然后按选择键当看到作者后再按一次回

到 初始界面。再按一次复位键闹钟就可以工作了。

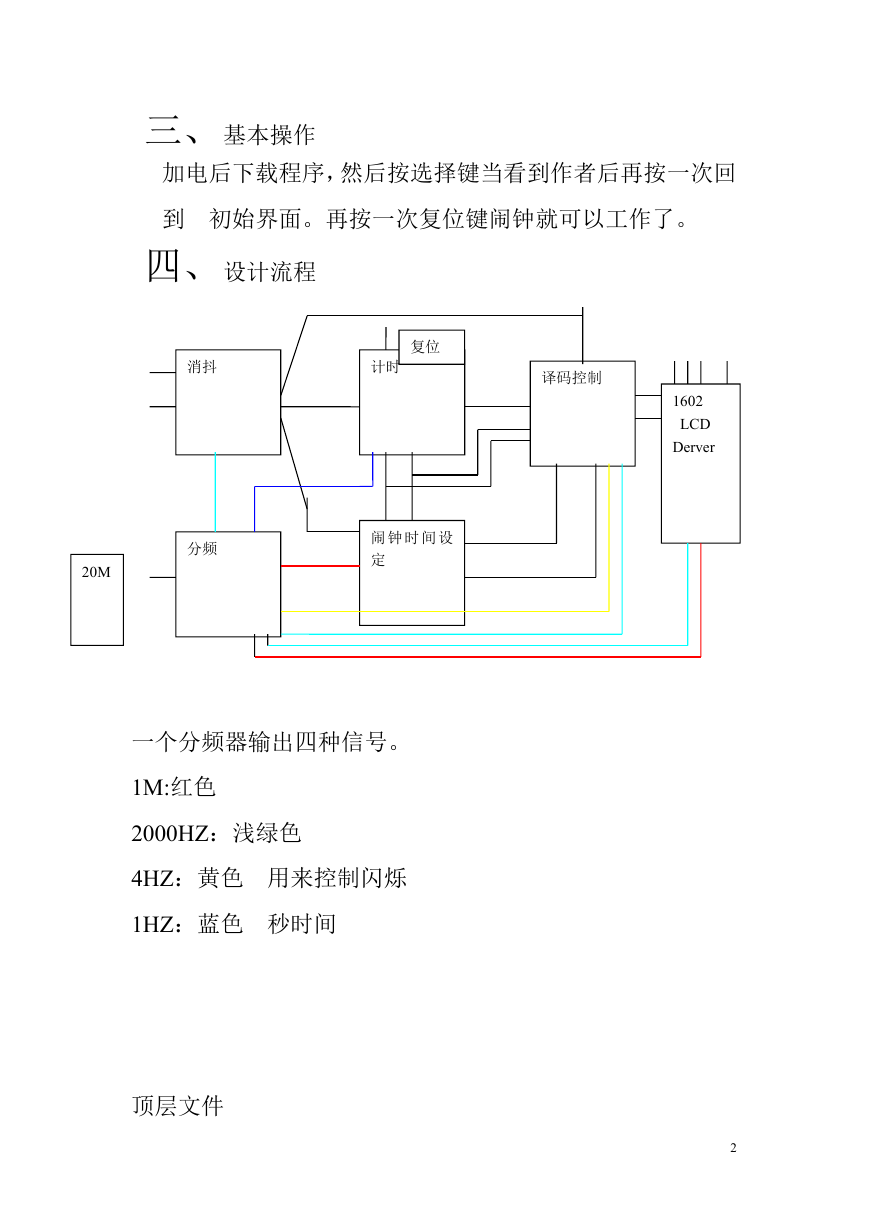

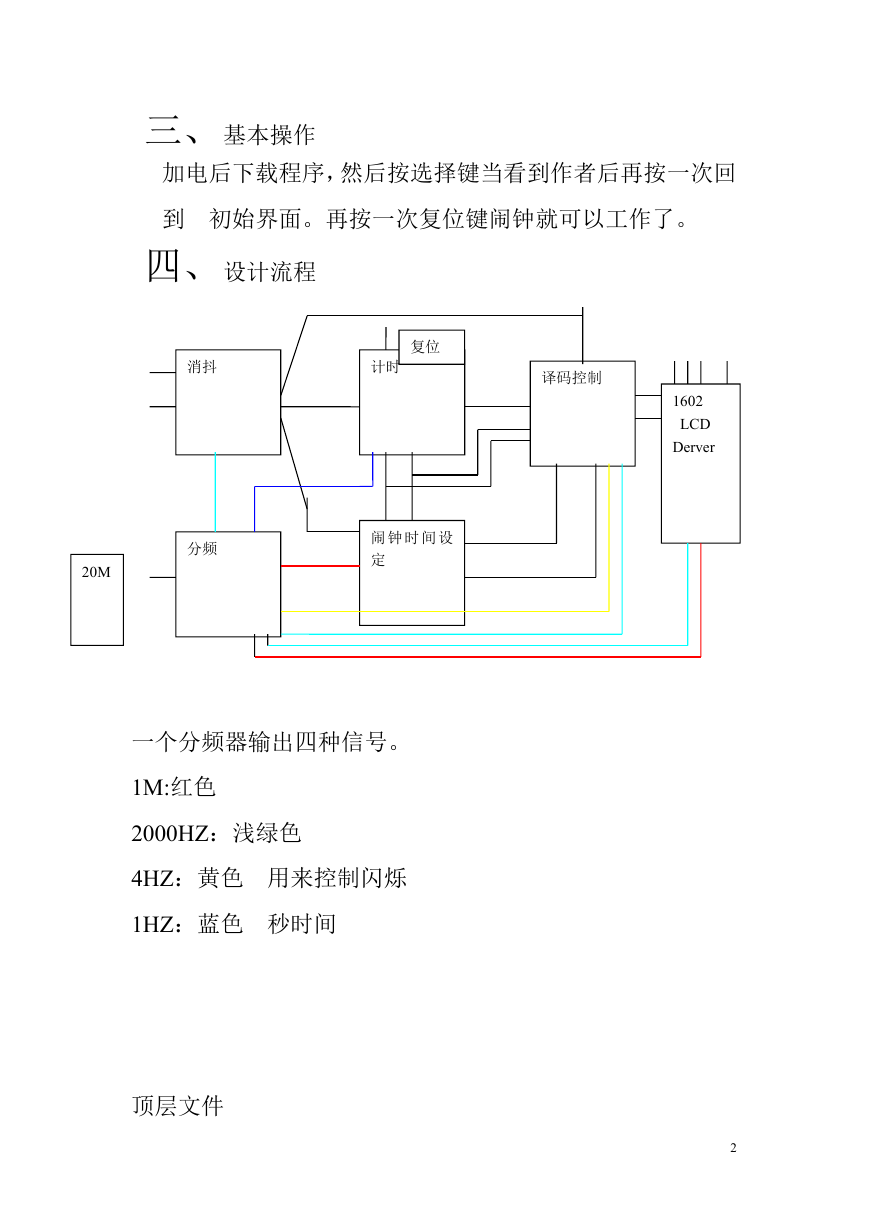

四、 设计流程

消抖

复位

计时

译码控制

1602

LCD

Derver

分频

20M

闹 钟 时 间 设

定

一个分频器输出四种信号。

1M:红色

2000HZ:浅绿色

4HZ:黄色 用来控制闪烁

1HZ:蓝色 秒时间

顶层文件

2

�

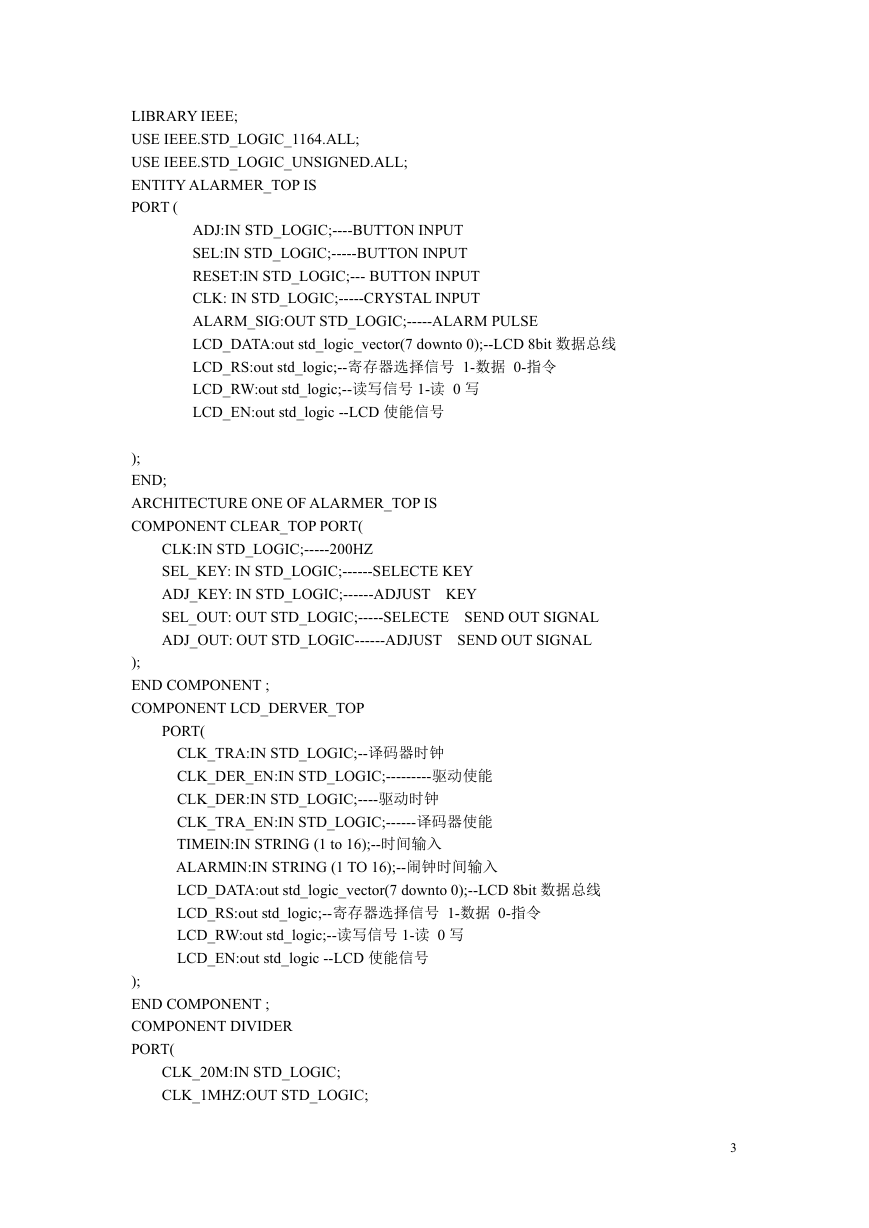

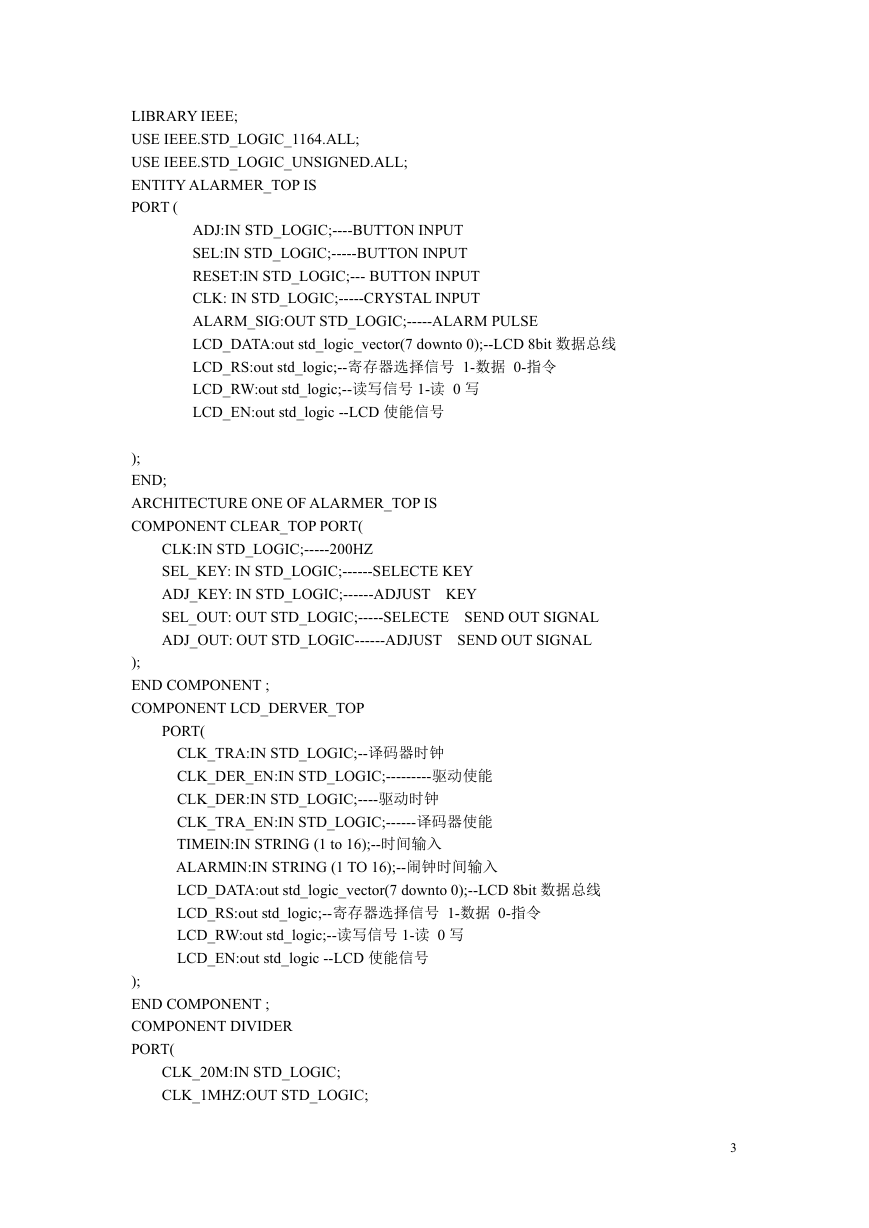

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ALARMER_TOP IS

PORT (

ADJ:IN STD_LOGIC;----BUTTON INPUT

SEL:IN STD_LOGIC;-----BUTTON INPUT

RESET:IN STD_LOGIC;--- BUTTON INPUT

CLK: IN STD_LOGIC;-----CRYSTAL INPUT

ALARM_SIG:OUT STD_LOGIC;-----ALARM PULSE

LCD_DATA:out std_logic_vector(7 downto 0);--LCD 8bit 数据总线

LCD_RS:out std_logic;--寄存器选择信号 1-数据 0-指令

LCD_RW:out std_logic;--读写信号 1-读 0 写

LCD_EN:out std_logic --LCD 使能信号

);

END;

ARCHITECTURE ONE OF ALARMER_TOP IS

COMPONENT CLEAR_TOP PORT(

CLK:IN STD_LOGIC;-----200HZ

SEL_KEY: IN STD_LOGIC;------SELECTE KEY

ADJ_KEY: IN STD_LOGIC;------ADJUST KEY

SEL_OUT: OUT STD_LOGIC;-----SELECTE SEND OUT SIGNAL

ADJ_OUT: OUT STD_LOGIC------ADJUST SEND OUT SIGNAL

);

END COMPONENT ;

COMPONENT LCD_DERVER_TOP

PORT(

CLK_TRA:IN STD_LOGIC;--译码器时钟

CLK_DER_EN:IN STD_LOGIC;---------驱动使能

CLK_DER:IN STD_LOGIC;----驱动时钟

CLK_TRA_EN:IN STD_LOGIC;------译码器使能

TIMEIN:IN STRING (1 to 16);--时间输入

ALARMIN:IN STRING (1 TO 16);--闹钟时间输入

LCD_DATA:out std_logic_vector(7 downto 0);--LCD 8bit 数据总线

LCD_RS:out std_logic;--寄存器选择信号 1-数据 0-指令

LCD_RW:out std_logic;--读写信号 1-读 0 写

LCD_EN:out std_logic --LCD 使能信号

);

END COMPONENT ;

COMPONENT DIVIDER

PORT(

CLK_20M:IN STD_LOGIC;

CLK_1MHZ:OUT STD_LOGIC;

3

�

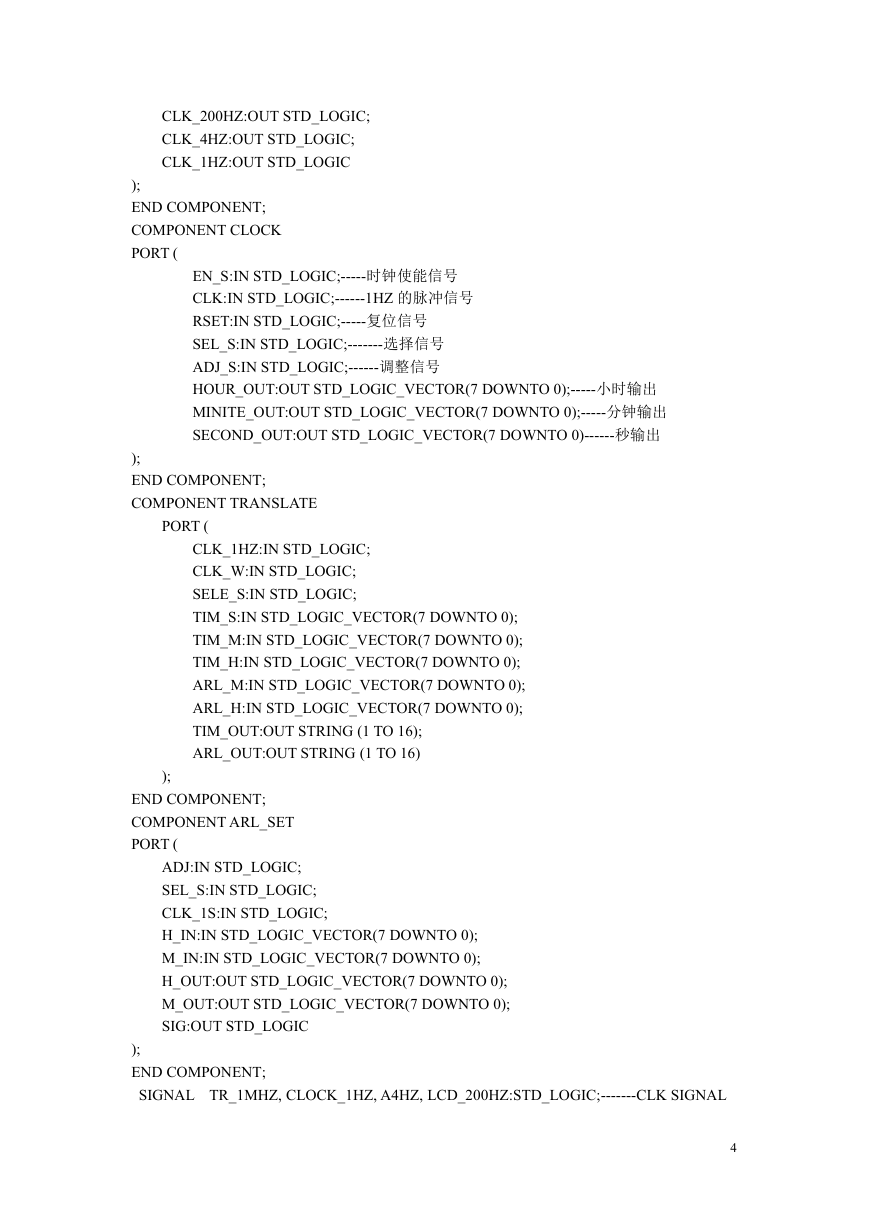

CLK_200HZ:OUT STD_LOGIC;

CLK_4HZ:OUT STD_LOGIC;

CLK_1HZ:OUT STD_LOGIC

);

END COMPONENT;

COMPONENT CLOCK

PORT (

EN_S:IN STD_LOGIC;-----时钟使能信号

CLK:IN STD_LOGIC;------1HZ 的脉冲信号

RSET:IN STD_LOGIC;-----复位信号

SEL_S:IN STD_LOGIC;-------选择信号

ADJ_S:IN STD_LOGIC;------调整信号

HOUR_OUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);-----小时输出

MINITE_OUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);-----分钟输出

SECOND_OUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)------秒输出

);

END COMPONENT;

COMPONENT TRANSLATE

PORT (

CLK_1HZ:IN STD_LOGIC;

CLK_W:IN STD_LOGIC;

SELE_S:IN STD_LOGIC;

TIM_S:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

TIM_M:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

TIM_H:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

ARL_M:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

ARL_H:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

TIM_OUT:OUT STRING (1 TO 16);

ARL_OUT:OUT STRING (1 TO 16)

);

END COMPONENT;

COMPONENT ARL_SET

PORT (

ADJ:IN STD_LOGIC;

SEL_S:IN STD_LOGIC;

CLK_1S:IN STD_LOGIC;

H_IN:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

M_IN:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

H_OUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

M_OUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

SIG:OUT STD_LOGIC

);

END COMPONENT;

SIGNAL TR_1MHZ, CLOCK_1HZ, A4HZ, LCD_200HZ:STD_LOGIC;-------CLK SIGNAL

4

�

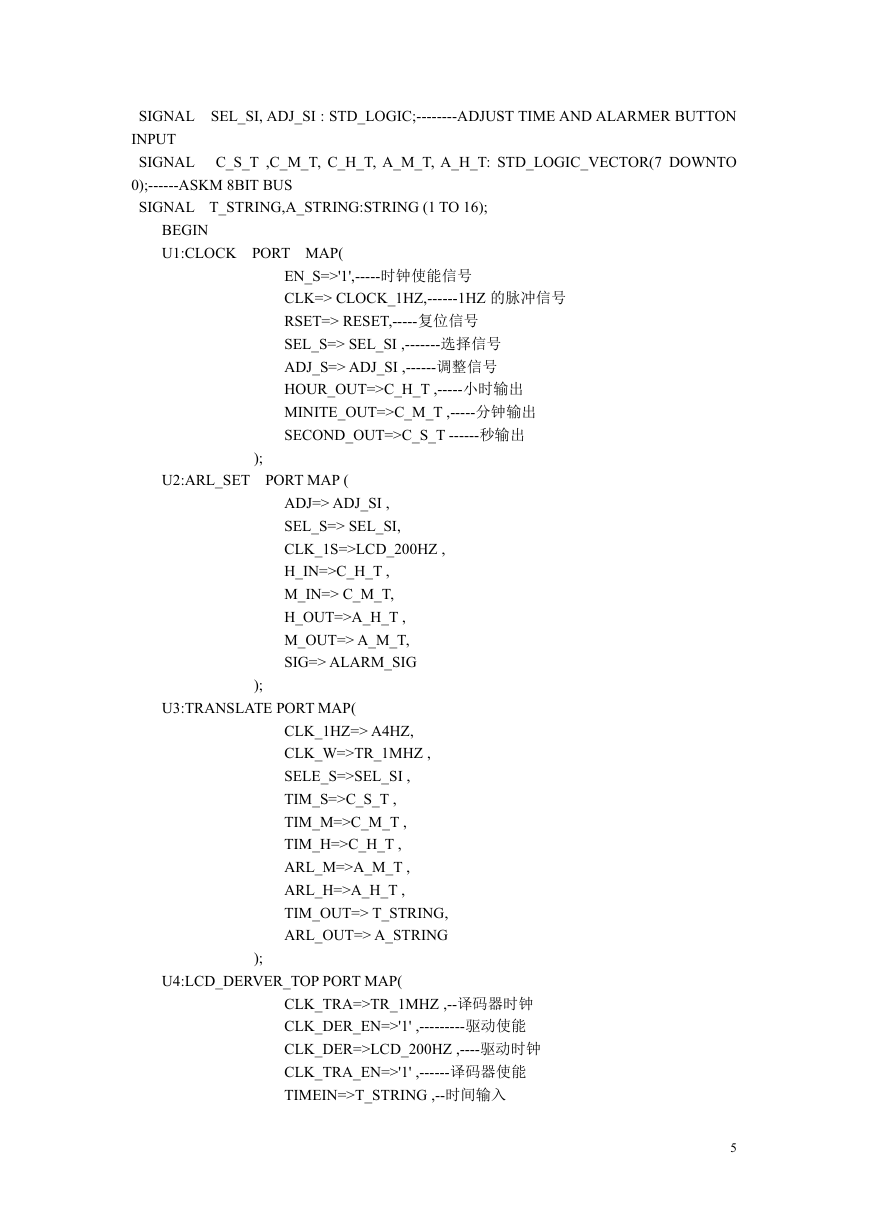

SIGNAL SEL_SI, ADJ_SI : STD_LOGIC;--------ADJUST TIME AND ALARMER BUTTON

INPUT

SIGNAL

0);------ASKM 8BIT BUS

SIGNAL T_STRING,A_STRING:STRING (1 TO 16);

C_S_T ,C_M_T, C_H_T, A_M_T, A_H_T: STD_LOGIC_VECTOR(7 DOWNTO

BEGIN

U1:CLOCK PORT MAP(

EN_S=>'1',-----时钟使能信号

CLK=> CLOCK_1HZ,------1HZ 的脉冲信号

RSET=> RESET,-----复位信号

SEL_S=> SEL_SI ,-------选择信号

ADJ_S=> ADJ_SI ,------调整信号

HOUR_OUT=>C_H_T ,-----小时输出

MINITE_OUT=>C_M_T ,-----分钟输出

SECOND_OUT=>C_S_T ------秒输出

);

U2:ARL_SET PORT MAP (

ADJ=> ADJ_SI ,

SEL_S=> SEL_SI,

CLK_1S=>LCD_200HZ ,

H_IN=>C_H_T ,

M_IN=> C_M_T,

H_OUT=>A_H_T ,

M_OUT=> A_M_T,

SIG=> ALARM_SIG

);

U3:TRANSLATE PORT MAP(

CLK_1HZ=> A4HZ,

CLK_W=>TR_1MHZ ,

SELE_S=>SEL_SI ,

TIM_S=>C_S_T ,

TIM_M=>C_M_T ,

TIM_H=>C_H_T ,

ARL_M=>A_M_T ,

ARL_H=>A_H_T ,

TIM_OUT=> T_STRING,

ARL_OUT=> A_STRING

);

U4:LCD_DERVER_TOP PORT MAP(

CLK_TRA=>TR_1MHZ ,--译码器时钟

CLK_DER_EN=>'1' ,---------驱动使能

CLK_DER=>LCD_200HZ ,----驱动时钟

CLK_TRA_EN=>'1' ,------译码器使能

TIMEIN=>T_STRING ,--时间输入

5

�

ALARMIN=>A_STRING ,--闹钟时间输入

LCD_DATA=>LCD_DATA ,--LCD 8bit 数据总线

LCD_RS=>LCD_RS ,--寄存器选择信号 1-数据 0-指令

LCD_RW=>LCD_RW ,--读写信号 1-读 0 写

LCD_EN=>LCD_EN --LCD 使能信号

);

U5:CLEAR_TOP PORT MAP (

CLK=>LCD_200HZ ,-----200HZ

SEL_KEY=>SEL ,------SELECTE KEY

ADJ_KEY=> ADJ,------ADJUST KEY

SEL_OUT=>SEL_SI ,-----SELECTE SEND OUT SIGNAL

ADJ_OUT=>ADJ_SI ------ADJUST SEND OUT SIGNAL

);

U6:DIVIDER PORT MAP (

CLK_20M=>CLK ,

CLK_1MHZ=>TR_1MHZ ,

CLK_200HZ=>LCD_200HZ ,

CLK_4HZ=>A4HZ ,

CLK_1HZ=>CLOCK_1HZ

);

END;

五、 各个模块的功能及其代码

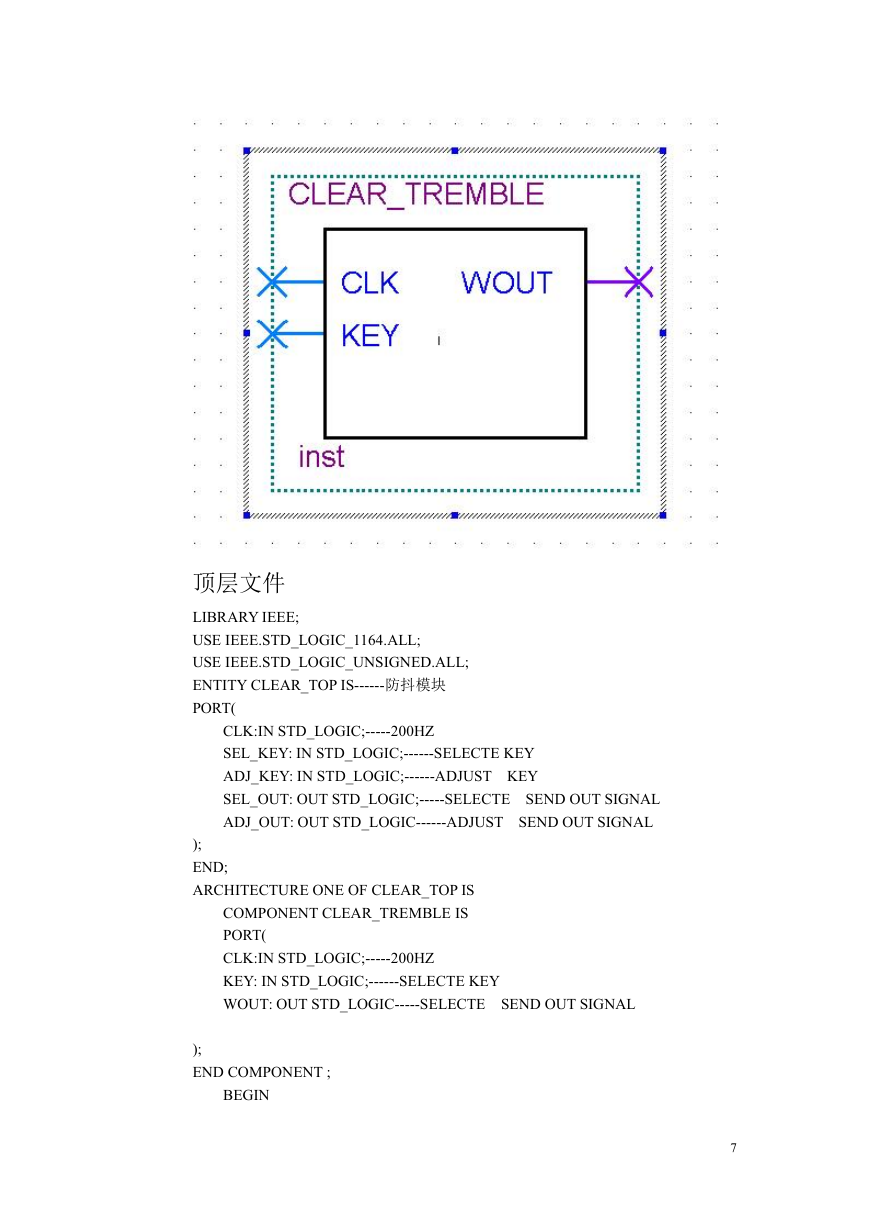

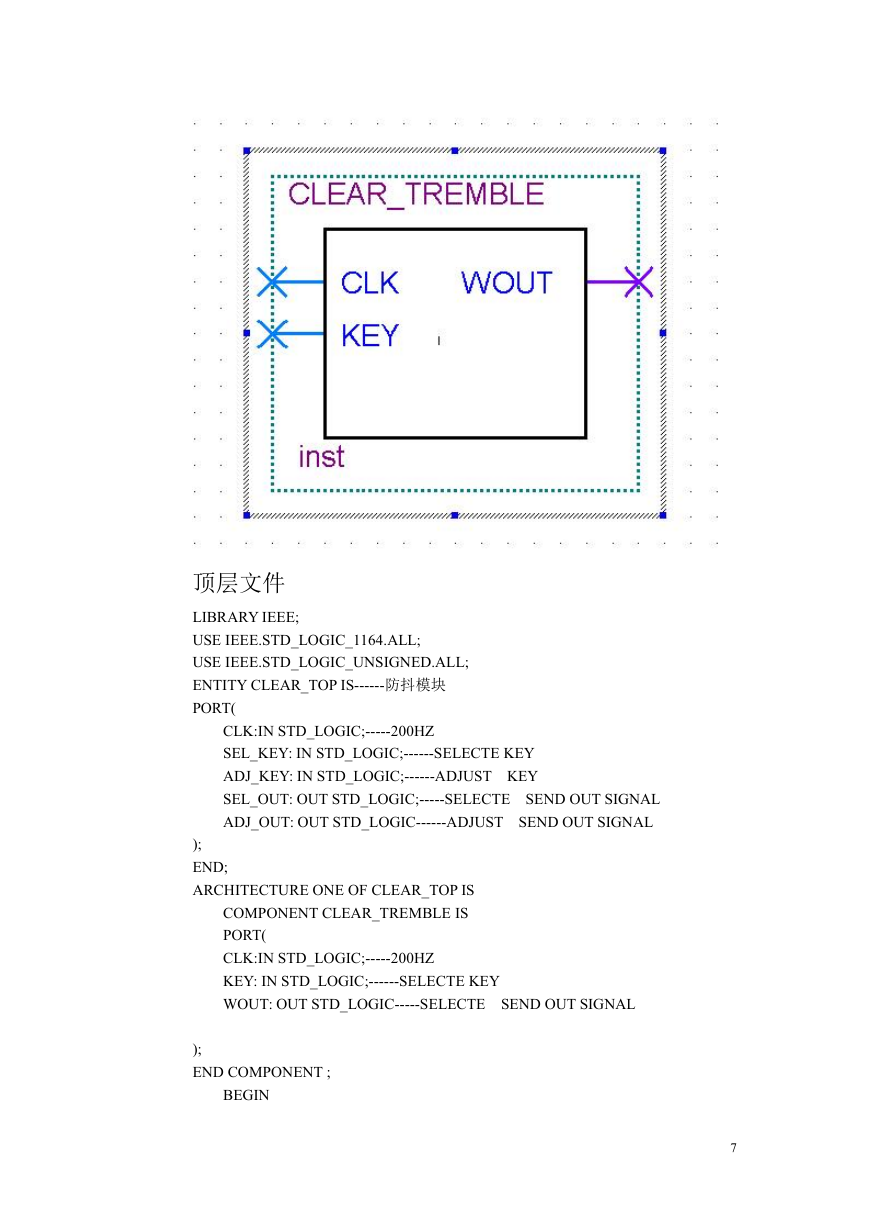

(1)、消除抖动模块

消除抖动有很多的方法,有在某段时间里取第一个上

升沿,有某个信号(高电平或者低电平)持续某个时

间值以上,有的信号在长按得情况下能输出一个连续

平稳脉冲。总而言之就是不能让一次按键输入产生多

次按键输入信号。这里使用的是在某个信号持续 5 毫

秒以上算一次信号。代码如下

这里的消抖不能实现两个按键同事按下 同时生效

6

�

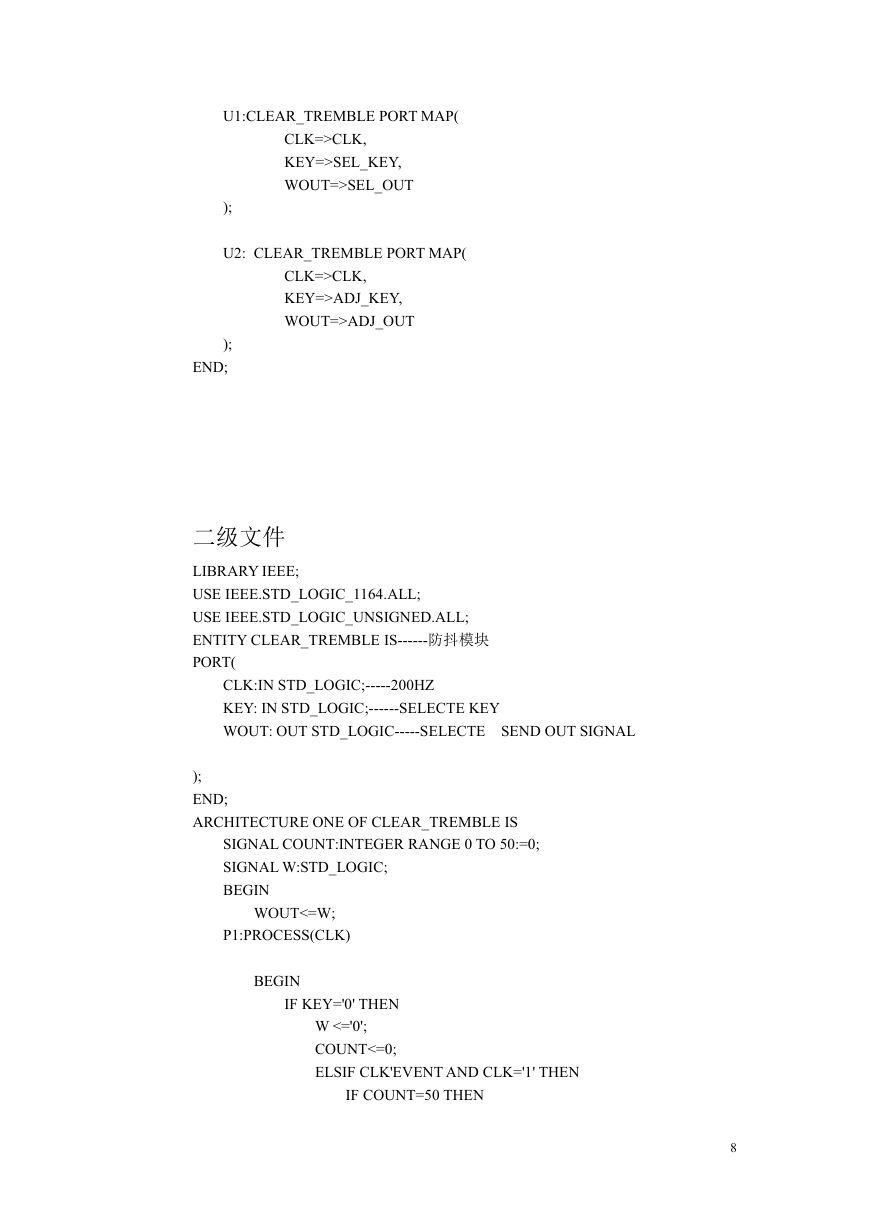

顶层文件

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CLEAR_TOP IS------防抖模块

PORT(

CLK:IN STD_LOGIC;-----200HZ

SEL_KEY: IN STD_LOGIC;------SELECTE KEY

ADJ_KEY: IN STD_LOGIC;------ADJUST KEY

SEL_OUT: OUT STD_LOGIC;-----SELECTE SEND OUT SIGNAL

ADJ_OUT: OUT STD_LOGIC------ADJUST SEND OUT SIGNAL

);

END;

ARCHITECTURE ONE OF CLEAR_TOP IS

COMPONENT CLEAR_TREMBLE IS

PORT(

CLK:IN STD_LOGIC;-----200HZ

KEY: IN STD_LOGIC;------SELECTE KEY

WOUT: OUT STD_LOGIC-----SELECTE SEND OUT SIGNAL

);

END COMPONENT ;

BEGIN

7

�

U1:CLEAR_TREMBLE PORT MAP(

CLK=>CLK,

KEY=>SEL_KEY,

WOUT=>SEL_OUT

);

U2: CLEAR_TREMBLE PORT MAP(

CLK=>CLK,

KEY=>ADJ_KEY,

WOUT=>ADJ_OUT

);

END;

二级文件

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CLEAR_TREMBLE IS------防抖模块

PORT(

CLK:IN STD_LOGIC;-----200HZ

KEY: IN STD_LOGIC;------SELECTE KEY

WOUT: OUT STD_LOGIC-----SELECTE SEND OUT SIGNAL

);

END;

ARCHITECTURE ONE OF CLEAR_TREMBLE IS

SIGNAL COUNT:INTEGER RANGE 0 TO 50:=0;

SIGNAL W:STD_LOGIC;

BEGIN

WOUT<=W;

P1:PROCESS(CLK)

BEGIN

IF KEY='0' THEN

W <='0';

COUNT<=0;

ELSIF CLK'EVENT AND CLK='1' THEN

IF COUNT=50 THEN

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc