OLE_LINK18

OLE_LINK19

OLE_LINK20

OLE_LINK22

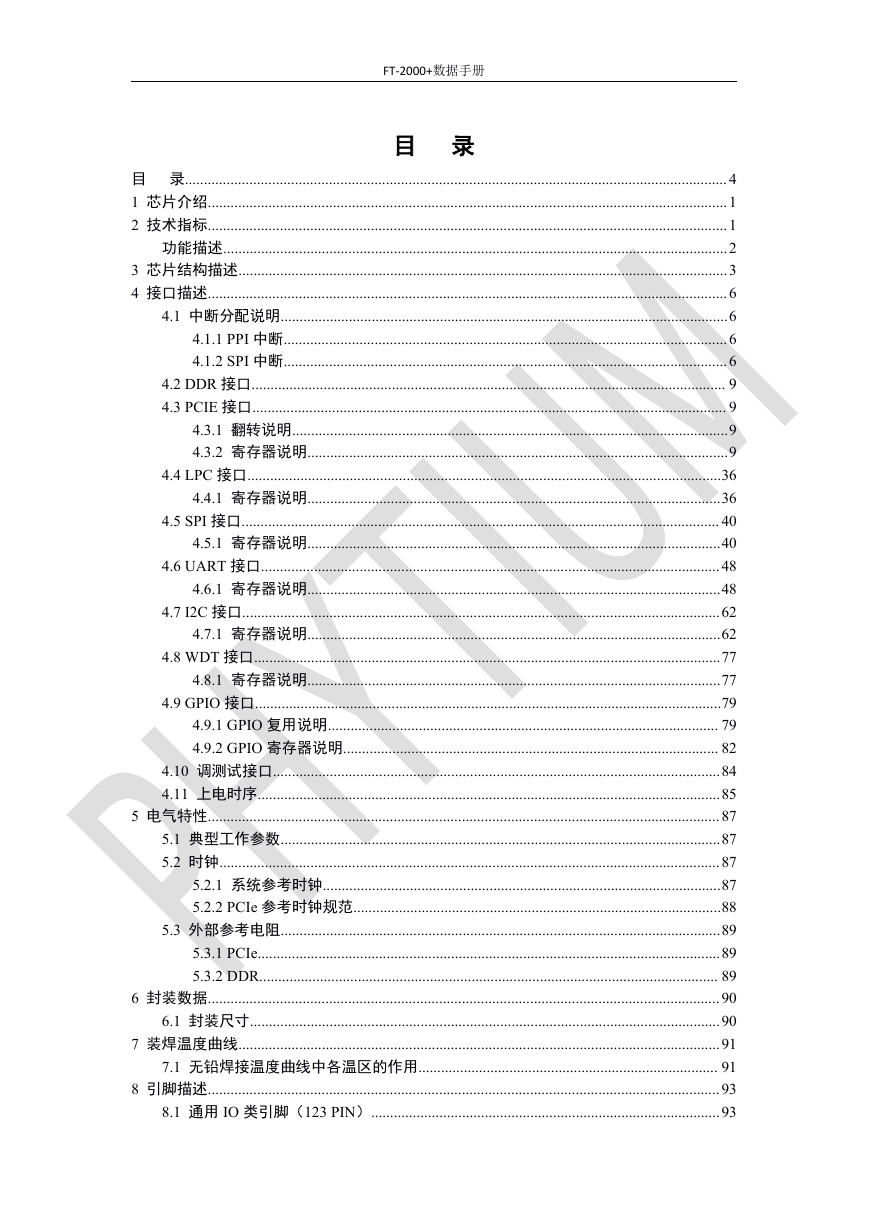

1芯片介绍

2技术指标

1.用户拿到的芯片所能达到的具体速率需要与技术支持确认。

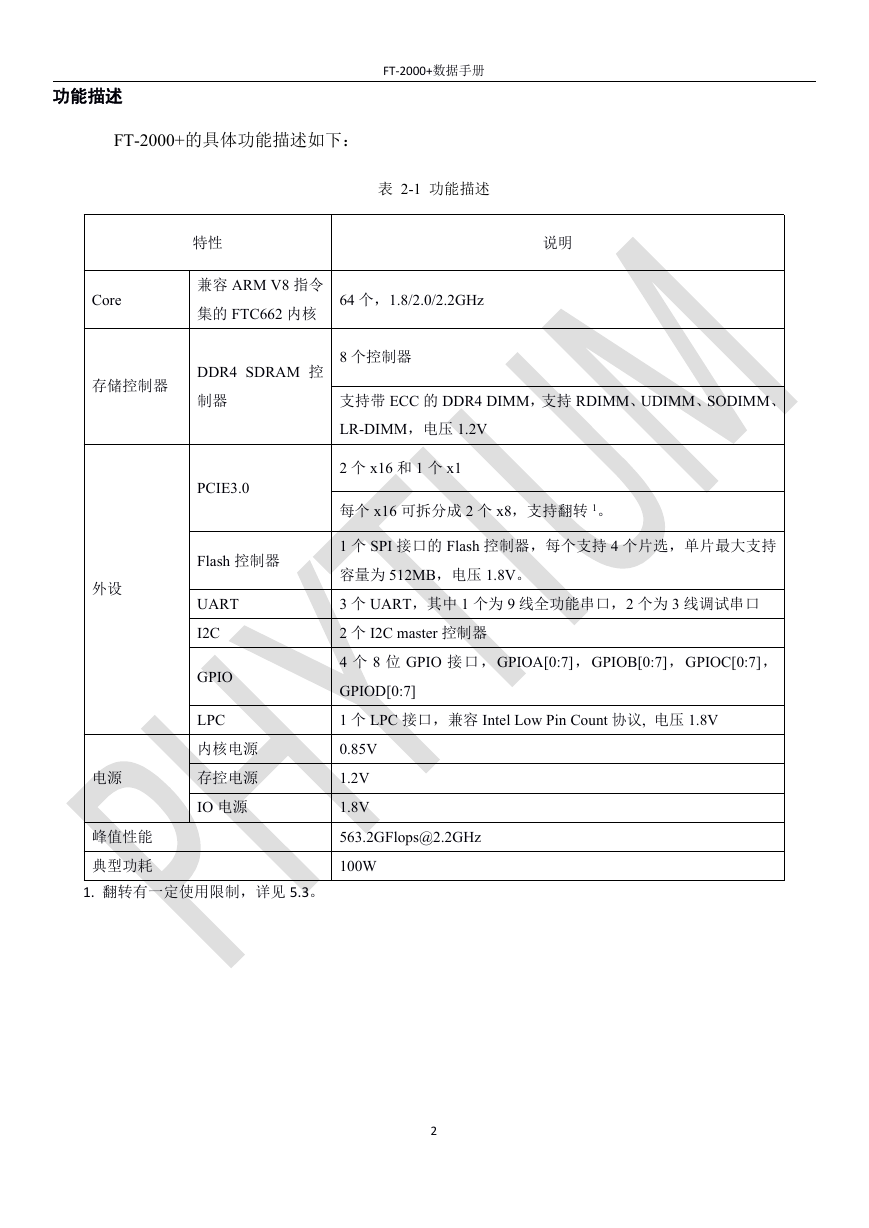

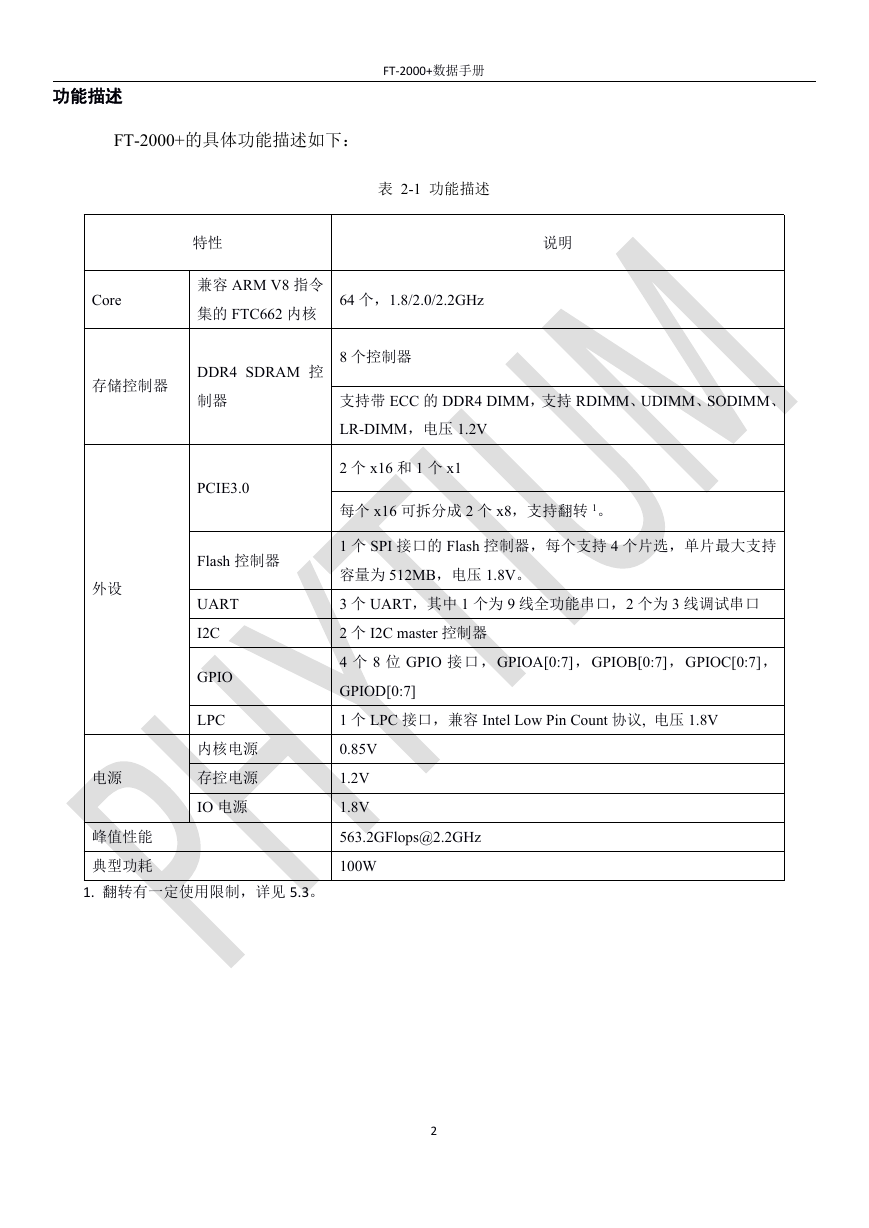

功能描述

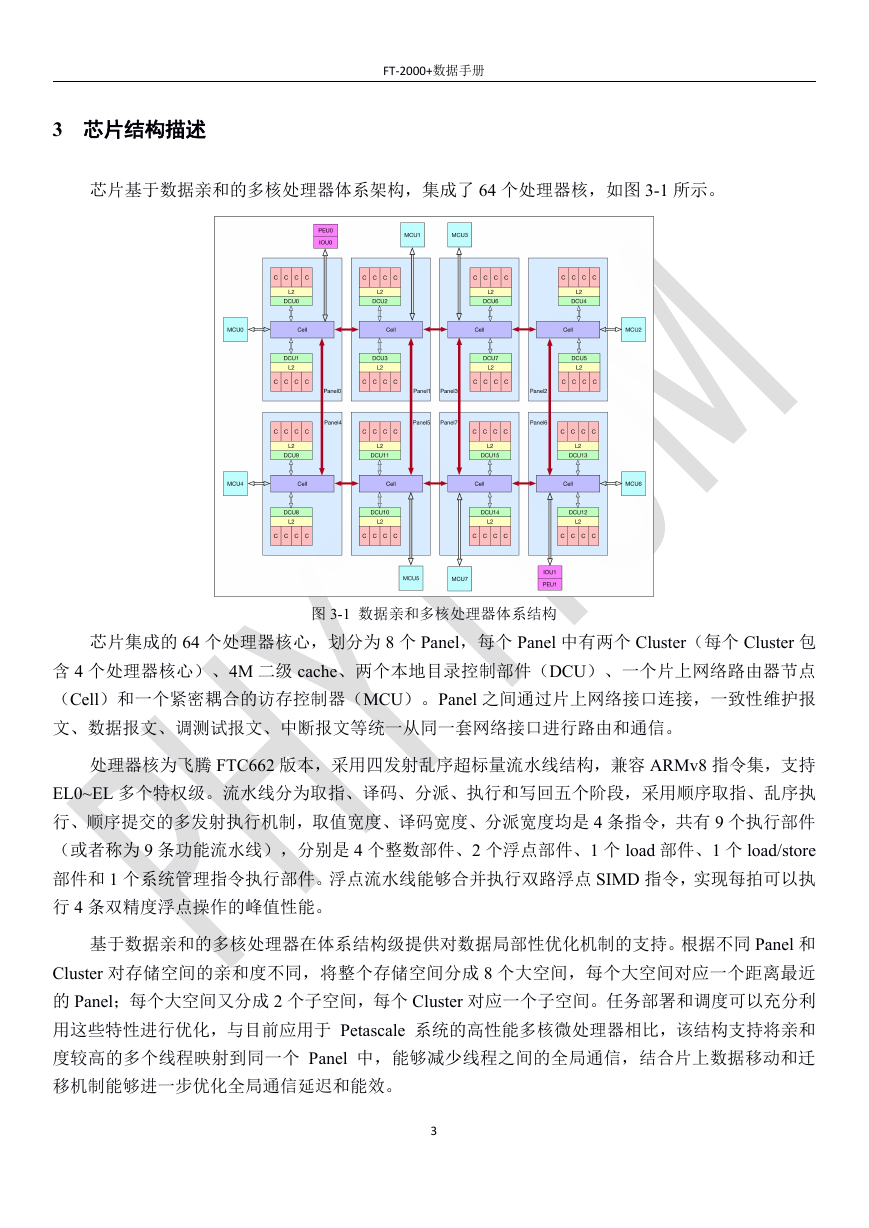

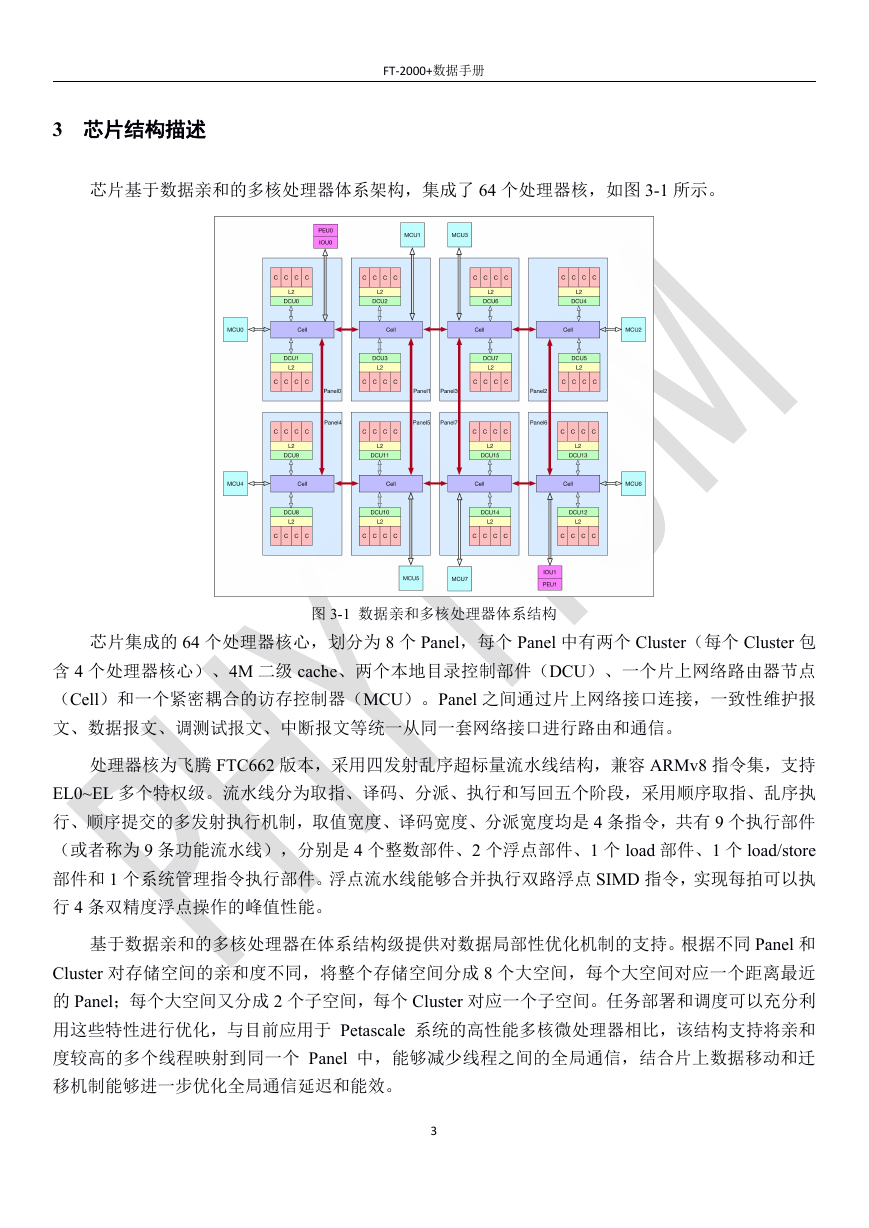

3芯片结构描述

4接口描述

4.1中断分配说明

4.1.1PPI中断

4.1.2SPI中断

4.2DDR接口

4.3PCIE接口

4.3.1翻转说明

4.3.2寄存器说明

4.3.2.1寄存器列表

4.3.2.1.1HPB寄存器

4.3.2.1.2INTX中断状态寄存器(0x000)

4.3.2.1.3INTX中断使能寄存器(0x004)

4.3.2.1.4杂散中断状态寄存器 (0x008)

4.3.2.1.5杂散中断使能寄存器 (0x00c)

4.3.2.1.6消息中断使能寄存器(0x010)

4.3.2.1.7消息队列状态寄存器(0x014)

4.3.2.1.8C0消息头队列寄存器

4.3.2.1.9C1消息头队列寄存器

4.3.2.1.10C2消息头队列寄存器

4.3.2.1.11C0消息数据队列寄存器

4.3.2.1.12C1消息数据队列寄存器

4.3.2.1.13C2消息数据队列寄存器

4.3.2.1.14控制器错误状态寄存器(0x0C0)

4.3.2.1.15控制器错误记录使能寄存器(0x0C4)

4.3.2.1.16控制器错误中断使能寄存器(0x0C8)

4.3.2.1.17控制器错误写1置寄存器(0x0CC)

4.3.2.1.18控制器错误写1清寄存器(0x0D0)

4.3.2.1.19控制器MSI使能寄存器(0x200)

4.3.2.1.20控制器MSI64高位地址寄存器(0x208)

4.3.2.1.21控制器MSI64低位地址寄存器(0x20C)

4.3.2.1.22BIOS SRAM校验使能寄存器(0x600)

4.3.2.1.23MMU CACHE DOMAIN设置寄存器0(0x620)

4.3.2.1.24MMU CACHE DOMAIN设置寄存器1(0x624)

4.3.2.1.25MMU REGION BAR设置寄存器0(0x628)

4.3.2.1.26MMU REGION BAR设置寄存器1(0x62c)

4.3.2.1.27MMU SNOOP设置寄存器0(0x630)

4.3.2.1.28MMU SNOOP设置寄存器1(0x634)

4.3.2.1.29VGA使能寄存器 (0x700)

4.3.2.1.30PIO超时使能寄存器 (0x708)

4.3.2.1.31PIO写超时地址寄存器0 (0x710)

4.3.2.1.32PIO写超时地址寄存器1 (0x714)

4.3.2.1.33PIO读超时地址寄存器0 (0x718)

4.3.2.1.34PIO读超时地址寄存器1 (0x71c)

4.3.2.1.35PEU分拆模式寄存器(0x800)

4.3.2.1.36PEU设备类型寄存器(0x804)

4.3.2.1.37PEU链路训练使能寄存器(0x80C)

4.3.2.1.38PEU GEN3预设值寄存器0(0x814)

4.3.2.1.39PEU GEN3预设值寄存器1(0x818)

4.3.2.1.40PEU C0杂项设置寄存器(0x81C)

4.3.2.1.41PEU C1杂项设置寄存器(0x820)

4.3.2.1.42PEU C2杂项设置寄存器(0x824)

4.3.2.1.43PEU观察时钟选择寄存器(0x82C)

4.3.2.1.44PEU控制器热复位寄存器(0x830)

4.3.2.1.45PEU控制器sticky复位寄存器(0x834)

4.3.2.1.46PEU控制器链路数目设置寄存器(0x838)

4.3.2.1.47PEU链路状态寄存器(0x83c)

4.3.2.1.48PHY PIPE复位撤销寄存器(0xa00)

4.3.2.1.49控制器复位撤销寄存器(0xa04)

4.3.2.1.50控制器和PIPE时钟状态寄存器(0xa08)

4.3.2.1.51控制器错误注入寄存器(0xa0c)

4.3.2.1.52FLR状态寄存器(0xa10)

4.3.2.1.53FLR完成置位寄存器(0xa14)

4.3.2.1.54总线模式寄存器(0xa20)

4.3.2.1.55控制器C0起始总线号(0xa24)

4.3.2.1.56控制器C1起始总线号(0xa28)

4.3.2.1.57控制器C2起始总线号(0xa2c)

4.3.2.1.58EP模式C0_PREF_BASE_LIMIT寄存器 (0xa30)

4.3.2.1.59EP模式C0_PREF_BASE_LIMIT_UP32寄存器 (0xa34)

4.3.2.1.60EP模式C0_MEM_BASE_LIMIT寄存器 (0xa38)

4.3.2.1.61EP模式C1_PREF_BASE_LIMIT寄存器 (0xa40)

4.3.2.1.62EP模式C1_PREF_BASE_LIMIT_UP32寄存器 (0xa44)

4.3.2.1.63EP模式C1_MEM_BASE_LIMIT寄存器 (0xa48)

4.3.2.1.64EP模式C2_PREF_BASE_LIMIT寄存器 (0xa50)

4.3.2.1.65EP模式C2_PREF_BASE_LIMIT_UP32寄存器 (0xa54)

4.3.2.1.66EP模式C2_MEM_BASE_LIMIT寄存器 (0xa58)

4.3.2.1.67读响应模式寄存器 (0xb00)

4.3.2.1.68控制器寄存器

4.4LPC接口

4.4.1寄存器说明

4.4.1.1基地址

4.4.1.2寄存器列表

4.4.1.2.1int_apb_spce_conf寄存器(0x7FF_FFFC)

4.4.1.2.2reg_long_timeout寄存器(0x7FF_FFF8)

4.4.1.2.3int_state寄存器(0x7FF_FFF4)

4.4.1.2.4clr_int寄存器(0x7FF_FFF0)

4.4.1.2.5nu_serirq_config寄存器(0x7FF_FFE8)

4.4.1.2.6err_stt寄存器(0x7FF_FFE4)

4.4.1.2.7Firmwr_id_conf_strtb寄存器(0x7FF_FFE0)

4.4.1.2.8Dma_chnnlnu_conf寄存器(0x7FF_FFDC)

4.4.1.2.9int_mask寄存器(0x7FF_FFD8)

4.4.1.2.10start_cycle寄存器(0x7FF_FFD4)

4.4.1.2.11mem_highbit_addr寄存器(0x7FF_FFD0)

4.5SPI接口

4.5.1寄存器说明

4.5.1.1基地址

4.5.1.2寄存器列表

4.5.1.2.1SPI配置寄存器(0x1fff_ff00)

4.5.1.2.2错误使能寄存器(0x1fff_ff04)

4.5.1.2.3错误记录寄存器(0x1fff_ff08)

4.5.1.2.4WP寄存器(0x1fff_ff0c)

4.5.1.2.5CS延迟寄存器(0x1fff_ff10)

4.5.1.2.6Flash容量设置寄存器(0x1fff_ff14)

4.5.1.2.7写缓冲flush寄存器(0x1fff_ff18)

4.5.1.2.8安全访问控制寄存器(0x1fff_ff1c)

4.5.1.2.9命令端口寄存器(0x1fff_ff20)

4.5.1.2.10地址端口寄存器(0x1fff_ff24)

4.5.1.2.11高位数据寄存器(0x1fff_ff28)

4.5.1.2.12低位数据寄存器(0x1fff_ff2c)

4.5.1.2.13CS0起始地址配置寄存器(0x1fff_ff30)

4.5.1.2.14CS1起始地址配置寄存器(0x1fff_ff34)

4.5.1.2.15CS2起始地址配置寄存器(0x1fff_ff38)

4.5.1.2.16CS3起始地址配置寄存器(0x1fff_ff3c)

4.5.1.2.17时钟控制设置寄存器(0x1fff_ff40)

4.5.1.2.18时钟控制清除寄存器(0x1fff_ff44)

4.5.1.2.19容量寄存器(0x14)

4.5.1.2.20写缓冲寄存器(0x18)

4.5.1.2.21命令端口寄存器(0x20)

4.5.1.2.22地址端口寄存器(0x24)

4.5.1.2.23高位寄存器(0x28)

4.5.1.2.24低位寄存器(0x2C)

4.6UART接口

4.6.1寄存器说明

4.6.1.1基地址

4.6.1.2寄存器列表

4.6.1.2.1RBR(0x00)

4.6.1.2.2THR(0x00)

4.6.1.2.3DLH(0x04)

4.6.1.2.4DLL(0x00)

4.6.1.2.5IER(0x04)

4.6.1.2.6IIR(0x08)

4.6.1.2.7LCR(0x0C)

4.6.1.2.8LSR(0X14)

4.6.1.2.9USR(0x7C)

4.7I2C接口

4.7.1寄存器说明

4.7.1.1基地址

4.7.1.2寄存器列表

4.7.1.2.1IC_CON(0x00)

4.7.1.2.2IC_TAR(0x04)

4.7.1.2.3IC_SAR(0x08)

4.7.1.2.4IC_DATA_CMD(0x10)

4.7.1.2.5IC_SS_SCL_HCNT(0x14)

4.7.1.2.6IC_SS_SCL_LCNT(0x18)

4.7.1.2.7IC_FS_SCL_HCNT(0x1C)

4.7.1.2.8IC_FS_SCL_LCNT(0x20)

4.7.1.2.9IC_HS_SCL_HCNT(0x24)

4.7.1.2.10IC_HS_SCL_LCNT(0x28)

4.7.1.2.11IC_INTR_MASK(0x30)

4.7.1.2.12IC_RAW_INTR_STAT(0x34)

4.7.1.2.13IC_RX_TL(0x38)

4.7.1.2.14IC_TX_TL(0x3C)

4.7.1.2.15IC_ENABLE(0x6C)

4.7.1.2.16IC_STATUS(0x70)

4.8WDT接口

4.8.1寄存器说明

4.8.1.1基地址

4.8.1.2寄存器列表

4.8.1.2.1WDT_CR(0x00)

4.8.1.2.2WDT_TORR(0x04)

4.8.1.2.3WDT_CCVR(0x08)

4.8.1.2.4WDT_CRR(0x0c)

4.8.1.2.5WDT_STAT(0x10)

4.8.1.2.6WDT_EOI(0x14)

4.9GPIO接口

4.9.1GPIO复用说明

4.9.1.1GPIO复用寄存器地址

4.9.1.2GPIO复用寄存器描述

OLE_LINK4

OLE_LINK7

4.9.2GPIO寄存器说明

4.9.2.1.1基地址

4.9.2.1.2寄存器列表

4.9.2.1.2.1数据寄存器 GPIOX_DR

4.9.2.1.2.2方向寄存器GPIOX_DDR

4.9.2.1.2.3外部数据寄存器GPIO_EXT_PORTX

4.10调测试接口

4.11上电时序

5电气特性

5.1典型工作参数

5.2时钟

5.2.1系统参考时钟

5.2.2PCIe参考时钟规范

5.3外部参考电阻

5.3.1PCIe

5.3.2DDR

6封装数据

6.1封装尺寸

7装焊温度曲线

7.1无铅焊接温度曲线中各温区的作用

OLE_LINK5

OLE_LINK2

8引脚描述

8.1通用IO类引脚(123 PIN)

8.2PCIE引脚(149 PIN)

OLE_LINK1

8.3DDR4引脚(1280 PIN)

8.4电源引脚(2024 PIN)

OLE_LINK6

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc