Vivado Design Suite Tutorial: High-Level Synthesis

Revision History

Tutorial Description

Overview

High-Level Synthesis Introduction

C Validation

Interface Synthesis

Arbitrary Precision Types

Design Analysis

Design Optimization

RTL Verification

Using HLS IP in IP Integrator

Using HLS IP in a Zynq Processor Design

Using HLS IP in System Generator for DSP

Software Requirements

Hardware Requirements

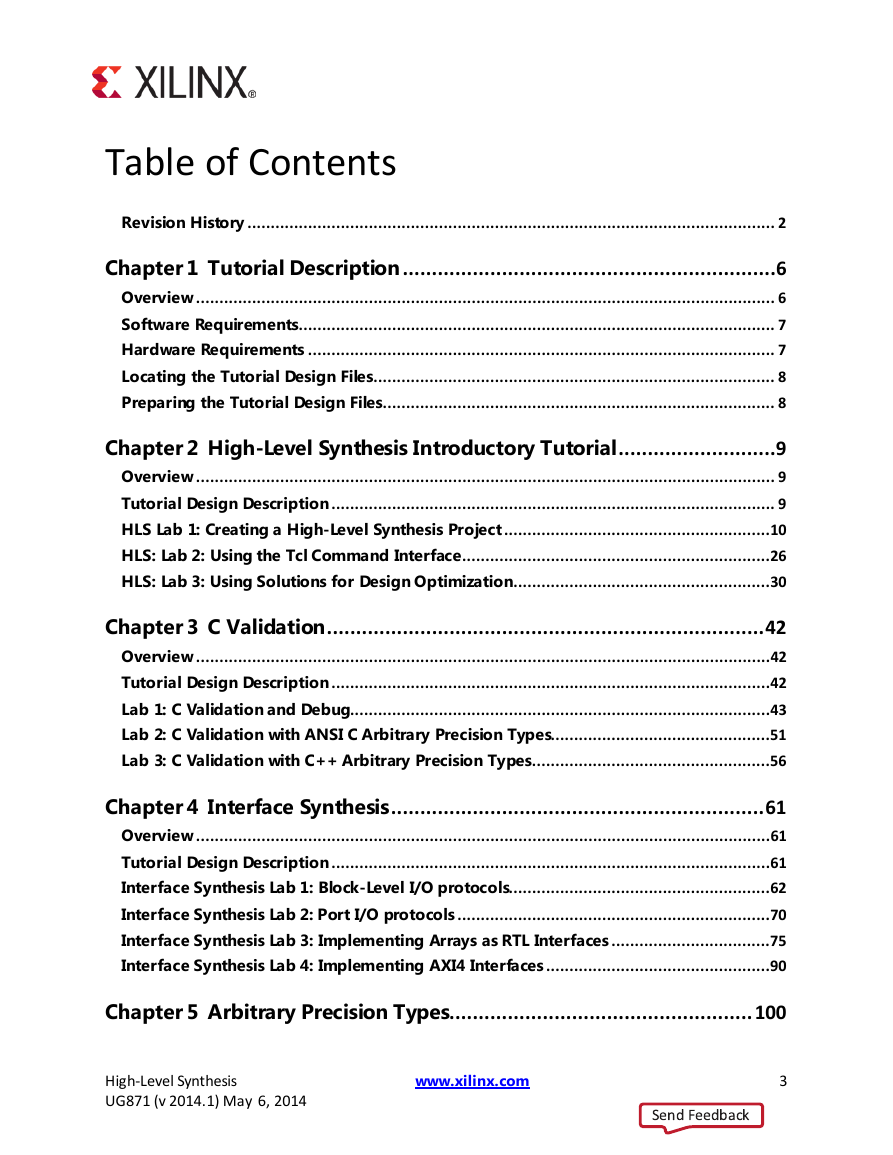

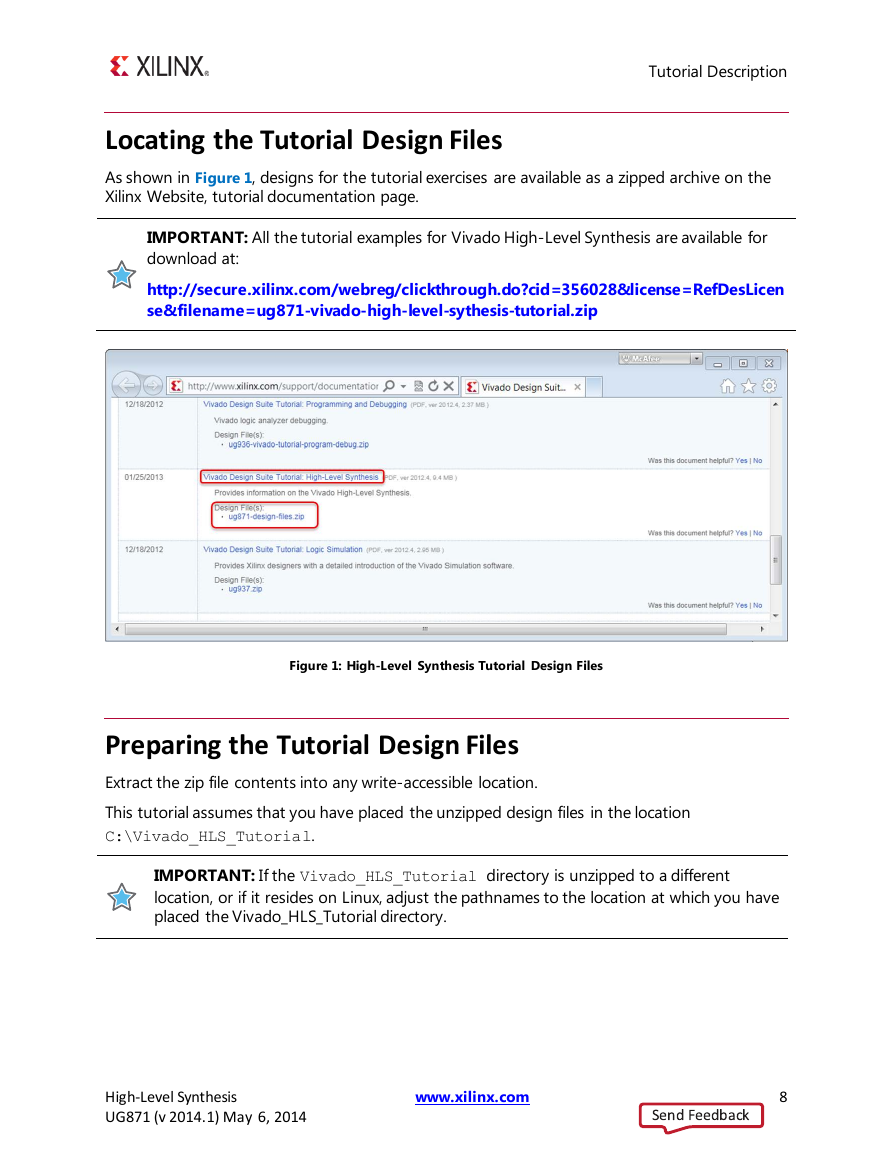

Locating the Tutorial Design Files

Preparing the Tutorial Design Files

High-Level Synthesis Introductory Tutorial

Overview

Lab 1

Lab 2

Lab 3

Tutorial Design Description

HLS Lab 1: Creating a High-Level Synthesis Project

Introduction

Step 1: Creating a New Project

Understanding the Graphical User Interface (GUI)

Explorer Pane

Information Pane

Auxiliary Pane

Console Pane

Toolbar Buttons

Perspectives

Step 2: Validate the C Source Code

Step 3: High-Level Synthesis

Step 4: RTL Verification

Step 5: IP Creation

HLS: Lab 2: Using the Tcl Command Interface

Introduction

Step 1: Create a Tcl file

HLS: Lab 3: Using Solutions for Design Optimization

Introduction

Step 1: Creating a New Project

Step 2: Optimize the I/O Interfaces

Step 3: Analyze the Results

Step 4: Optimize for the Highest Throughput (lowest interval)

Conclusion

C Validation

Overview

Tutorial Design Description

Lab 1: C Validation and Debug

Overview

Step 1: Create and Open the Project

Step 2: Review Test Bench and Run C Simulation

Step 3: Run the C Debugger

Lab 2: C Validation with ANSI C Arbitrary Precision Types

Introduction

Step 1: Create and Open the Project

Step 2: Run the C Debugger

Lab 3: C Validation with C++ Arbitrary Precision Types

Overview

Step 1: Create and Open the Project

Step 2: Run the C Debugger

Conclusion

Interface Synthesis

Overview

Tutorial Design Description

About the Labs

Interface Synthesis Lab 1: Block-Level I/O protocols

Overview

Step 1: Create and Open the Project

Step 2: Create and Review the Default Block-Level I/O Protocol

Step 3: Modify the Block-Level I/O protocol

Interface Synthesis Lab 2: Port I/O protocols

Overview

Step 1: Create and Open the Project

Step 2: Specify the I/O Protocol for Ports

Interface Synthesis Lab 3: Implementing Arrays as RTL Interfaces

Introduction

Step 1: Create and Open the Project

Step 2: Synthesize Array Function Arguments to RAM ports

Step 3: Using Dual-port RAM and FIFO interfaces

Step 4: Partitioned RAM and FIFO Array interfaces

Step 5: Fully Partitioned Array interfaces

Interface Synthesis Lab 4: Implementing AXI4 Interfaces

Introduction

Step 1: Create and Open the Project

Step 2: Create an Optimized Design with AXI4 Stream Interfaces

Step 3: Implementing an AXI4-Lite Interfaces

Conclusion

Arbitrary Precision Types

Overview

Tutorial Design Description

Arbitrary Precision: Lab 1

Step 1: Create and Open the Project

Step 2: Review Test Bench and Run C Simulation

Step 3: Synthesize the Design and Review Results

Arbitray Precision: Lab 2

Introduction

Step 1: Create and Simulate the Project

Step 2: Synthesize the Design and Review Results

Conclusion

Design Analysis

Overview

Lab1

Tutorial Design Description

Lab 1: Design Optimization

Step 1: Create and Open the Project

Step 2: Review the source Code and Create the Initial Design

Step 3: Review the performance using the Synthesis Report

Step 4: Review the Performance using the Analysis Perspective

Step 5: Apply Loop Pipelining & Review for Loop Optimization

Step 6: Apply Loop Optimization and Review for Bottlenecks

Step 7: Partition Block RAMs and Analyze Concurrency

Step 8: Partition Block RAMs and Apply Dataflow optimization

Step 9: Optimize the Hierarchy for Dataflow

Conclusion

Design Optimization

Overview

Tutorial Design Description

Lab 1: Optimizing a Matrix Multiplier

Step 1: Create and Open the Project

Step 2: Synthesize and Analyze the Design

Step 3: Pipeline the Product Loop

Step 4: Pipeline the Col Loop

Step 5: Reshape the Arrays

Step 6: Apply FIFO Interfaces

Step 7: Pipeline the Function

Lab 2: C Code Optimized for I/O Accesses

Step 1: Create and Open the Project

Conclusion

RTL Verification

Overview

Lab1

Lab2

Lab3

Tutorial Design Description

Lab 1: RTL Verification and the C test bench

Step 1: Create and Open the Project

Step 2: Perform RTL Verification

Step 3: Modify the C test bench

Lab 2: Viewing Trace Files in Vivado

Step 1: Create an RTL Trace File using Xsim

Step 2: View the RTL Trace File in Vivado

Lab 3: Viewing Trace Files in ModelSim

Step 1: Create an RTL Trace File using ModelSim

Step 2: View the RTL Trace File in ModelSim

Conclusion

Using HLS IP in IP Integrator

Overview

Lab1

Tutorial Design Description

Lab 1: Integrate HLS IP with a Xilinx IP Block

Step 1: Create Vivado HLS IP Blocks

Step 2: Create a Vivado Design Suite Project

Step 3: Add HLS IP to an IP Repository

Step 4: Create a Block Design for RealFFT

Step 5: Verify the Design

Conclusion

Using HLS IP in a Zynq Processor Design

Overview

Lab1

Lab2

Tutorial Design Description

Lab 1: Implement Vivado HLS IP on a Zynq Device

Step 1: Create a Vivado HLS IP Block

Step 2: Create a Vivado Zynq Project

Step 3: Add HLS IP to the IP Catalog

Step 4: Creating an IP Integrator Block Design of the System

Step 5: Implementing the System

Step 6: Developing Software and Running it on the ZYNQ System

Step 7: Modify software to communicate with HLS block

Lab 2: Streaming data between the Zynq CPU and HLS Accelerator Blocks

Step 1: Generate the HLS IP

Step 2: Create a Vivado Design Suite Project

Step 3: Add HLS IP to an IP Repository

Step 4: Create a Top-level Block Design

Step 5: Implementing the System

Step 6: Setup SDK and test the ZYNQ System

Step 7: Modify software to communicate with HLS block

Using HLS IP in System Generator for DSP

Overview

Tutorial Design Description

Lab 1: Package HLS IP for System Generator

Step 1: Create a Vivado HLS IP Block

Step 2: Open the System Generator Project

Conclusion

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc