实验 1 Cache 模拟器的实现

一.实验目的

(1)加深对 Cache 的基本概念、基本组织结构以及基本工作原理的理解。

(2)掌握 Cache 容量、相联度、块大小对 Cache 性能的影响。

(3)掌握降低 Cache 不命中率的各种方法以及这些方法对提高 Cache 性能的好

处。

(4)理解 LRU 与随机法的基本思想以及它们对 Cache 性能的影响。

二、实验内容和步骤

1、启动 CacheSim。

2、根据课本上的相关知识,进一步熟悉 Cache 的概念和工作机制。

3、依次输入以下参数:Cache 容量、块容量、映射方式、替换策略和写策略。

Cache 容量

256KB

64KB

64KB

8KB

8 Byte

32 Byte

32 Byte

64 Byte

-------

-------

--------

---------

4 路组相联

4 路组相联

------

LRU

随机

LRU

直接映射

全相联

块容量

映射方式

替换策略

写策略

4、读取 cache-traces.zip 中的 trace 文件。

5、运行程序,观察 cache 的访问次数、读/写次数、平均命中率、读/写命中率。

思考:1、Cache 的命中率与其容量大小有何关系?

2、Cache 块大小对不命中率有何影响?

3、替换算法和相联度大小对不命中率有何影响?

三.实验结果分析

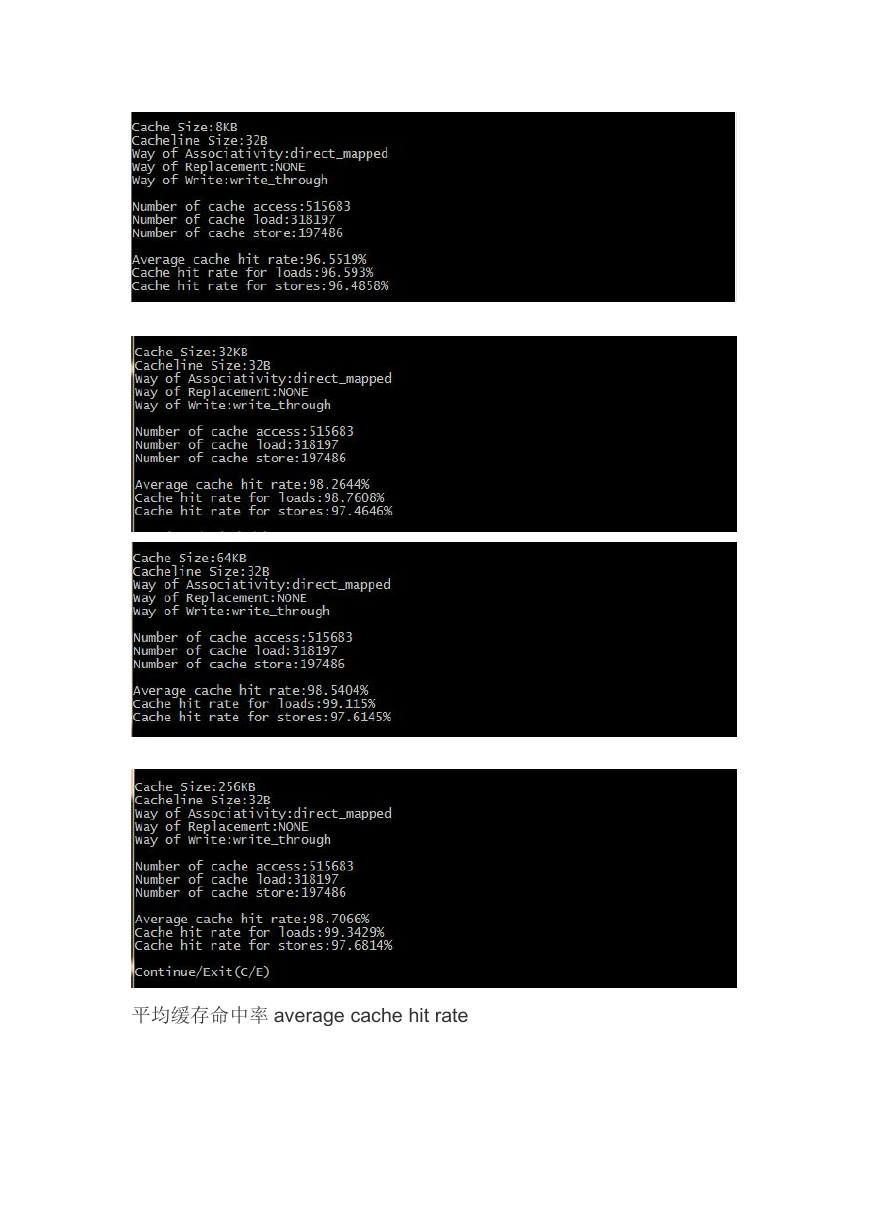

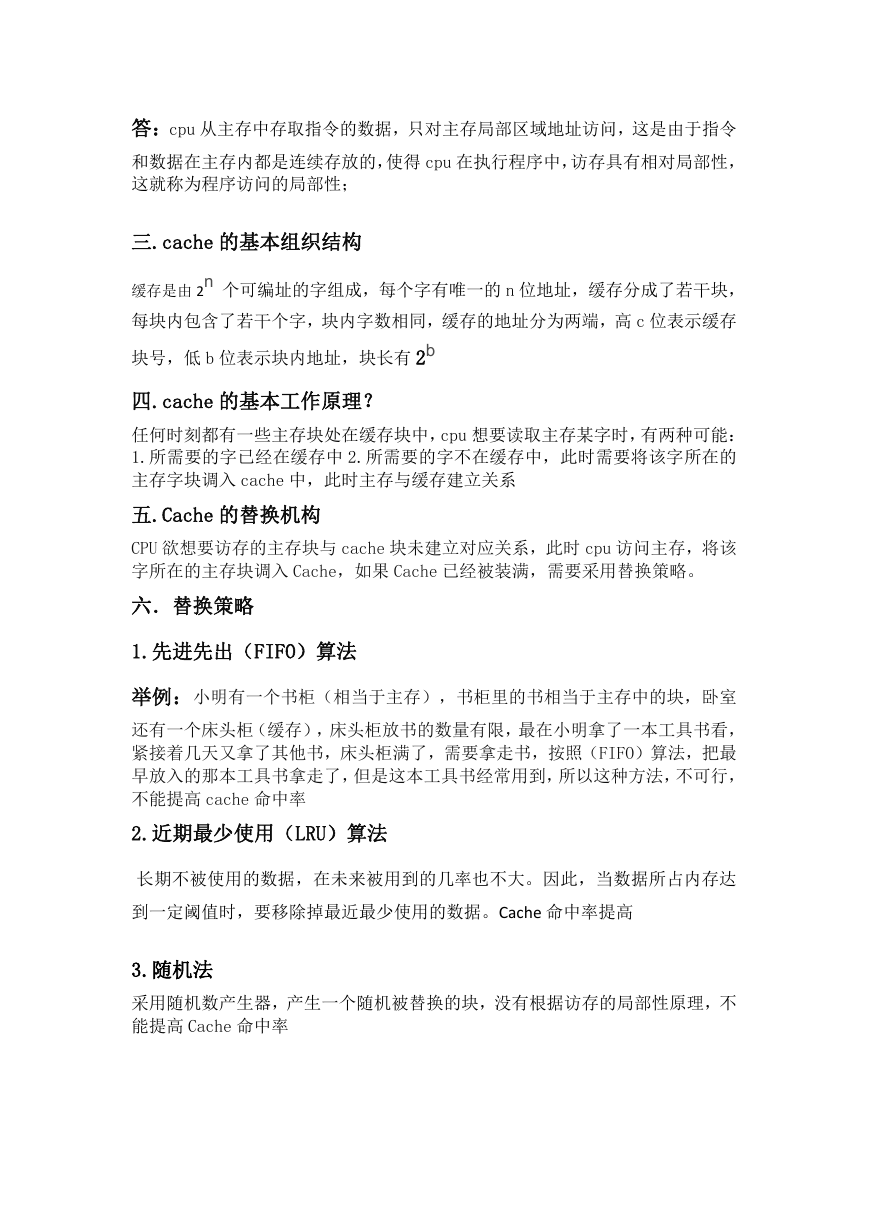

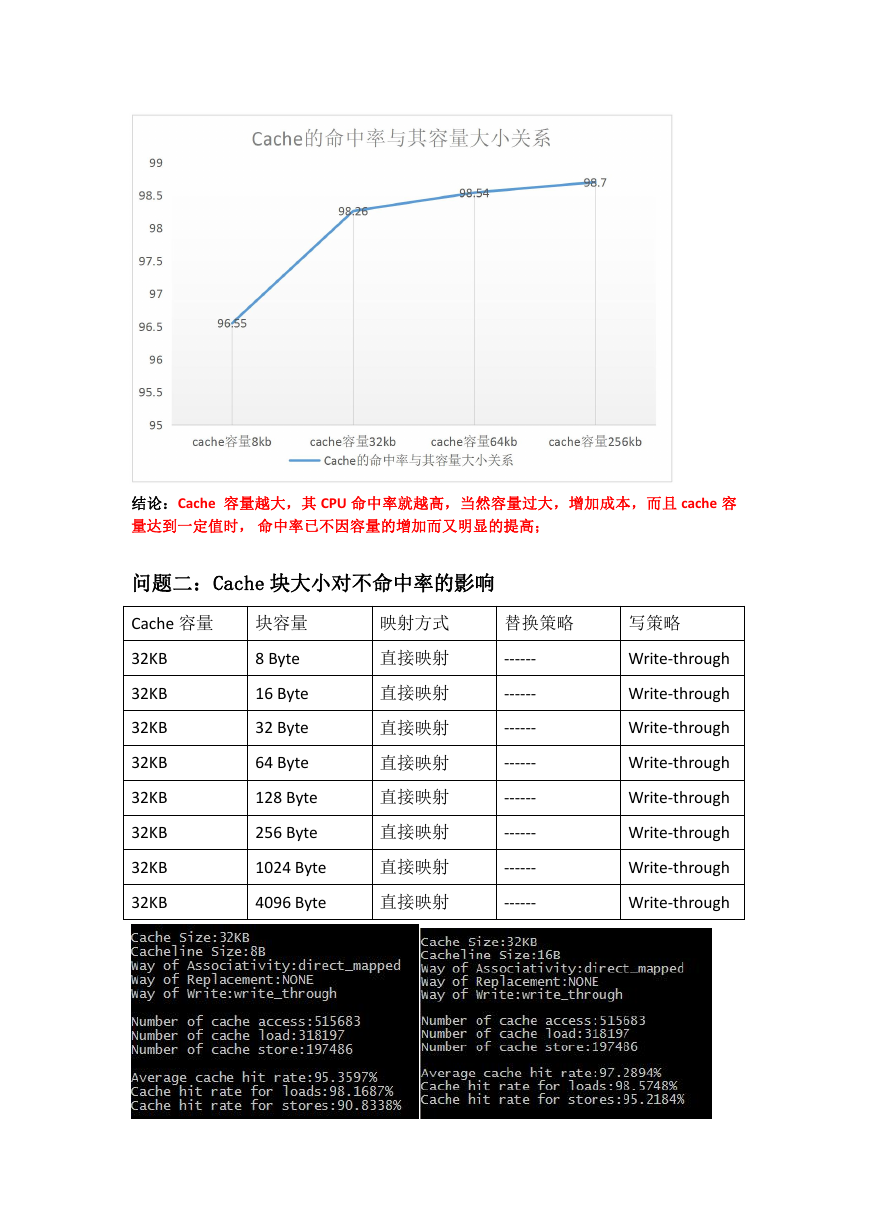

问题一:Cache 的命中率与其容量大小有何关系?

Cache 容量

256KB

64KB

32KB

8KB

块容量

32 Byte

32 Byte

32 Byte

32 Byte

映射方式

替换策略

写策略

直接映射

直接映射

直接映射

直接映射

------

------

------

------

Write-through

Write-through

Write-through

Write-through

�

平均缓存命中率 average cache hit rate

�

结论:Cache 容量越大,其 CPU 命中率就越高,当然容量过大,增加成本,而且 cache 容

量达到一定值时, 命中率已不因容量的增加而又明显的提高;

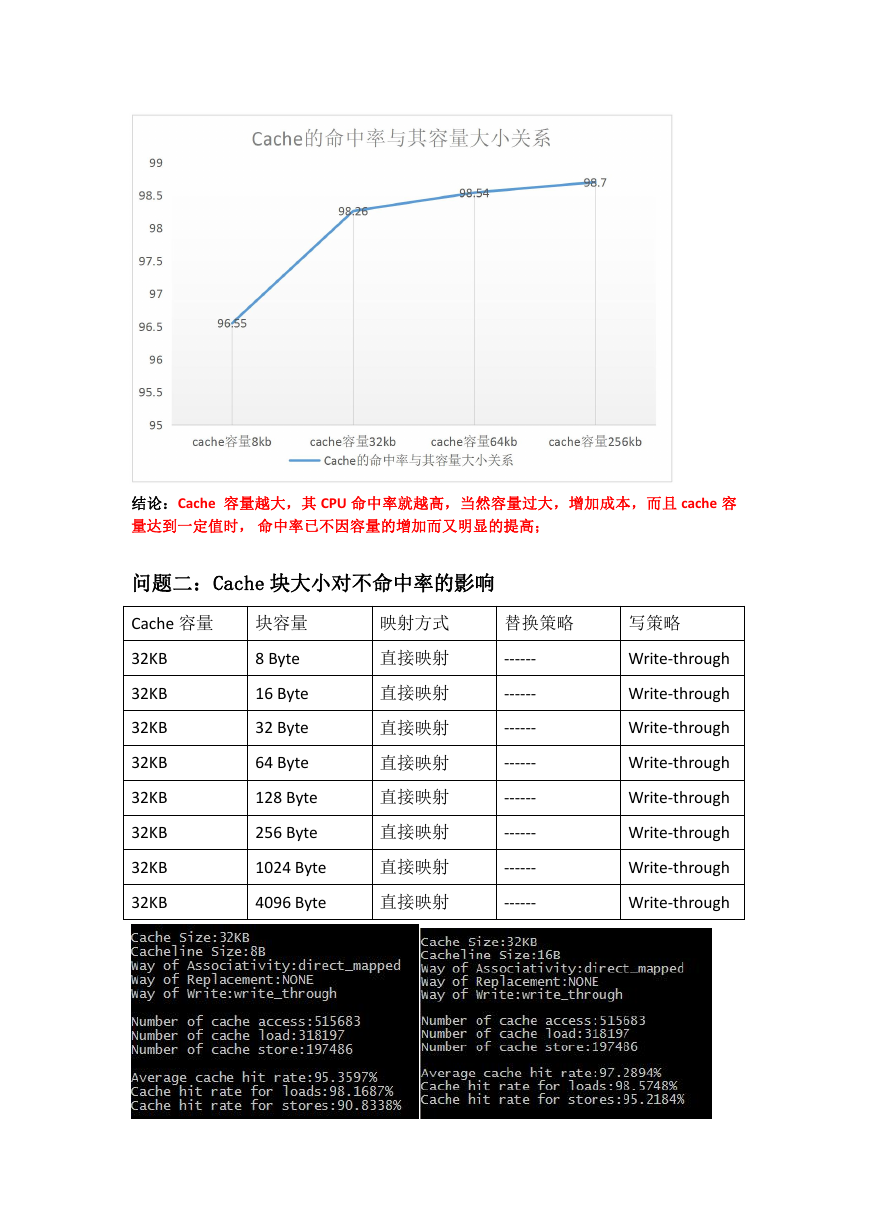

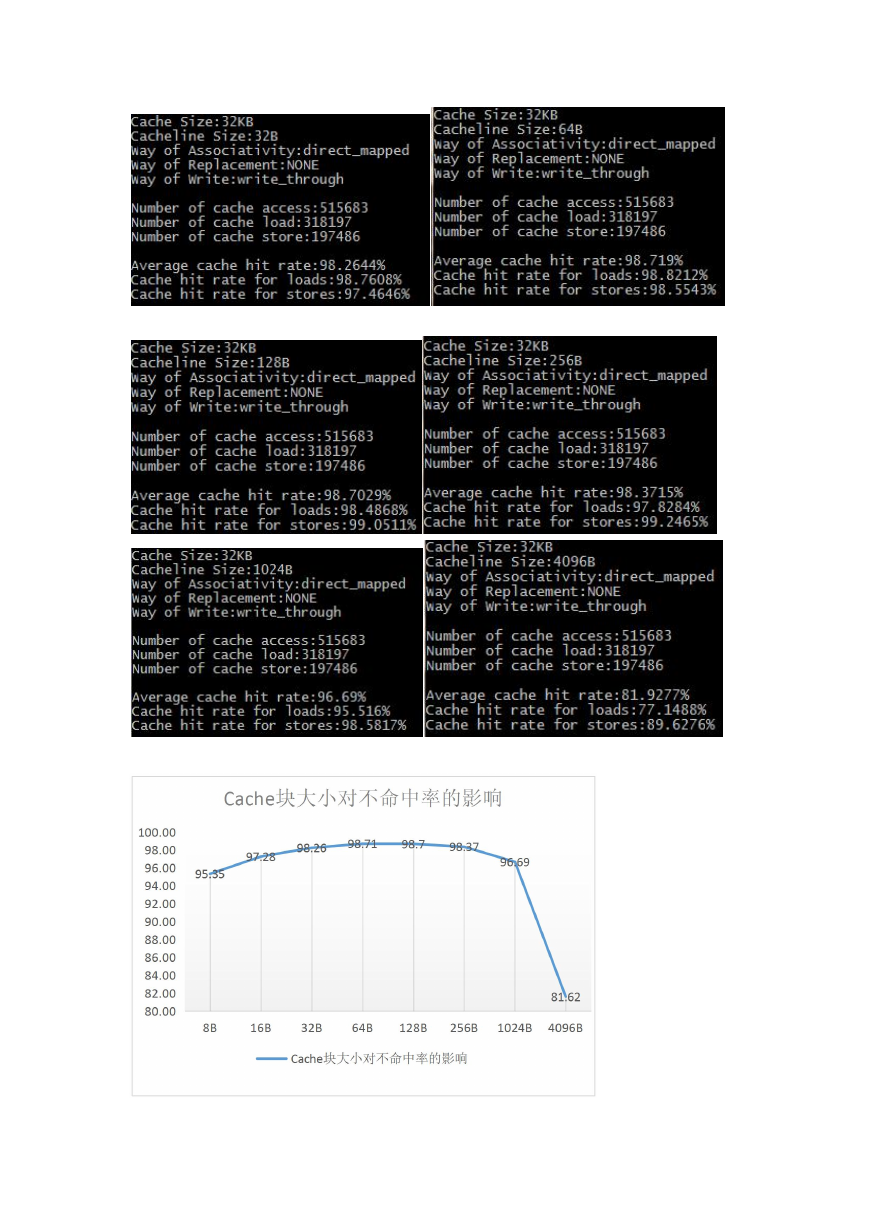

问题二:Cache 块大小对不命中率的影响

Cache 容量

32KB

32KB

32KB

32KB

32KB

32KB

32KB

32KB

块容量

映射方式

替换策略

写策略

8 Byte

16 Byte

32 Byte

64 Byte

128 Byte

256 Byte

1024 Byte

4096 Byte

直接映射

直接映射

直接映射

直接映射

直接映射

直接映射

直接映射

直接映射

------

------

------

------

------

------

------

------

Write-through

Write-through

Write-through

Write-through

Write-through

Write-through

Write-through

Write-through

�

�

结论:增大块长,由于局部性原理,起初命中率会提高,局部性原理指出,在被访问字的

附近,近期也可能被访问,因此,增大块长,最初可将更多有用字存入缓存,提高命中率;

但是继续增大块长,命中率可能下降,因为所装入缓存的有用数据反而少于被替换掉的有

用数据,由于块长增大,块数减少,装入新的块要覆盖旧块,很可能出现少数块刚装入就

被覆盖,故命中率可能下降;

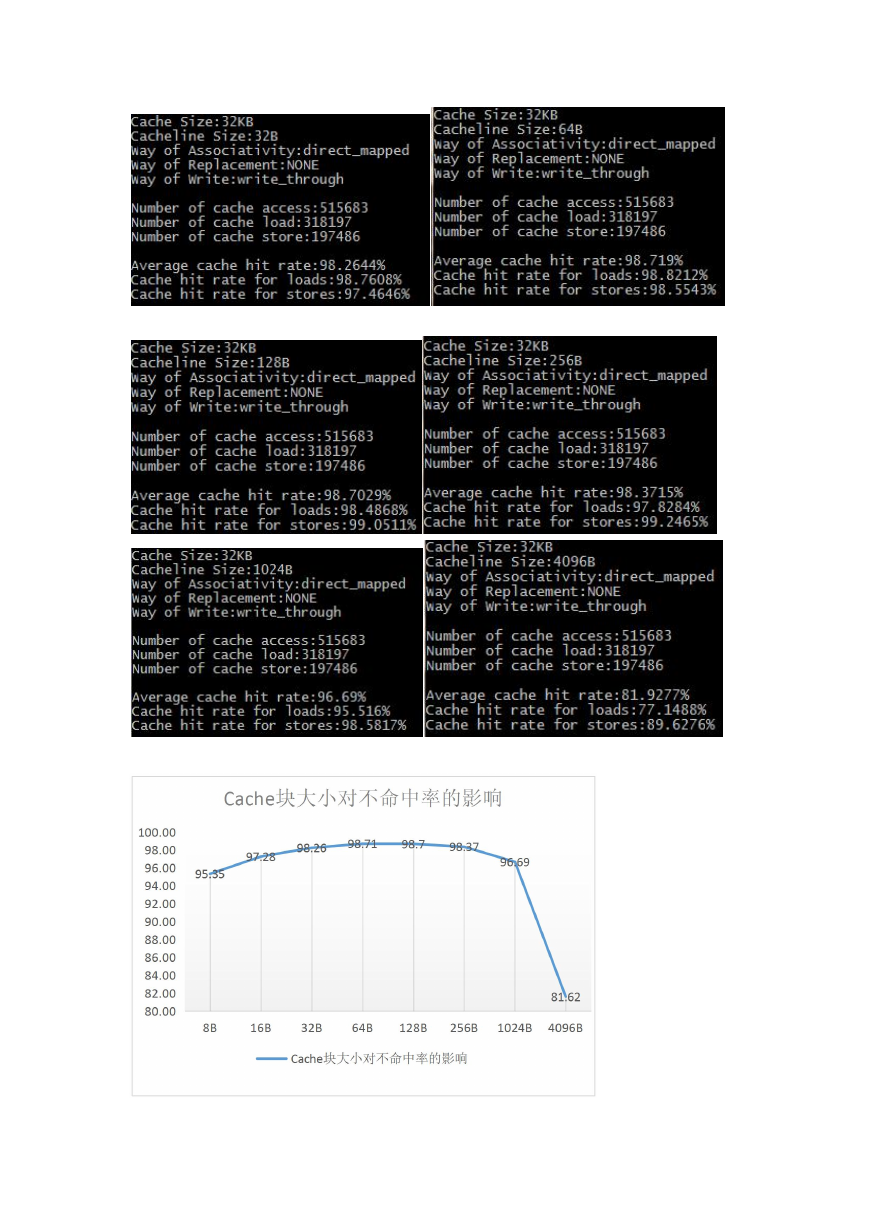

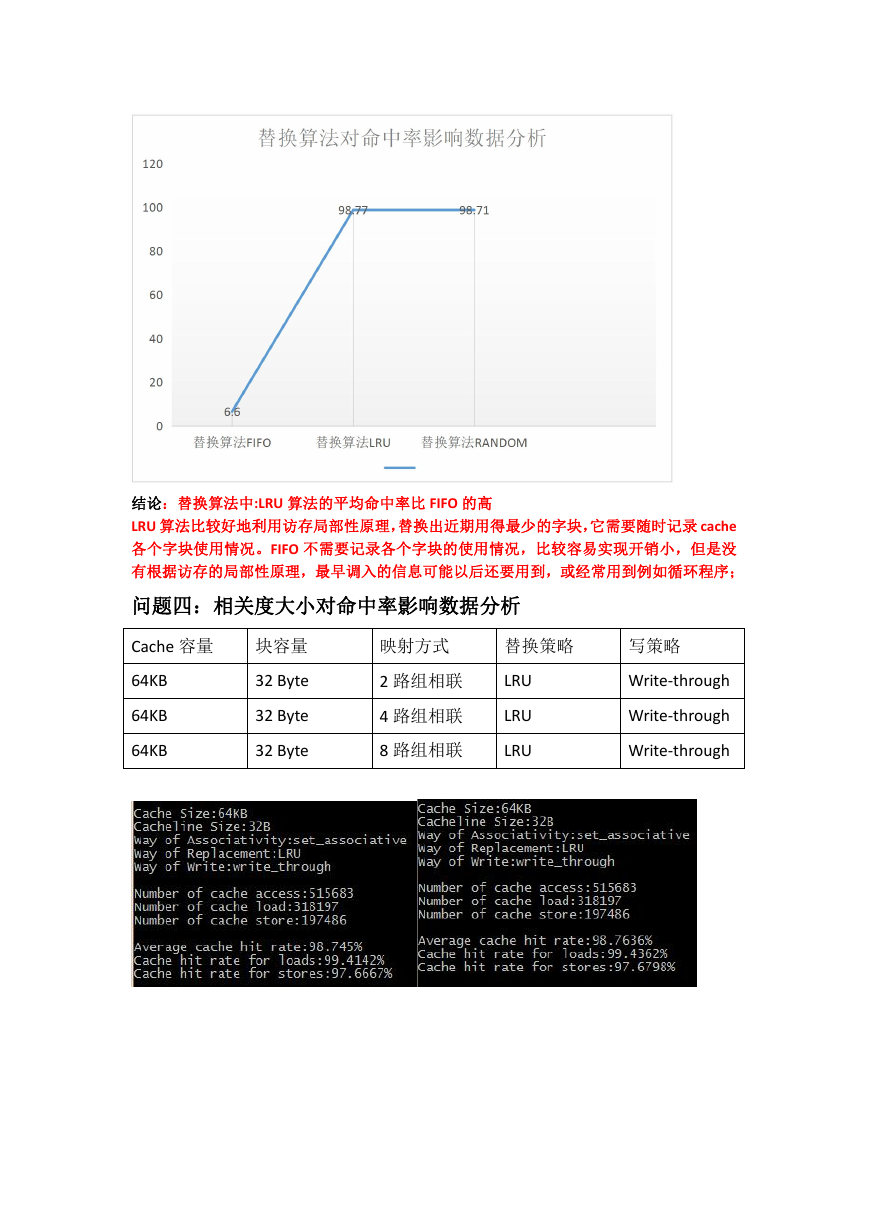

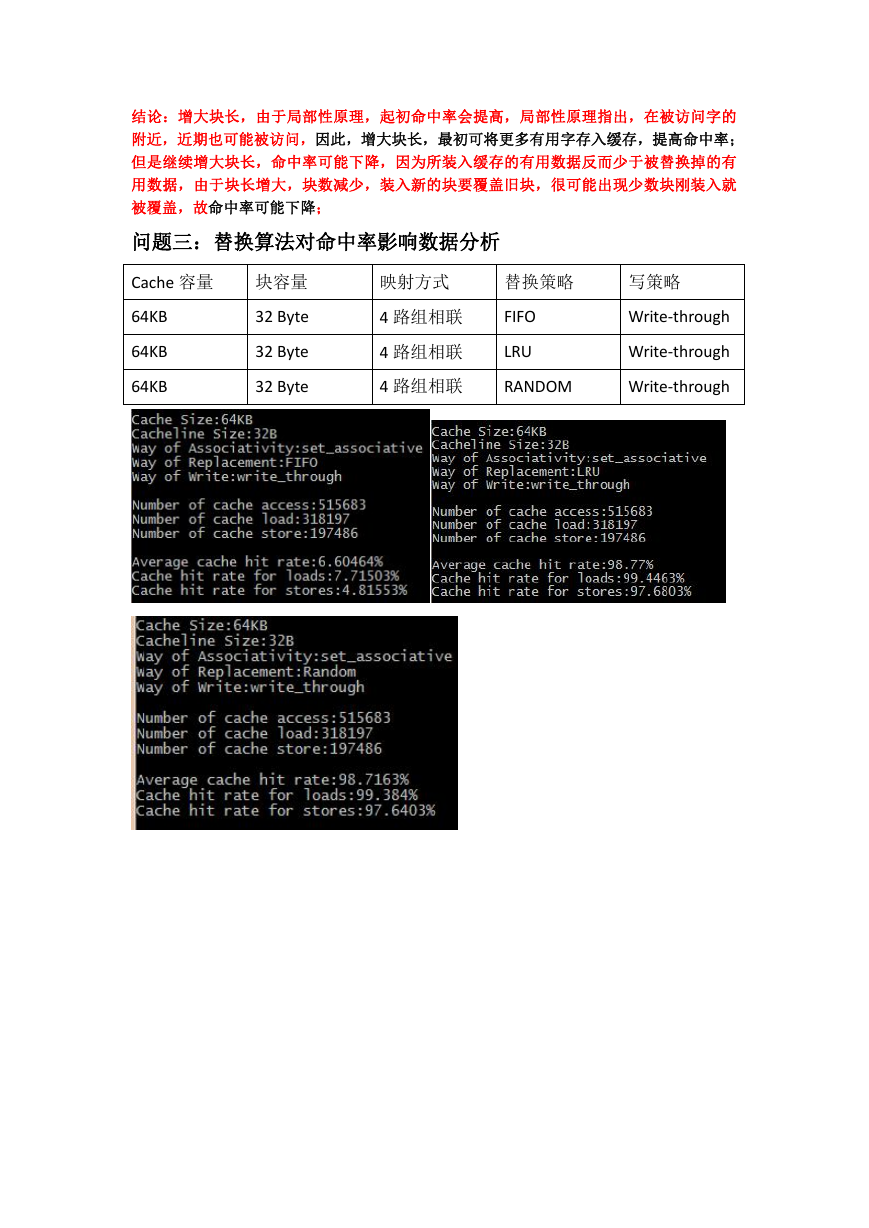

问题三:替换算法对命中率影响数据分析

Cache 容量

64KB

64KB

64KB

块容量

32 Byte

32 Byte

32 Byte

映射方式

替换策略

写策略

4 路组相联

4 路组相联

4 路组相联

FIFO

LRU

RANDOM

Write-through

Write-through

Write-through

�

结论:替换算法中:LRU 算法的平均命中率比 FIFO 的高

LRU 算法比较好地利用访存局部性原理,替换出近期用得最少的字块,它需要随时记录 cache

各个字块使用情况。FIFO 不需要记录各个字块的使用情况,比较容易实现开销小,但是没

有根据访存的局部性原理,最早调入的信息可能以后还要用到,或经常用到例如循环程序;

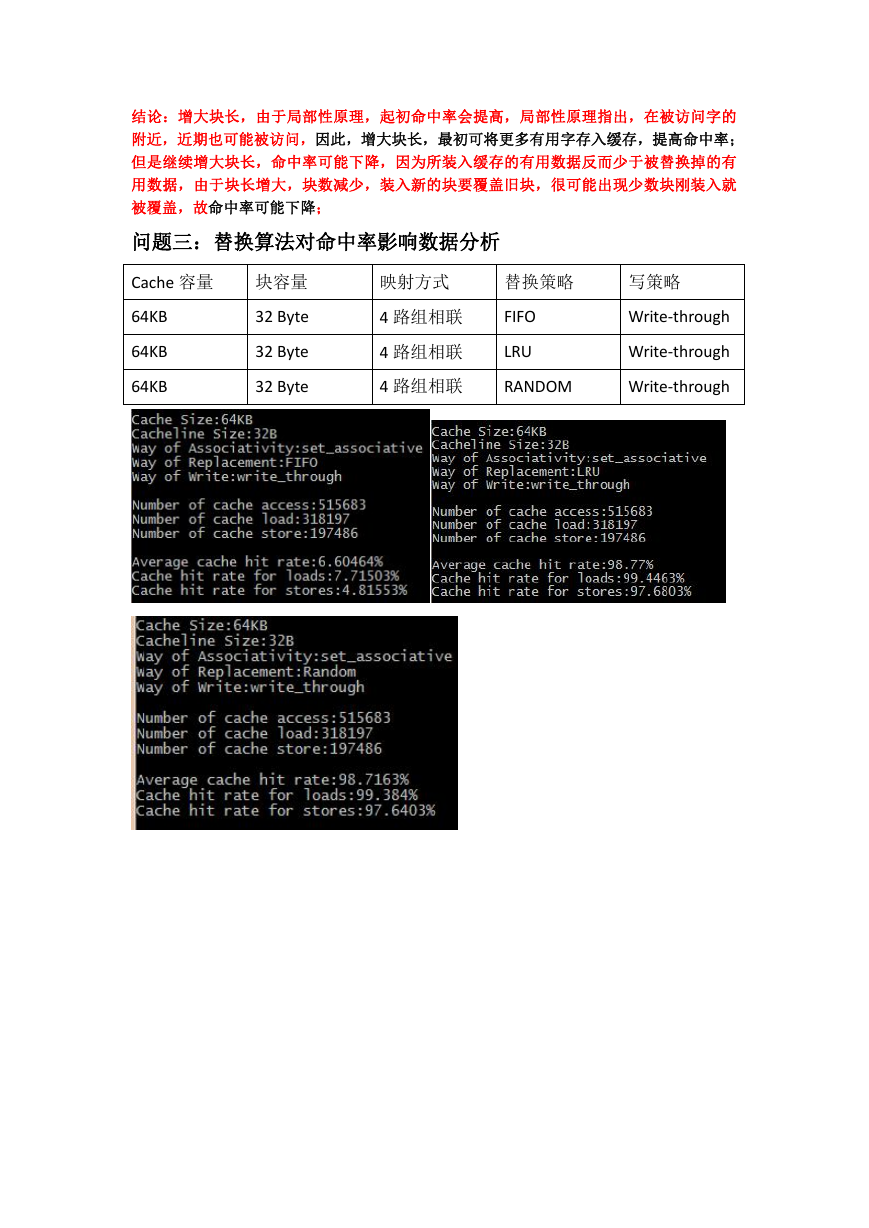

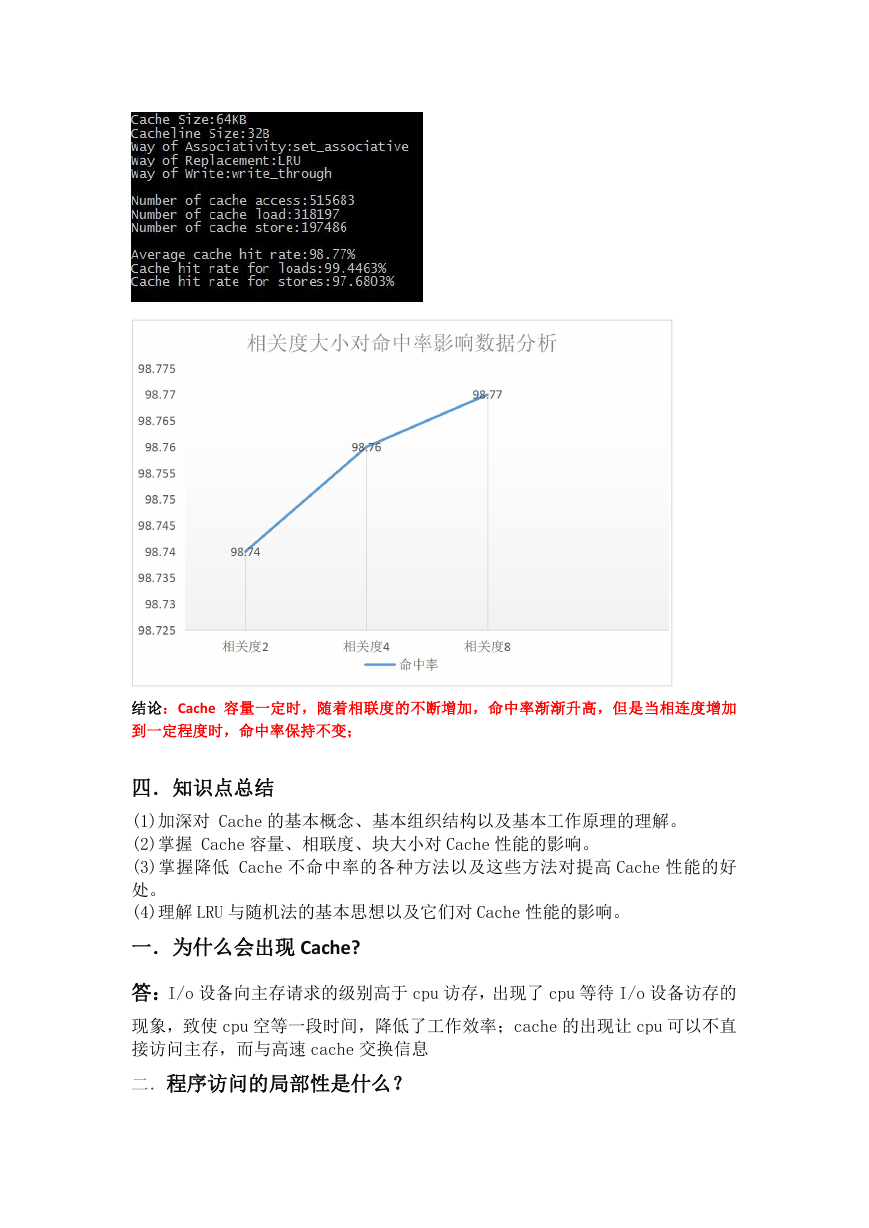

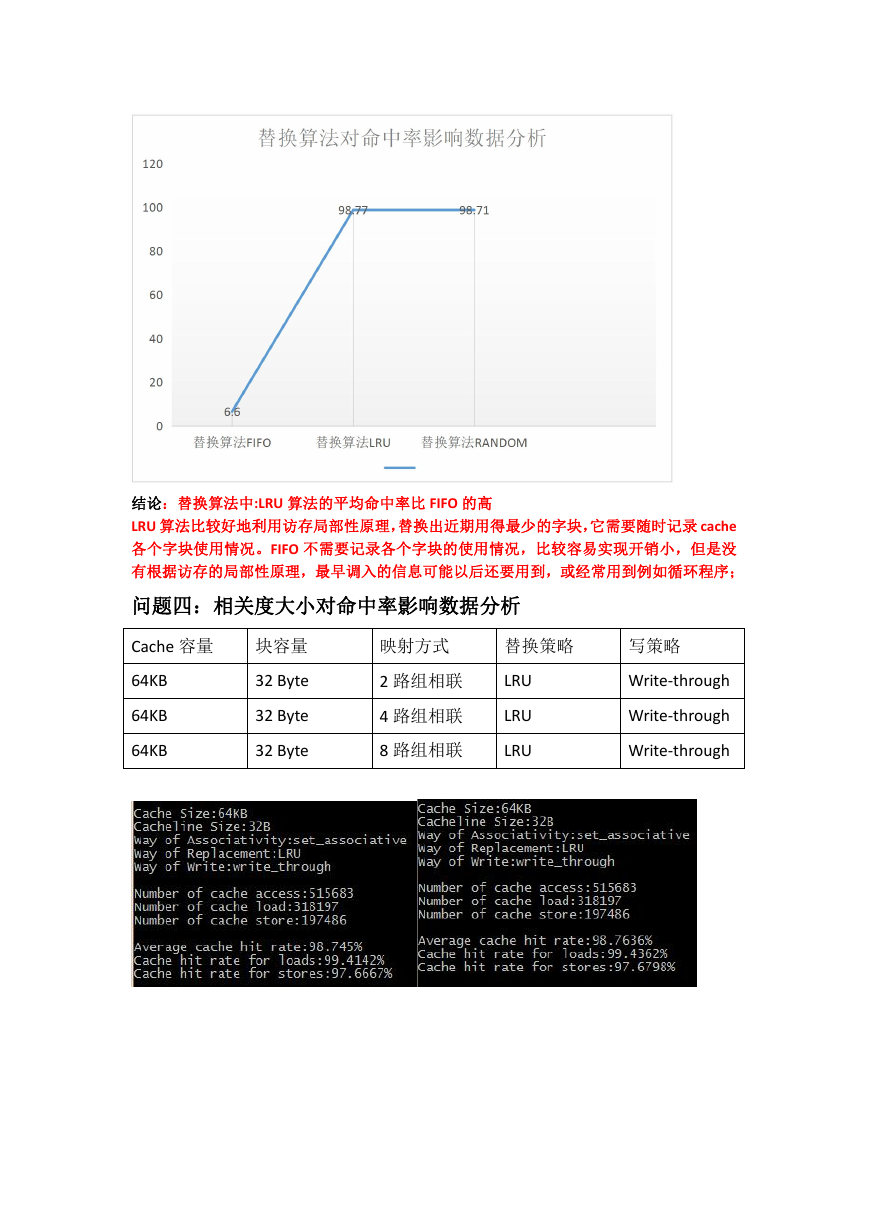

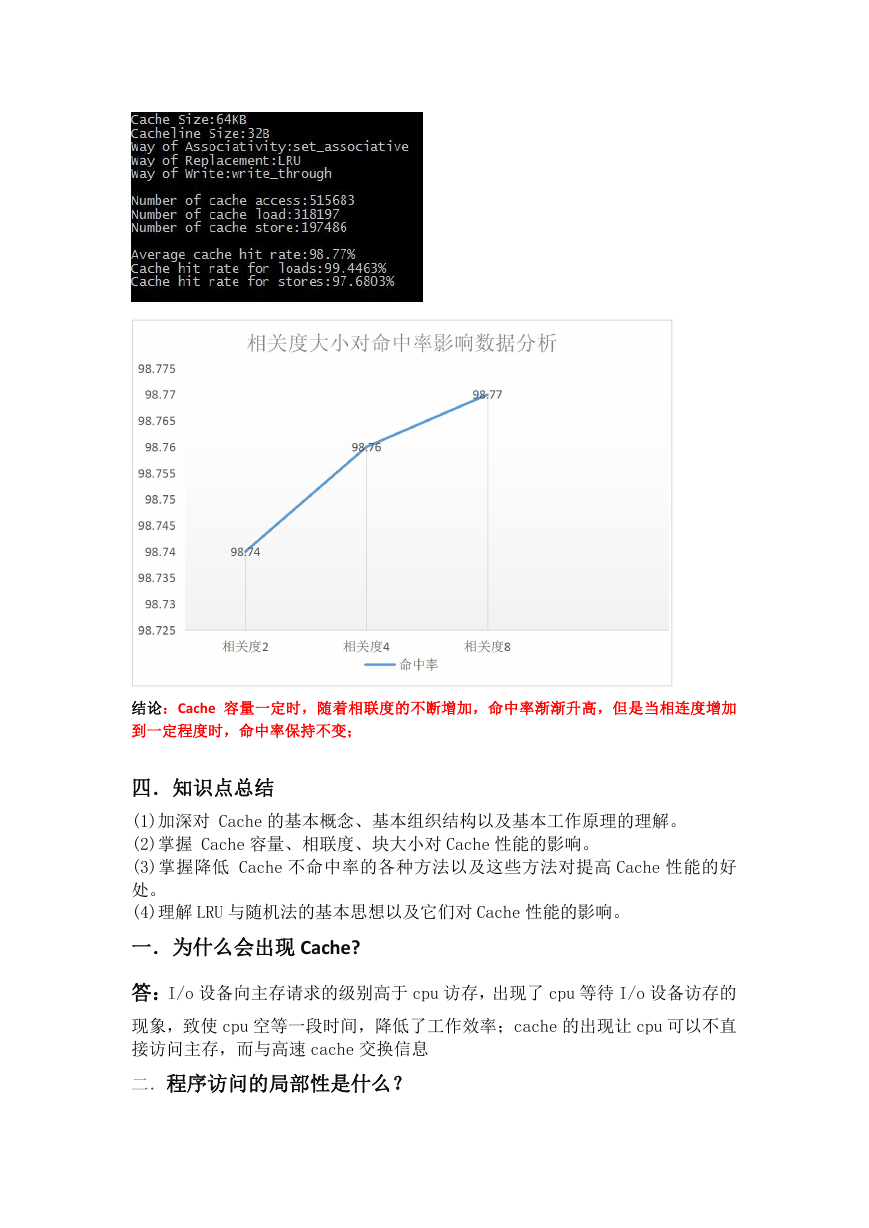

问题四:相关度大小对命中率影响数据分析

Cache 容量

64KB

64KB

64KB

块容量

32 Byte

32 Byte

32 Byte

映射方式

替换策略

写策略

2 路组相联

4 路组相联

8 路组相联

LRU

LRU

LRU

Write-through

Write-through

Write-through

�

结论:Cache 容量一定时,随着相联度的不断增加,命中率渐渐升高,但是当相连度增加

到一定程度时,命中率保持不变;

四.知识点总结

(1)加深对 Cache 的基本概念、基本组织结构以及基本工作原理的理解。

(2)掌握 Cache 容量、相联度、块大小对 Cache 性能的影响。

(3)掌握降低 Cache 不命中率的各种方法以及这些方法对提高 Cache 性能的好

处。

(4)理解 LRU 与随机法的基本思想以及它们对 Cache 性能的影响。

一.为什么会出现 Cache?

答:I/o 设备向主存请求的级别高于 cpu 访存,出现了 cpu 等待 I/o 设备访存的

现象,致使 cpu 空等一段时间,降低了工作效率;cache 的出现让 cpu 可以不直

接访问主存,而与高速 cache 交换信息

二.程序访问的局部性是什么?

�

答:cpu 从主存中存取指令的数据,只对主存局部区域地址访问,这是由于指令

和数据在主存内都是连续存放的,使得 cpu 在执行程序中,访存具有相对局部性,

这就称为程序访问的局部性;

三.cache 的基本组织结构

缓存是由 2n 个可编址的字组成,每个字有唯一的 n 位地址,缓存分成了若干块,

每块内包含了若干个字,块内字数相同,缓存的地址分为两端,高 c 位表示缓存

块号,低 b 位表示块内地址,块长有 2b

四.cache 的基本工作原理?

任何时刻都有一些主存块处在缓存块中,cpu 想要读取主存某字时,有两种可能:

1.所需要的字已经在缓存中 2.所需要的字不在缓存中,此时需要将该字所在的

主存字块调入 cache 中,此时主存与缓存建立关系

五.Cache 的替换机构

CPU 欲想要访存的主存块与 cache 块未建立对应关系,此时 cpu 访问主存,将该

字所在的主存块调入 Cache,如果 Cache 已经被装满,需要采用替换策略。

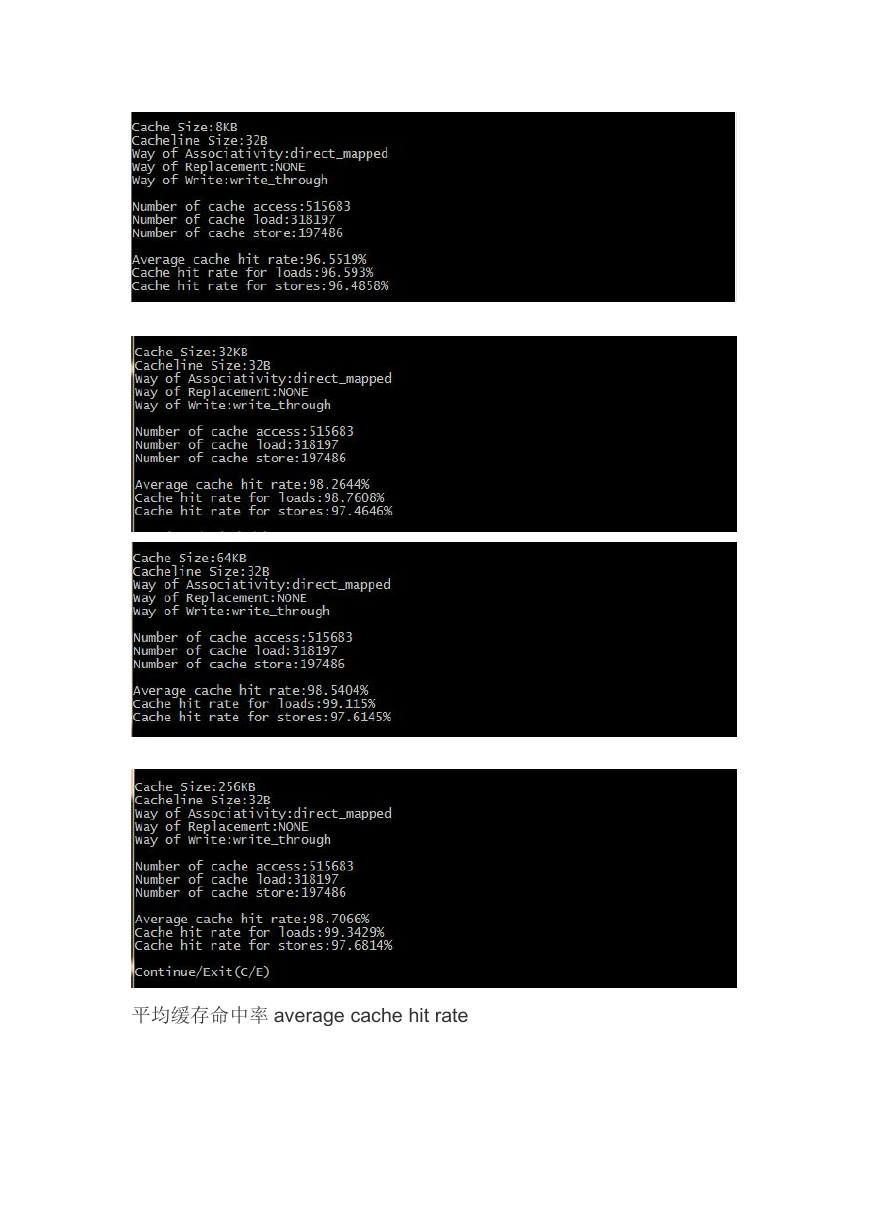

六.替换策略

1.先进先出(FIFO)算法

举例:小明有一个书柜(相当于主存),书柜里的书相当于主存中的块,卧室

还有一个床头柜(缓存),床头柜放书的数量有限,最在小明拿了一本工具书看,

紧接着几天又拿了其他书,床头柜满了,需要拿走书,按照(FIFO)算法,把最

早放入的那本工具书拿走了,但是这本工具书经常用到,所以这种方法,不可行,

不能提高 cache 命中率

2.近期最少使用(LRU)算法

长期不被使用的数据,在未来被用到的几率也不大。因此,当数据所占内存达

到一定阈值时,要移除掉最近最少使用的数据。Cache 命中率提高

3.随机法

采用随机数产生器,产生一个随机被替换的块,没有根据访存的局部性原理,不

能提高 Cache 命中率

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc