Arria 10收发器PHY用户指南

内容

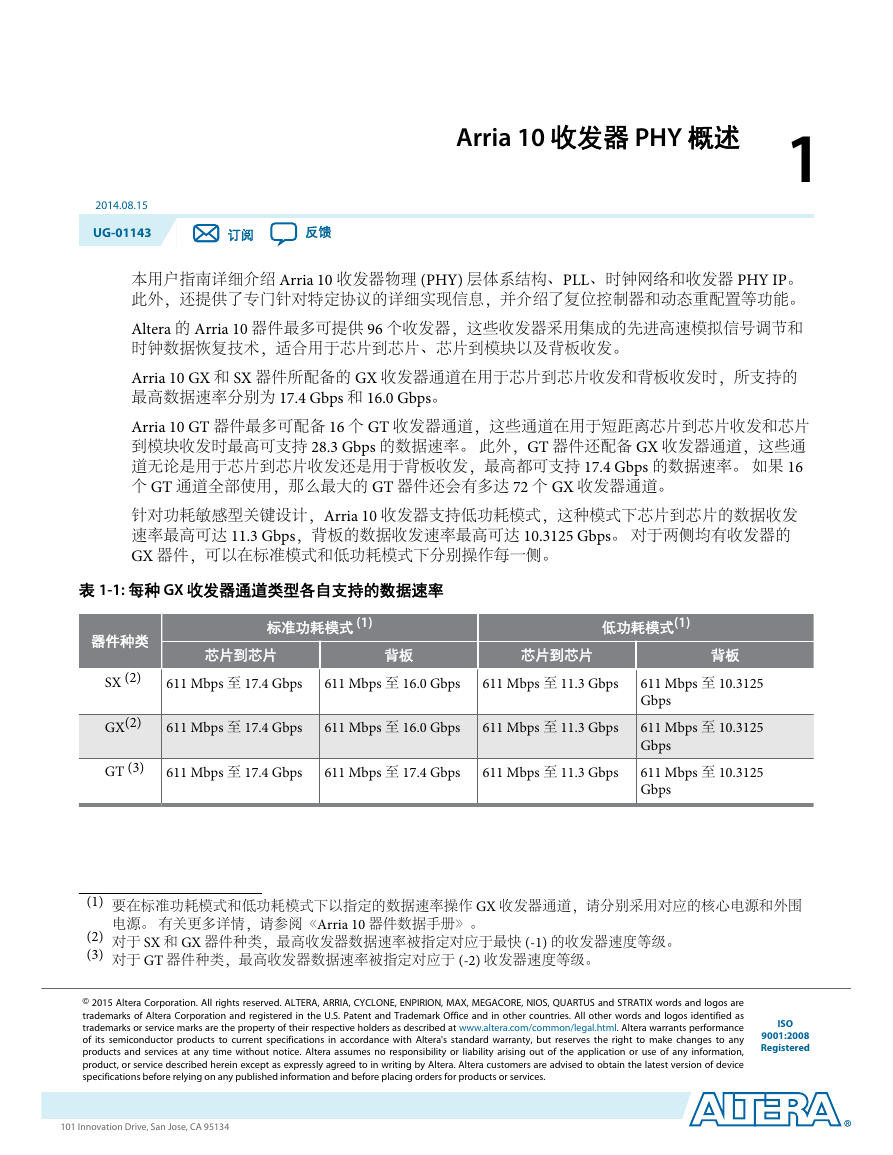

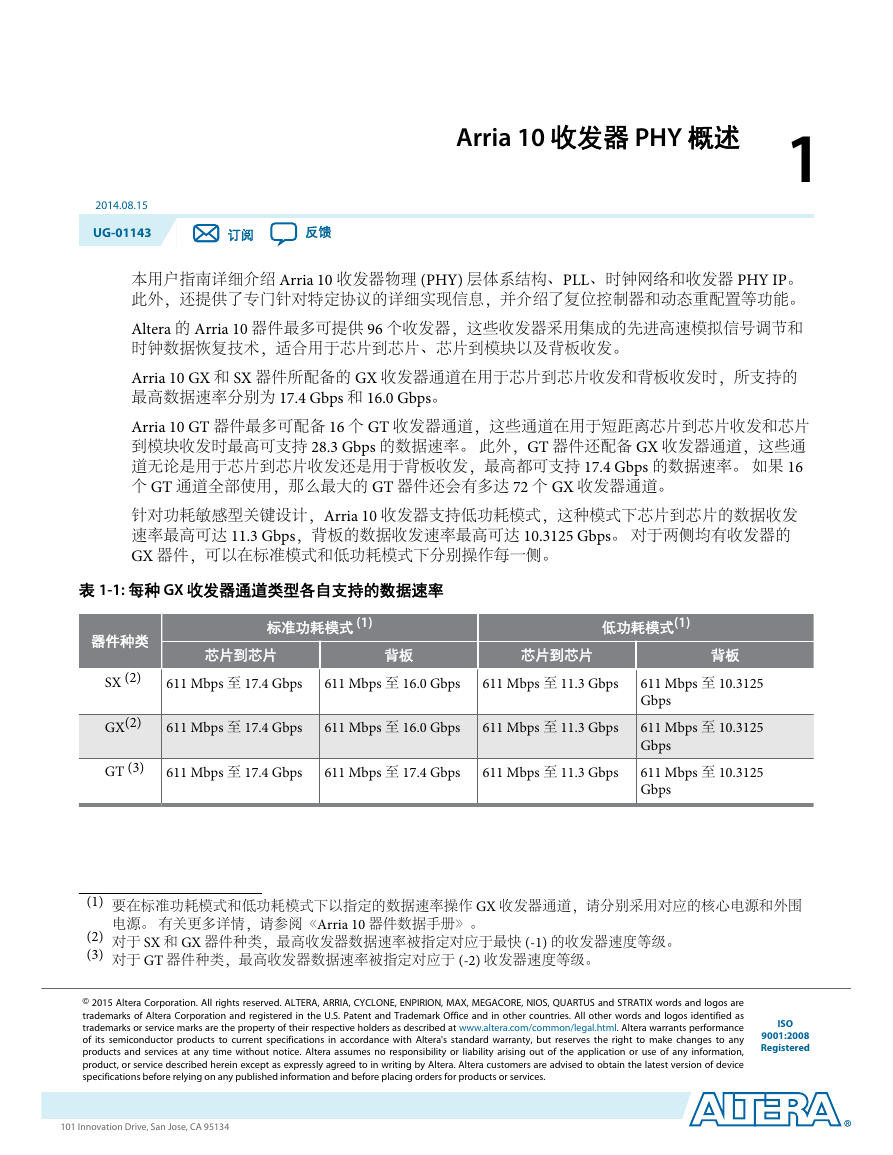

1. Arria 10 收发器 PHY 概述

器件收发器的布局

Arria 10 GX 器件收发器的布局

Arria 10 GT 器件收发器的布局

Arria 10 GX 和 GT 器件的封装详情

Arria 10 SX 器件收发器的布局

Arria 10 SX 器件的封装详情

收发器 PHY 体系结构概述

收发器 Bank 的体系结构

PHY 层收发器组件

GX 收发器通道

GT 收发器通道

收发器锁相环

高级发送 (ATX) PLL

小数分频 PLL (fPLL)

通道 PLL (CMU/CDR PLL)

时钟生成模块 (CGB)

校准

2. 实现Arria 10收发器中的协议

收发器设计IP模块

收发器设计流程

选择和例化PHY IP内核

配置PHY IP内核

生成PHY IP内核

选择PLL IP内核

配置PLL IP内核

生成PLL IP内核

复位控制器

创建重配置逻辑

连接PHY IP到PLL IP和复位控制器

连接收发器数据通路到MAC IP内核或者到数据生成器或分析器

编译设计

验证设计的功能性

使用Pin Planner和Assignment Editor进行管脚分配

Arria 10收发器协议和PHY IP支持

使用Arria 10 Transceiver Native PHY IP Core

预置

一般参数和数据通路参数

PMA参数

增强型PCS参数

标准PCS参数

动态重配置参数

PMA端口

增强型PCS端口

标准PCS端口

IP内核文件位置

Interlaken

元帧格式和成帧层控制字

Interlaken配置时钟和绑定

xN时钟绑定方案

PLL反馈补偿时钟绑定方案

TX多通道绑定和RX多通道去偏斜对齐状态机

TX FIFO软绑定

RX多通道FIFO去偏斜状态机

如何在Arria 10收发器中实现Interlaken

设计实例

Interlaken的Native PHY IP参数设置

Ethernet

千兆以太网 (GbE) 和采用 IEEE 1588v2 的 GbE

GbE 和采用 IEEE 1588v2 的 GbE 的 8B/10B 编码

GbE 和采用 IEEE 1588v2 的 GbE 中的 8B/10B 编码器复位情况

GbE 和采用 IEEE 1588v2 的 GbE 的字对齐

GbE 和采用 IEEE 1588v2 的 GbE 的 8B/10B 解码

GbE 的速率匹配 FIFO

如何在Arria 10收发器中实现 GbE 和采用 IEEE 1588v2 的 GbE

GbE 和采用 IEEE 1588v2 的 GbE 的本机 PHY IP 参数设置

10GBASE-R、采用 IEEE 1588v2 的 10GBASE-R 和具有 FEC 的 10GBASE-R 种类

10GBASE-R 中的 XGMII 时钟方案

TX FIFO 和 RX FIFO

如何在 Arria 10 收发器中实现 10GBASE-R、采用 IEEE 1588v2 的 10GBASE-R 和具有 FEC 的 10GBASE-R

10GBASE-R、采用 IEEE 1588v2 的 10GBASE-R 和具有 FEC 的 10GBASE-R 的本机 PHY IP 参数设置

10GBASE-R 和采用 IEEE 1588v2 的 10GBASE-R 收发器配置的本机 PHY IP 端口

10GBASE-R PHY IP Core

10GBASE-KR PHY 版本信息

10GBASE-KR PHY 的性能和资源使用情况

10GBASE-KR 功能说明

参数化 10GBASE-KR PHY

常规选项

10GBASE-R参数

10GBASE-KR 自动协商和链路训练参数

10GBASE-KR 可选参数

10GBASE-KR PHY 接口

时钟和复位接口

数据接口

到标准SDR XGMII数据的XGMII映射

串行数据接口

控制和状态接口

动态重配置接口

Avalon-MM寄存器接口

10GBASE-KR PHY 寄存器定义

硬核收发器 PHY 寄存器

増强型PCS的寄存器

PMA 寄存器

创建 10GBASE-KR 设计方案

设计示例

仿真支持

1-Gigabit/10-Gigabit Ethernet (GbE) PHY IP内核

1G/10GbE PHY发布信息

1G/10GbE PHY的性能和资源使用情况

1G/10GbE PHY功能说明

时钟和复位接口

参数化1G/10GbE PHY

常规选项

10GBASE-R参数

10M/100M/1Gb Ethernet参数

速度检测参数

PHY模拟参数

1G/10GbE PHY接口

时钟和复位接口

数据接口

到标准SDR XGMII数据的XGMII映射

GMII接口

串行数据接口

控制和状态接口

动态重配置接口

Avalon-MM寄存器接口

寄存器定义

硬核收发器 PHY 寄存器

増强型PCS的寄存器

Arria 10 GMII PCS寄存器

PMA 寄存器

速度切换汇总

创建一个1G/10GbE设计

设计指南

通道布局指南

设计实例

仿真支持

TimeQuest时序约束

XAUI PHY IP 内核

XAUI 配置中的收发器数据通道

XAUI 支持的特性

XAUI PHY 版本信息

XAUI PHY 器件系列支持

XAUI 配置中的收发器时钟和通道布局指南

XAUI PHY 的性能和资源使用情况

参数化 XAUI PHY

XAUI PHY 常规参数

XAUI PHY 高级选项参数

XAUI PHY 端口

XAUI PHY 接口

SDR XGMII TX 接口

SDR XGMII RX 接口

收发器串行数据接口

XAUI PHY 时钟、复位和断电接口

XAUI PHY PMA 通道控制器接口

XAUI PHY 可选 PMA 控制和状态接口

XAUI PHY 寄存器接口和寄存器说明

缩略语

PCI Express

PIPE的收发器通道数据通路

所支持的PIPE特性

Gen1/Gen2特性

Gen1 (2.5 Gbps)与Gen2 (5 Gbps)之间的动态切换

发送器电路空闲生成

电源状态管理

兼容码型传输支持的8B/10B编码器的使用情况

接收器电路空闲推断(EII)

接收器状态

接收器检测

Gen1和Gen2时钟补偿

PCIe反向并行环回

Gen3特性

自动速度协商

速率切换

Gen3发送器电路空闲生成

Gen3时钟补偿

Gen3电源状态管理

CDR控制

变速器

如何连接PIPE Gen1、Gen2和Gen3模式的TX PLL

如何在Arria 10收发器中实现PCI Express

PCI Express的Native PHY IP参数设置

PCI Express的Native PHY IP端口

如何对PIPE配置布局通道

绑定配置中的主通道

Gen3数据速率的PHY IP Core for PCIe (PIPE)链路均衡

设计实例

CPRI

CPRI 的收发器通道数据通路和时钟

CPRI的TX PLL选择

自动协商

CPRI支持的特性

CPRI确定性延迟模式下的字对齐器

发送器和接收器延迟

CPRI的手动模式下的字对齐器

如何在Arria 10收发器中实现CPRI

CPRI的Native PHY IP参数设置

其它协议

使用Enhanced PCS的"Basic (Enhanced PCS)"和"Basic with KR FEC" 配置

如何在Arria 10收发器中实现Basic (Enhanced PCS)和Basic with KR FEC收发器配置规则

Basic (Enhanced PCS)和Basic with KR FEC的Native PHY IP参数设置

如何在Basic Enhanced PCS中低延时

TX Bitslip

TX极性反转

RX Bit Slip

RX极性反转

使用标准 PCS 的基本/自定义协议和带有速率匹配配置的基本/自定义协议

字对齐器手动模式

字对齐器同步状态机模式

RX 比特滑移

RX 极性反转

RX比特反转

RX字节反转

基本(单宽度)模式下的速率匹配FIFO

速率匹配FIFO基本(双宽度)模式

8B/10B编码器和解码器

8B/10B TX差异控制

如何在基本模式下使能低延时

TX比特滑移

TX极性倒转

TX比特反转

TX字节反转

如何在Arria 10收发器中实现Basic,Basic with Rate Match收发器配置规则

Basic,Basic with Rate Match配置的Native PHY IP参数设置

使用Arria 10 GT通道,数据速率超过17.4 Gbps的设计考量

Arria 10 的 GT 通道使用

收发器PHY IP

PLL和GT收发器通道时钟线

复位控制器

PCS Direct收发器配置规则的Native PHY IP参数设置

如何使用低延时模式的增强PCS来实现高于17.4 Gbps的设计

如何实现PCS Direct收发器配置规则

仿真收发器Native PHY IP内核

NativeLink仿真流程

如何使用NativeLink指定一个ModelSim-Altera仿真

如何使用NativeLink运行一个ModelSim-Altera仿真

如何使用NativeLink指定第三方RTL仿真器

定制仿真流程

如何使用仿真库编译器

如何生成脚本

定制仿真脚本

Qsys仿真脚本

在Qsys中生成脚本

使用ip-make-simscript工具

3. PLL和时钟网络

PLL

ATX PLL

例化ATX PLL IP内核

ATX PLL IP 内核

fPLL

例化fPLL IP内核

fPLL IP内核

CMU PLL

例化CMU PLL IP内核

CMU PLL IP内核

输入参考时钟源

专用参考时钟管脚

接收器输入管脚

作为输入参考时钟源的PLL级联

参考时钟网络

作为输入参考时钟的全局时钟或内核时钟

发送器时钟网络

x1 时钟线

x6时钟线

xN 时钟线

GT 时钟线

时钟生成模块

FPGA内核逻辑-收发器接口时钟

发送器数据路径接口时钟

接收器数据通路接口时钟

通道绑定

PMA绑定

x6/xN绑定

PLL反馈补偿绑定

PMA和PCS绑定

选择通道绑定方案

偏移计算

PLL反馈和级联时钟网络

使用PLL和时钟网络

非bonded配置

实现单通道x1非Bonded配置

实现多通道x1非Bonded配置

实现多通道xN非Bonded配置

Bonded配置

实现x6/xN绑定模式

实现PLL反馈补偿绑定模式

实现PLL级联

混合和匹配实例

4. 复位收发器通道

什么时候需要复位?

如何进行复位?

所建议的复位序列

器件上电后复位发送器

器件操作过程中复位发送器

器件上电后复位接收器

器件操作过程中复位接收器

CDR手动锁定模式中复位收发器。

CDR手动锁定模式的控制设置

CDR手动锁定模式中复位收发器

复位和断电信号影响的收发器模块

使用Altera收发器PHY复位控制器

参数化收发器PHY复位控制器的IP

收发器PHY复位控制器参数

收发器PHY复位控制器接口

收发器PHY复位控制器资源使用

使用用户编码复位控制器

用户编码复位控制器信号

合并状态或PLL锁定信号

Bonded PCS和PMA通道的时序约束

5. Arria 10 收发器 PHY 体系结构

Arria 10 PMA 体系结构

发送器

串化器

发送器缓冲器

可编程的输出差分电压

可编程预加重

可编程的发送器片上终端 (OCT)

接收器

接收器缓冲器

可编程的共模电压 (VCM)

可编程的差分片上终端 (OCT)

信号检测器

连续时间线性均衡 (CTLE)

高增益模式

高数据速率模式

如何启用 CTLE

可变增益放大器 (VGA)

判定反馈均衡 (DFE)

如何启用 DFE

嵌入芯片的仪器 (ODI)

时钟数据恢复 (CDR) 单元

锁定到参考时钟模式

锁定到数据模式

CDR 锁定模式

自动锁定模式

手动锁定模式

解串器

环回

Arria 10 增强型 PCS 体系结构

发送器数据路径

增强型 PCS TX FIFO(与标准 PCS 和 PCIe Gen3 PCS 共享)

相位补偿模式

寄存器模式

Interlaken 模式

基本模式

Interlaken 帧生成器

Interlaken CRC-32 生成器

64B/66B 编码器和发送器状态机

增强型 PCS 模式生成器

PRBS 生成器

伪随机模式生成器

扰频器

Interlaken 差异生成器

TX 变速器、TX Bitslip 和极性反转

KR FEC 模块

接收器数据路径

RX 变速器、RX Bitslip 和极性反转

模块同步器

Interlaken 差异检查器

解扰器

Interlaken 帧同步器

64B/66B 解码器和发送器状态机

PRBS 验证器

PRP 验证器

10GBASE-R 误码率 (BER) 检查器

Interlaken CRC-32 检查器

增强型 PCS RX FIFO

相位补偿模式

寄存器模式

Interlaken 模式

10GBASE-R 模式

删除空闲数据/OS

删除空闲字

基本模式

RX KR FEC 模块

Arria 10 Standard PCS体系结构

发送器数据路径

TX FIFO(与增强型 PCS 和 PCIe Gen3 PCS 共享)

TX FIFO 低延时模式

TX FIFO 寄存器模式

字节串化器

绑定字节串化器

字节串化器禁用模式

字节串化器串化 x2 模式

字节串化器串化 x4 模式

8B/10B 编码器

8B/10B 编码器控制代码编码

8B/10B 编码器复位条件

8B/10B 编码器空闲字符替换功能

8B/10B 编码器当前运行差异控制功能

8B/10B 编码器位反转功能

8B/10B 编码器字节反转功能

极性反转功能

伪随机二进制序列 (PRBS) 生成器

TX Bitslip

接收器数据路径

字对齐器

字对齐器 Bitslip 模式

字对齐器手动模式

字对齐器同步状态机模式

字对齐器确定性延迟模式

各种字对齐器模式的字对齐器模式长度

字对齐器 RX 位反转功能

字对齐器 RX 字节反转功能

RX 极性反转功能

速率匹配 FIFO

8B/10B 解码器

8B/10B 解码器控制代码编码

8B/10B 解码器运行差异检查器功能

伪随机二进制序列 (PRBS) 验证器

字节解串器

字节解串器禁用模式

字节解串器解串 x2 模式

字节解串器解串 x4 模式

绑定字节解串器

RX FIFO(与增强型 PCS 和 PCIe Gen3 PCS 共享)

RX FIFO 低延时模式

RX FIFO 寄存器模式

Arria 10 PCI Express Gen3 PCS 体系结构

发送器数据路径

TX FIFO(与标准 PCS 和增强型 PCS 共享)

变速器

接收器数据路径

模块同步器

速率匹配 FIFO

RX FIFO(与标准 PCS 和增强型 PCS 共享)

PIPE 接口

自动速度协商

时钟数据恢复控制

6. 重配置接口和动态重配置

端口和参数

嵌入式调试

本机 PHY IP 内核嵌入式调试

PRBS 软核累加器

PLL IP 内核嵌入式调试

通道合并要求

与重配置接口进行交互

对重配置接口执行读取

对重配置接口执行写入

重新配置通道和 PLL 模块

第 1 步: 生成所需的配置文件

第 2 步: 确定地址偏移和差异

第 3 步: 执行读取-修改-写入

第 4 步: 将收发器通道或收发器 PLL 复位

使用配置文件

切换发送器 PLL

切换参考时钟

ATX 参考时钟切换

fPLL 参考时钟切换

CDR 和 CMU 参考时钟切换

更改 PMA 模拟参数

使用数据码型生成器和检查器

使用 PRBS 和方波数据码型生成器和检查器

启用 PRBS 和方波数据生成器

启用 PRBS 数据检查器

启用伪随机码型测试模式

启用 PRBS 码型反转

不支持的功能

Arria 10 收发器寄存器映射

7. 模拟参数设置

使用 Assignment Editor 进行模拟参数设置

使用已知的分配更新 Quartus 设置文件

模拟参数设置列表

接收器常规模拟设置

XCVR_A10_RX_LINK

XCVR_A10_RX_TERM_SEL

接收器均衡设置

XCVR_A10_RX_EQ_DC_GAIN_TRIM

XCVR_A10_RX_ADP_CTLE_ACGAIN_4S

XCVR_A10_RX_ADP_CTLE_EQZ_1S_SEL

XCVR_A10_RX_ADP_VGA_SEL

XCVR_A10_RX_ONE_STAGE_ENABLE

判定反馈均衡器 (DFE) 设置

XCVR_A10_RX_ADP_DFE_FXTAP

发送器常规模拟设置

XCVR_A10_TX_LINK

XCVR_A10_TX_COMPENSATION_EN

发送器预加重设置

XCVR_A10_TX_PRE_EMP_SIGN_PRE_TAP_1T

XCVR_A10_TX_PRE_EMP_SIGN_PRE_TAP_2T

XCVR_A10_TX_PRE_EMP_SIGN_1ST_POST_TAP

XCVR_A10_TX_PRE_EMP_SIGN_2ND_POST_TAP

XCVR_A10_TX_PRE_EMP_SWITCHING_CTRL_PRE_TAP_1T

XCVR_A10_TX_PRE_EMP_SWITCHING_CTRL_PRE_TAP_2T

XCVR_A10_TX_PRE_EMP_SWITCHING_CTRL_1ST_POST_TAP

XCVR_A10_TX_PRE_EMP_SWITCHING_CTRL_2ND_POST_TAP

XCVR_A10_TX_VOD_OUTPUT_SWING_CTRL

专用参考时钟设置

XCVR_A10_REFCLK_TERM_TRISTATE

8. 当前版本的文档修订历史

先前版本的文档修订历史

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc