FPGA 通过 SPI 对 ADC 配置简介(一)------- 什么是 SPI?

原创小青菜哥哥 最后发布于 2018-03-12 16:36:28 阅读数 3613 收藏

展开

所谓 SPI(Serial Peripheral Interface),即串行外设接口。它是一种高速、全双工的数据通信

总线,并且在芯片的管脚只占有 4 根线,节省了芯片的管脚,同时极大的方便了 PCB 的布

局。正是由于这种简单、易用的特性,如今越来越多的芯片集成了这种通信协议,比如我们

经常使用的 ADC 芯片。

目前,市面上绝大多数的 ADC(模数转换器)芯片都内嵌专用的 SPI 配置接口,通过配置其

SPI 接口可以对 ADC 内部的控制寄存器进行读、写操作,从而灵活的使用 ADC 芯片的各种功

能。甚至对于某些 ADC 来说,如果不事先对其进行正确、有效的配置,则该 ADC 无法正常

工作。

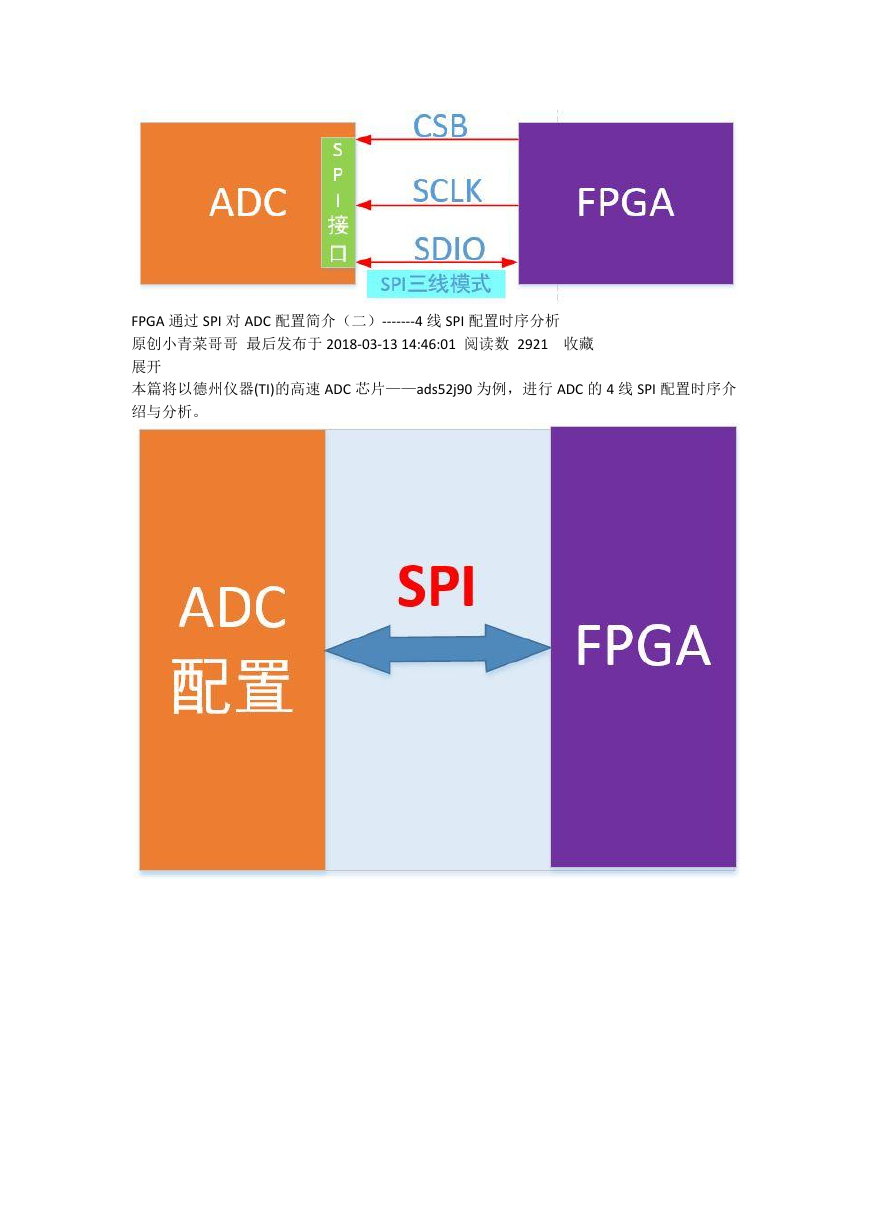

用于 ADC 配置的 SPI 接口分为 4 线模式(例如 Analog Device 的 AD9639)和 3 线模式(Analog

Device 的 AD9249)。对于 4 线模式来说,它有 4 根信号线,分别为:SDI(Serial Data In)、

SDO(Serial Data Out)、SCLK(Serial Clock)以及 CS(Chip Select)。3 线模式与 4 线模式的不

同之处在于 SDI 与 SDO 信号合并,称为 SDIO。另外,某些 ADC 的三线模式较为简单,SDIO

只用做输入端口 SDI(例如德州仪器的 ADS5281 芯片),没有 SDO 的功能,实现起来较为简

单。

�

FPGA 通过 SPI 对 ADC 配置简介(二)-------4 线 SPI 配置时序分析

原创小青菜哥哥 最后发布于 2018-03-13 14:46:01 阅读数 2921 收藏

展开

本篇将以德州仪器(TI)的高速 ADC 芯片——ads52j90 为例,进行 ADC 的 4 线 SPI 配置时序介

绍与分析。

�

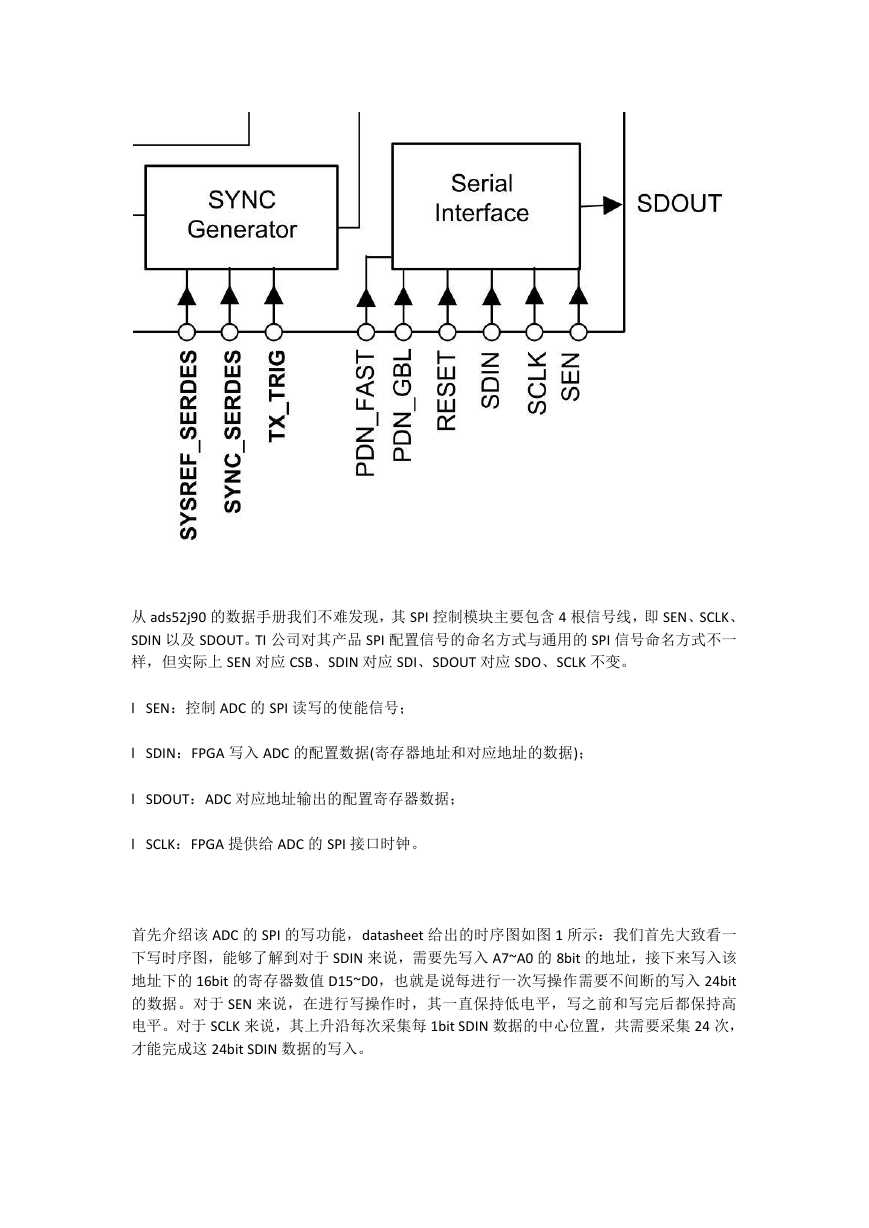

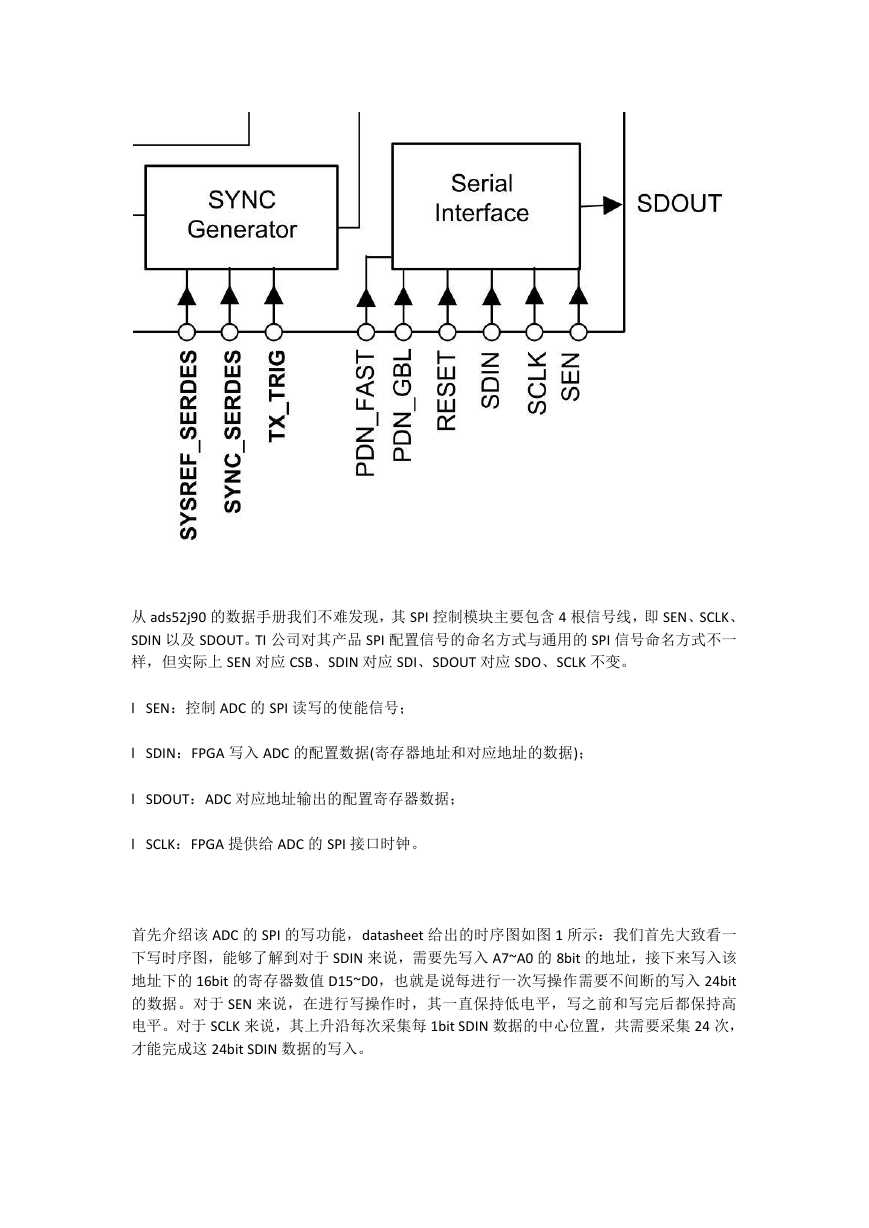

从 ads52j90 的数据手册我们不难发现,其 SPI 控制模块主要包含 4 根信号线,即 SEN、SCLK、

SDIN 以及 SDOUT。TI 公司对其产品 SPI 配置信号的命名方式与通用的 SPI 信号命名方式不一

样,但实际上 SEN 对应 CSB、SDIN 对应 SDI、SDOUT 对应 SDO、SCLK 不变。

l SEN:控制 ADC 的 SPI 读写的使能信号;

l SDIN:FPGA 写入 ADC 的配置数据(寄存器地址和对应地址的数据);

l SDOUT:ADC 对应地址输出的配置寄存器数据;

l SCLK:FPGA 提供给 ADC 的 SPI 接口时钟。

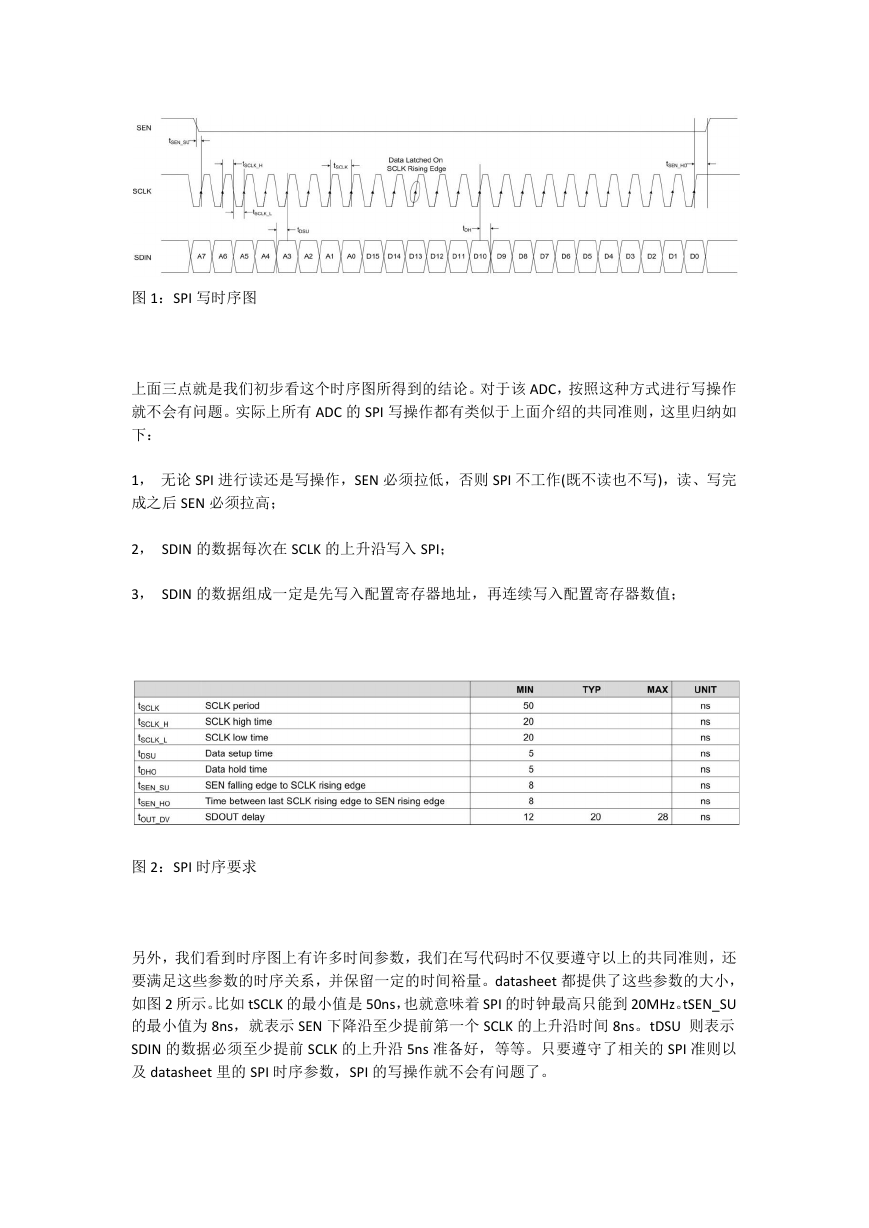

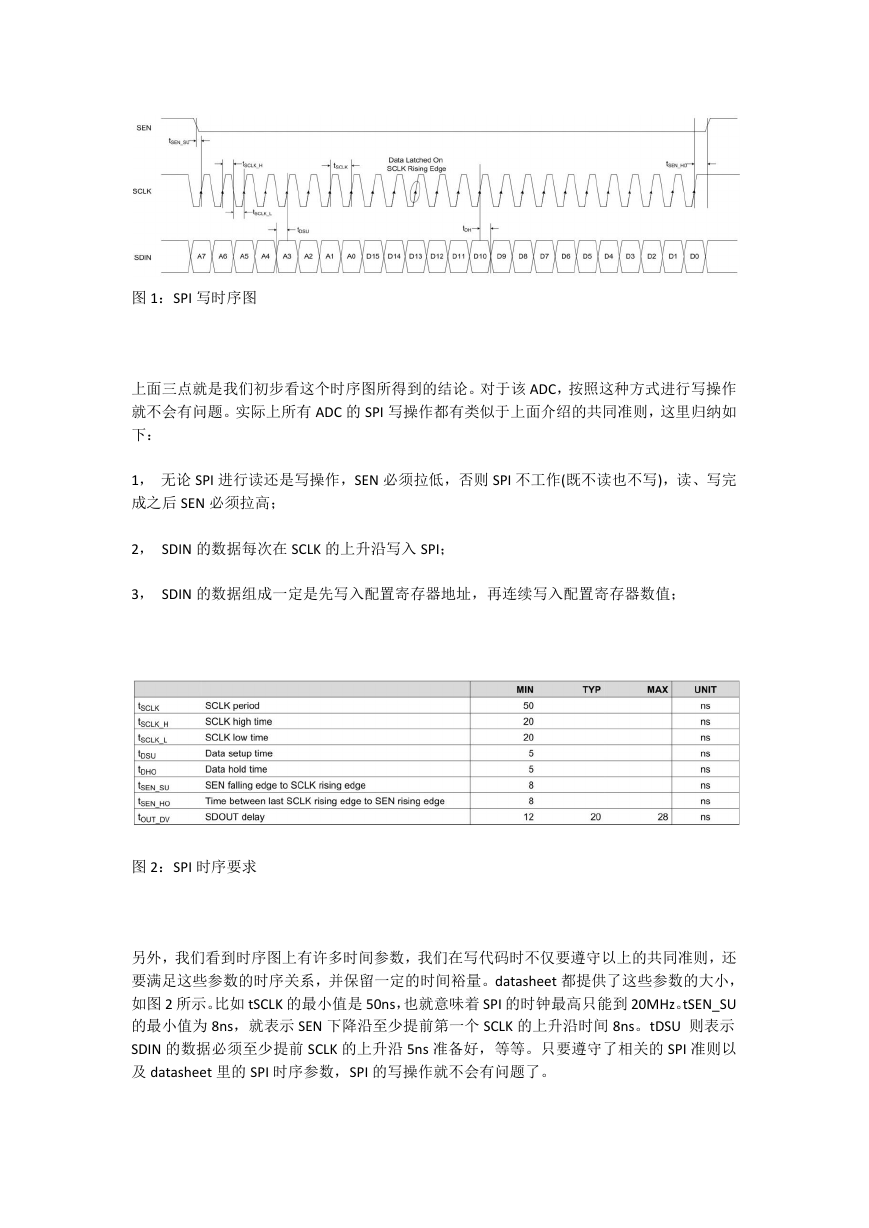

首先介绍该 ADC 的 SPI 的写功能,datasheet 给出的时序图如图 1 所示:我们首先大致看一

下写时序图,能够了解到对于 SDIN 来说,需要先写入 A7~A0 的 8bit 的地址,接下来写入该

地址下的 16bit 的寄存器数值 D15~D0,也就是说每进行一次写操作需要不间断的写入 24bit

的数据。对于 SEN 来说,在进行写操作时,其一直保持低电平,写之前和写完后都保持高

电平。对于 SCLK 来说,其上升沿每次采集每 1bit SDIN 数据的中心位置,共需要采集 24 次,

才能完成这 24bit SDIN 数据的写入。

�

图 1:SPI 写时序图

上面三点就是我们初步看这个时序图所得到的结论。对于该 ADC,按照这种方式进行写操作

就不会有问题。实际上所有 ADC 的 SPI 写操作都有类似于上面介绍的共同准则,这里归纳如

下:

1, 无论 SPI 进行读还是写操作,SEN 必须拉低,否则 SPI 不工作(既不读也不写),读、写完

成之后 SEN 必须拉高;

2, SDIN 的数据每次在 SCLK 的上升沿写入 SPI;

3, SDIN 的数据组成一定是先写入配置寄存器地址,再连续写入配置寄存器数值;

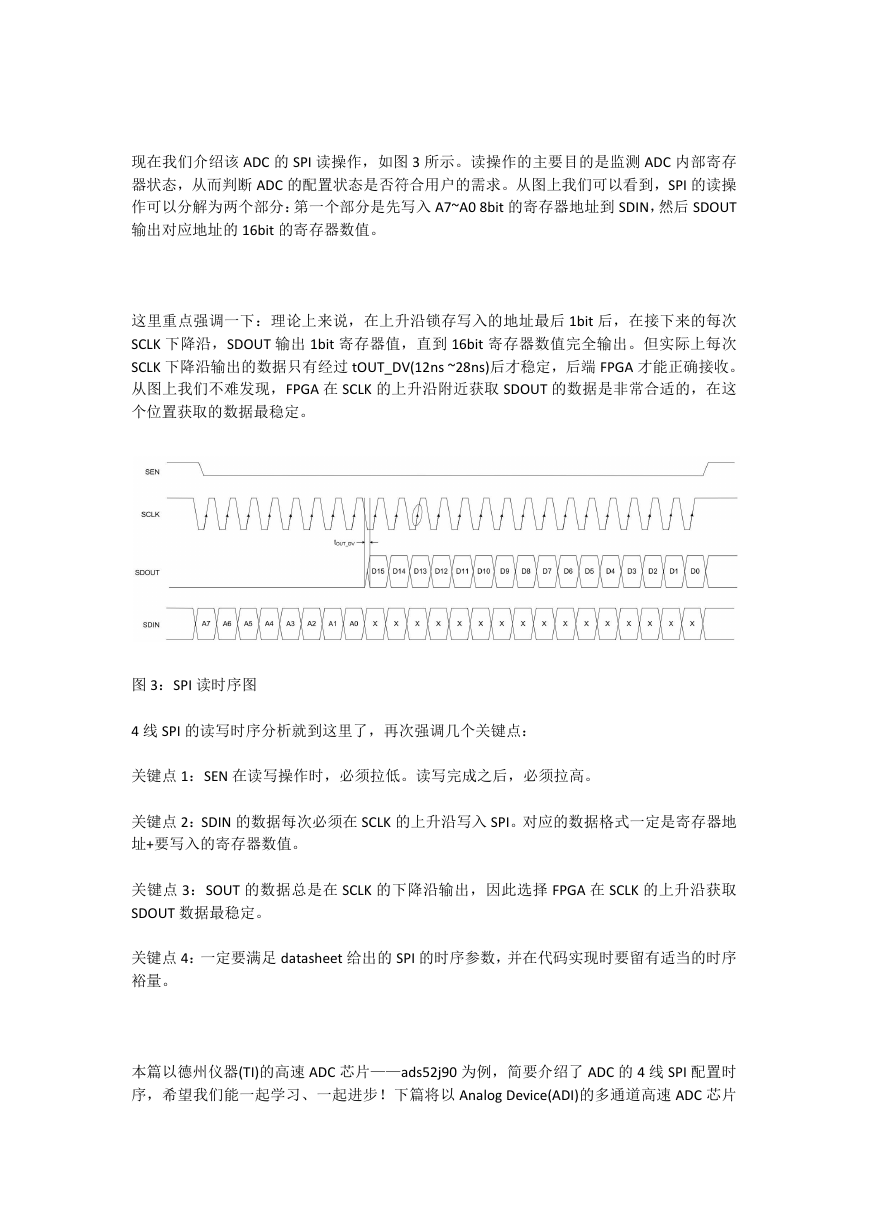

图 2:SPI 时序要求

另外,我们看到时序图上有许多时间参数,我们在写代码时不仅要遵守以上的共同准则,还

要满足这些参数的时序关系,并保留一定的时间裕量。datasheet 都提供了这些参数的大小,

如图 2 所示。比如 tSCLK 的最小值是 50ns,也就意味着 SPI 的时钟最高只能到 20MHz。tSEN_SU

的最小值为 8ns,就表示 SEN 下降沿至少提前第一个 SCLK 的上升沿时间 8ns。tDSU 则表示

SDIN 的数据必须至少提前 SCLK 的上升沿 5ns 准备好,等等。只要遵守了相关的 SPI 准则以

及 datasheet 里的 SPI 时序参数,SPI 的写操作就不会有问题了。

�

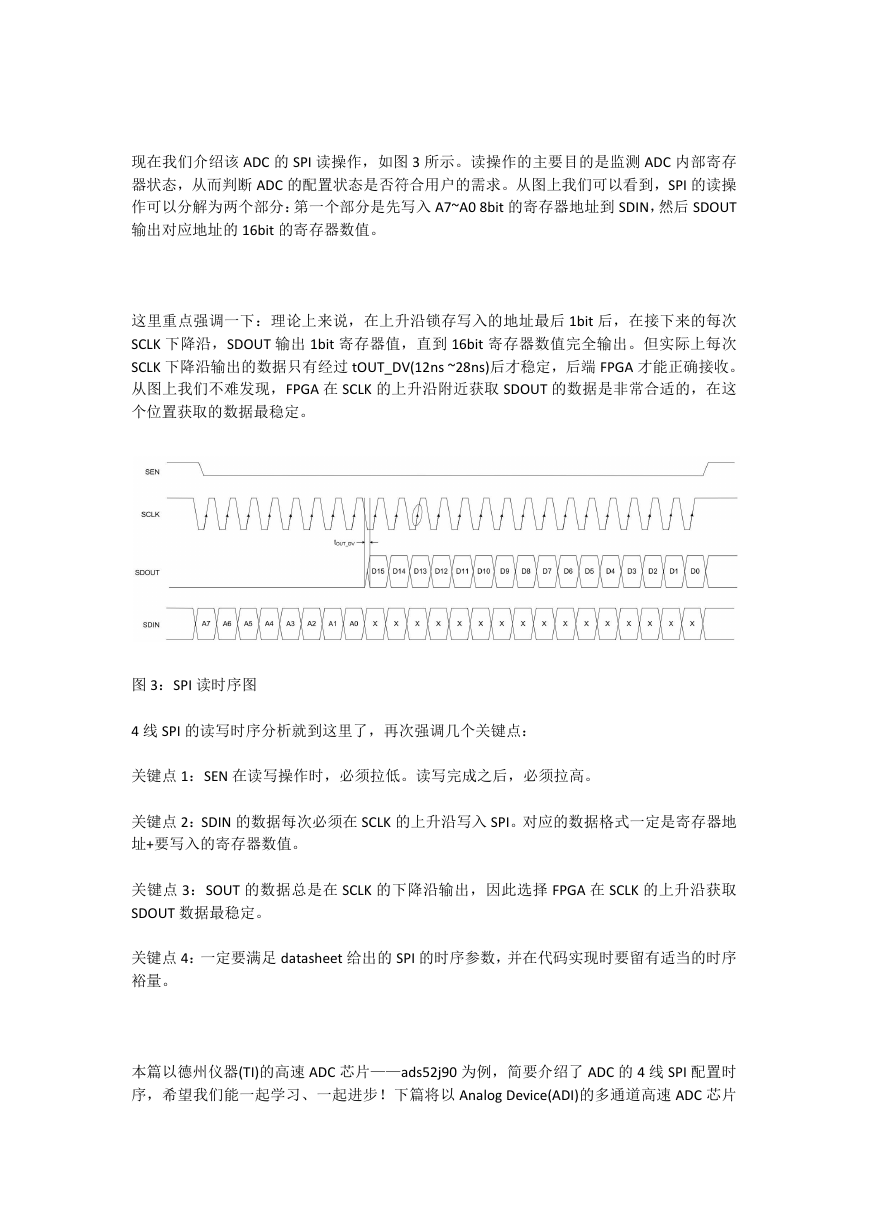

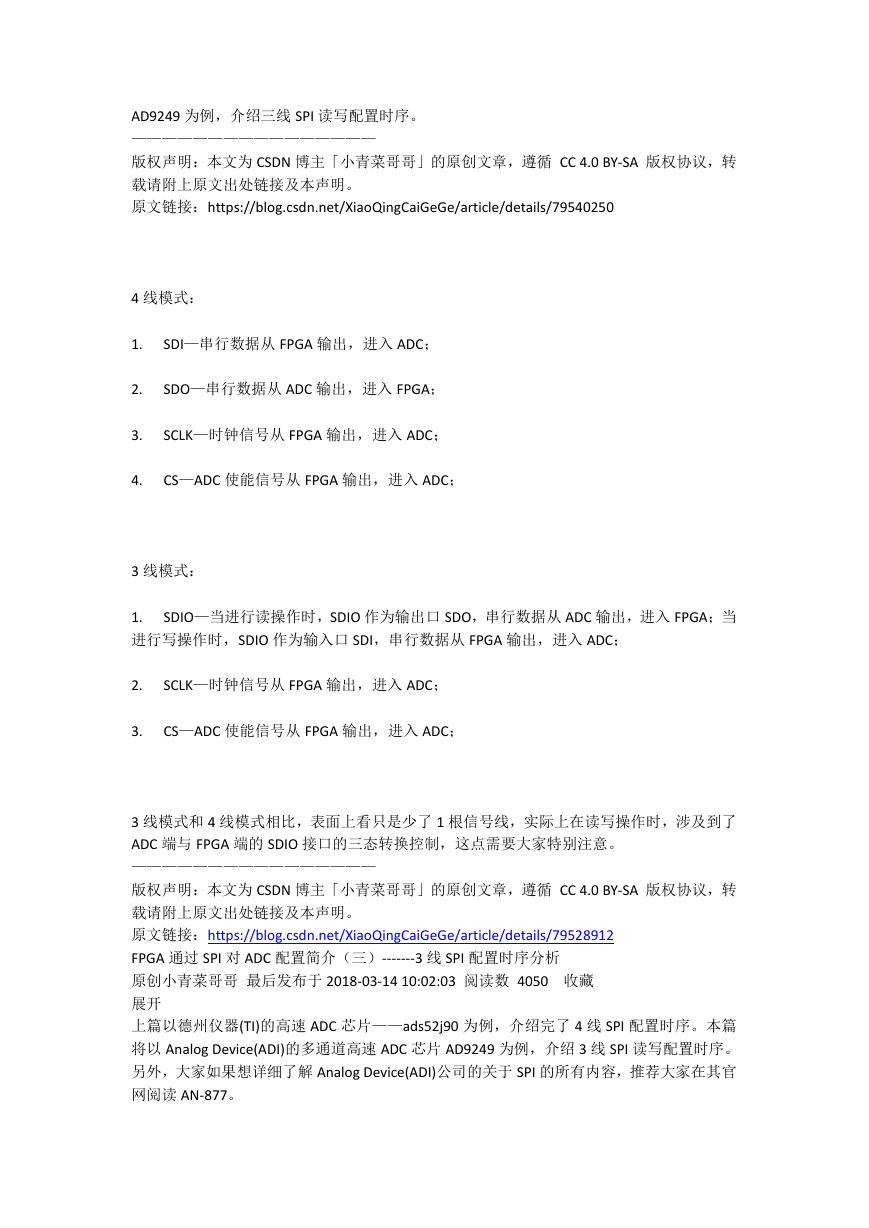

现在我们介绍该 ADC 的 SPI 读操作,如图 3 所示。读操作的主要目的是监测 ADC 内部寄存

器状态,从而判断 ADC 的配置状态是否符合用户的需求。从图上我们可以看到,SPI 的读操

作可以分解为两个部分:第一个部分是先写入 A7~A0 8bit 的寄存器地址到 SDIN,然后 SDOUT

输出对应地址的 16bit 的寄存器数值。

这里重点强调一下:理论上来说,在上升沿锁存写入的地址最后 1bit 后,在接下来的每次

SCLK 下降沿,SDOUT 输出 1bit 寄存器值,直到 16bit 寄存器数值完全输出。但实际上每次

SCLK 下降沿输出的数据只有经过 tOUT_DV(12ns ~28ns)后才稳定,后端 FPGA 才能正确接收。

从图上我们不难发现,FPGA 在 SCLK 的上升沿附近获取 SDOUT 的数据是非常合适的,在这

个位置获取的数据最稳定。

图 3:SPI 读时序图

4 线 SPI 的读写时序分析就到这里了,再次强调几个关键点:

关键点 1:SEN 在读写操作时,必须拉低。读写完成之后,必须拉高。

关键点 2:SDIN 的数据每次必须在 SCLK 的上升沿写入 SPI。对应的数据格式一定是寄存器地

址+要写入的寄存器数值。

关键点 3:SOUT 的数据总是在 SCLK 的下降沿输出,因此选择 FPGA 在 SCLK 的上升沿获取

SDOUT 数据最稳定。

关键点 4:一定要满足 datasheet 给出的 SPI 的时序参数,并在代码实现时要留有适当的时序

裕量。

本篇以德州仪器(TI)的高速 ADC 芯片——ads52j90 为例,简要介绍了 ADC 的 4 线 SPI 配置时

序,希望我们能一起学习、一起进步!下篇将以 Analog Device(ADI)的多通道高速 ADC 芯片

�

AD9249 为例,介绍三线 SPI 读写配置时序。

————————————————

版权声明:本文为 CSDN 博主「小青菜哥哥」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转

载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/XiaoQingCaiGeGe/article/details/79540250

4 线模式:

1.

2.

3.

4.

SDI—串行数据从 FPGA 输出,进入 ADC;

SDO—串行数据从 ADC 输出,进入 FPGA;

SCLK—时钟信号从 FPGA 输出,进入 ADC;

CS—ADC 使能信号从 FPGA 输出,进入 ADC;

3 线模式:

SDIO—当进行读操作时,SDIO 作为输出口 SDO,串行数据从 ADC 输出,进入 FPGA;当

1.

进行写操作时,SDIO 作为输入口 SDI,串行数据从 FPGA 输出,进入 ADC;

2.

3.

SCLK—时钟信号从 FPGA 输出,进入 ADC;

CS—ADC 使能信号从 FPGA 输出,进入 ADC;

3 线模式和 4 线模式相比,表面上看只是少了 1 根信号线,实际上在读写操作时,涉及到了

ADC 端与 FPGA 端的 SDIO 接口的三态转换控制,这点需要大家特别注意。

————————————————

版权声明:本文为 CSDN 博主「小青菜哥哥」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转

载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/XiaoQingCaiGeGe/article/details/79528912

FPGA 通过 SPI 对 ADC 配置简介(三)-------3 线 SPI 配置时序分析

原创小青菜哥哥 最后发布于 2018-03-14 10:02:03 阅读数 4050 收藏

展开

上篇以德州仪器(TI)的高速 ADC 芯片——ads52j90 为例,介绍完了 4 线 SPI 配置时序。本篇

将以 Analog Device(ADI)的多通道高速 ADC 芯片 AD9249 为例,介绍 3 线 SPI 读写配置时序。

另外,大家如果想详细了解 Analog Device(ADI)公司的关于 SPI 的所有内容,推荐大家在其官

网阅读 AN-877。

�

AD9249 的 SPI 控制模块包含 4 根信号线,即 CSB1、CSB2、SDIO 以及 SCLK。但 CSB1、CSB2

可以一起由 CSB 来控制,实际上就是 3 线 SPI。由于 3 线 SPI 数据的读、写操作在同一根信

号线 SDIO 上实现,因此其配置方式与 4 线的配置稍微有些不一样。下面我们将详细介绍读

写操作:

CSB:SPI 控制读写使能信号;

SDIO:SPI 的数据、地址读写端口;

SCLK:FPGA 提供给 ADC 的 SPI 接口时钟;

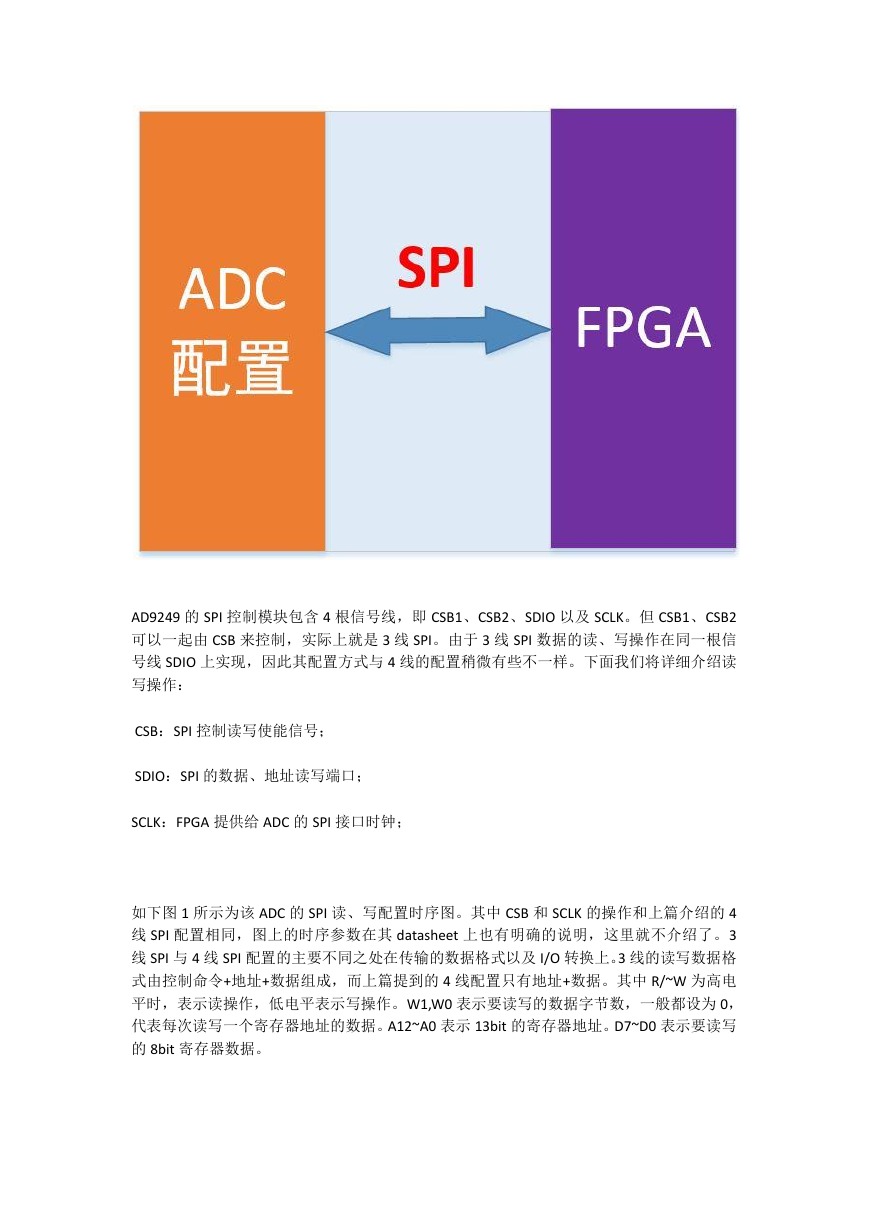

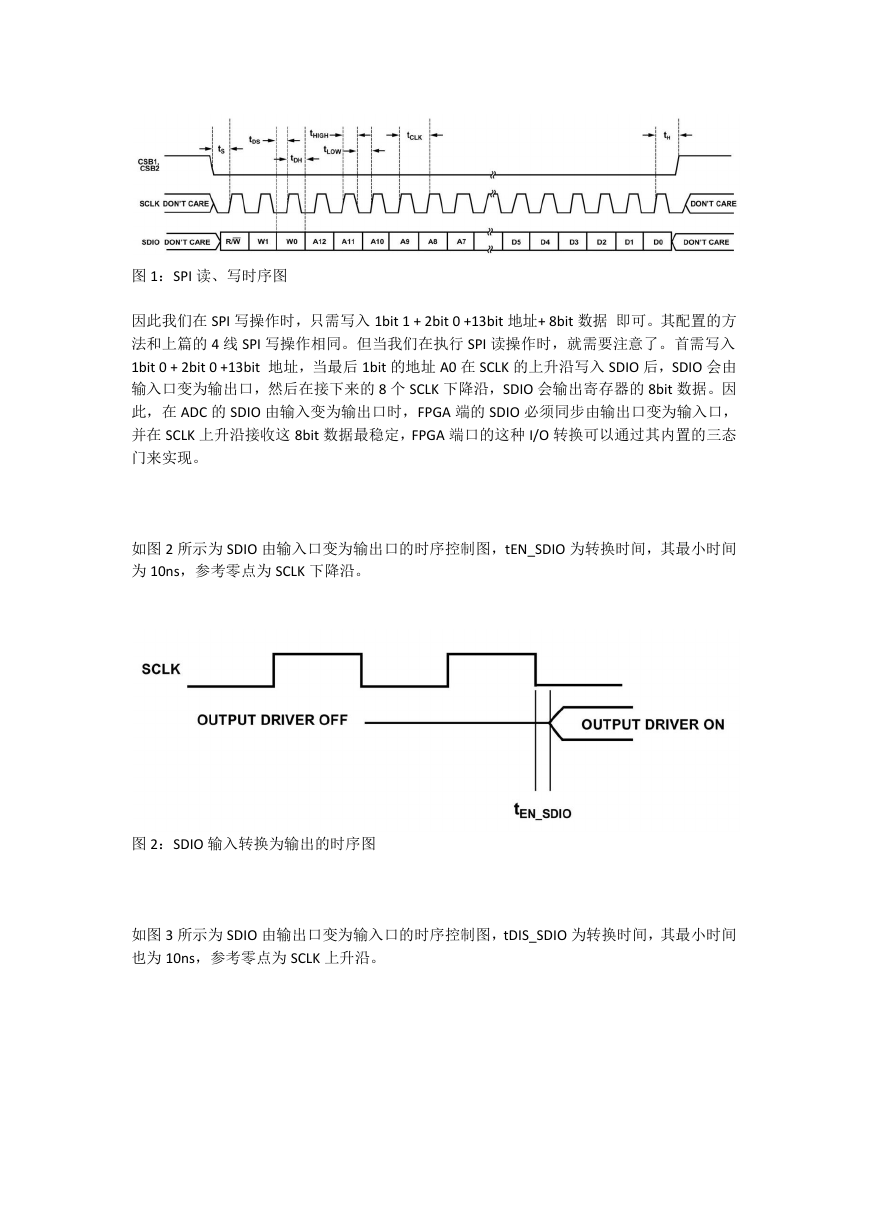

如下图 1 所示为该 ADC 的 SPI 读、写配置时序图。其中 CSB 和 SCLK 的操作和上篇介绍的 4

线 SPI 配置相同,图上的时序参数在其 datasheet 上也有明确的说明,这里就不介绍了。3

线 SPI 与 4 线 SPI 配置的主要不同之处在传输的数据格式以及 I/O 转换上。3 线的读写数据格

式由控制命令+地址+数据组成,而上篇提到的 4 线配置只有地址+数据。其中 R/~W 为高电

平时,表示读操作,低电平表示写操作。W1,W0 表示要读写的数据字节数,一般都设为 0,

代表每次读写一个寄存器地址的数据。A12~A0 表示 13bit 的寄存器地址。D7~D0 表示要读写

的 8bit 寄存器数据。

�

图 1:SPI 读、写时序图

因此我们在 SPI 写操作时,只需写入 1bit 1 + 2bit 0 +13bit 地址+ 8bit 数据 即可。其配置的方

法和上篇的 4 线 SPI 写操作相同。但当我们在执行 SPI 读操作时,就需要注意了。首需写入

1bit 0 + 2bit 0 +13bit 地址,当最后 1bit 的地址 A0 在 SCLK 的上升沿写入 SDIO 后,SDIO 会由

输入口变为输出口,然后在接下来的 8 个 SCLK 下降沿,SDIO 会输出寄存器的 8bit 数据。因

此,在 ADC 的 SDIO 由输入变为输出口时,FPGA 端的 SDIO 必须同步由输出口变为输入口,

并在 SCLK 上升沿接收这 8bit 数据最稳定,FPGA 端口的这种 I/O 转换可以通过其内置的三态

门来实现。

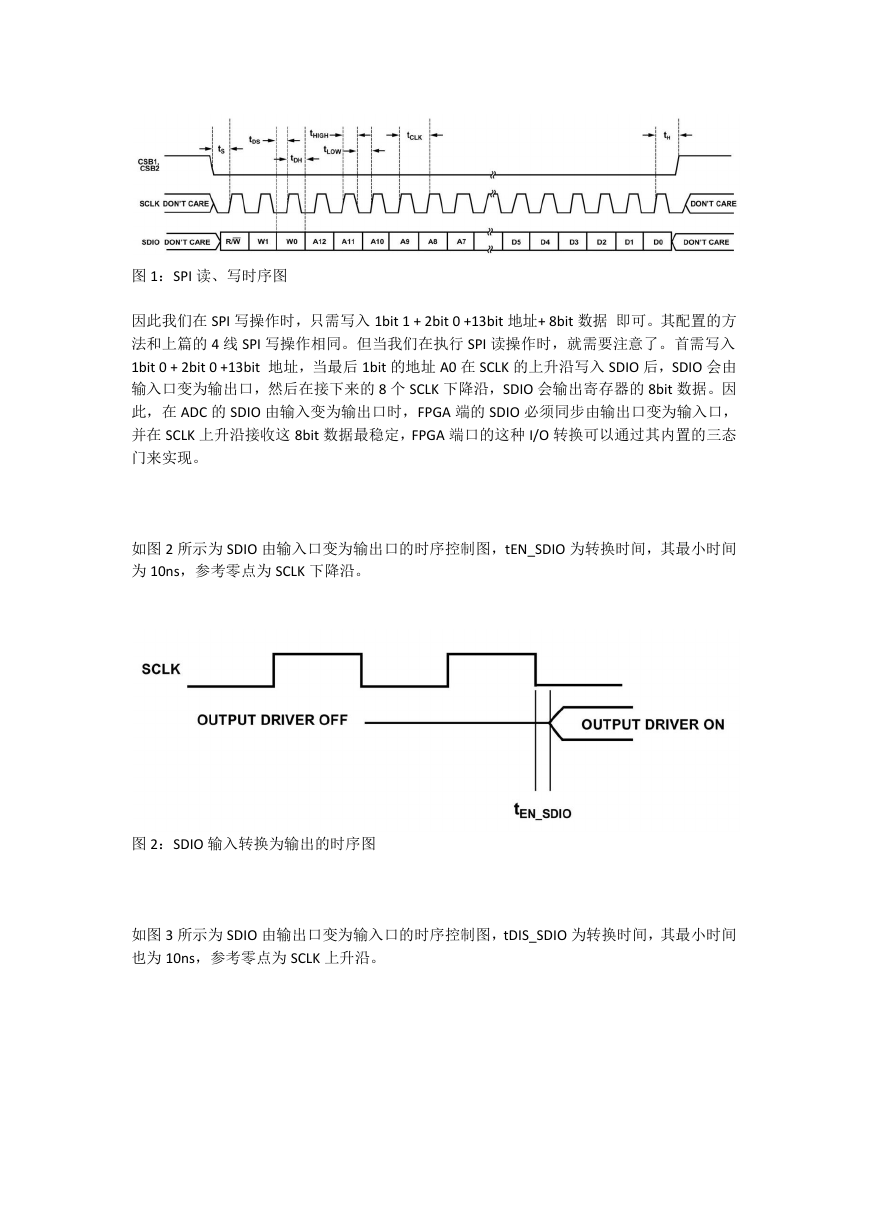

如图 2 所示为 SDIO 由输入口变为输出口的时序控制图,tEN_SDIO 为转换时间,其最小时间

为 10ns,参考零点为 SCLK 下降沿。

图 2:SDIO 输入转换为输出的时序图

如图 3 所示为 SDIO 由输出口变为输入口的时序控制图,tDIS_SDIO 为转换时间,其最小时间

也为 10ns,参考零点为 SCLK 上升沿。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc