实验一: 8 位加法器的设计

1.实验目的

(1)学习 isEXPERT/MAX+plus Ⅱ/Foudation Series 软件的基本使用方法。

(2)学习 GW48-CK EDA 实验开发系统的基本使用方法。

(3)了解 VHDL 程序的基本结构。

2.实验内容

设计并调试一个由两个 4 位二进制并行加法器级联而成的 8 位二进制并行加法器,并用

GW48_CK EDA 实验开发系统(拟采用的实验芯片的型号为 isPLSI1032E OLCC_84)进行

硬件验证。

3.实验条件

(1)画出系统的原理框架图,说明系统中各主要部分的功能。

(2)编写各个 VHDL 源程序。

(3)根据选用的软件编好用于系统仿真的测试文件。

(4)根据选用的软件及 EDA 实验开发装置编好用于硬件验证的管脚锁定文件。

(5)记录系统仿真、硬件验证结果。

(6)记录式样过程中出现的问题及解决方法。

4.实验设计

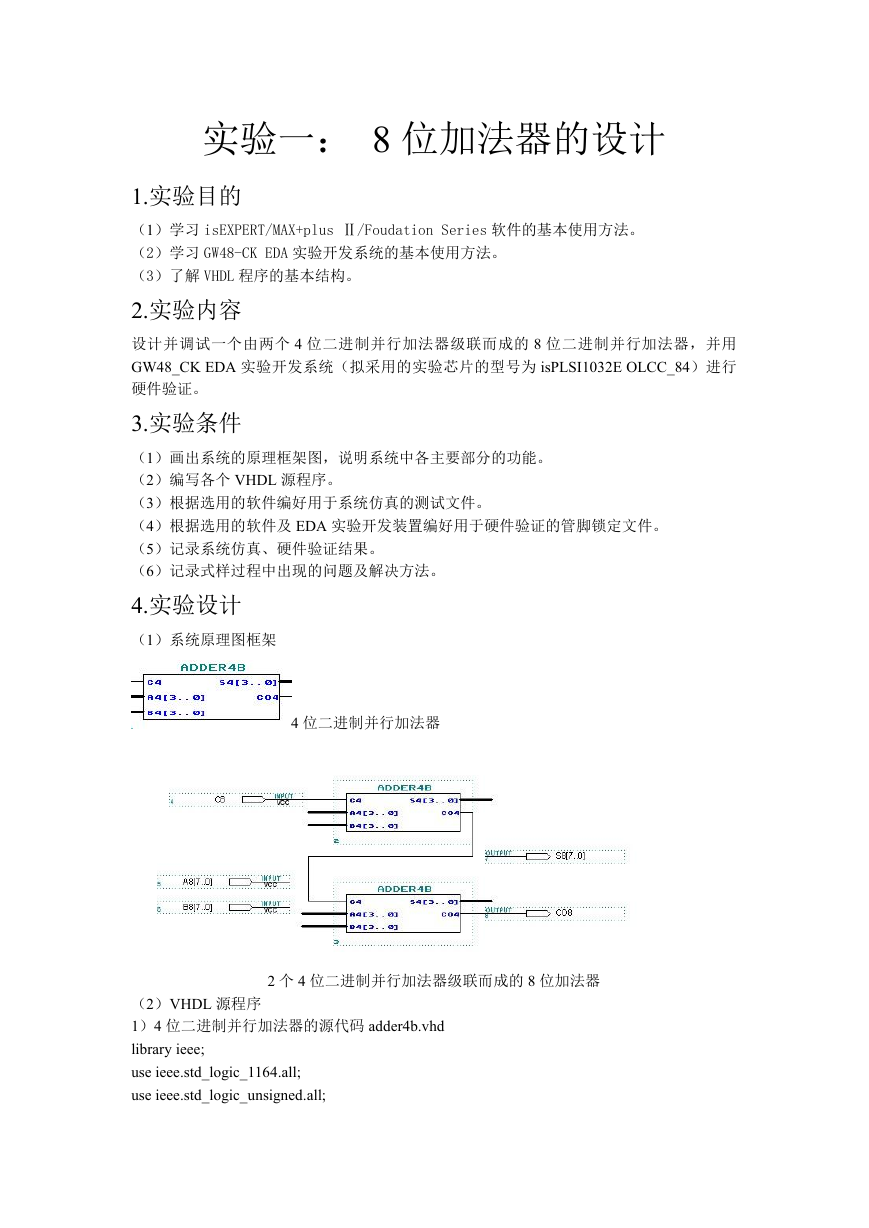

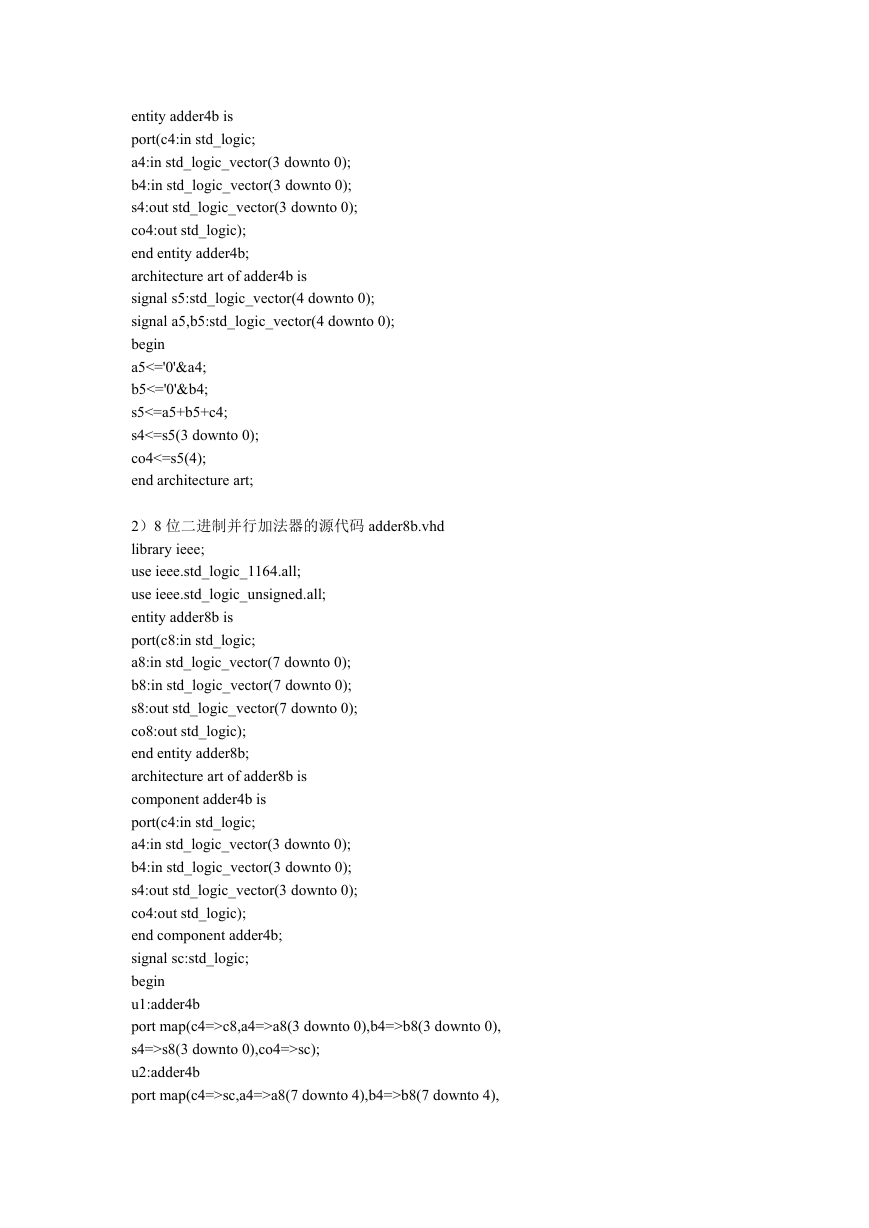

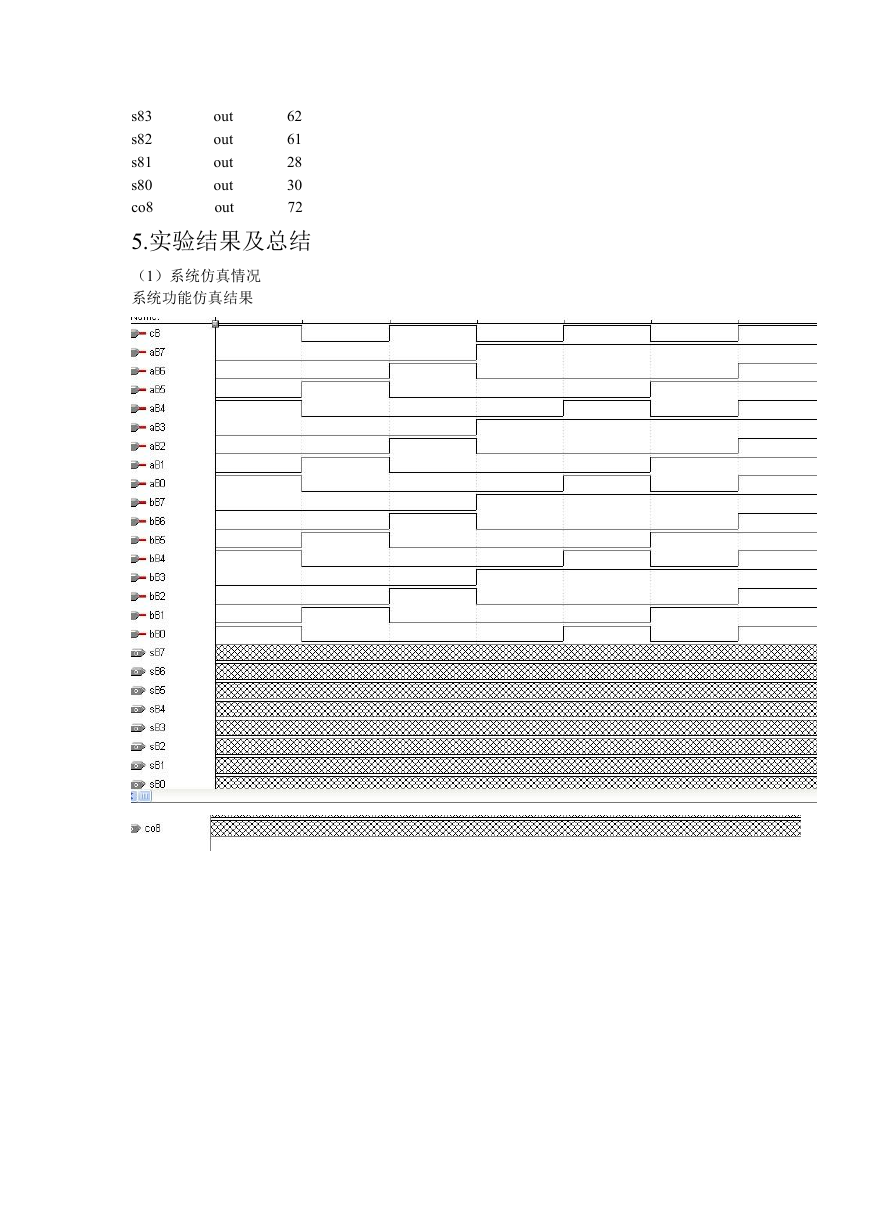

(1)系统原理图框架

4 位二进制并行加法器

2 个 4 位二进制并行加法器级联而成的 8 位加法器

(2)VHDL 源程序

1)4 位二进制并行加法器的源代码 adder4b.vhd

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

�

entity adder4b is

port(c4:in std_logic;

a4:in std_logic_vector(3 downto 0);

b4:in std_logic_vector(3 downto 0);

s4:out std_logic_vector(3 downto 0);

co4:out std_logic);

end entity adder4b;

architecture art of adder4b is

signal s5:std_logic_vector(4 downto 0);

signal a5,b5:std_logic_vector(4 downto 0);

begin

a5<='0'&a4;

b5<='0'&b4;

s5<=a5+b5+c4;

s4<=s5(3 downto 0);

co4<=s5(4);

end architecture art;

2)8 位二进制并行加法器的源代码 adder8b.vhd

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity adder8b is

port(c8:in std_logic;

a8:in std_logic_vector(7 downto 0);

b8:in std_logic_vector(7 downto 0);

s8:out std_logic_vector(7 downto 0);

co8:out std_logic);

end entity adder8b;

architecture art of adder8b is

component adder4b is

port(c4:in std_logic;

a4:in std_logic_vector(3 downto 0);

b4:in std_logic_vector(3 downto 0);

s4:out std_logic_vector(3 downto 0);

co4:out std_logic);

end component adder4b;

signal sc:std_logic;

begin

u1:adder4b

port map(c4=>c8,a4=>a8(3 downto 0),b4=>b8(3 downto 0),

s4=>s8(3 downto 0),co4=>sc);

u2:adder4b

port map(c4=>sc,a4=>a8(7 downto 4),b4=>b8(7 downto 4),

�

s4=>s8(7 downto 4),co4=>co8);

end architecture art;

(3)波形仿真文件

Module adder8b;

C8,a8[7..0],b8[7..0],s8[7..0],co8 pin;

Test_vectors

(C8,a8[7..0],b8[7..0]->s8[7..0],co8);

[0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,]->[x,x,x,x,x,x,x,x,x];

[1,0,0,0,1,0,0,0,1,0,0,0,1,0,0,0,1,]->[x,x,x,x,x,x,x,x,x];

[0,0,0,1,0,0,0,1,0,0,0,1,0,0,0,1,0,]->[x,x,x,x,x,x,x,x,x];

[1,0,0,1,1,0,0,1,1,0,0,1,1,0,0,1,1,]->[x,x,x,x,x,x,x,x,x];

[0,0,1,0,0,0,1,0,0,0,1,0,0,0,1,0,0,]->[x,x,x,x,x,x,x,x,x];

[1,0,1,0,1,0,1,0,1,0,1,0,1,0,1,0,1,]->[x,x,x,x,x,x,x,x,x];

[0,0,1,1,0,0,1,1,0,0,1,1,0,0,1,1,0,]->[x,x,x,x,x,x,x,x,x];

[1,0,1,1,1,0,1,1,1,0,1,1,1,0,1,1,1,]->[x,x,x,x,x,x,x,x,x];

[0,1,0,0,0,0,0,0,0,1,0,0,0,1,0,0,0,]->[x,x,x,x,x,x,x,x,x];

[1,1,0,0,1,1,0,0,1,1,0,0,1,1,0,0,1,]->[x,x,x,x,x,x,x,x,x];

[0,1,0,1,0,1,0,1,0,1,0,1,0,1,0,1,0,]->[x,x,x,x,x,x,x,x,x];

[1,1,0,1,1,1,0,1,1,1,0,1,1,1,0,1,1,]->[x,x,x,x,x,x,x,x,x];

[0,1,1,0,0,1,1,0,0,1,1,0,0,1,1,0,0,]->[x,x,x,x,x,x,x,x,x];

[1,1,1,0,1,1,1,0,1,1,1,0,1,1,1,0,1,]->[x,x,x,x,x,x,x,x,x];

[0,1,1,1,0,1,1,1,0,1,1,1,0,1,1,1,0,]->[x,x,x,x,x,x,x,x,x];

[1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,]->[x,x,x,x,x,x,x,x,x];

End;

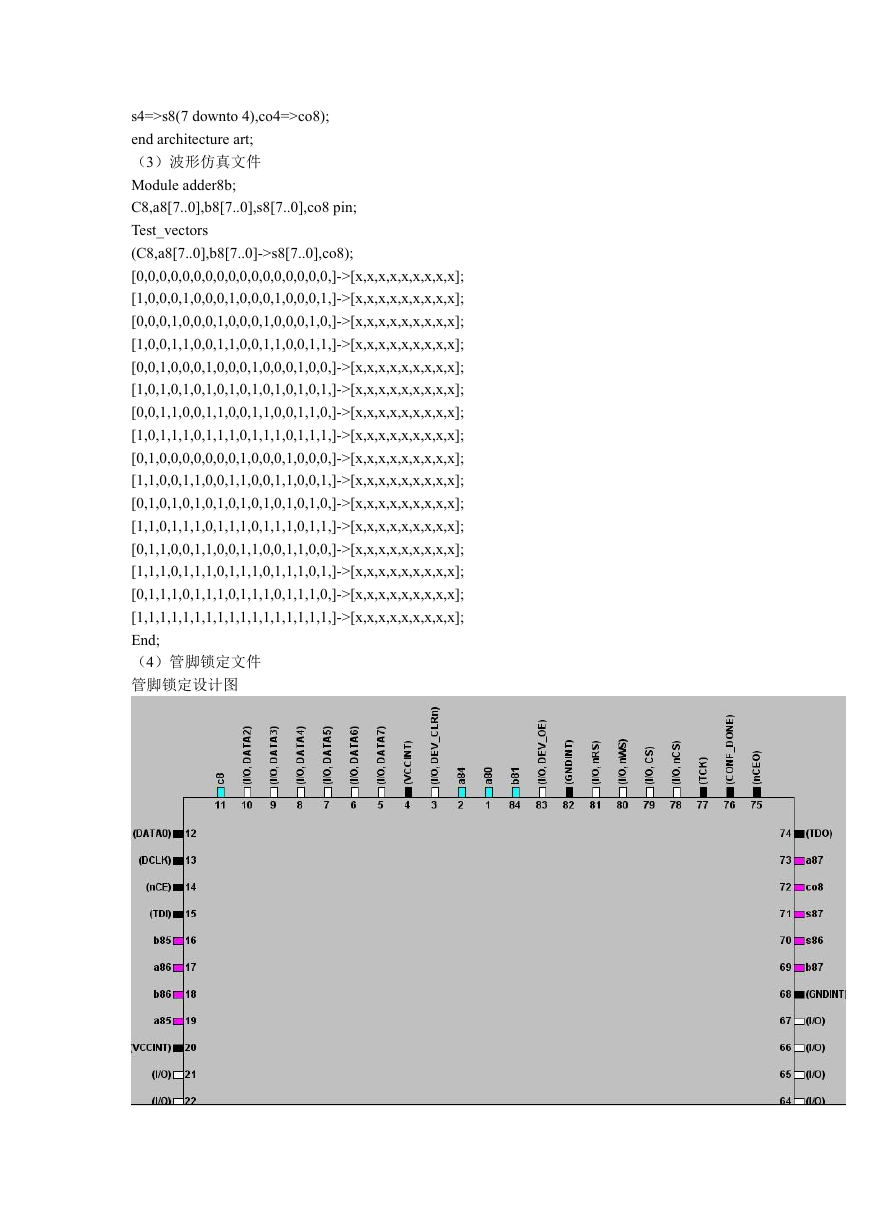

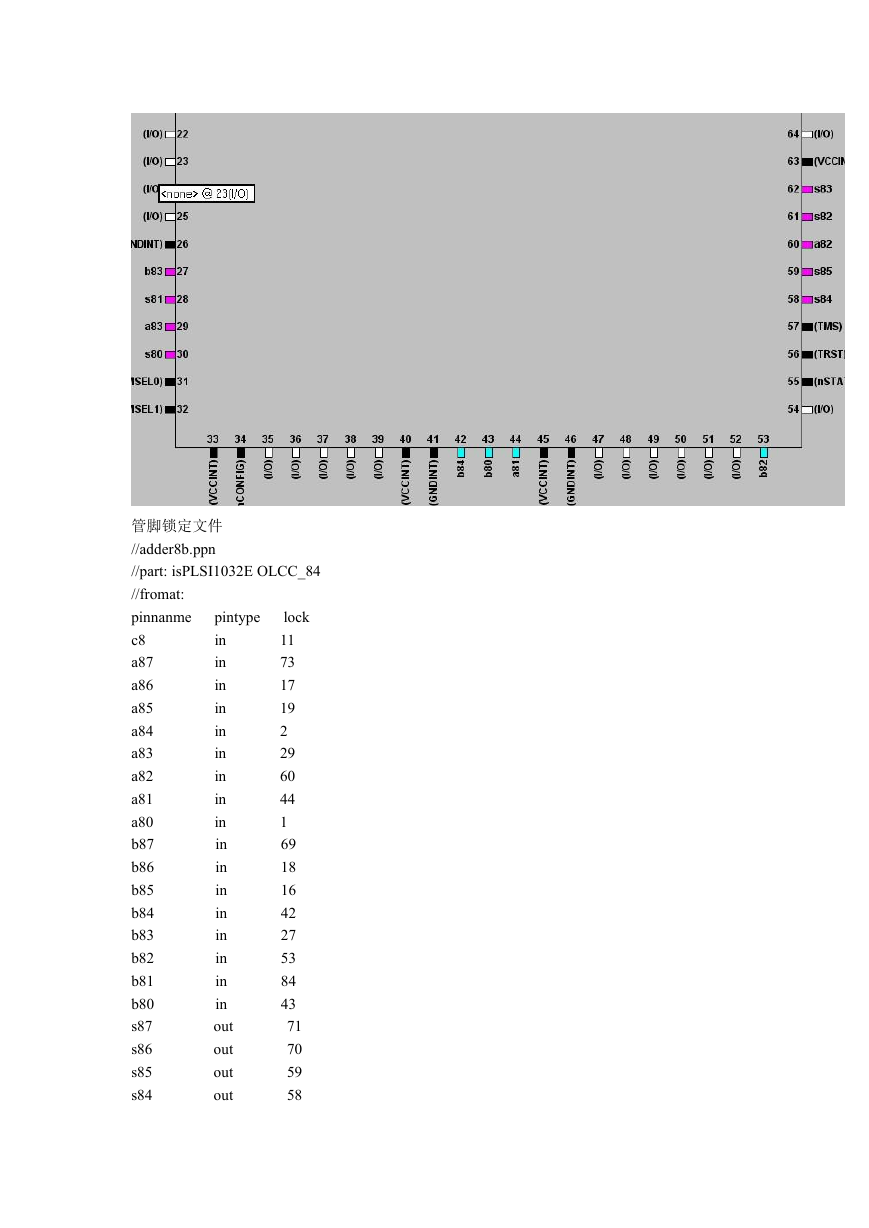

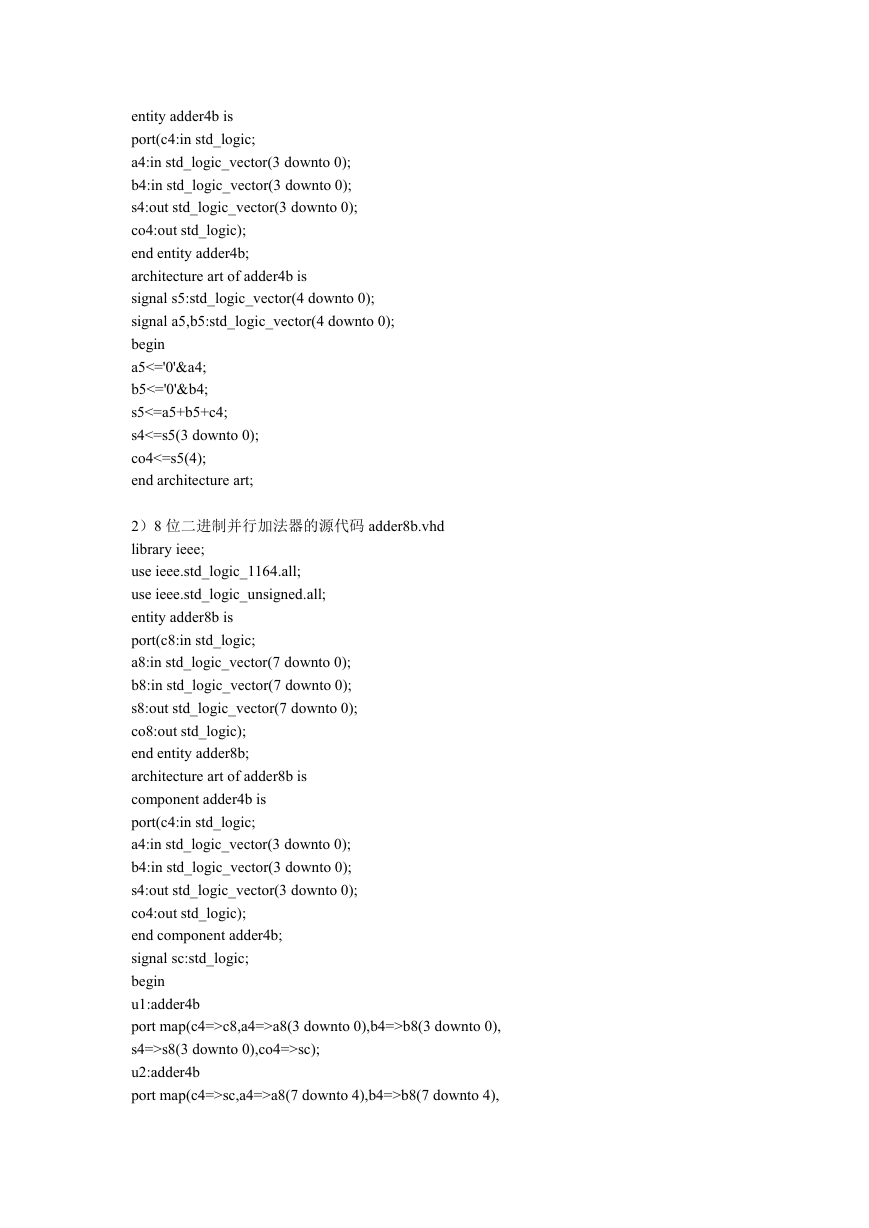

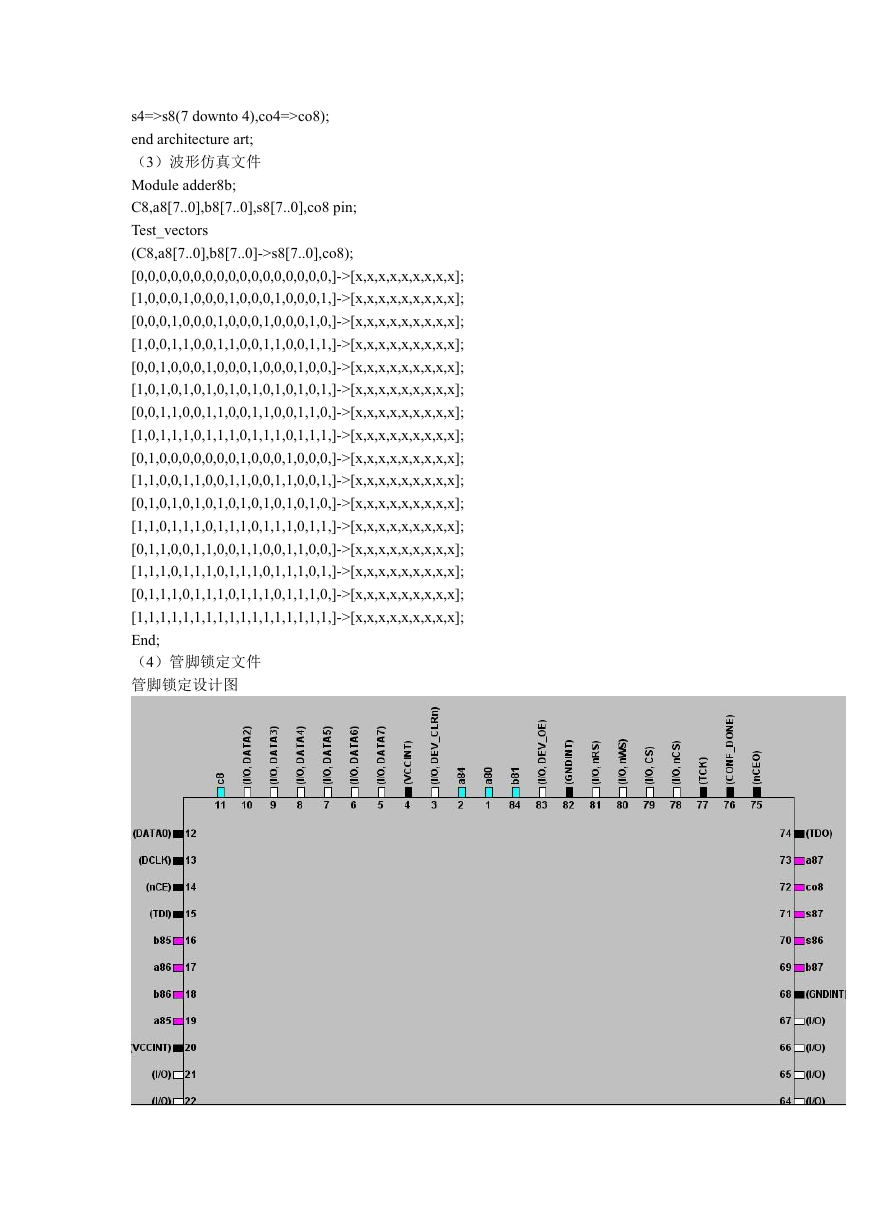

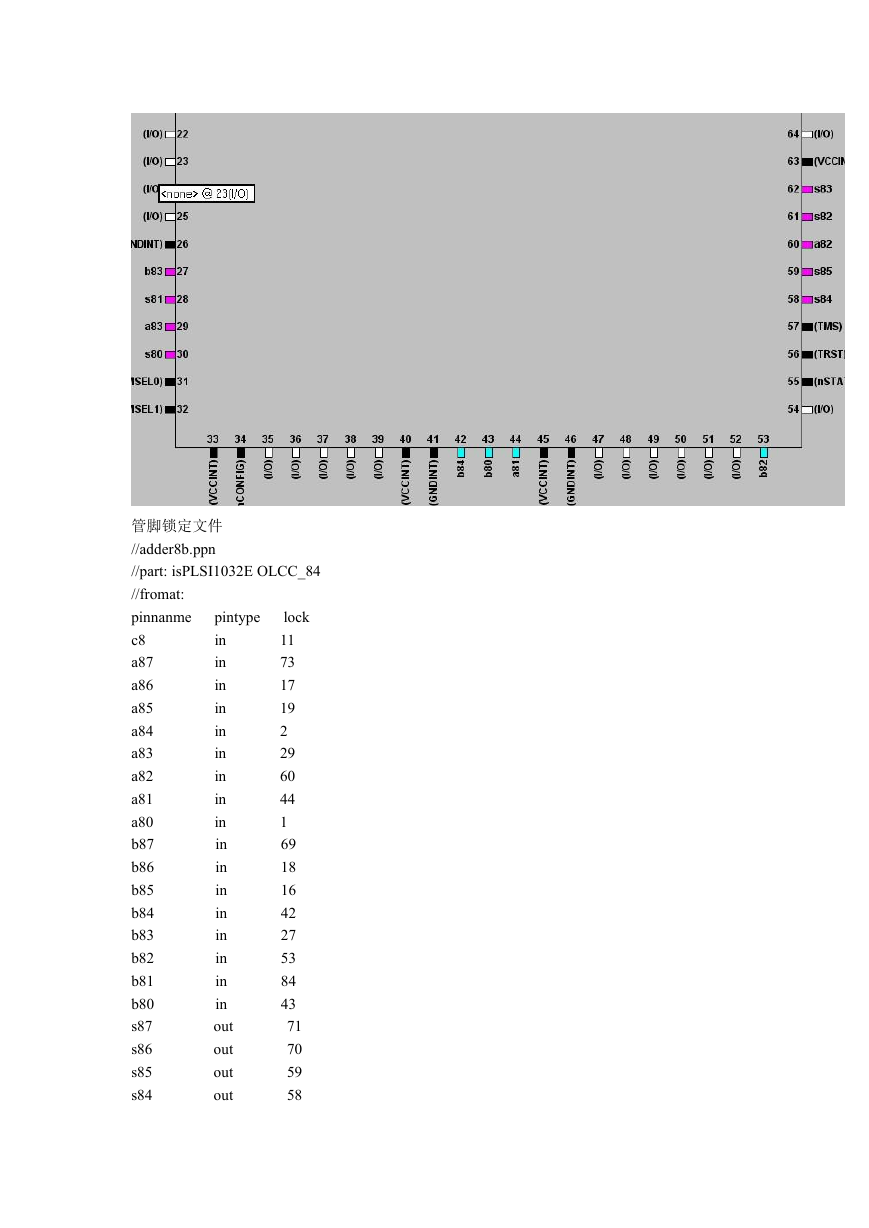

(4)管脚锁定文件

管脚锁定设计图

�

管脚锁定文件

//adder8b.ppn

//part: isPLSI1032E OLCC_84

//fromat:

pinnanme

c8

a87

a86

a85

a84

a83

a82

a81

a80

b87

b86

b85

b84

b83

b82

b81

b80

s87

s86

s85

s84

pintype

in

in

in

in

in

in

in

in

in

in

in

in

in

in

in

in

in

out

out

out

out

lock

11

73

17

19

2

29

60

44

1

69

18

16

42

27

53

84

43

71

70

59

58

�

out

out

out

out

out

s83

62

s82

61

s81

28

s80

30

co8

72

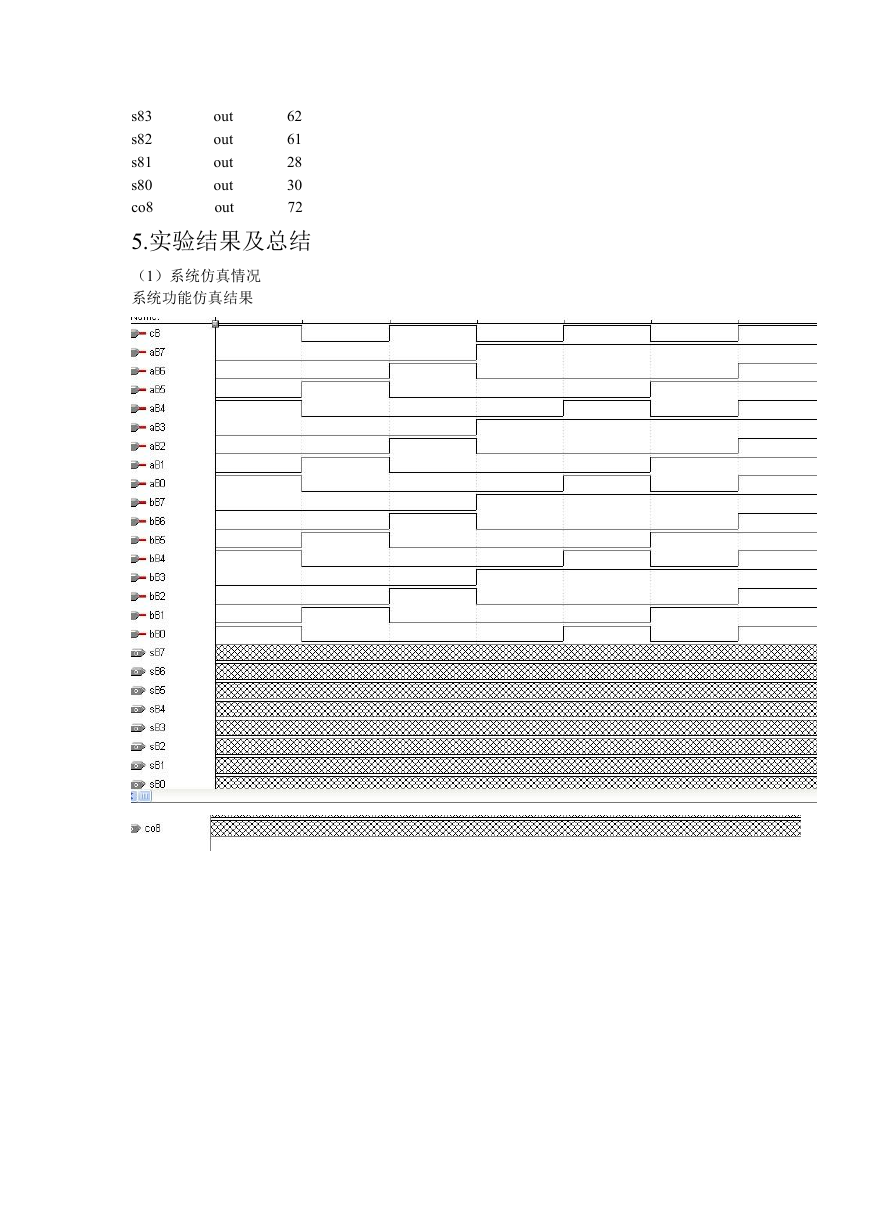

5.实验结果及总结

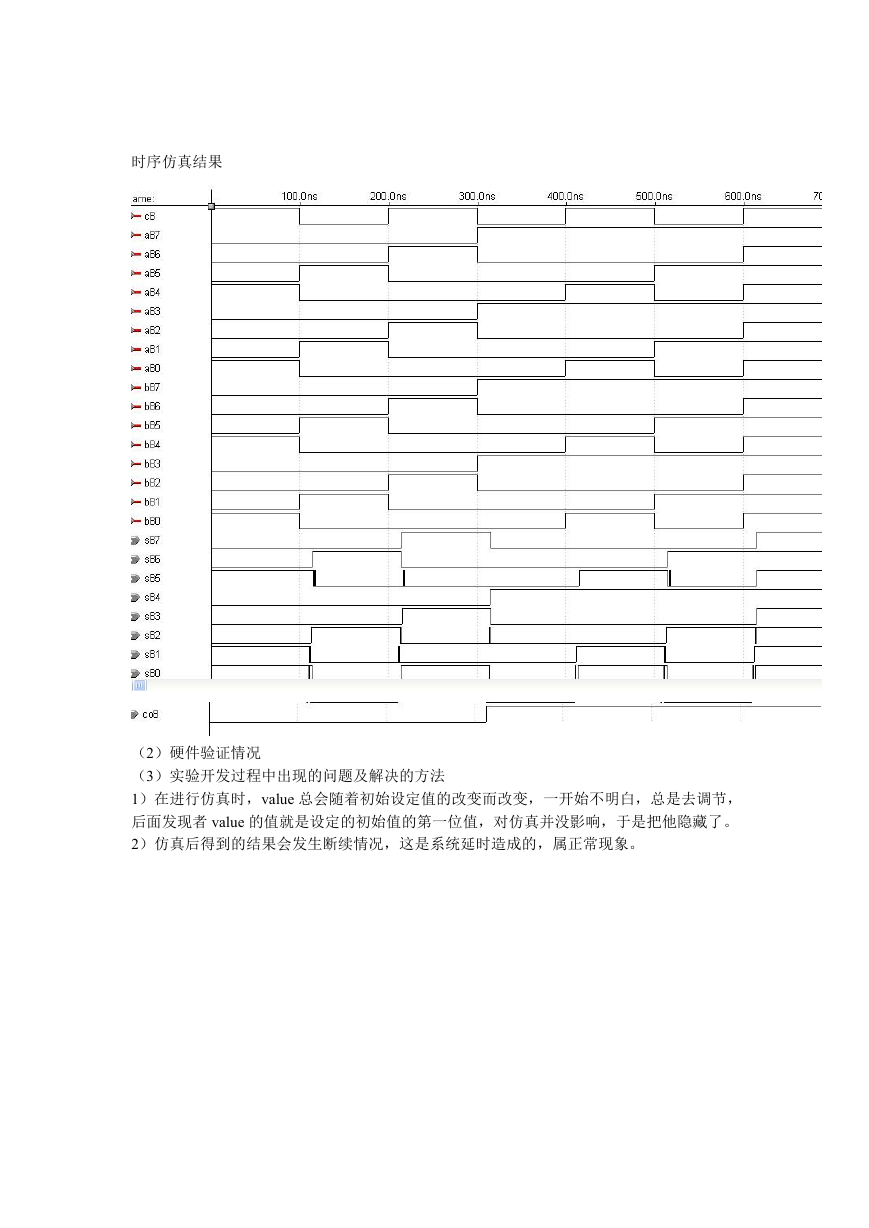

(1)系统仿真情况

系统功能仿真结果

�

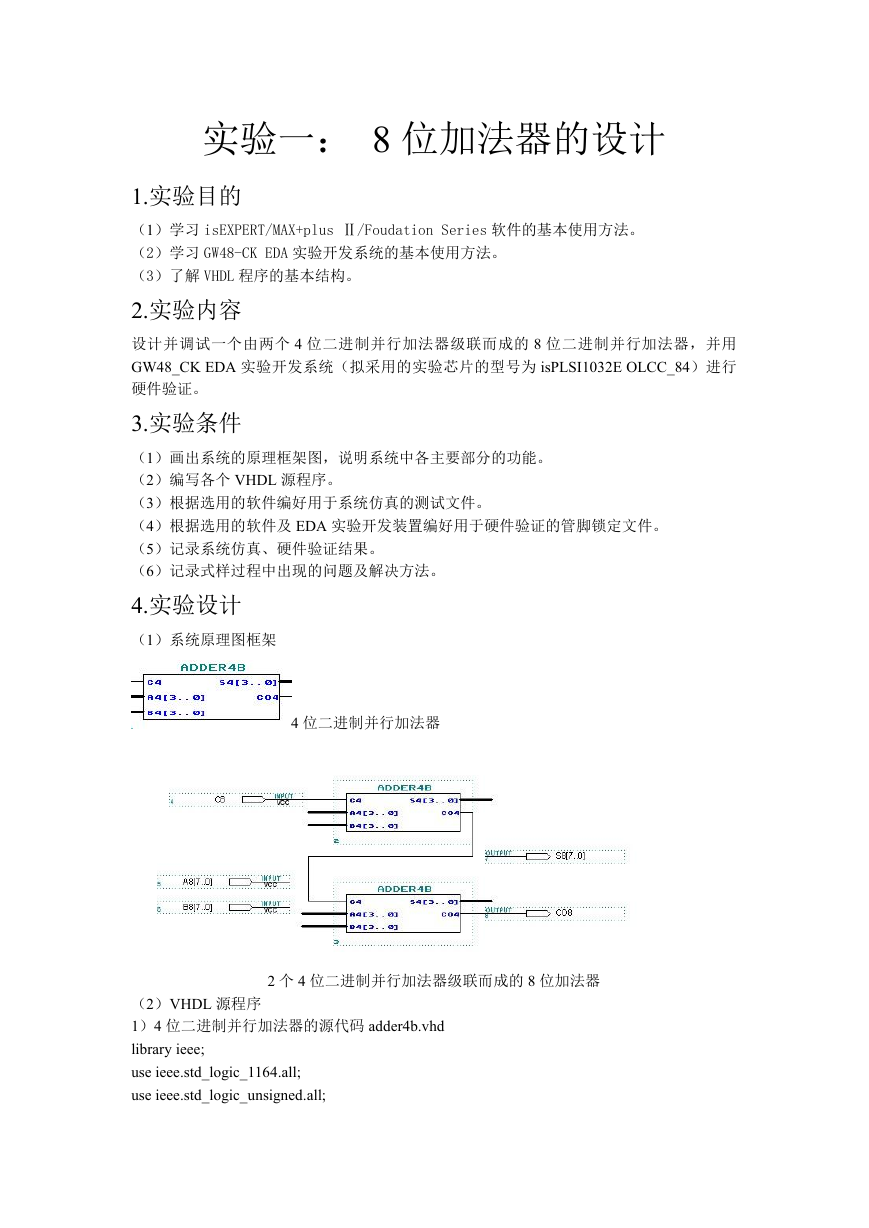

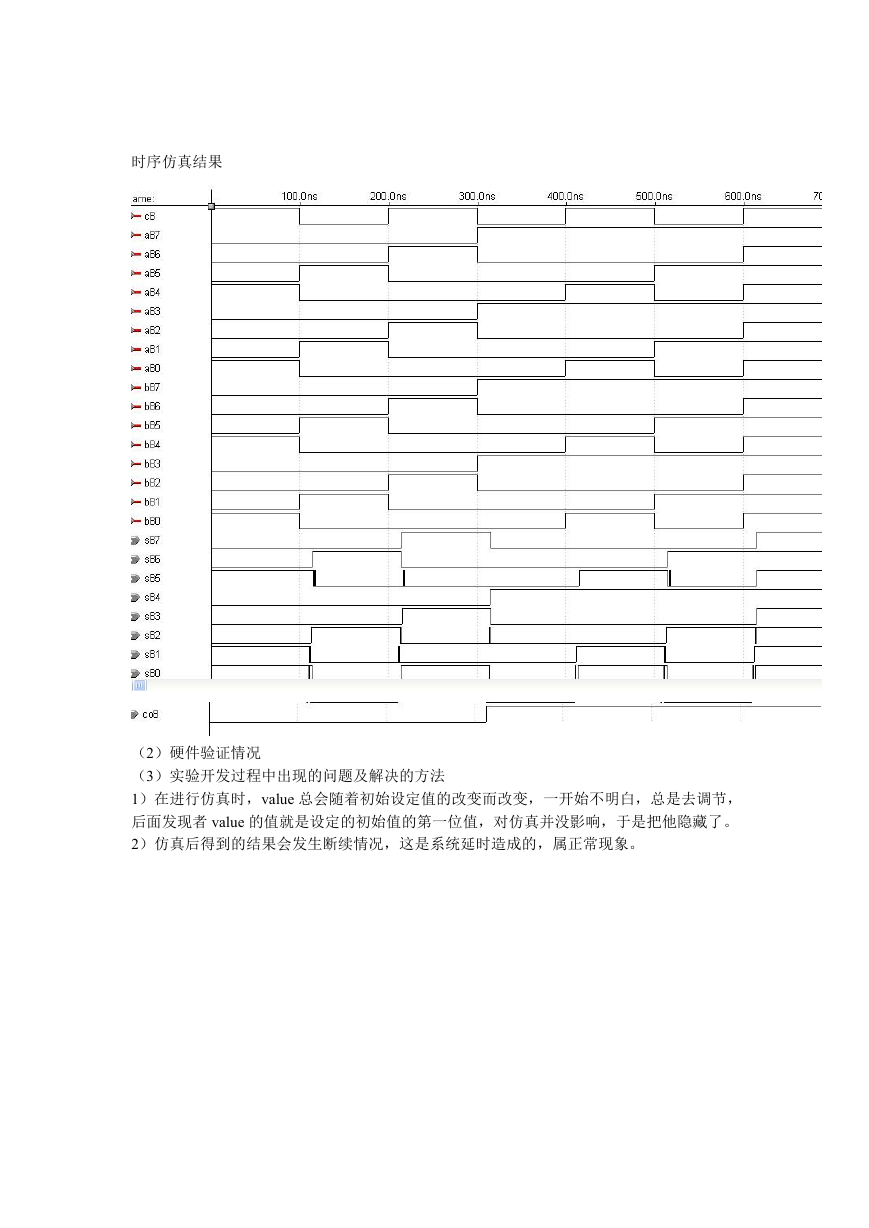

时序仿真结果

(2)硬件验证情况

(3)实验开发过程中出现的问题及解决的方法

1)在进行仿真时,value 总会随着初始设定值的改变而改变,一开始不明白,总是去调节,

后面发现者 value 的值就是设定的初始值的第一位值,对仿真并没影响,于是把他隐藏了。

2)仿真后得到的结果会发生断续情况,这是系统延时造成的,属正常现象。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc