CPCI 规范目录(中文)

1 概述 ...........................................................................................................................................................................- 1 -

1.1 CPCI 目标 .....................................................................................................................................................- 1 -

1.2 背景和术语 ...................................................................................................................................................- 1 -

1.3 预期读者 .......................................................................................................................................................- 1 -

1.4 CPCI 特性 .....................................................................................................................................................- 1 -

1.5 应用文献 .......................................................................................................................................................- 1 -

1.6 管理 ...............................................................................................................................................................- 1 -

1.7 名字和标志的用法 ...................................................................................................................................... - 1 -

2 特性设置 ...................................................................................................................................................................- 2 -

2.1 外形特征 .......................................................................................................................................................- 2 -

2.2 连接器 ...........................................................................................................................................................- 3 -

2.3 模块化 ...........................................................................................................................................................- 4 -

2.4 热插拔功能 ...................................................................................................................................................- 4 -

3 电气需求 ...................................................................................................................................................................- 4 -

3.1 适配器设计准则 .......................................................................................................................................... - 4 -

3.1.1 退耦需求 ............................................................................................................................................ - 4 -

3.1.2 CPCI 附加信号 ................................................................................................................................ - 5 -

3.1.3 CPCI 端接终端 ................................................................................................................................ - 5 -

3.1.4 外围适配器信号端接长度 ................................................................................................................ - 5 -

3.1.5 阻抗特性 ............................................................................................................................................ - 6 -

3.1.6 系统槽适配器信号端接长度 ............................................................................................................ - 6 -

3.1.7 外围适配器 PCI 时钟信号长度 ........................................................................................................- 6 -

3.1.8 上拉定位 ............................................................................................................................................ - 6 -

3.1.9 适配板连接器屏蔽需求 .................................................................................................................... - 7 -

3.2 背板设计准则 ...............................................................................................................................................- 7 -

阻抗特性 ...................................................................................................................................... - 7 -

3.2.1

3.2.2

8 插槽背板终端 ............................................................................................................................. - 7 -

3.2.3 信号环境 ........................................................................................................................................ - 8 -

IDSEL 板选信号分配 ....................................................................................................................- 8 -

3.2.4

3.2.5

REQ#/GNT#信号线分配 ...........................................................................................................- 8 -

PCI 中断绑定................................................................................................................................. - 9 -

3.2.6

3.2.7

CPCI 附加信号 ............................................................................................................................ - 10 -

3.2.8 电源分配 ........................................................................................................................................ - 12 -

3.2.9 电源去耦 ........................................................................................................................................ - 13 -

3.2.10 健全(Healthy#)....................................................................................................................- 13 -

33MHzPCI 时钟分配............................................................................................................................... - 13 -

3.3.1 背板时钟线路设计准则 .............................................................................................................. - 14 -

3.3.2 系统槽适配板时钟线路设计准则 ..............................................................................................- 14 -

64 位设计准则....................................................................................................................................... - 14 -

66MHz 电气需求 ..................................................................................................................................... - 15 -

66MHz 适配板设计准则.............................................................................................................- 15 -

66MHz 系统槽适配板设计准则 .................................................................................................- 16 -

66MHz 背板设计准则 .................................................................................................................- 16 -

66MHzPCI 时钟分配 ...................................................................................................................- 16 -

66MHz 系统槽适配板时钟线设计准则.....................................................................................- 16 -

3.5.1

3.5.2

3.5.3

3.5.4

3.5.5

3.3

3.4

3.5

I

�

3.5.6

4

66MHz 热插拔............................................................................................................................. - 17 -

3.6 系统和适配板接地 .................................................................................................................................. - 17 -

3.6.1 适配器前面板接地需求 ................................................................................................................ - 17 -

3.6.2 背板接地需求 ................................................................................................................................ - 17 -

CPCI 缓冲器模型..................................................................................................................................... - 17 -

3.7

机械需求 ...........................................................................................................................................................- 17 -

4.1 适配板需求............................................................................................................................................ - 17 -

3U 板卡 ...........................................................................................................................................- 18 -

4.1.1

6U 板卡 ...........................................................................................................................................- 18 -

4.1.2

4.1.3 后面板 I/O 板卡 .............................................................................................................................- 18 -

4.1.4 ESD 静电导出条............................................................................................................................- 18 -

4.1.5 ESD 接线柱....................................................................................................................................- 19 -

4.1.6 剖视图............................................................................................................................................ - 19 -

4.1.7 构件略图和翘曲(Component outline and warpage)................................................................- 19 -

4.1.8 焊料侧盖 ........................................................................................................................................ - 19 -

4.1.9 前面板............................................................................................................................................ - 28 -

4.1.10 系统槽识别.................................................................................................................................... - 28 -

4.2 后面板 I/O 适配器需求............................................................................................................................ - 28 -

4.2.1 机械部件 .......................................................................................................................................... - 28 -

4.2.2 电源 ...................................................................................................................................................- 31 -

4.2.3 后面板按键 ...................................................................................................................................... - 31 -

4.3 背板需求 .....................................................................................................................................................- 31 -

4.3.1 连接器位置 ...................................................................................................................................... - 31 -

4.3.2 槽间距 ...............................................................................................................................................- 31 -

4.3.3 插槽标号 .......................................................................................................................................... - 32 -

4.3.4 总线段 ...............................................................................................................................................- 32 -

4.3.5 背板尺寸 .......................................................................................................................................... - 32 -

5 连接器实现 .........................................................................................................................................................- 35 -

5.1 概述 .............................................................................................................................................................- 35 -

5.1.1 连接器位置 ................................................................................................................................ - 35 -

5.1.2 构架类型 ...................................................................................................................................... - 35 -

5.1.3 连接器末端长 .............................................................................................................................. - 36 -

5.1.4 背板/板卡可选数量 .................................................................................................................... - 36 -

J1(32 位 PCI 信号)............................................................................................................................. - 36 -

J2 连接器 ..................................................................................................................................................- 36 -

5.3.1 外围槽 64 位 PCI......................................................................................................................... - 36 -

5.3.2 外围槽后面 I/O........................................................................................................................... - 36 -

5.3.3 系统槽 64 位 PCI......................................................................................................................... - 36 -

5.3.4 系统槽后面 I/O........................................................................................................................... - 37 -

5.4 预留的通信引脚 ...................................................................................................................................... - 37 -

5.5 预留的非通信引脚 .................................................................................................................................. - 37 -

5.6 电源引脚 ...................................................................................................................................................- 37 -

5V/3.3V PCI 按键 ................................................................................................................................... - 37 -

5.7

5.8 引脚分配 .....................................................................................................................................................- 38 -

CPCI 手册的修订史 ...................................................................................................................................................- 42 -

附录 .............................................................................................................................................................................- 42 -

5.2

5.3

II

�

1 概述

1.1 CPCI 目标

CPCI 规范改进自 PCI 电气规范 2.1,应用于工业和嵌入式领域。它使用工业机械组装标准,

具有高性能连接技术,可以提供一套最优化系统以便于不同应用。CPCI 在电气方面可以兼容 PCI

规范,允许低成本 PCI 组件

CPCI 规范是 PICMG(PCI 工业计算机制造商联盟)开发并管理的一套开放式规范。PICMG

是一个在嵌入式领域使用 PCI 协议的公司联盟。

1.2 背景和术语

欧式卡

1.3 预期读者

1.4 CPCI 特性

1.5 应用文献

1.6 管理

1.7 名字和标志的用法

PCI 工业计算机制造商联盟允许以下情况使用商标:PICMG,Compact PCI 以及 PICMG,

Compact PCI 标识。

任何公司都可以要求同 PICMG 兼容,不论是否是 PICMG 中的成员。

仅有那些在最新的成员权利文档中规定的近期已经交纳了会费的特指成员,自动拥有使用

PICMG 和 Compact PCI 标识的权利。

会员发言人和销售代表可以使用 PICMG 和 Compact PCI 标识来促进会员产品的销售。

PICMG 和 Compact PCI 标识将以黑白插图或彩色插图的形式打印在标识页。包含“PICMG”

或“Compact PCI” 短语的中心栏必须水平设置且保持其纵横比不变,但是它的大小可以改变。

PICMG 和 Compact PCI 标识中不能添加或删除任何一点。

因为 PICMG、Compact PCI 标识和 PICMG、Compact PCI 称谓是 PICMG 联盟的注册商标,

接下来的声明将被包含在所有的著作和广告素材中。

- 1 -

�

2 特性设置

2.1 外形特征

CPCI 板的封装结构基于 IEC 60297-3、IEC 60297-4 以及 IEEE 1101.10 定义的欧式板卡外形。

共定义了 3U(100 mm × 160 mm)和 6U(233.35 mm × 160 mm)两种板卡尺寸。

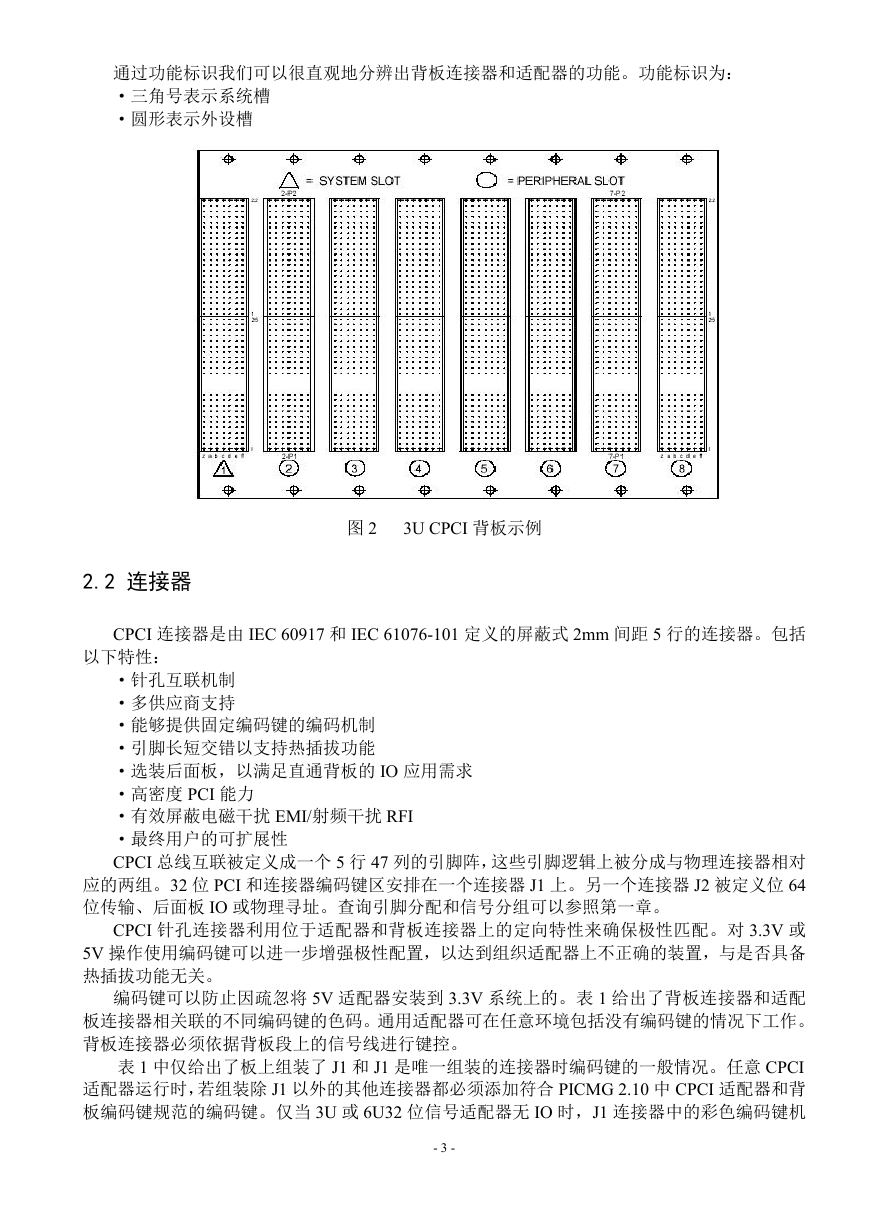

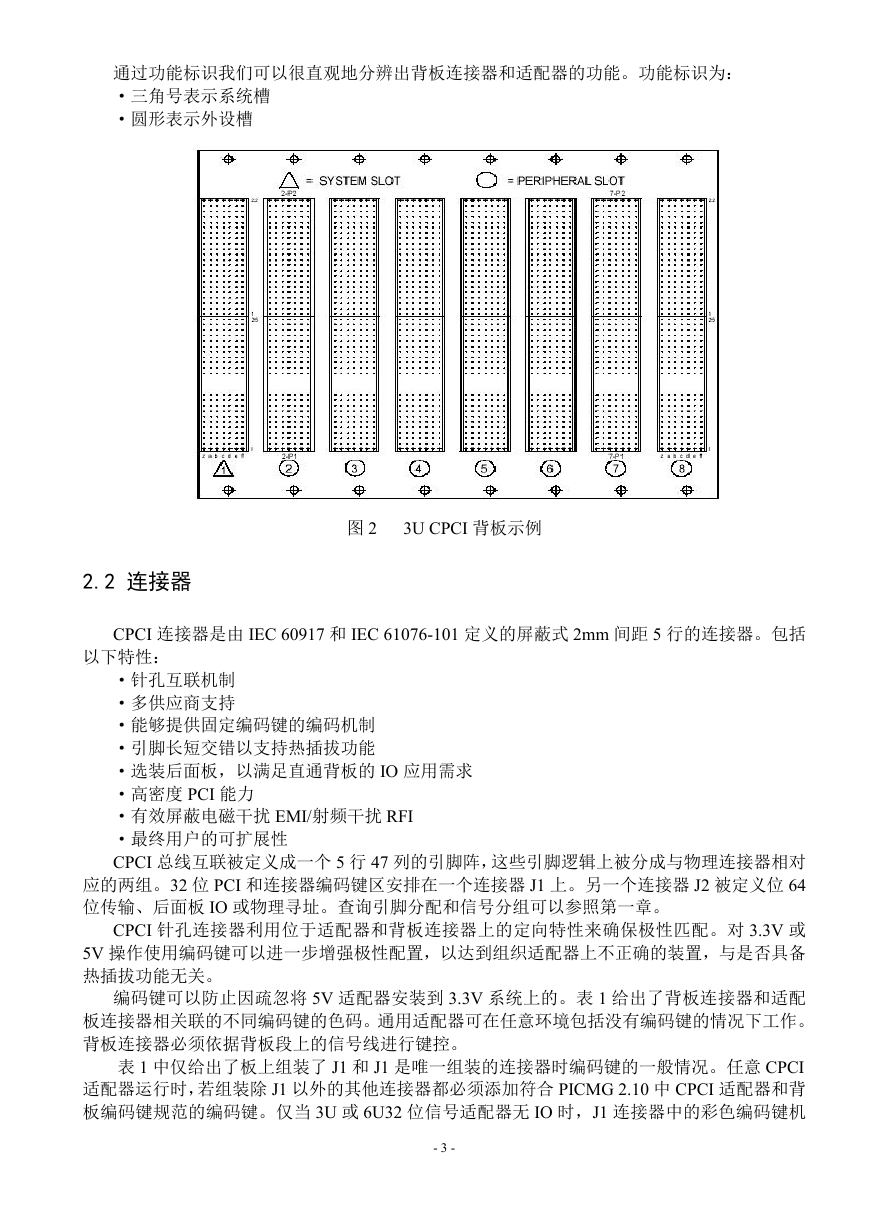

图 1 展示了一个 3U 型板卡

图 1

3U 64-bit CPCI 外形尺寸图

一个 CPCI 系统由一个或多个 CPCI 总线段组成。每个总线段又由 8 个 CPCI 插槽组成

(33MHZ 情况),板中心间距 20.32mm(0.8 inch)。每个 CPCI 总线段包括一个系统槽和最多 7

个外围设备槽。

系统槽为总线段上的所有适配器提供仲裁、时钟分配以及复位功能。系统槽通过管理每个局

部适配器上的 IDSEL 板选信号完成系统初始化。实际上,系统槽可以被固定在背板上的任意位

置。为了简单起见,本技术规范假定每个 CPCI 总线段上的系统槽都定位于总线段的最左端,当

我们从背板的前方看过去时。

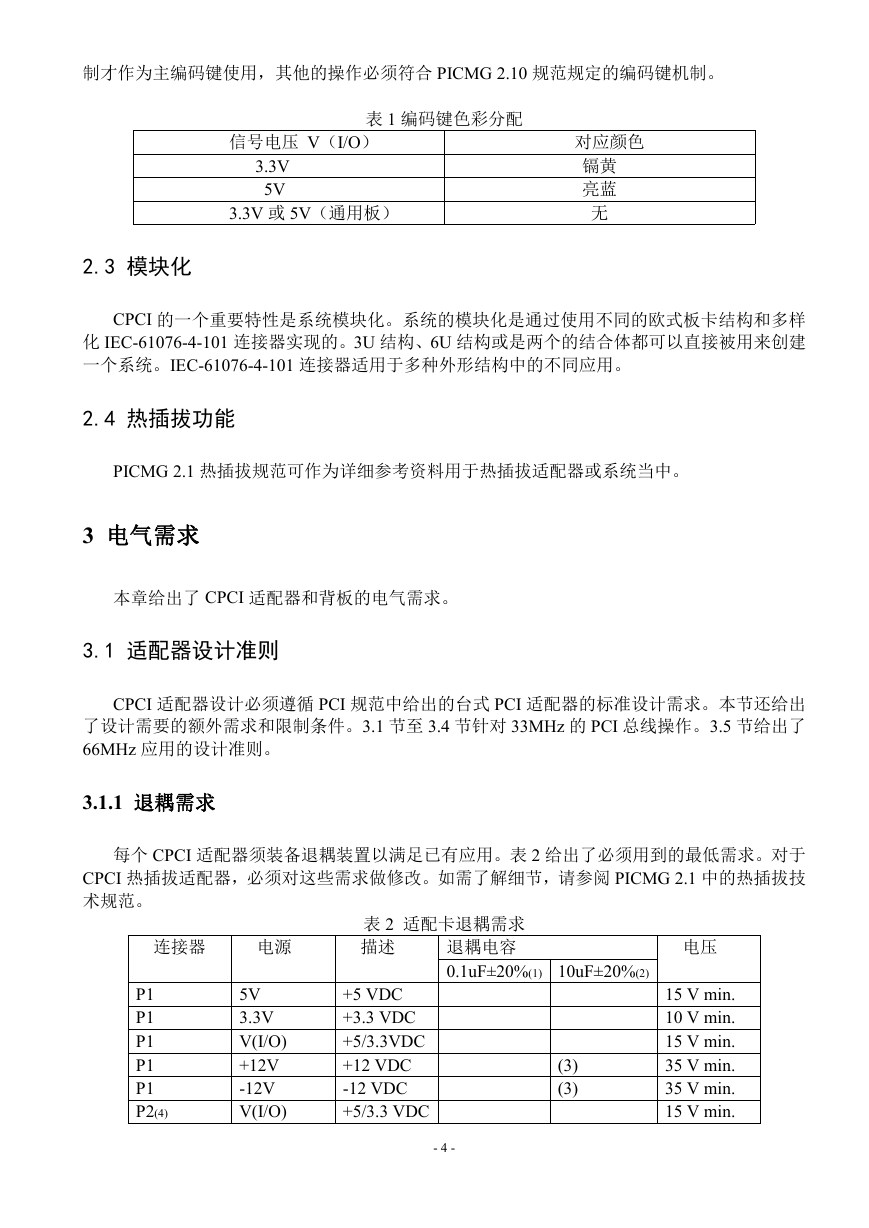

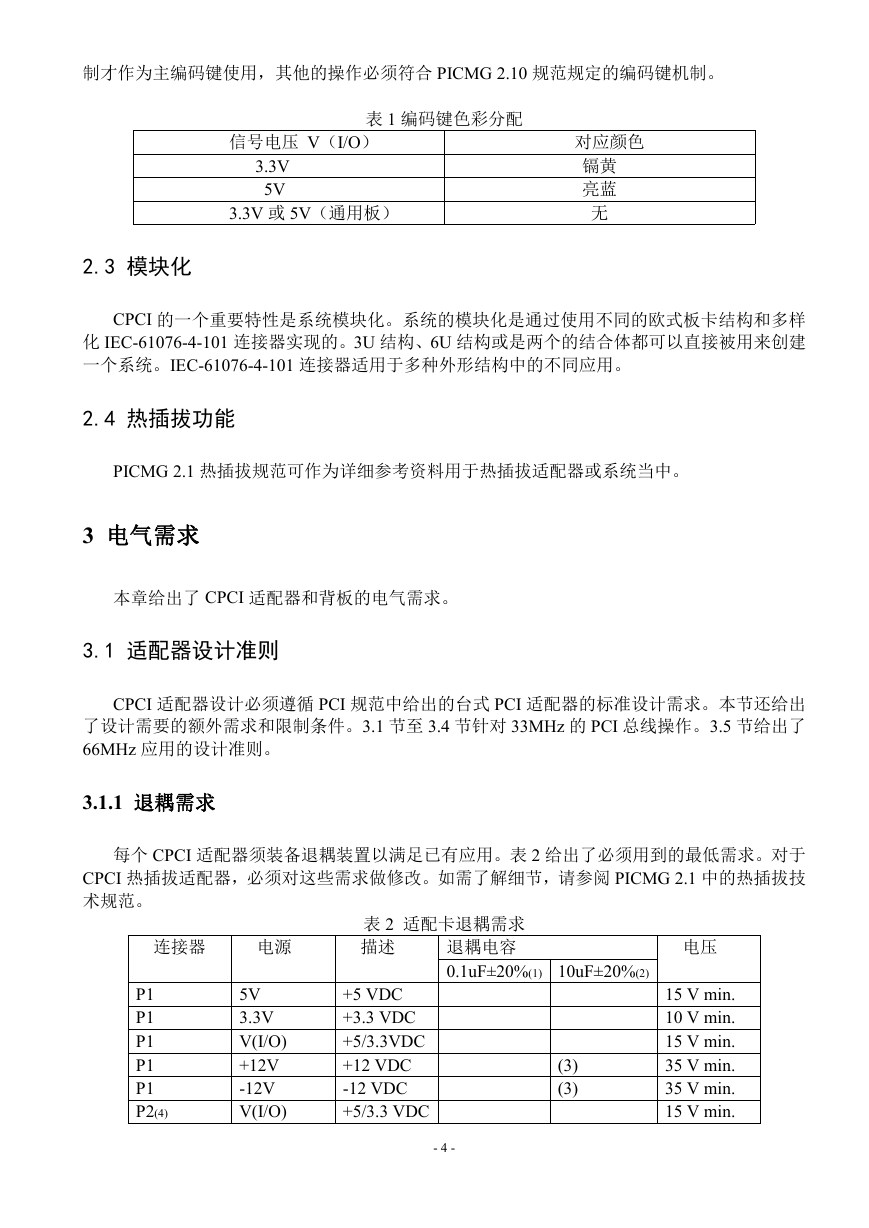

外围槽可安装简单适配器也可以安装智能化从设备或 PCI 总线主适配卡。图 2 给出了前端看

过去的一个典型的 3UCPCI 总线段。除了图 2 给出的线性排列以外 CPCI 规范还允许其他形式的

拓扑结构。然而,此规范和所有的背板模拟都采用系统槽位于总线段左边或右边、板间距为

20.32mm(0.8inch)的线性排列结构。别的拓扑结构必须通过模拟或其他方法验证能够兼容 PCI

规范后才能使用。

CPCI 基于物理槽和逻辑槽的概念定义插槽编号。物理槽必须从机箱最左端开始编号,编号

从 1 开始。。CPCI 系统必须在相互兼容的前提下标识每个物理槽。图 2 给出了兼容背景下编号

物理槽的示例。

逻辑槽号的定义是通过 IDSEL 板选信号和关联地址来选择的。使用逻辑号来定义总线段上

连接器的物理特征。图 2 中,逻辑号位于连接器的下方。逻辑槽号和物理槽号并不是总保持一

致。

- 2 -

�

通过功能标识我们可以很直观地分辨出背板连接器和适配器的功能。功能标识为:

·三角号表示系统槽

·圆形表示外设槽

图 2

3U CPCI 背板示例

2.2 连接器

CPCI 连接器是由 IEC 60917 和 IEC 61076-101 定义的屏蔽式 2mm 间距 5 行的连接器。包括

以下特性:

·针孔互联机制

·多供应商支持

·能够提供固定编码键的编码机制

·引脚长短交错以支持热插拔功能

·选装后面板,以满足直通背板的 IO 应用需求

·高密度 PCI 能力

·有效屏蔽电磁干扰 EMI/射频干扰 RFI

·最终用户的可扩展性

CPCI 总线互联被定义成一个 5 行 47 列的引脚阵,这些引脚逻辑上被分成与物理连接器相对

应的两组。32 位 PCI 和连接器编码键区安排在一个连接器 J1 上。另一个连接器 J2 被定义位 64

位传输、后面板 IO 或物理寻址。查询引脚分配和信号分组可以参照第一章。

CPCI 针孔连接器利用位于适配器和背板连接器上的定向特性来确保极性匹配。对 3.3V 或

5V 操作使用编码键可以进一步增强极性配置,以达到组织适配器上不正确的装置,与是否具备

热插拔功能无关。

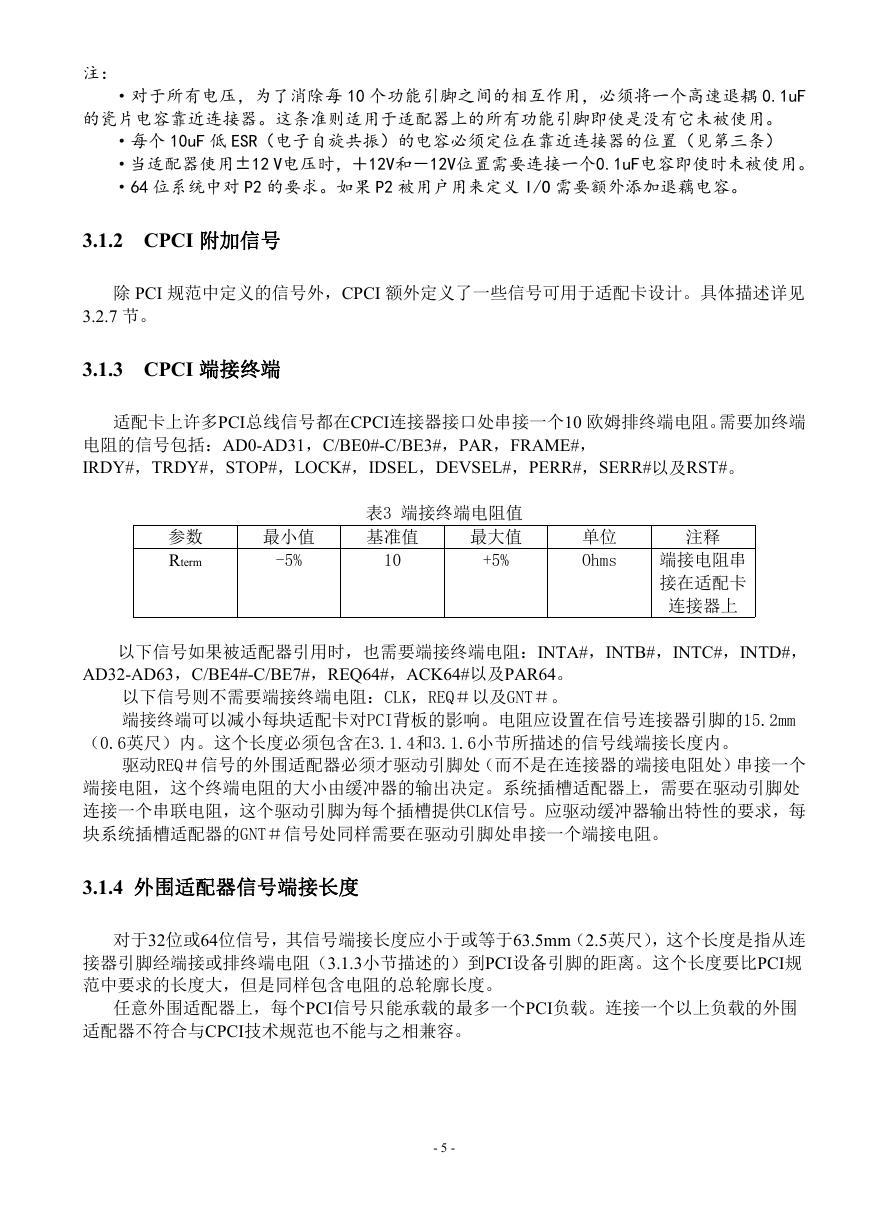

编码键可以防止因疏忽将 5V 适配器安装到 3.3V 系统上的。表 1 给出了背板连接器和适配

板连接器相关联的不同编码键的色码。通用适配器可在任意环境包括没有编码键的情况下工作。

背板连接器必须依据背板段上的信号线进行键控。

表 1 中仅给出了板上组装了 J1 和 J1 是唯一组装的连接器时编码键的一般情况。任意 CPCI

适配器运行时,若组装除 J1 以外的其他连接器都必须添加符合 PICMG 2.10 中 CPCI 适配器和背

板编码键规范的编码键。仅当 3U 或 6U32 位信号适配器无 IO 时,J1 连接器中的彩色编码键机

- 3 -

�

制才作为主编码键使用,其他的操作必须符合 PICMG 2.10 规范规定的编码键机制。

表 1 编码键色彩分配

信号电压 V(I/O)

3.3V

5V

3.3V 或 5V(通用板)

2.3 模块化

对应颜色

镉黄

亮蓝

无

CPCI 的一个重要特性是系统模块化。系统的模块化是通过使用不同的欧式板卡结构和多样

化 IEC-61076-4-101 连接器实现的。3U 结构、6U 结构或是两个的结合体都可以直接被用来创建

一个系统。IEC-61076-4-101 连接器适用于多种外形结构中的不同应用。

2.4 热插拔功能

PICMG 2.1 热插拔规范可作为详细参考资料用于热插拔适配器或系统当中。

3 电气需求

本章给出了 CPCI 适配器和背板的电气需求。

3.1 适配器设计准则

CPCI 适配器设计必须遵循 PCI 规范中给出的台式 PCI 适配器的标准设计需求。本节还给出

了设计需要的额外需求和限制条件。3.1 节至 3.4 节针对 33MHz 的 PCI 总线操作。3.5 节给出了

66MHz 应用的设计准则。

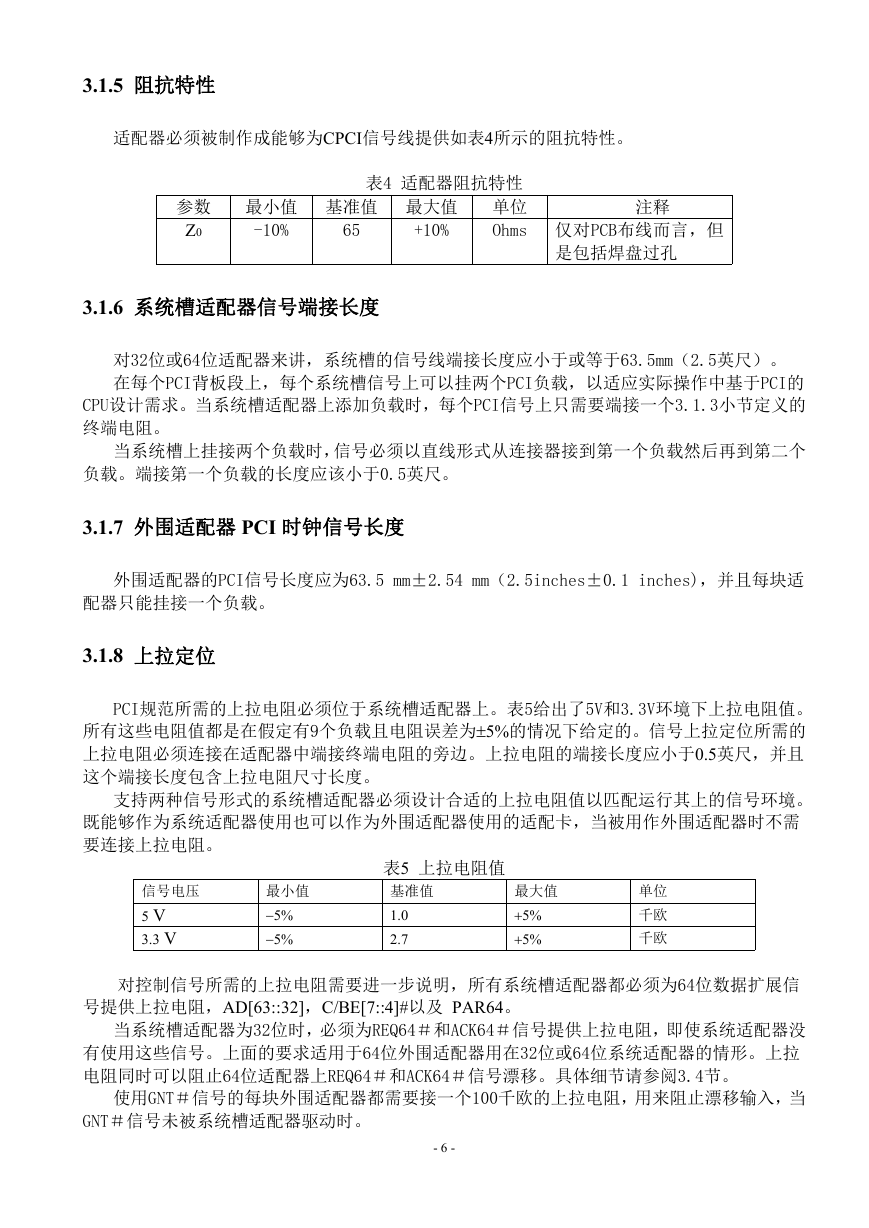

3.1.1 退耦需求

每个 CPCI 适配器须装备退耦装置以满足已有应用。表 2 给出了必须用到的最低需求。对于

CPCI 热插拔适配器,必须对这些需求做修改。如需了解细节,请参阅 PICMG 2.1 中的热插拔技

术规范。

表 2 适配卡退耦需求

退耦电容

描述

0.1uF±20%(1) 10uF±20%(2)

电压

15 V min.

10 V min.

15 V min.

35 V min.

35 V min.

15 V min.

连接器

电源

P1

P1

P1

P1

P1

P2(4)

5V

3.3V

V(I/O)

+12V

-12V

V(I/O)

+5 VDC

+3.3 VDC

+5/3.3VDC

+12 VDC

-12 VDC

+5/3.3 VDC

(3)

(3)

- 4 -

�

注:

·对于所有电压,为了消除每 10 个功能引脚之间的相互作用,必须将一个高速退耦 0.1uF

的瓷片电容靠近连接器。这条准则适用于适配器上的所有功能引脚即使是没有它未被使用。

·每个 10uF 低 ESR(电子自旋共振)的电容必须定位在靠近连接器的位置(见第三条)

·当适配器使用±12 V电压时,+12V和-12V位置需要连接一个0.1uF电容即使时未被使用。

·64 位系统中对 P2 的要求。如果 P2 被用户用来定义 I/O 需要额外添加退藕电容。

3.1.2 CPCI 附加信号

除 PCI 规范中定义的信号外,CPCI 额外定义了一些信号可用于适配卡设计。具体描述详见

3.2.7 节。

3.1.3 CPCI 端接终端

适配卡上许多PCI总线信号都在CPCI连接器接口处串接一个10欧姆排终端电阻。需要加终端

电阻的信号包括:AD0-AD31,C/BE0#-C/BE3#,PAR,FRAME#,

IRDY#,TRDY#,STOP#,LOCK#,IDSEL,DEVSEL#,PERR#,SERR#以及RST#。

参数

Rterm

最小值

-5%

表3 端接终端电阻值

基准值

最大值

10

+5%

单位

Ohms

注释

端接电阻串

接在适配卡

连接器上

以下信号如果被适配器引用时,也需要端接终端电阻:INTA#,INTB#,INTC#,INTD#,

AD32-AD63,C/BE4#-C/BE7#,REQ64#,ACK64#以及PAR64。

以下信号则不需要端接终端电阻:CLK,REQ#以及GNT#。

端接终端可以减小每块适配卡对PCI背板的影响。电阻应设置在信号连接器引脚的15.2mm

(0.6英尺)内。这个长度必须包含在3.1.4和3.1.6小节所描述的信号线端接长度内。

驱动REQ#信号的外围适配器必须才驱动引脚处(而不是在连接器的端接电阻处)串接一个

端接电阻,这个终端电阻的大小由缓冲器的输出决定。系统插槽适配器上,需要在驱动引脚处

连接一个串联电阻,这个驱动引脚为每个插槽提供CLK信号。应驱动缓冲器输出特性的要求,每

块系统插槽适配器的GNT#信号处同样需要在驱动引脚处串接一个端接电阻。

3.1.4 外围适配器信号端接长度

对于32位或64位信号,其信号端接长度应小于或等于63.5mm(2.5英尺),这个长度是指从连

接器引脚经端接或排终端电阻(3.1.3小节描述的)到PCI设备引脚的距离。这个长度要比PCI规

范中要求的长度大,但是同样包含电阻的总轮廓长度。

任意外围适配器上,每个PCI信号只能承载的最多一个PCI负载。连接一个以上负载的外围

适配器不符合与CPCI技术规范也不能与之相兼容。

- 5 -

�

3.1.5 阻抗特性

适配器必须被制作成能够为CPCI信号线提供如表4所示的阻抗特性。

表4 适配器阻抗特性

参数 最小值 基准值 最大值 单位

Z0

-10%

65

+10%

Ohms 仅对PCB布线而言,但

注释

是包括焊盘过孔

3.1.6 系统槽适配器信号端接长度

对32位或64位适配器来讲,系统槽的信号线端接长度应小于或等于63.5mm(2.5英尺)。

在每个PCI背板段上,每个系统槽信号上可以挂两个PCI负载,以适应实际操作中基于PCI的

CPU设计需求。当系统槽适配器上添加负载时,每个PCI信号上只需要端接一个3.1.3小节定义的

终端电阻。

当系统槽上挂接两个负载时,信号必须以直线形式从连接器接到第一个负载然后再到第二个

负载。端接第一个负载的长度应该小于0.5英尺。

3.1.7 外围适配器 PCI 时钟信号长度

外围适配器的PCI信号长度应为63.5 mm±2.54 mm(2.5inches±0.1 inches),并且每块适

配器只能挂接一个负载。

3.1.8 上拉定位

PCI规范所需的上拉电阻必须位于系统槽适配器上。表5给出了5V和3.3V环境下上拉电阻值。

所有这些电阻值都是在假定有9个负载且电阻误差为5%的情况下给定的。信号上拉定位所需的

上拉电阻必须连接在适配器中端接终端电阻的旁边。上拉电阻的端接长度应小于0.5英尺,并且

这个端接长度包含上拉电阻尺寸长度。

支持两种信号形式的系统槽适配器必须设计合适的上拉电阻值以匹配运行其上的信号环境。

既能够作为系统适配器使用也可以作为外围适配器使用的适配卡,当被用作外围适配器时不需

要连接上拉电阻。

信号电压

V

V

最小值

表5 上拉电阻值

基准值

最大值

单位

千欧

千欧

对控制信号所需的上拉电阻需要进一步说明,所有系统槽适配器都必须为64位数据扩展信

号提供上拉电阻,AD[63::32],C/BE[7::4]#以及 PAR64。

当系统槽适配器为32位时,必须为REQ64#和ACK64#信号提供上拉电阻,即使系统适配器没

有使用这些信号。上面的要求适用于64位外围适配器用在32位或64位系统适配器的情形。上拉

电阻同时可以阻止64位适配器上REQ64#和ACK64#信号漂移。具体细节请参阅3.4节。

使用GNT#信号的每块外围适配器都需要接一个100千欧的上拉电阻,用来阻止漂移输入,当

GNT#信号未被系统槽适配器驱动时。

- 6 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc