�

The Verilog® Hardware Description Language,

Fifth Edition

This page intentionally left blank

�

The Verilog® Hardware Description Language,

Fifth Edition

Donald E. Thomas

ECE Department

Carnegie Mellon University

Pittsburgh, PA

Philip R. Moorby

Co-design Automation, Inc.

www.co-design.com

Verilog® is a registered trade mark of Cadence Design Systems, Inc.

�

eBook ISBN: 0-306-47666-5

1-4020-7089-6

Print ISBN:

©2002 Kluwer Academic Publishers

New York, Boston, Dordrecht, London, Moscow

Print ©2002 Kluwer Academic Publishers

Dordrecht

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic,

mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Kluwer Online at:

and Kluwer's eBookstore at:

http://kluweronline.com

http://ebooks.kluweronline.com

�

To Sandie,

and John and Holland,

and Jill.

�

This page intentionally left blank

�

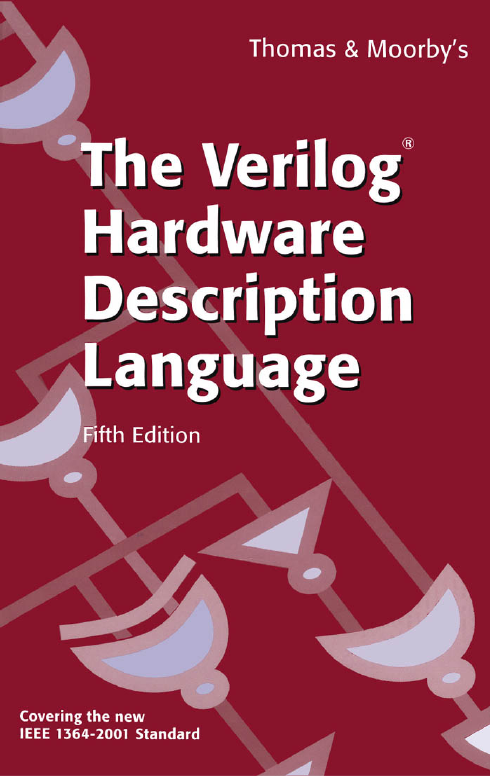

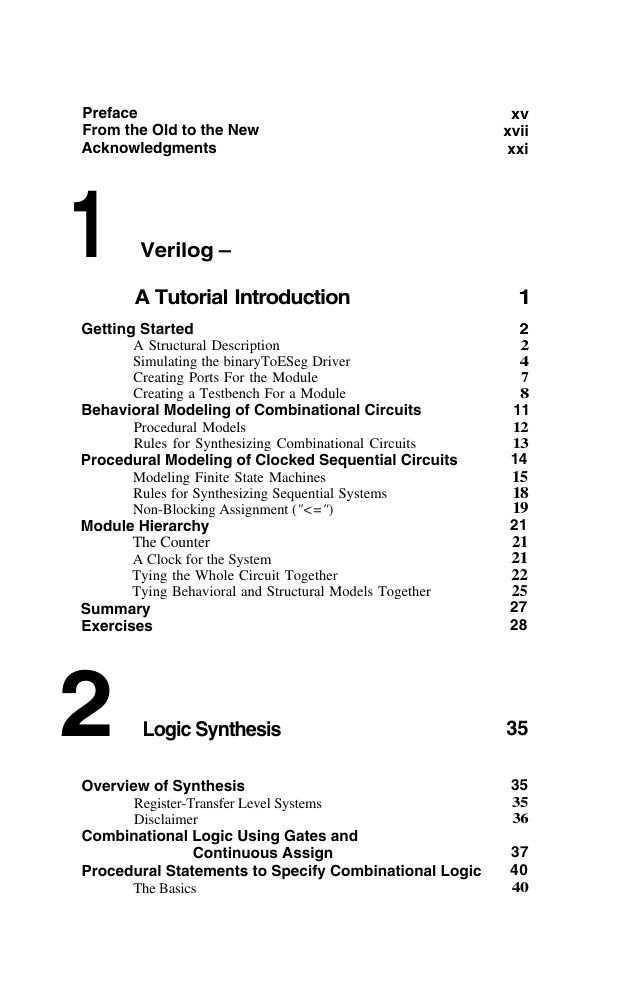

Preface

From the Old to the New

Acknowledgments

1 Verilog –

A Tutorial Introduction

Getting Started

A Structural Description

Simulating the binaryToESeg Driver

Creating Ports For the Module

Creating a Testbench For a Module

Behavioral Modeling of Combinational Circuits

Procedural Models

Rules for Synthesizing Combinational Circuits

Procedural Modeling of Clocked Sequential Circuits

Modeling Finite State Machines

Rules for Synthesizing Sequential Systems

Non-Blocking Assignment ("<=")

Module Hierarchy

The Counter

A Clock for the System

Tying the Whole Circuit Together

Tying Behavioral and Structural Models Together

Summary

Exercises

2 Logic Synthesis

Overview of Synthesis

Register-Transfer Level Systems

Disclaimer

Combinational Logic Using Gates and

Continuous Assign

Procedural Statements to Specify Combinational Logic

The Basics

xv

xvii

xxi

1

2

2

4

7

8

11

12

13

14

15

18

19

21

21

21

22

25

27

28

35

35

35

36

37

40

40

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc