《VLSI 电路设计》---项目设计

传输门全加器设计

指导老师:

组长:

�

目录

一.项目设计方案 .............................................................................................................................. 2

1.1 一位全加器简介: .............................................................................................................. 2

1.2 一位全加器的真值表: ......................................................................................................2

1.3 镜像 CMOS 全加器电路图:.............................................................................................3

1.4 镜像 CMOS 全加器的棍棒图: .........................................................................................4

1.5 镜像 CMOS 全加器的优化棍棒图: ................................................................................ 4

1.6 镜像 CMOS 全加器的欧拉路径:.....................................................................................5

1.7 镜像 CMOS 全加器的网表:.............................................................................................5

二.项目设计完成情况 .................................................................................................................... 7

1. HSPICE 前仿真: ................................................................................................................. 7

2.版图: ..................................................................................................................................... 8

3.DRC/LVS/PEX 完成情况: ...................................................................................................8

4.HSPICE 后仿真情况: .......................................................................................................... 9

5.全加器面积及性能: ............................................................................................................. 9

6.项目展望: ........................................................................................................................... 10

附录一...................................................................................................................................... 10

附录二...................................................................................................................................... 10

1

�

一.项目设计方案

1.1 一位全加器简介:

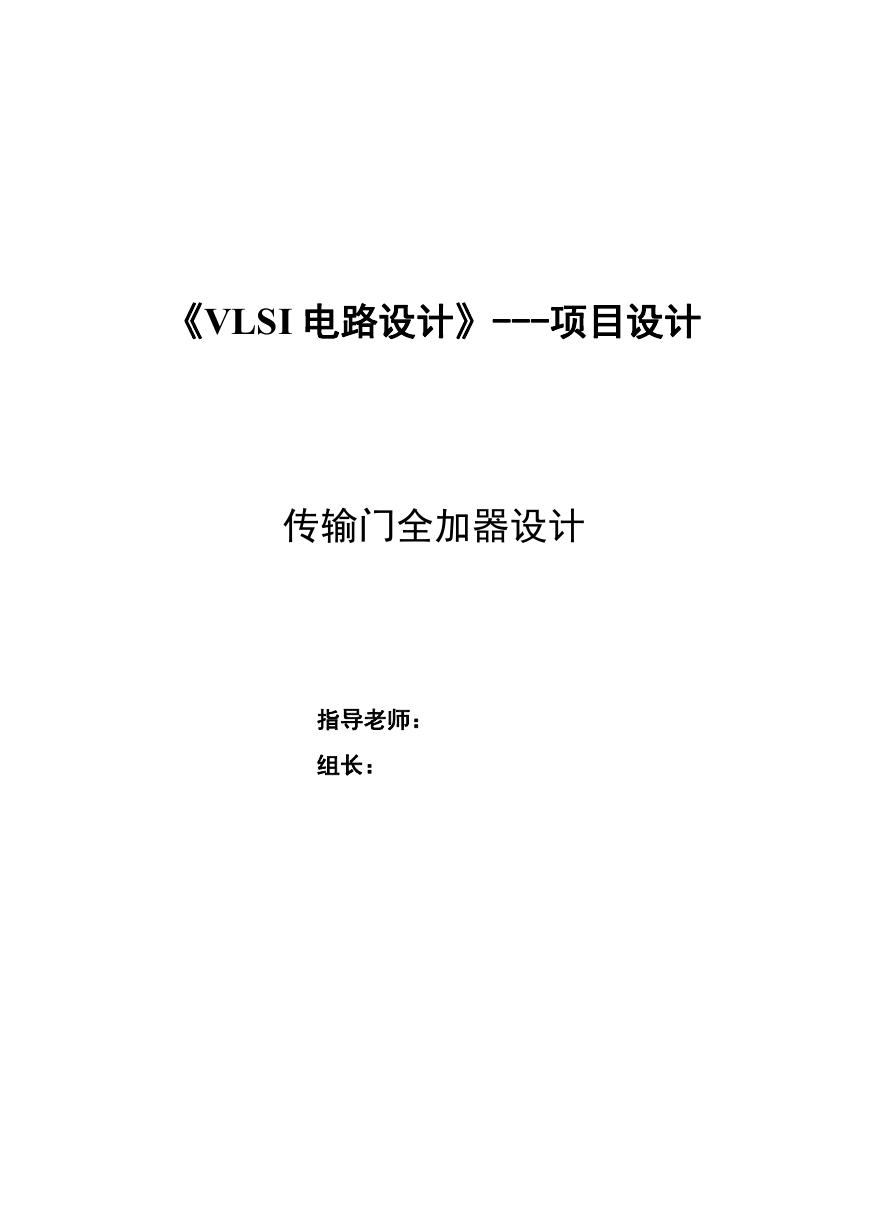

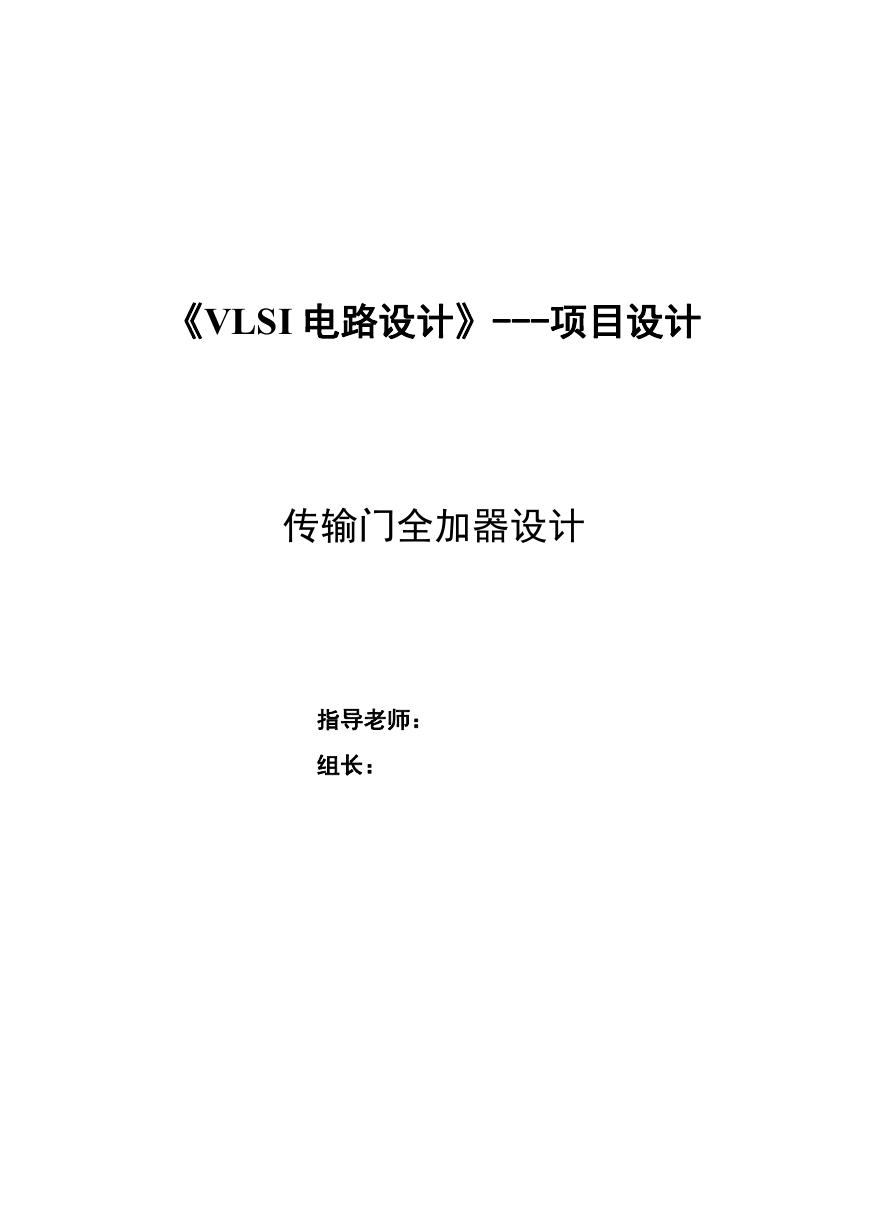

全加器是算术运算电路运算中的基本单元,也是构成多位

加法器的基本单元,介于加法器在算术运算电路当中的重要

作用,使得全加器的设计显得十分重要。通常情况下,我们

采用两种结构构成全加器电路,一种是由两个半加器组成,

另一种为镜像结构。全加器的基本符号如图 1-1 所示。其中,

A、B 为加法器的输入,Cin 进位输入,Sum 为输出,Cout 进

位输出。

A

B

Cin

FULL ADDER

Cout

Sum

1-1 全加器基本符号

全加器的逻辑表达式为:Cout=AB+BCin+ACin

Sum=ABCin+Cout(A+B+Cin)

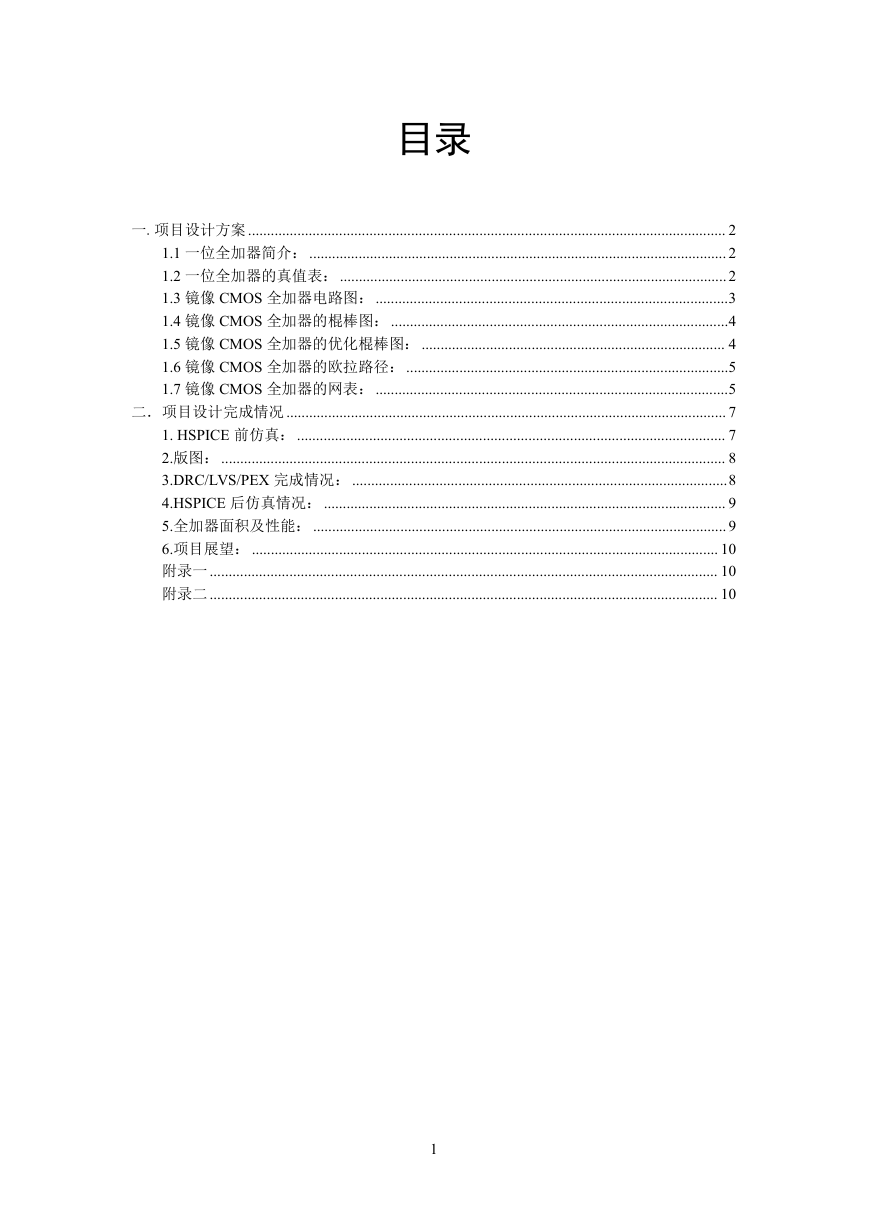

1.2 一位全加器的真值表:

2

�

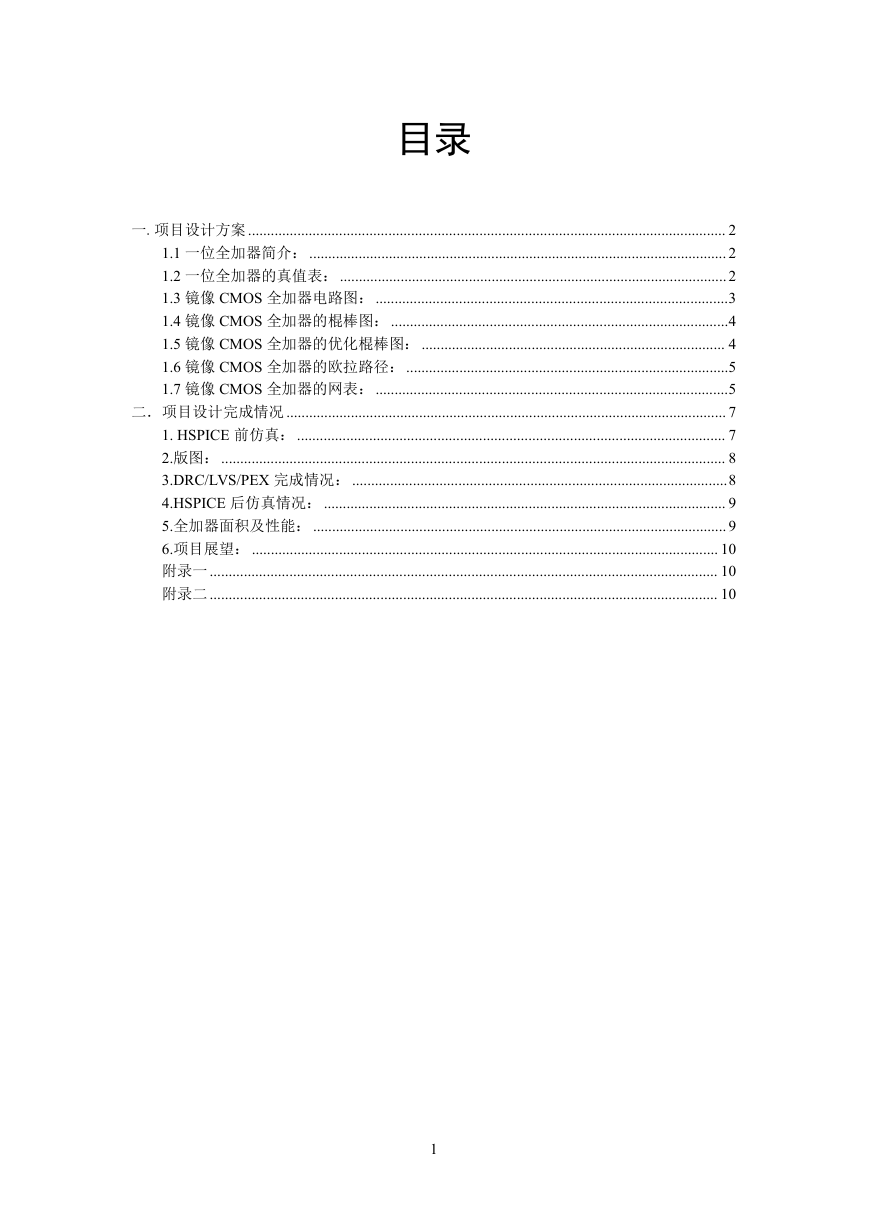

A

0

0

0

0

1

1

1

1

输入

输出

B

0

0

1

1

0

0

1

1

Cin

Sum

Cout

0

1

0

1

0

1

0

1

0

1

1

0

1

0

0

1

0

0

0

1

0

1

1

1

1-2 全加器真值表

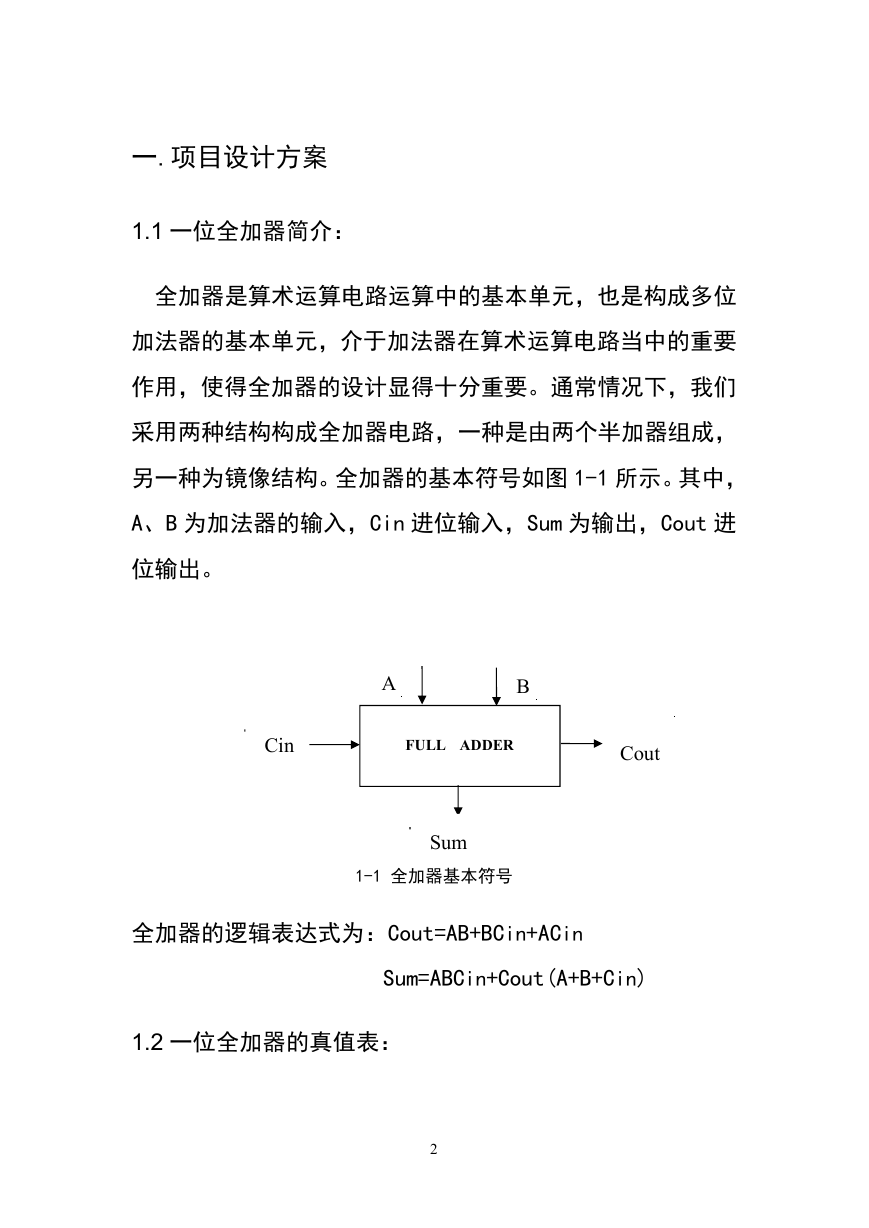

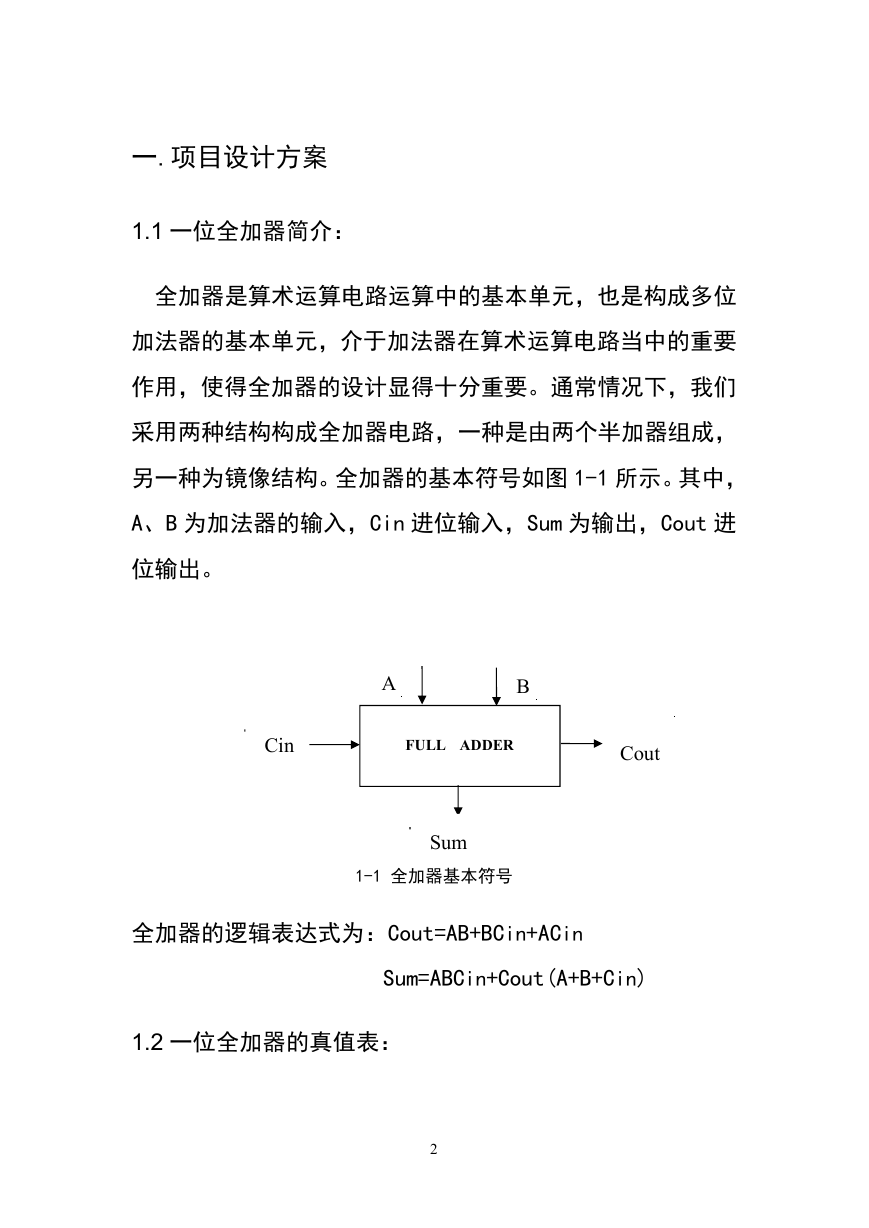

1.3 镜像 CMOS 全加器电路图:

1-3 镜像全加器电路图

当 D 为高时,!Cout 被置为 Vdd,清除进位;当 G 为高时,!

3

�

Cout 被置为 0,产生进位。当 P 为 1 时,输入进位反向传递

到!Cout,同时,可以分析求和电路,当 A,B,Cin 同时为 0,!

S 为 1,和为 0;当 A,B,Cin 同时为 1,!S 为 0,和为 1;当 A,

B,Cin 既有 1 也有 0 时,!S 的输出由!Cout 取反决定。由于

PMOS 和 NMOS 管完全对称,所以易于画出版图。该电路的工

作速度快于互补 CMOS 全加器。

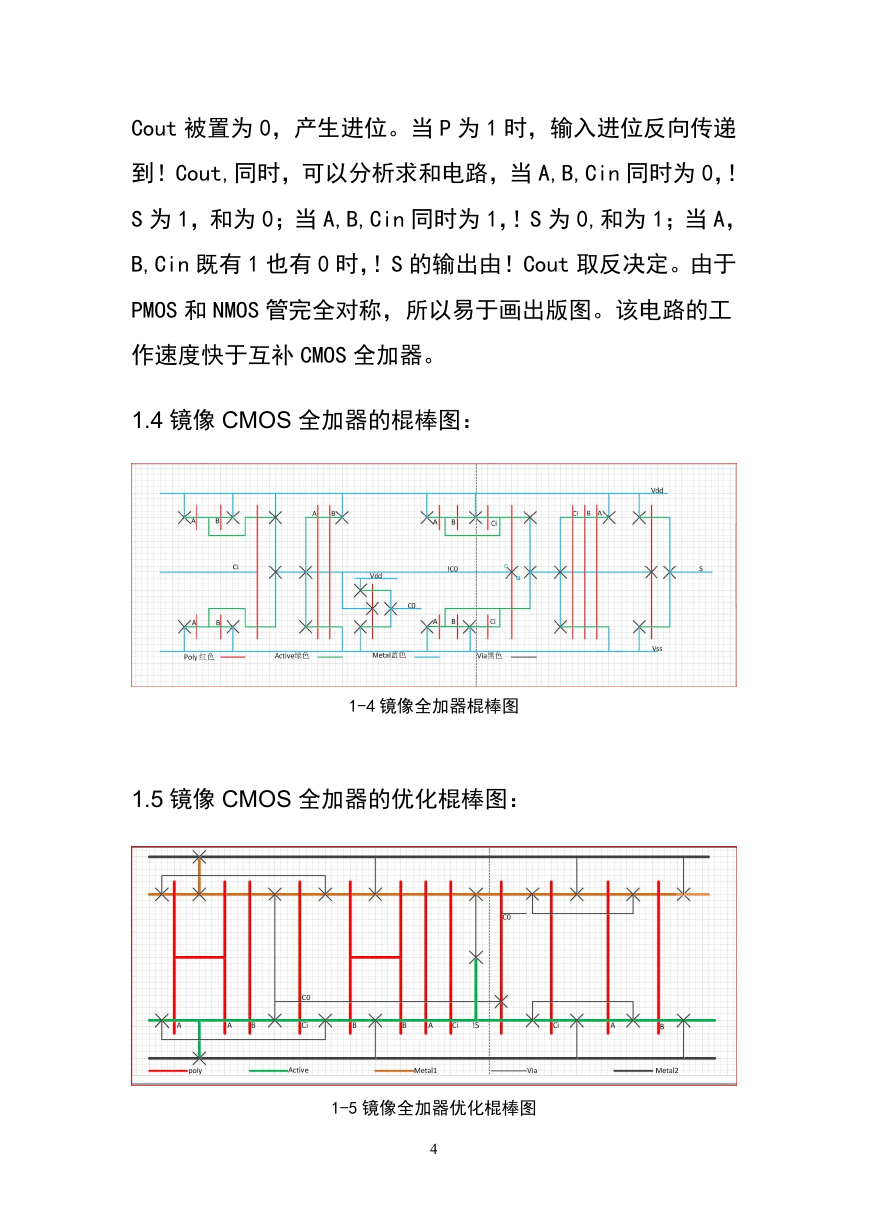

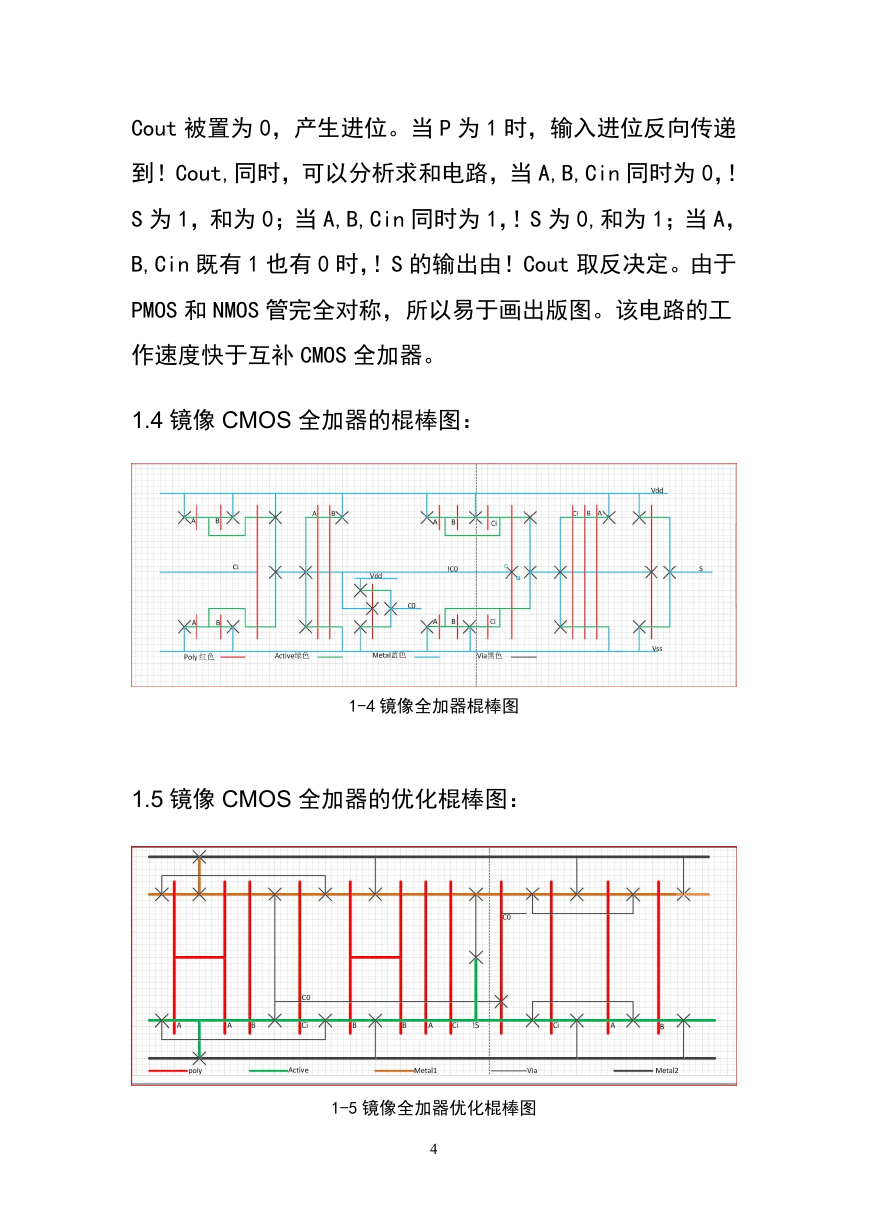

1.4 镜像 CMOS 全加器的棍棒图:

1-4 镜像全加器棍棒图

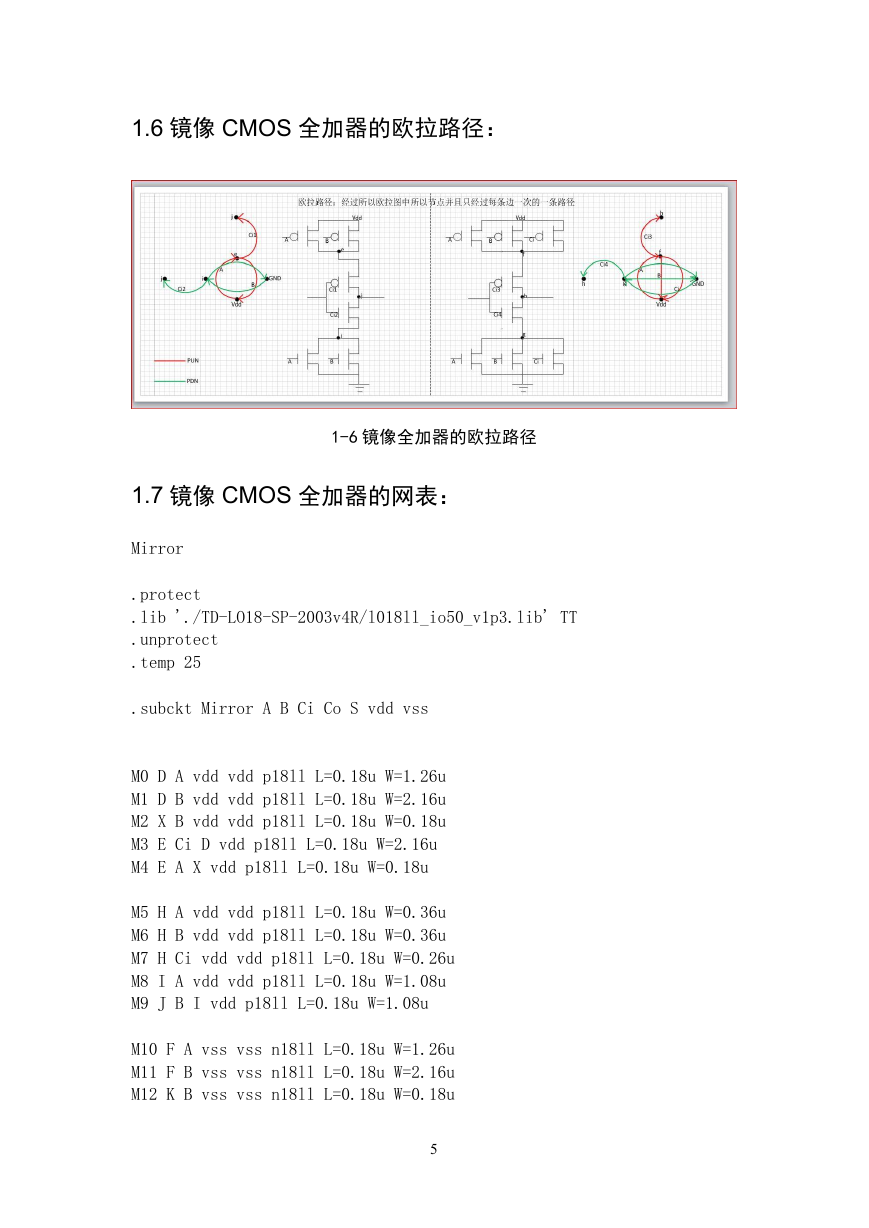

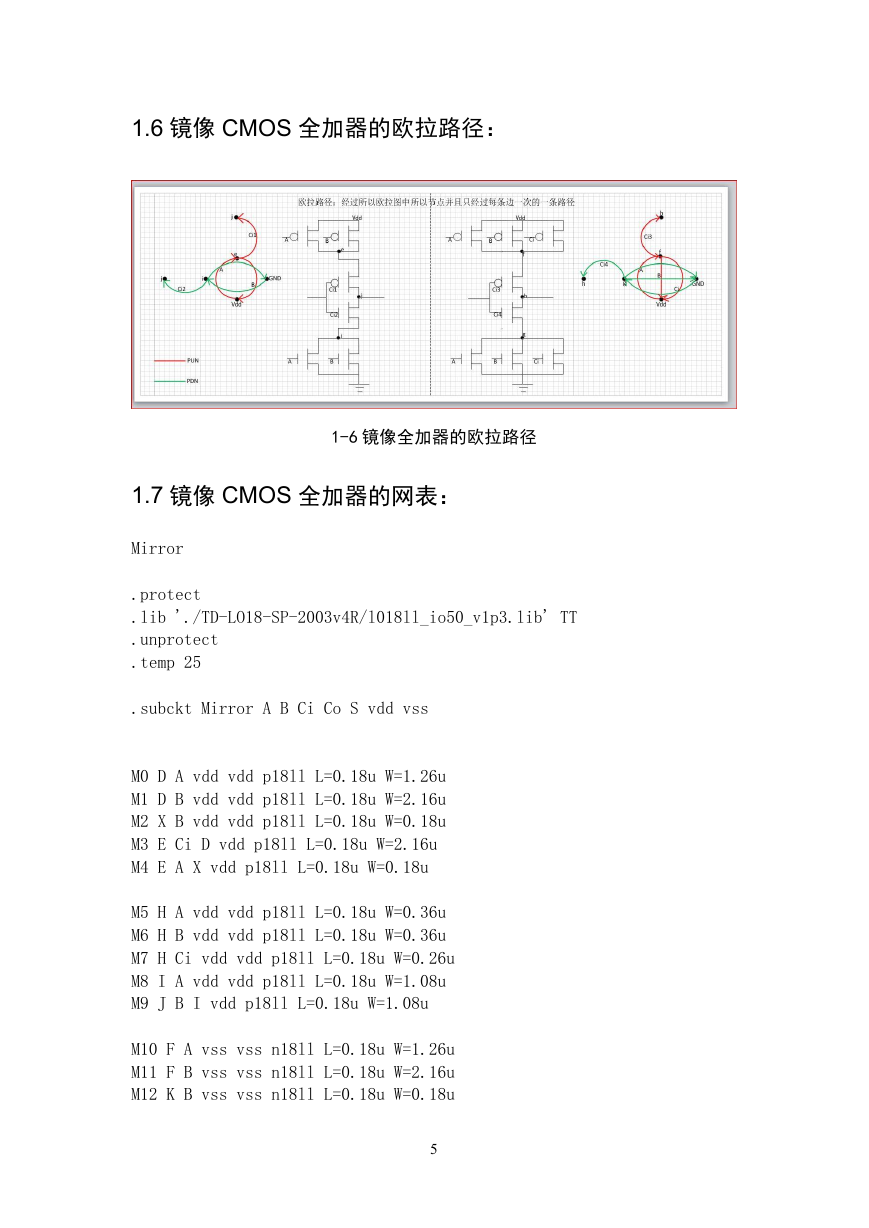

1.5 镜像 CMOS 全加器的优化棍棒图:

1-5 镜像全加器优化棍棒图

4

�

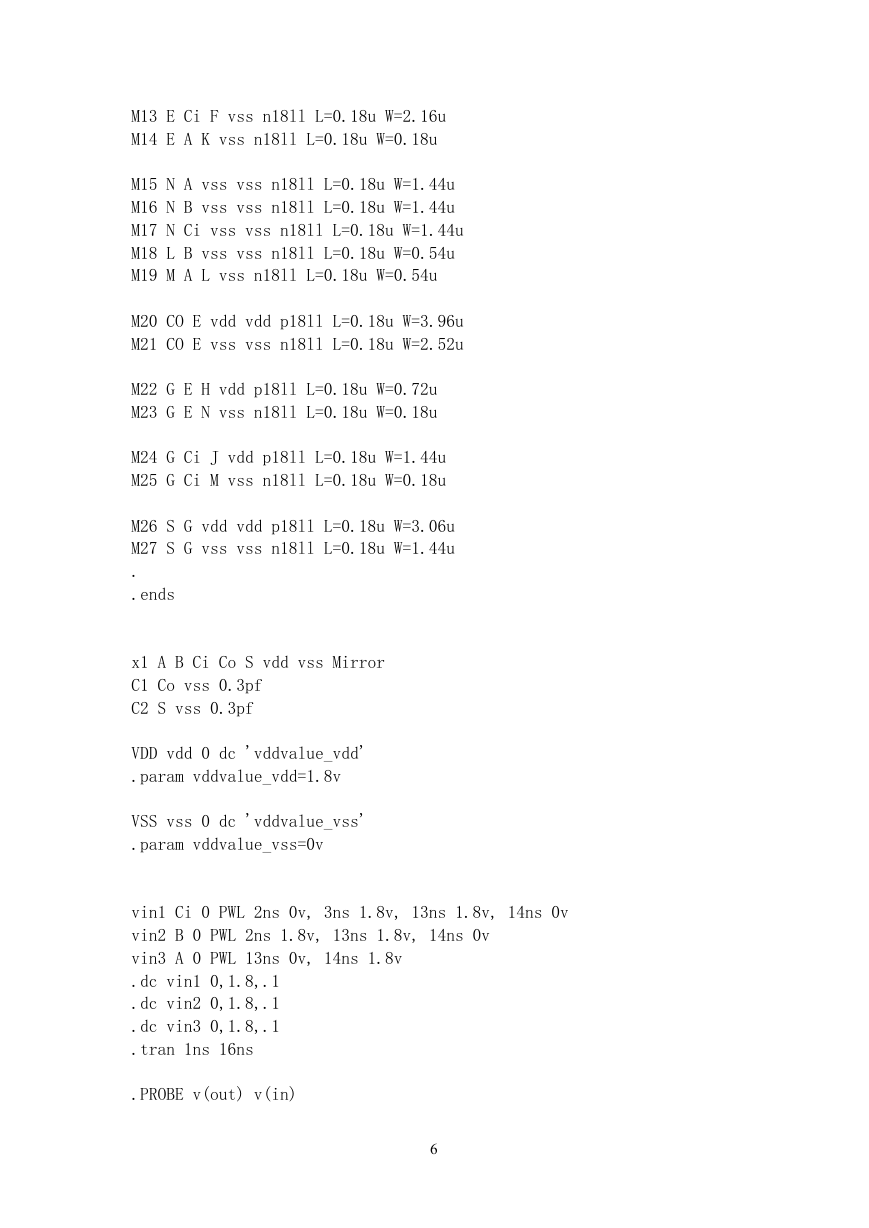

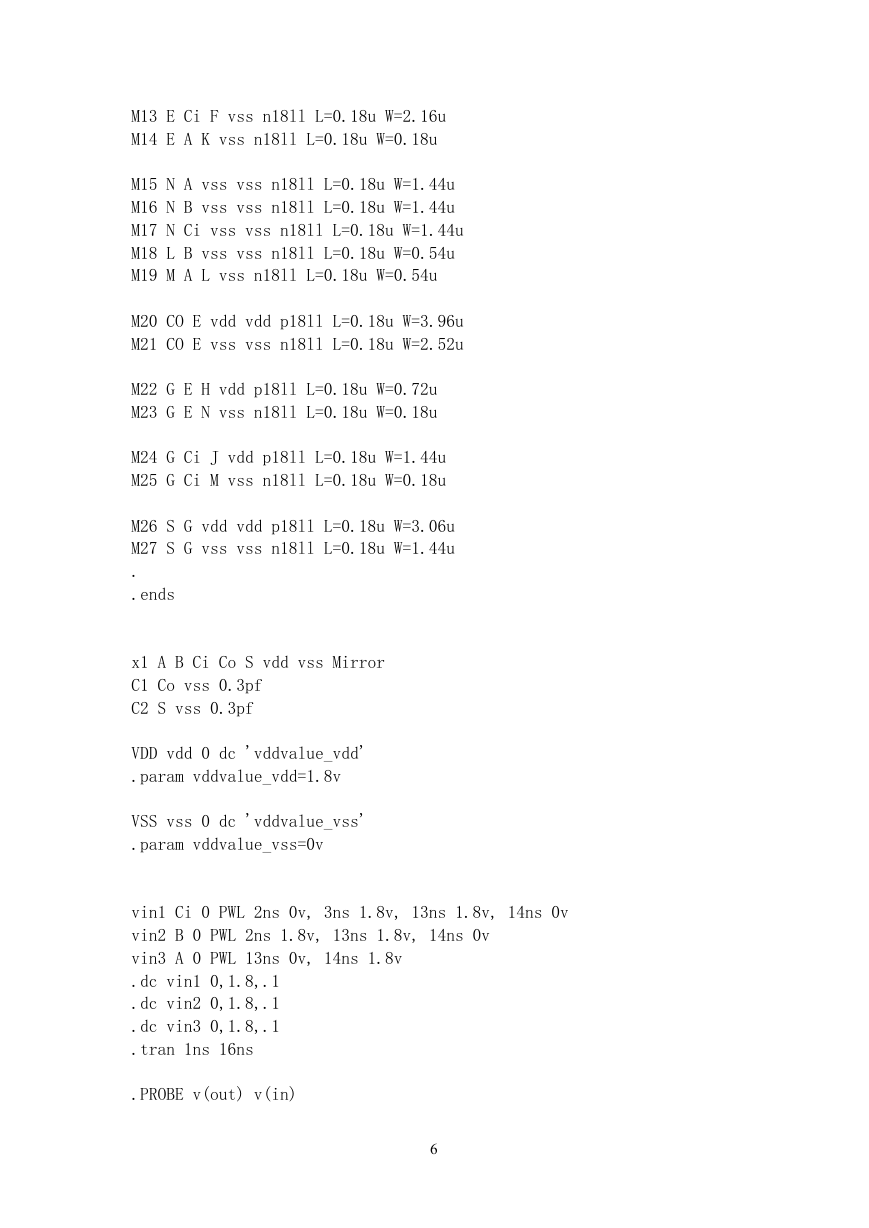

1.6 镜像 CMOS 全加器的欧拉路径:

1-6 镜像全加器的欧拉路径

1.7 镜像 CMOS 全加器的网表:

Mirror

.protect

.lib './TD-LO18-SP-2003v4R/l018ll_io50_v1p3.lib' TT

.unprotect

.temp 25

.subckt Mirror A B Ci Co S vdd vss

M0 D A vdd vdd p18ll L=0.18u W=1.26u

M1 D B vdd vdd p18ll L=0.18u W=2.16u

M2 X B vdd vdd p18ll L=0.18u W=0.18u

M3 E Ci D vdd p18ll L=0.18u W=2.16u

M4 E A X vdd p18ll L=0.18u W=0.18u

M5 H A vdd vdd p18ll L=0.18u W=0.36u

M6 H B vdd vdd p18ll L=0.18u W=0.36u

M7 H Ci vdd vdd p18ll L=0.18u W=0.26u

M8 I A vdd vdd p18ll L=0.18u W=1.08u

M9 J B I vdd p18ll L=0.18u W=1.08u

M10 F A vss vss n18ll L=0.18u W=1.26u

M11 F B vss vss n18ll L=0.18u W=2.16u

M12 K B vss vss n18ll L=0.18u W=0.18u

5

�

M13 E Ci F vss n18ll L=0.18u W=2.16u

M14 E A K vss n18ll L=0.18u W=0.18u

M15 N A vss vss n18ll L=0.18u W=1.44u

M16 N B vss vss n18ll L=0.18u W=1.44u

M17 N Ci vss vss n18ll L=0.18u W=1.44u

M18 L B vss vss n18ll L=0.18u W=0.54u

M19 M A L vss n18ll L=0.18u W=0.54u

M20 CO E vdd vdd p18ll L=0.18u W=3.96u

M21 CO E vss vss n18ll L=0.18u W=2.52u

M22 G E H vdd p18ll L=0.18u W=0.72u

M23 G E N vss n18ll L=0.18u W=0.18u

M24 G Ci J vdd p18ll L=0.18u W=1.44u

M25 G Ci M vss n18ll L=0.18u W=0.18u

M26 S G vdd vdd p18ll L=0.18u W=3.06u

M27 S G vss vss n18ll L=0.18u W=1.44u

.

.ends

x1 A B Ci Co S vdd vss Mirror

C1 Co vss 0.3pf

C2 S vss 0.3pf

VDD vdd 0 dc 'vddvalue_vdd'

.param vddvalue_vdd=1.8v

VSS vss 0 dc 'vddvalue_vss'

.param vddvalue_vss=0v

vin1 Ci 0 PWL 2ns 0v, 3ns 1.8v, 13ns 1.8v, 14ns 0v

vin2 B 0 PWL 2ns 1.8v, 13ns 1.8v, 14ns 0v

vin3 A 0 PWL 13ns 0v, 14ns 1.8v

.dc vin1 0,1.8,.1

.dc vin2 0,1.8,.1

.dc vin3 0,1.8,.1

.tran 1ns 16ns

.PROBE v(out) v(in)

6

�

.end

二.项目设计完成情况

基本按照项目要求完成镜像全加器的设计,从电路图、

棍棒图到前仿真的网表以及最后的版图设计和后仿真,按

照步骤全部完成。

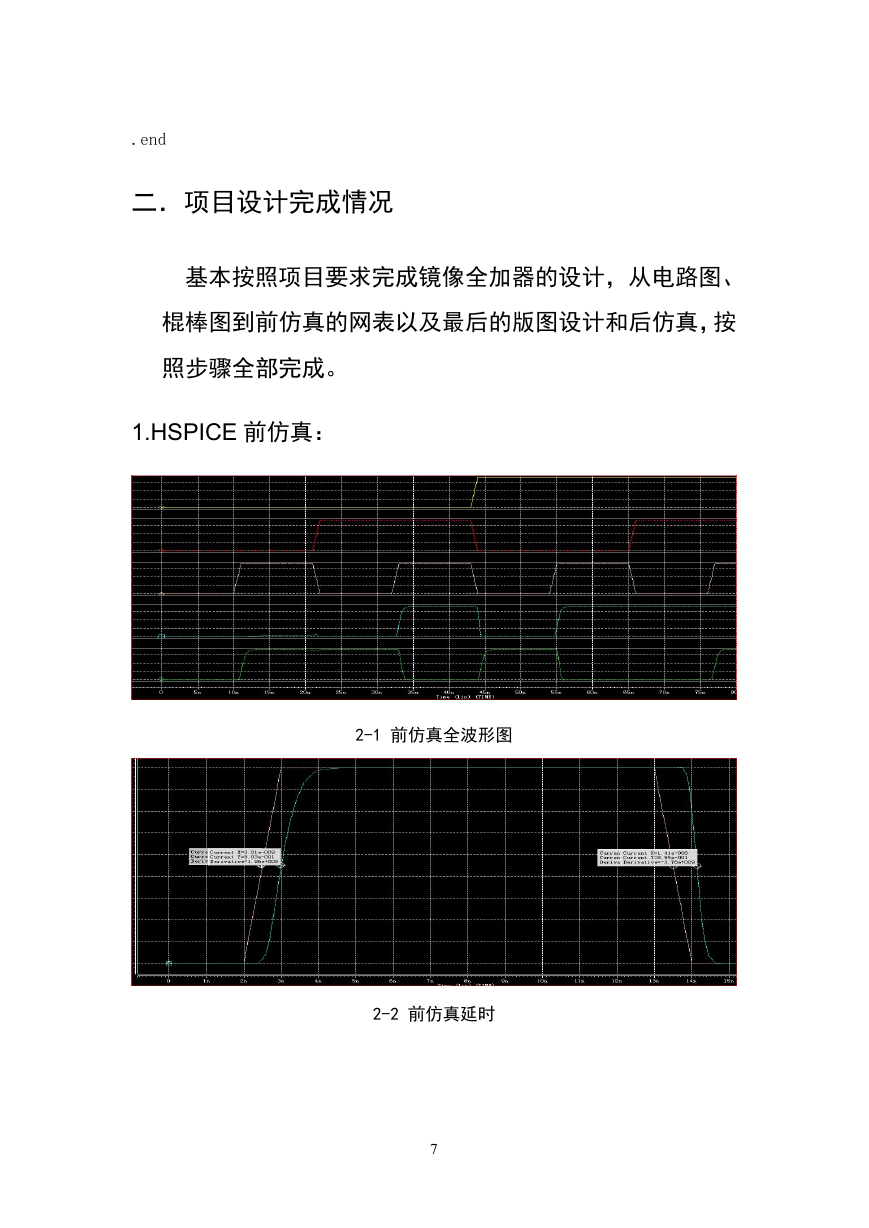

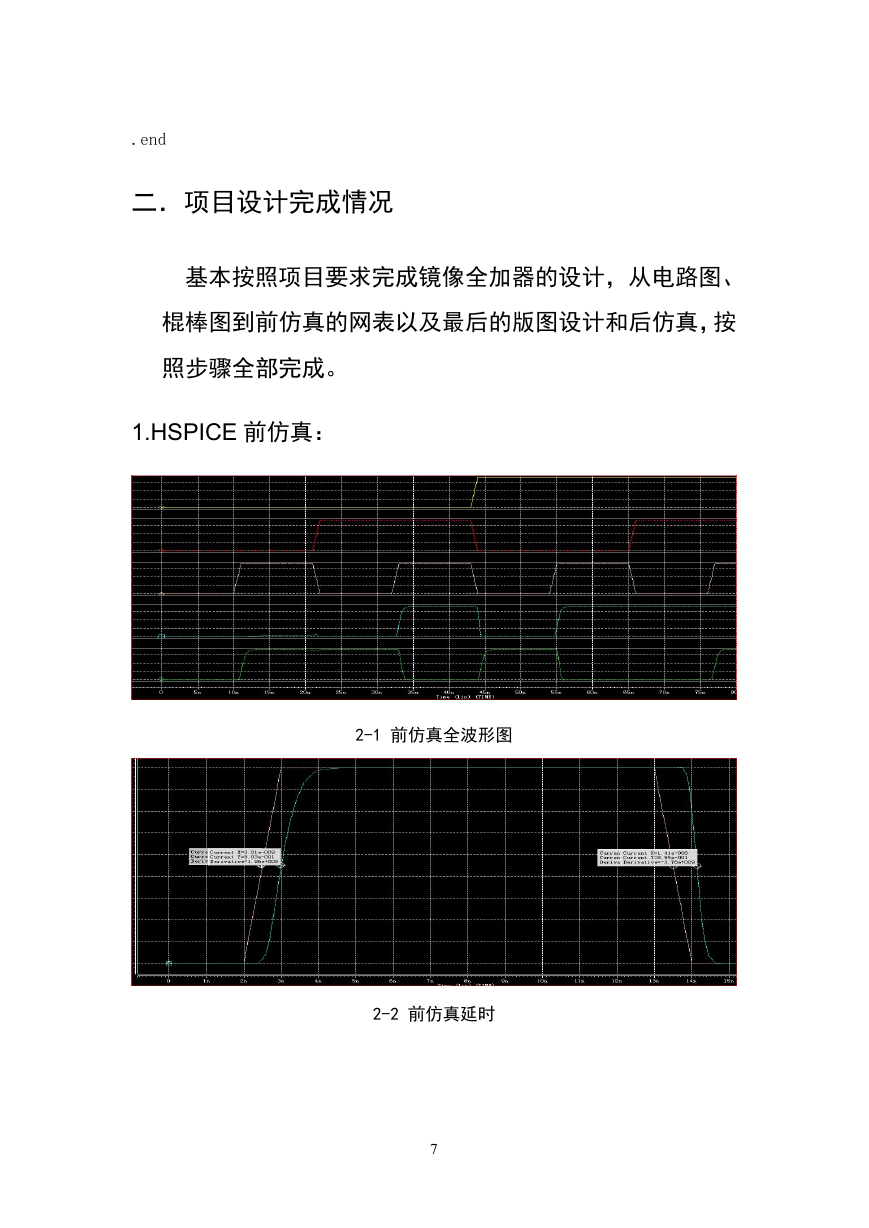

1.HSPICE 前仿真:

2-1 前仿真全波形图

2-2 前仿真延时

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc