STM32 OTG_FS/HS模块

Lilian YAO

�

OTG模块概览

Presentation Title

04/05/2015

�

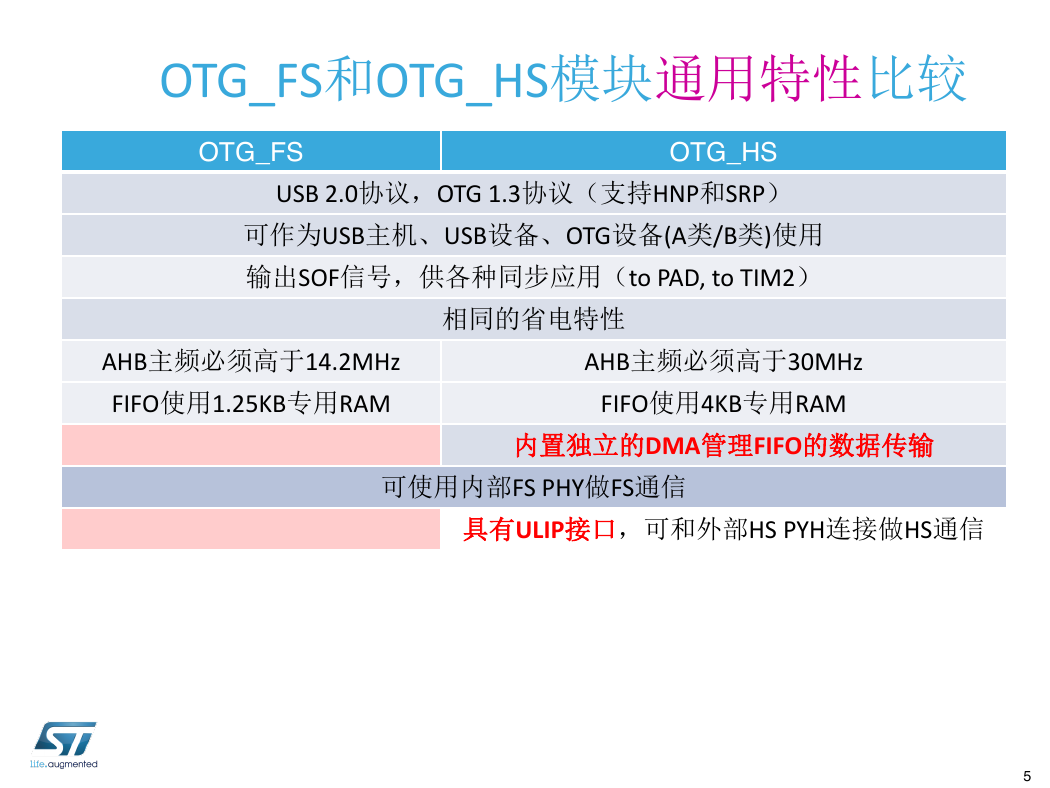

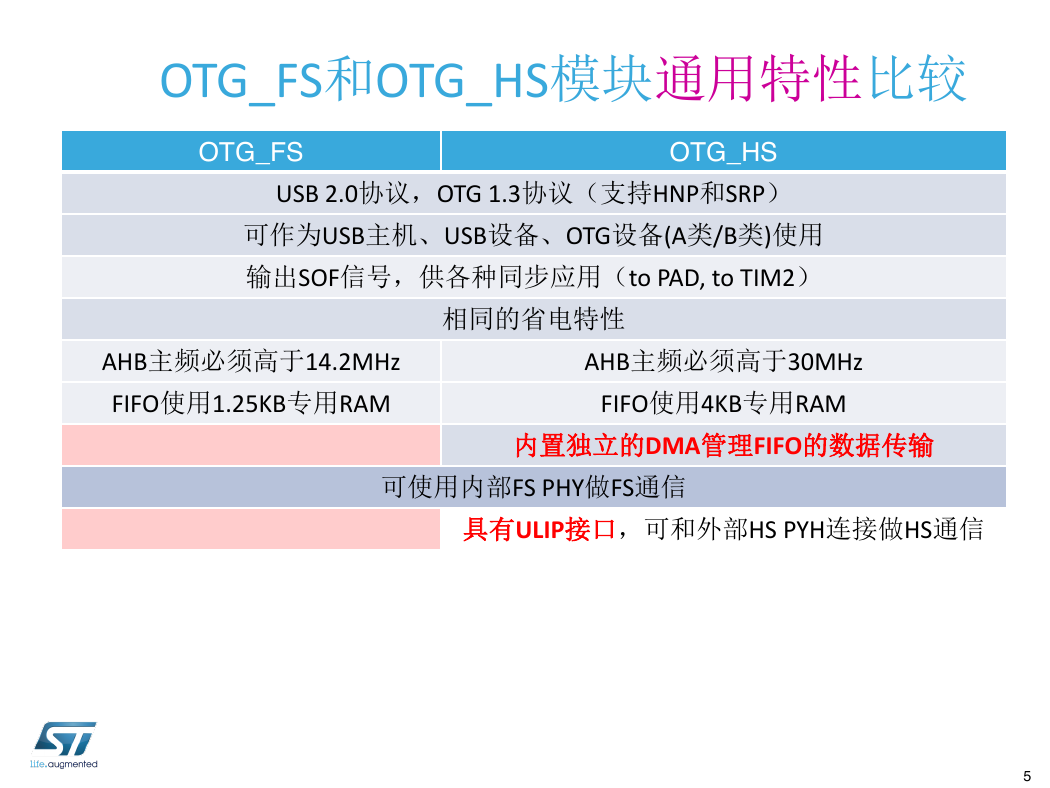

OTG_FS和OTG_HS模块通用特性比较

OTG_FS

OTG_HS

USB 2.0协议,OTG 1.3协议(支持HNP和SRP)

可作为USB主机、USB设备、OTG设备(A类/B类)使用

输出SOF信号,供各种同步应用(to PAD, to TIM2)

相同的省电特性

AHB主频必须高于14.2MHz

FIFO使用1.25KB专用RAM

AHB主频必须高于30MHz

FIFO使用4KB专用RAM

内置独立的DMA管理FIFO的数据传输

可使用内部FS PHY做FS通信

具有ULIP接口,可和外部HS PYH连接做HS通信

5

�

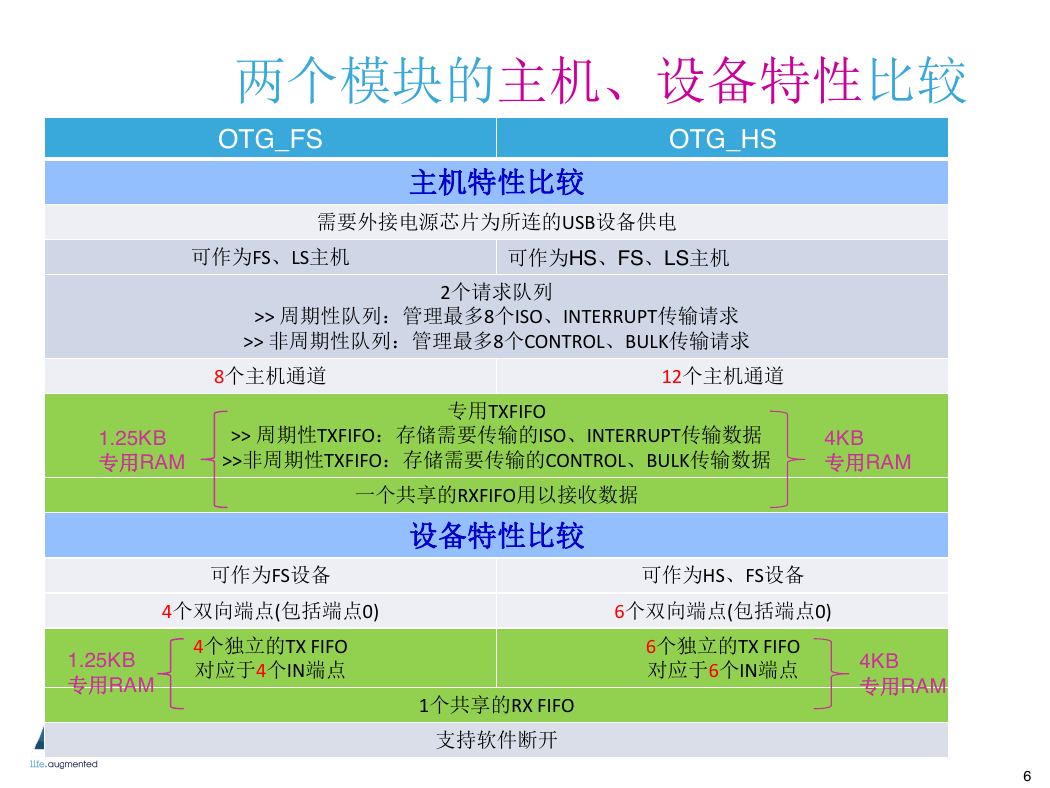

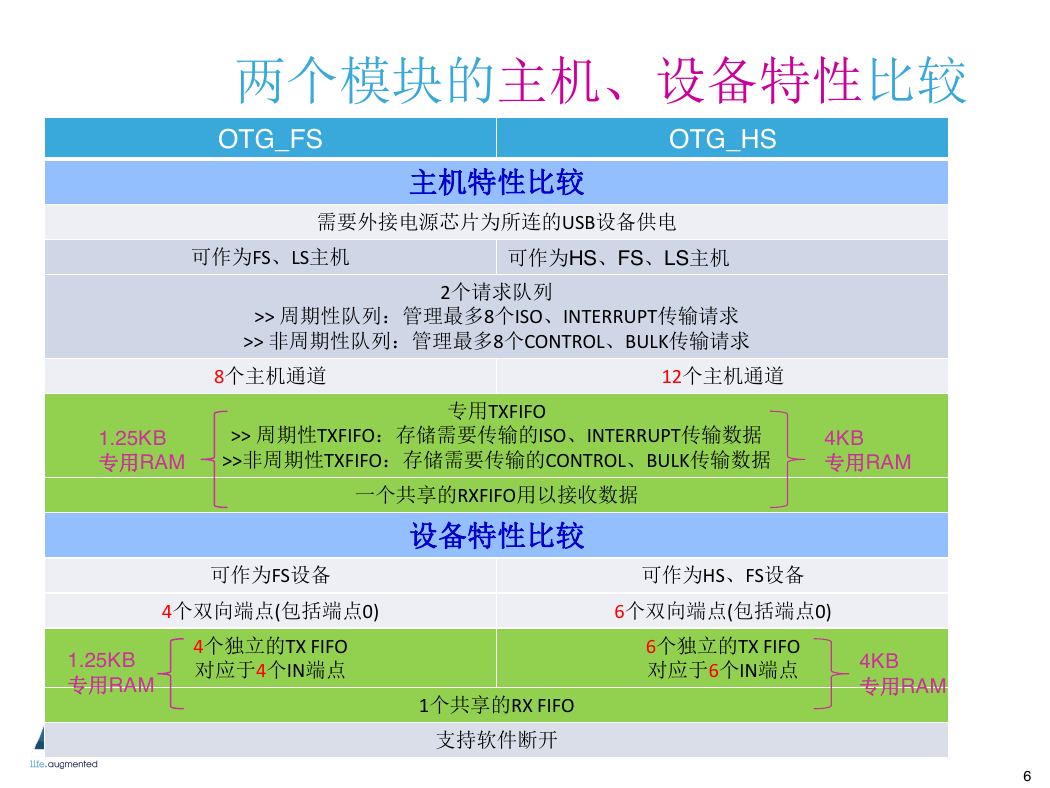

两个模块的主机、设备特性比较

OTG_FS

OTG_HS

主机特性比较

需要外接电源芯片为所连的USB设备供电

可作为FS、LS主机

可作为HS、FS、LS主机

2个请求队列

>> 周期性队列:管理最多8个ISO、INTERRUPT传输请求

>> 非周期性队列:管理最多8个CONTROL、BULK传输请求

8个主机通道

12个主机通道

1.25KB

专用RAM

>> 周期性TXFIFO:存储需要传输的ISO、INTERRUPT传输数据

>>非周期性TXFIFO:存储需要传输的CONTROL、BULK传输数据

4KB

专用RAM

专用TXFIFO

一个共享的RXFIFO用以接收数据

设备特性比较

可作为FS设备

4个双向端点(包括端点0)

4个独立的TX FIFO

对应于4个IN端点

1.25KB

专用RAM

1个共享的RX FIFO

支持软件断开

可作为HS、FS设备

6个双向端点(包括端点0)

6个独立的TX FIFO

对应于6个IN端点

4KB

专用RAM

6

�

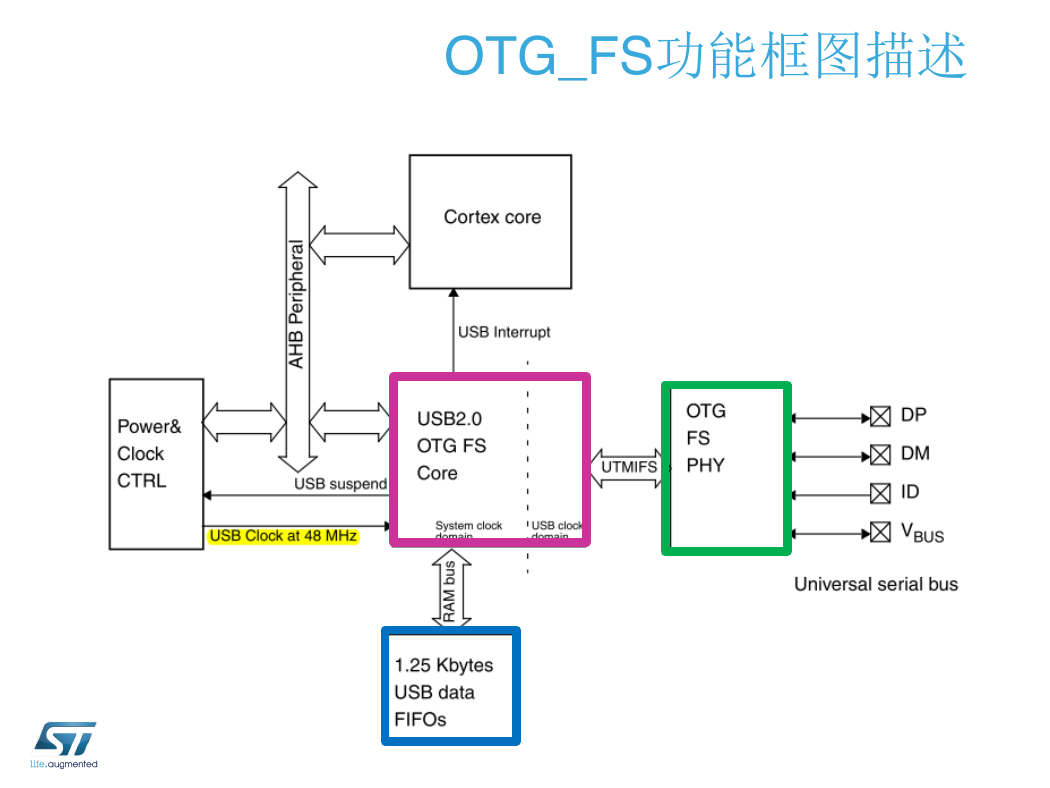

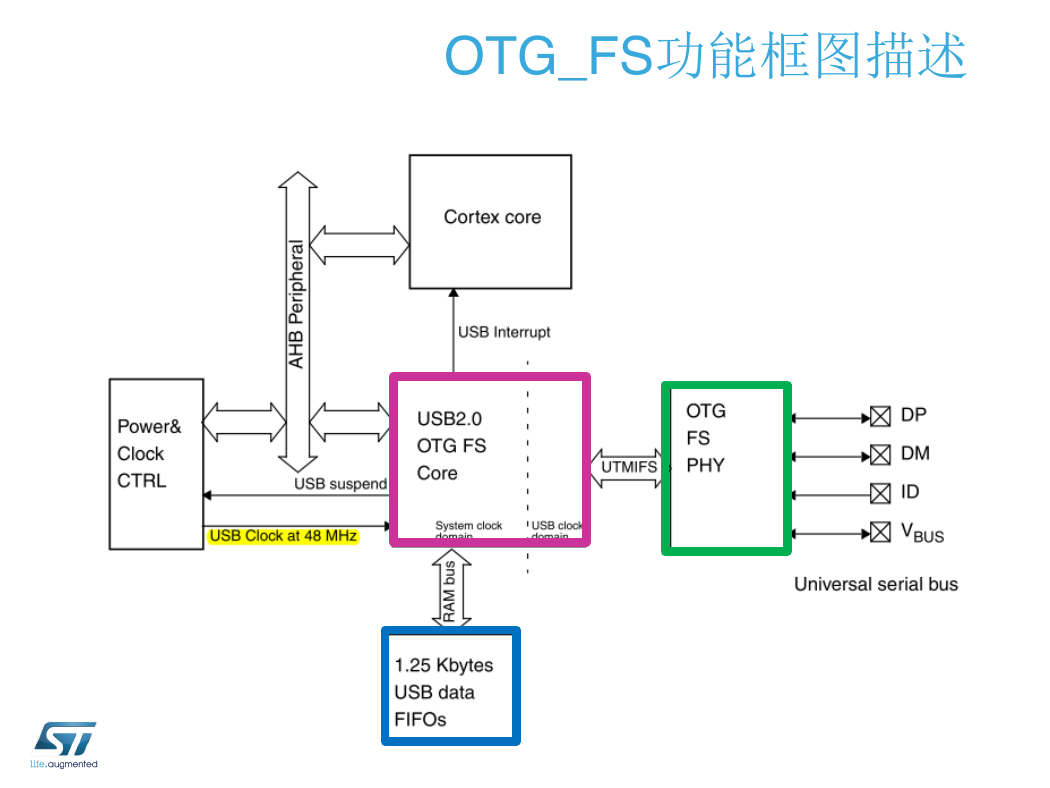

OTG_FS功能框图描述

�

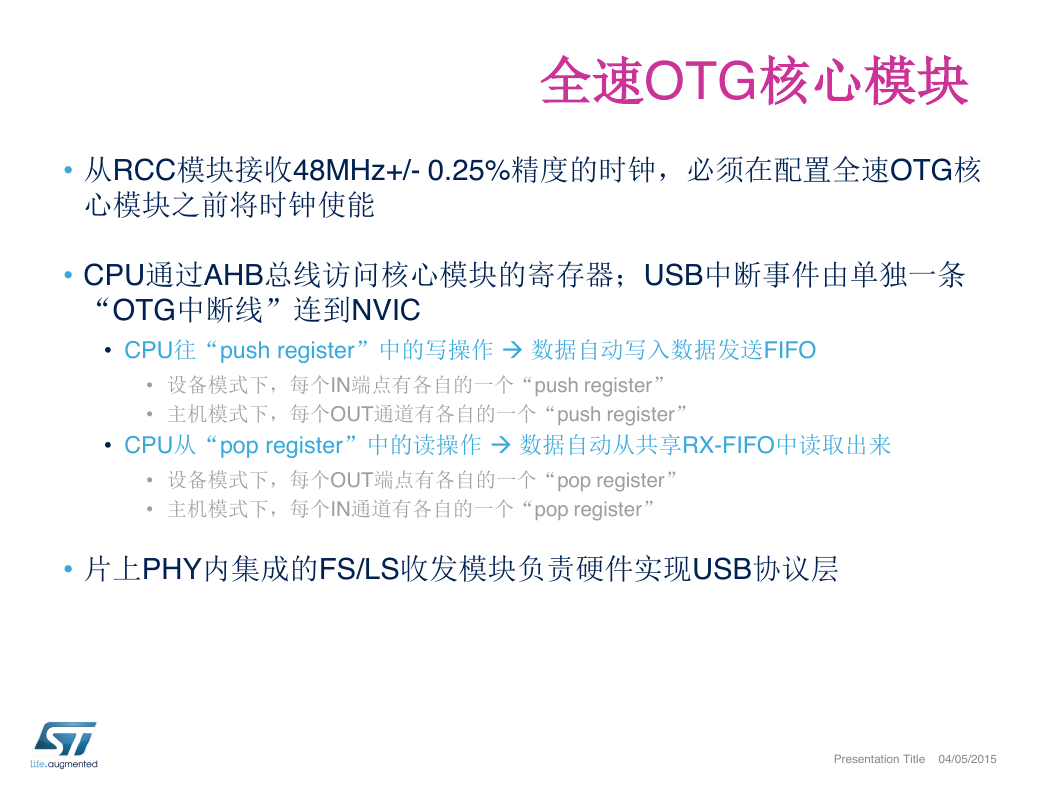

全速OTG核心模块

• 从RCC模块接收48MHz+/- 0.25%精度的时钟,必须在配置全速OTG核

心模块之前将时钟使能

• CPU通过AHB总线访问核心模块的寄存器;USB中断事件由单独一条

“OTG中断线”连到NVIC

• CPU往“push register”中的写操作 数据自动写入数据发送FIFO

• 设备模式下,每个IN端点有各自的一个“push register”

• 主机模式下,每个OUT通道有各自的一个“push register”

• CPU从“pop register”中的读操作 数据自动从共享RX-FIFO中读取出来

• 设备模式下,每个OUT端点有各自的一个“pop register”

• 主机模式下,每个IN通道有各自的一个“pop register”

• 片上PHY内集成的FS/LS收发模块负责硬件实现USB协议层

Presentation Title

04/05/2015

�

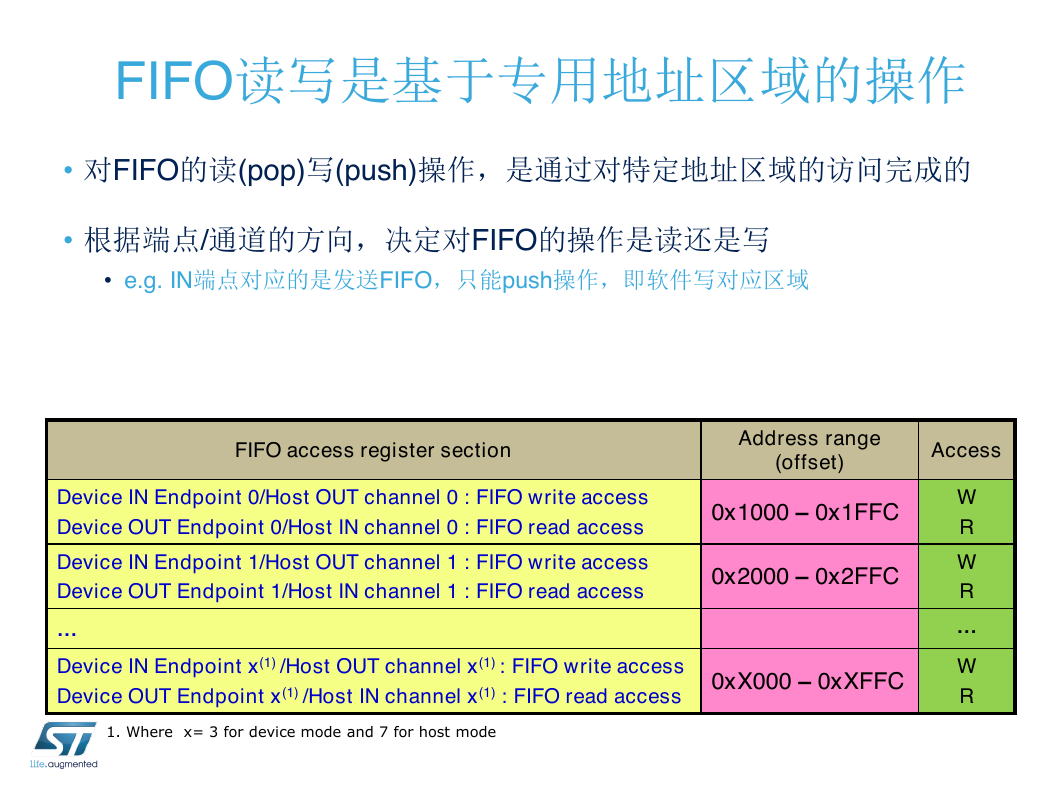

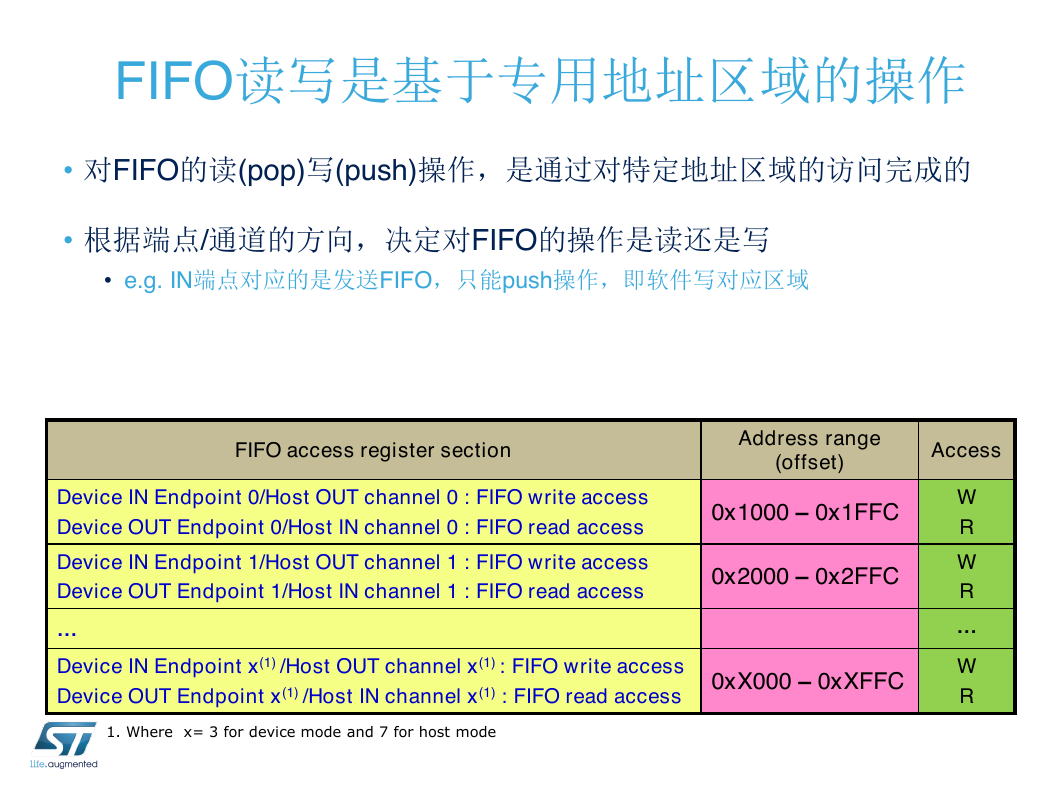

FIFO读写是基于专用地址区域的操作

• 对FIFO的读(pop)写(push)操作,是通过对特定地址区域的访问完成的

• 根据端点/通道的方向,决定对FIFO的操作是读还是写

• e.g. IN端点对应的是发送FIFO,只能push操作,即软件写对应区域

FIFO access register section

Address range

(offset)

Access

Device IN Endpoint 0/Host OUT channel 0 : FIFO write access

Device OUT Endpoint 0/Host IN channel 0 : FIFO read access

0x1000 – 0x1FFC

Device IN Endpoint 1/Host OUT channel 1 : FIFO write access

Device OUT Endpoint 1/Host IN channel 1 : FIFO read access

0x2000 – 0x2FFC

…

Device IN Endpoint x(1) /Host OUT channel x(1) : FIFO write access

Device OUT Endpoint x(1) /Host IN channel x(1) : FIFO read access

0xX000 – 0xXFFC

1. Where x= 3 for device mode and 7 for host mode

W

R

W

R

…

W

R

�

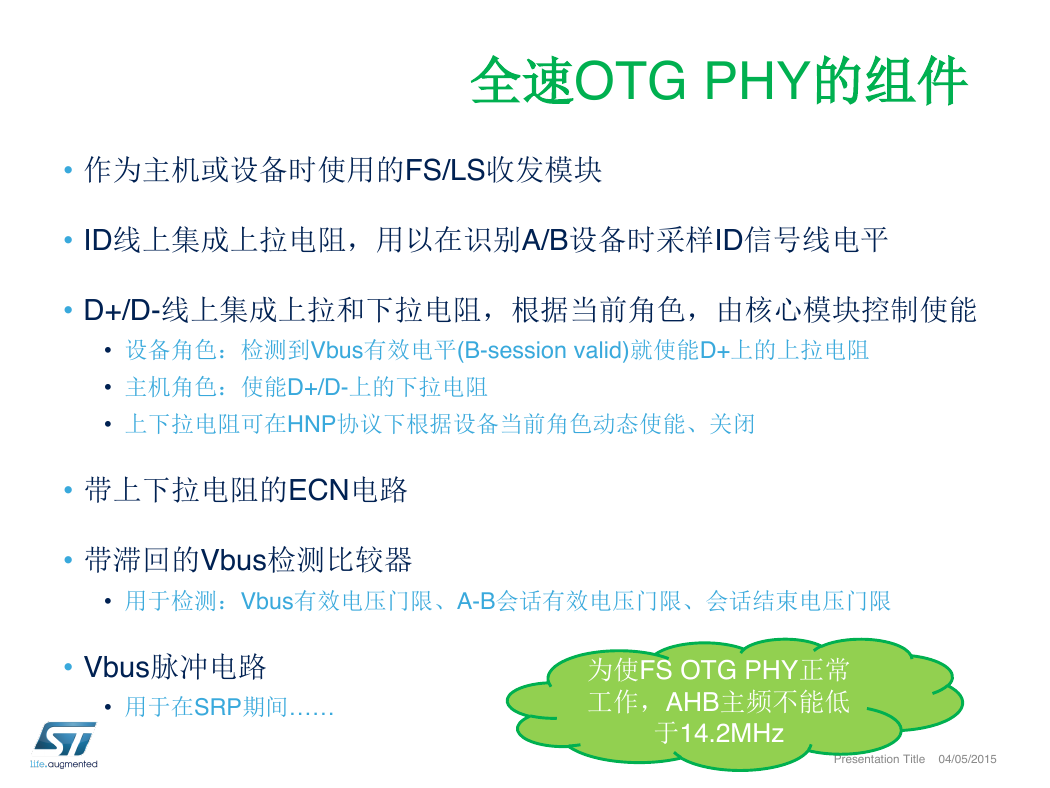

全速OTG PHY的组件

• 作为主机或设备时使用的FS/LS收发模块

• ID线上集成上拉电阻,用以在识别A/B设备时采样ID信号线电平

• D+/D-线上集成上拉和下拉电阻,根据当前角色,由核心模块控制使能

• 设备角色:检测到Vbus有效电平(B-session valid)就使能D+上的上拉电阻

• 主机角色:使能D+/D-上的下拉电阻

• 上下拉电阻可在HNP协议下根据设备当前角色动态使能、关闭

• 带上下拉电阻的ECN电路

• 带滞回的Vbus检测比较器

• 用于检测:Vbus有效电压门限、A-B会话有效电压门限、会话结束电压门限

• Vbus脉冲电路

• 用于在SRP期间……

为使FS OTG PHY正常

工作,AHB主频不能低

于14.2MHz

Presentation Title

04/05/2015

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc