2005 年第 6 期

基金项目论文

FO UNDAT IO N SUPPO RTED PRO JECT

文章编号 : 1001 - 893X (2005) 06 - 0026 - 07

8B /10B编码器的设计及实现

李 宥 谋

(西安邮电学院 专用集成电路设计中心 ,陕西 西安 710061)

3

摘 要 :本文介绍了 8B /10B编码技术 ,提出了一种简单 、实用的 8B /10B编码器的实现方法 ,并且采

用 Verilog语言设计了一种通用的软核 。通过在 FPGA 器件上进行测试 ,电路稳定 、可靠 ,可直接嵌

入到需要 8B /10B 编码功能的收发器电路中 。

关键词 :串行数据传输 ; 8B /10B编码 ;极性偏差 (RD ) ; Verilog语言

中图分类号 : TN919. 3; TN762 文献标识码 : A

Design and Realization of an 8B /10B Encoder

L I You - m ou

(ASIC Design Center , Xi’an Institute of Posts and Telecommunications, Xi’an 710061, China)

Abstract: This paper introduces 8B /10B encoding technique, and puts forward a simp le and p ractical real

ization method of an 8B /10B encoder. Furthermore, a versatile soft - core designed w ith Verilog is p resen

ted.

It is tested to be stable and reliable by FPGA devices, and can be directly embedded in transceiver

circuit with 8B /10B encoding function.

Key words: Serial data transm ission; 8B /10B encoding; R running disparity (RD ) ; Verilog language

一 、引 言

在高速的串行数据传输中 ,传送的数据被编码

成自同步的数据流 ,就是将数据和时钟组合成单一

的信号进行传送 ,使得接收方能容易准确地将数据

和时钟分离 ,而且要达到令人满意的误码率 ,其关键

技术在于串行传输中数据的编码方法 。目前大多数

高速串行标准都采用 8B /10B 编码方案 ,例如光纤

通道 1、PC I - Exp ress、串行 ATA、以太网 、XAU I、In

finiBand和串行相连 SCSI等 。使用 8B /10B 编码技

术 ,较好地解决了以下问题 。

(1)转换密度 :保证数据流中有足够的信号转

换 。采用 8B /10B编码方法 ,数据流中连续的“1”或

连续的“0”不超过 5个 ,使接收端锁相环 ( PLL )能正

常工作 ,避免接收端时钟漂移或同步丢失而引起数

据丢失 。

(2) DC补偿 : 在高速的数据传输线路中 ,一般

采用差分信号 ,需要直流分量尽量小 ,而 8B /10B 有

DC补偿功能 ,即链路中不会随着时间推移而出现

DC偏移 。

(3)检错 : 8B /10B 编码采用冗余方式 ,将 8位

的数据和一些特殊字符按照特定的规则编码成 10

位的数据 ,根据这些规则 ,能检测出传输过程中发生

错误的信息 。

(4)特殊字符 : 8B /10B 编码规定了一些特殊字

符 ,可用作帧同步字符和其他的分隔符或控制字符 。

8B /10B 编码是由 IBM 公司开发 ,把 8 位数据

字节转换成串行传输使用的 10位码 。8B /10B 编码

保证了 1和 0的相对平衡组合 ,而与数据值无关 ,简

化了时钟恢复 ,降低了接收机成本 。编码提供的其

收稿日期 : 2004 - 12 - 25

基金项目 :国家 863计划项目 (2003AA1Z1190) ;国家自然科学基金资助项目 (90207015)

·62·

�

2005 年第 6 期

它位还促进了误码检测 。8B /10B 编码提供了构建

串行通信使用的一套基础数据和控制字符 。许多独

立标准都以这个公共字符集为基础 ,定义更高的协

议层 。

二 、8B /10B 编码技术

将 8 bit数据分成 3 bit和 5 bit两组 ,分别对应

10 bit中的 4 bit和 6 bit,直流平衡代码的不平衡度

就是通过“0”的个数减去“1”的个数来计算得到的 。

如果 4 bit和 6 bit的各分组中“0”和“1”的个数相

等 ,称为完美平衡代码 ,或称为完美的直流平衡代

码 ,无需补偿 ,但是这种情况是不可能的 。因为在 4

bit的子分组中 , 16 种编码中只有 6 种是完美平衡

的 ,这对于 3 bit的 8种编码值是不够的 。同时 ,在 6

bit的子分组中也只有 20种编码是完美平衡的 ,对

于 5 bit的 32种编码值也是不够的 。由于 4 bit和 6

bit的两个子分组都是偶数个位数 ,而不平衡度不可

能是“ + 1”或“ - 1”,因此 ,在 8B /10B 编码方案中

还要使用不平衡度为“ + 2”和“ - 2”的值 。在编码

过程中 ,用一个极性偏差 ( running disparity, RD )参

数表示不平衡度 ,在不平衡时用 2 个 10 bit字符表

示一个 8位字符 ,其中一个称为 RD - ,表示“1”的

个数比“0”的个数多 2个 ,另一个称为 RD + ,表示

“0”的个数比“1”的个数多 2个 。

8B /10B编码方法是把 8 bit代码组合编码成 10

bit代码 ,代码组合包含 256 个数据字符编码和 12

个控制字符编码 ,分别记为 Dx. y和 Kx. y。

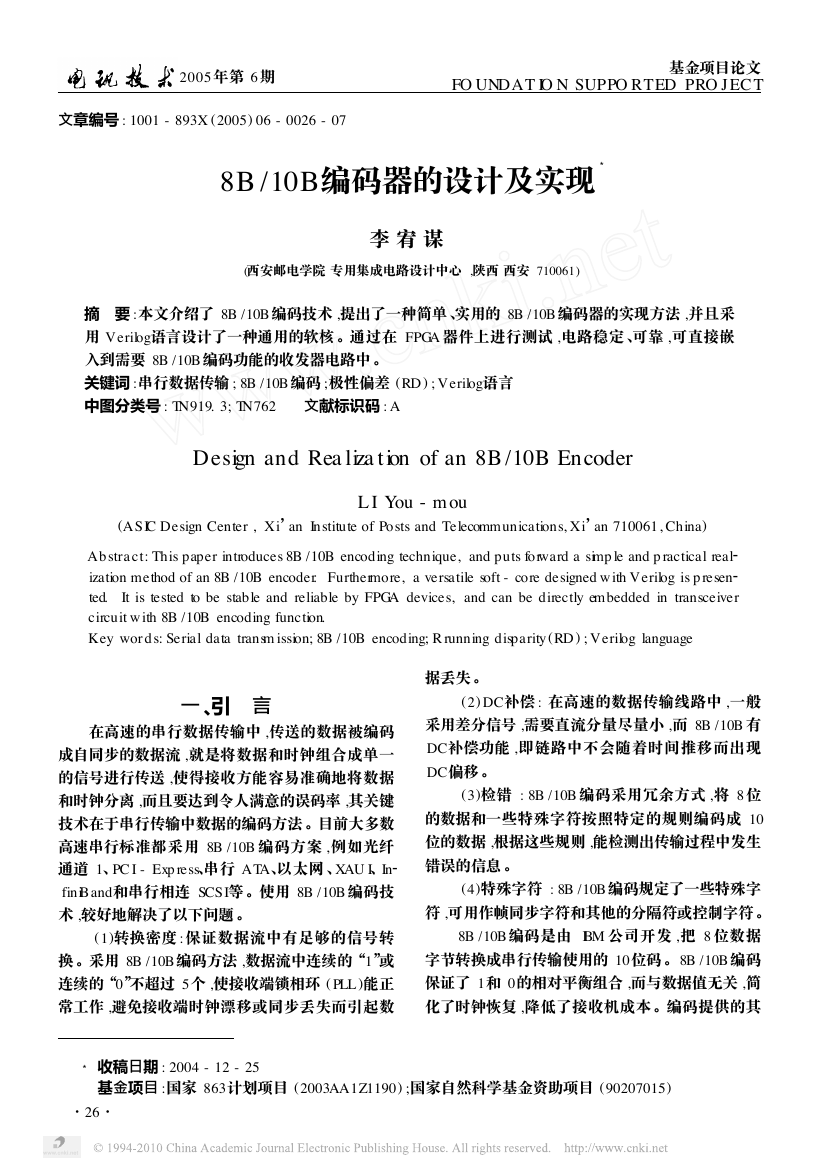

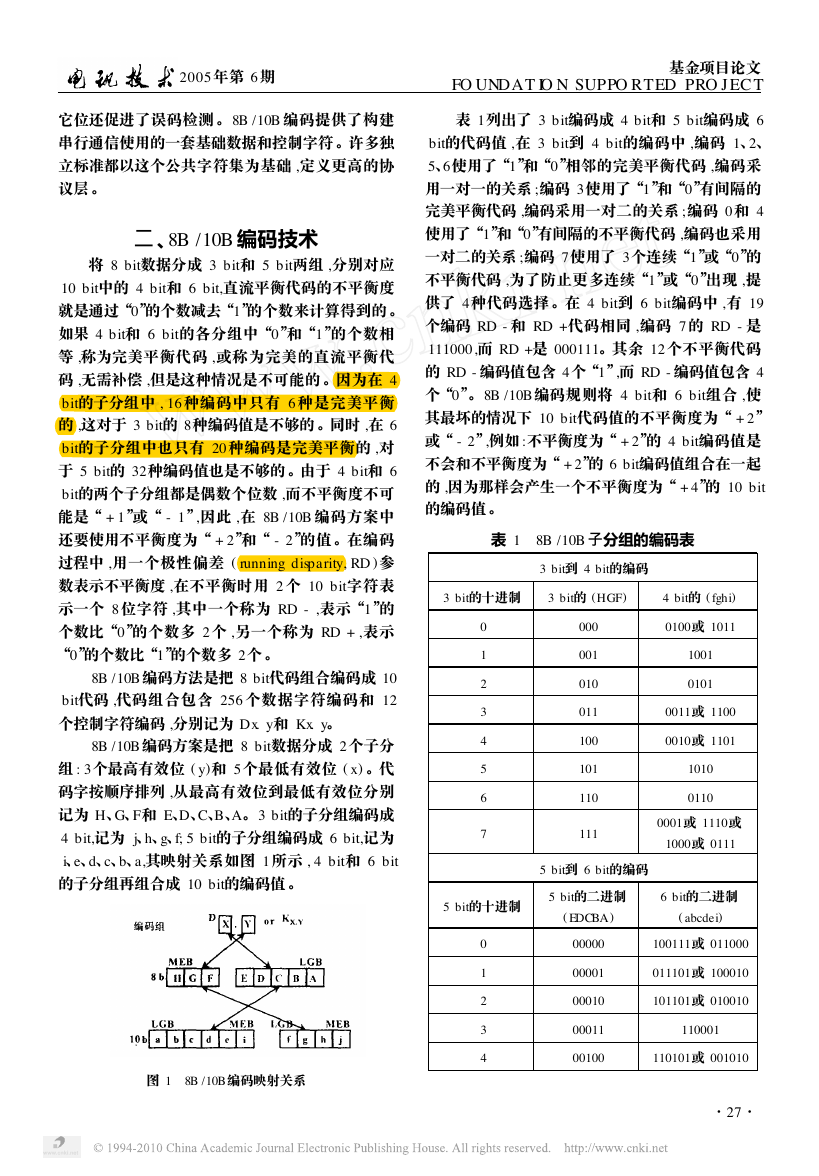

8B /10B编码方案是把 8 bit数据分成 2个子分

组 : 3个最高有效位 ( y)和 5个最低有效位 ( x) 。代

码字按顺序排列 ,从最高有效位到最低有效位分别

记为 H、G、F和 E、D、C、B、A。3 bit的子分组编码成

4 bit,记为 j、h、g、f; 5 bit的子分组编码成 6 bit,记为

i、e、d、c、b、a,其映射关系如图 1所示 , 4 bit和 6 bit

的子分组再组合成 10 bit的编码值 。

图 1 8B /10B编码映射关系

基金项目论文

FO UNDAT IO N SUPPO RTED PRO JECT

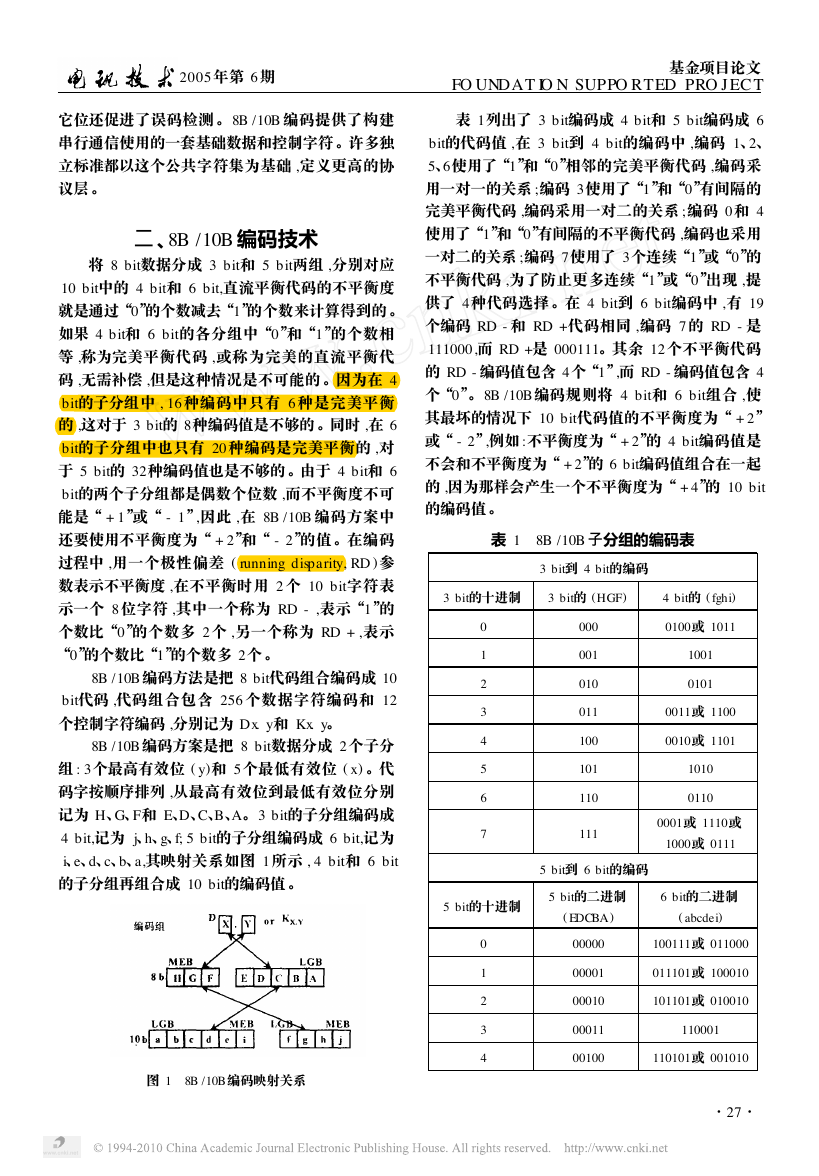

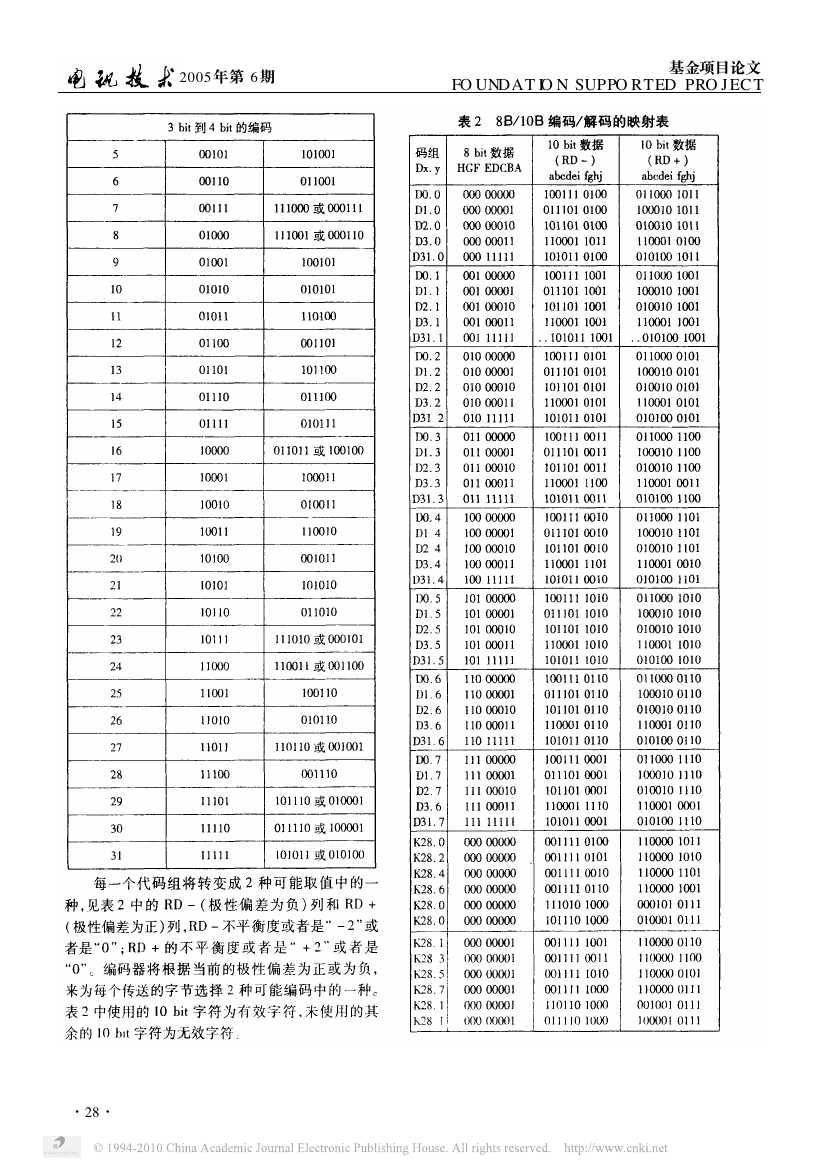

表 1列出了 3 bit编码成 4 bit和 5 bit编码成 6

bit的代码值 ,在 3 bit到 4 bit的编码中 ,编码 1、2、

5、6使用了“1”和“0”相邻的完美平衡代码 ,编码采

用一对一的关系 ;编码 3使用了“1”和“0”有间隔的

完美平衡代码 ,编码采用一对二的关系 ;编码 0和 4

使用了“1”和“0”有间隔的不平衡代码 ,编码也采用

一对二的关系 ;编码 7使用了 3个连续“1”或“0”的

不平衡代码 ,为了防止更多连续“1”或“0”出现 ,提

供了 4种代码选择 。在 4 bit到 6 bit编码中 ,有 19

个编码 RD - 和 RD +代码相同 ,编码 7 的 RD - 是

111000,而 RD +是 000111。其余 12个不平衡代码

的 RD - 编码值包含 4个“1”,而 RD - 编码值包含 4

个“0”。8B /10B编码规则将 4 bit和 6 bit组合 ,使

其最坏的情况下 10 bit代码值的不平衡度为“ + 2”

或“ - 2”,例如 :不平衡度为“ + 2”的 4 bit编码值是

不会和不平衡度为“ + 2”的 6 bit编码值组合在一起

的 ,因为那样会产生一个不平衡度为“ + 4”的 10 bit

的编码值 。

表 1 8B /10B 子分组的编码表

3 bit到 4 bit的编码

3 bit的十进制

3 bit的 (HGF)

4 bit的 ( fghi)

0

1

2

3

4

5

6

7

000

001

010

011

100

101

110

111

0100或 1011

1001

0101

0011或 1100

0010或 1101

1010

0110

0001或 1110或

1000或 0111

5 bit到 6 bit的编码

5 bit的十进制

5 bit的二进制

6 bit的二进制

( EDCBA)

( abcdei)

0

1

2

3

4

00000

00001

00010

00011

00100

100111或 011000

011101或 100010

101101或 010010

110001

110101或 001010

·72·

�

2005 年第 6 期

基金项目论文

FO UNDAT IO N SUPPO RTED PRO JECT

·82·

�

2005 年第 6 期

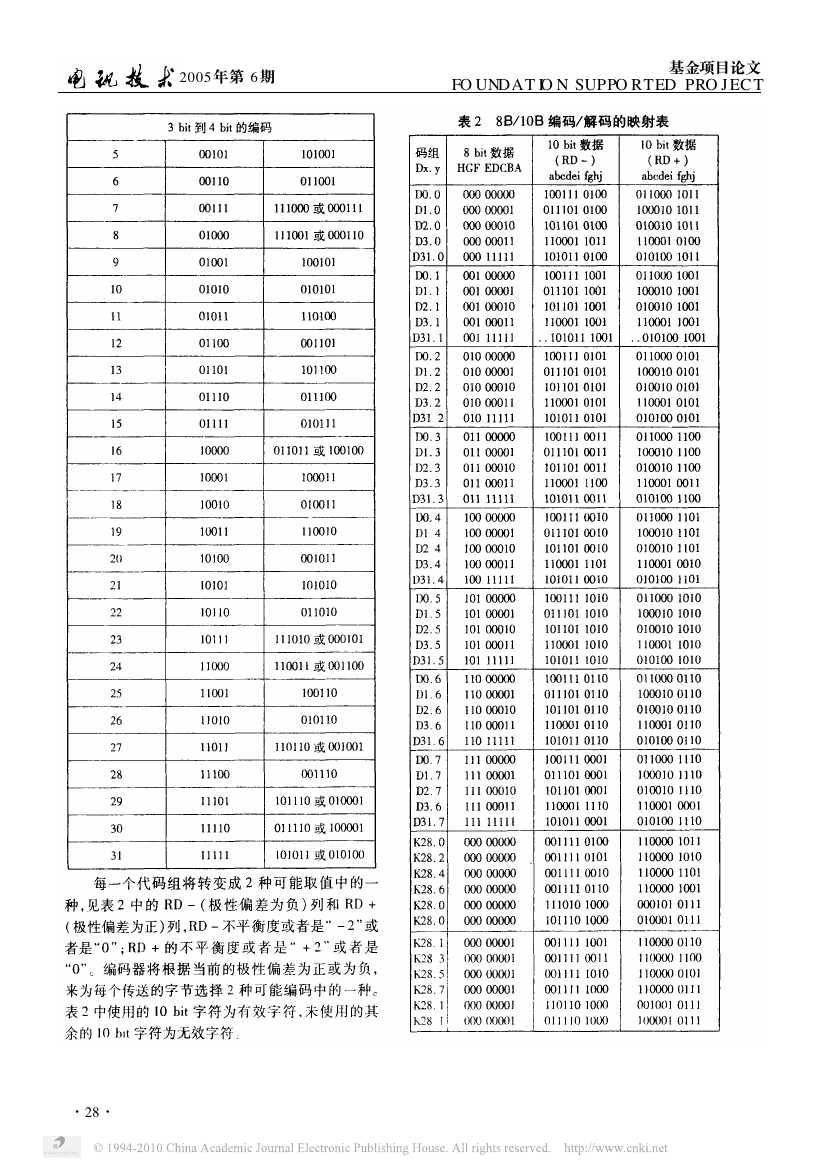

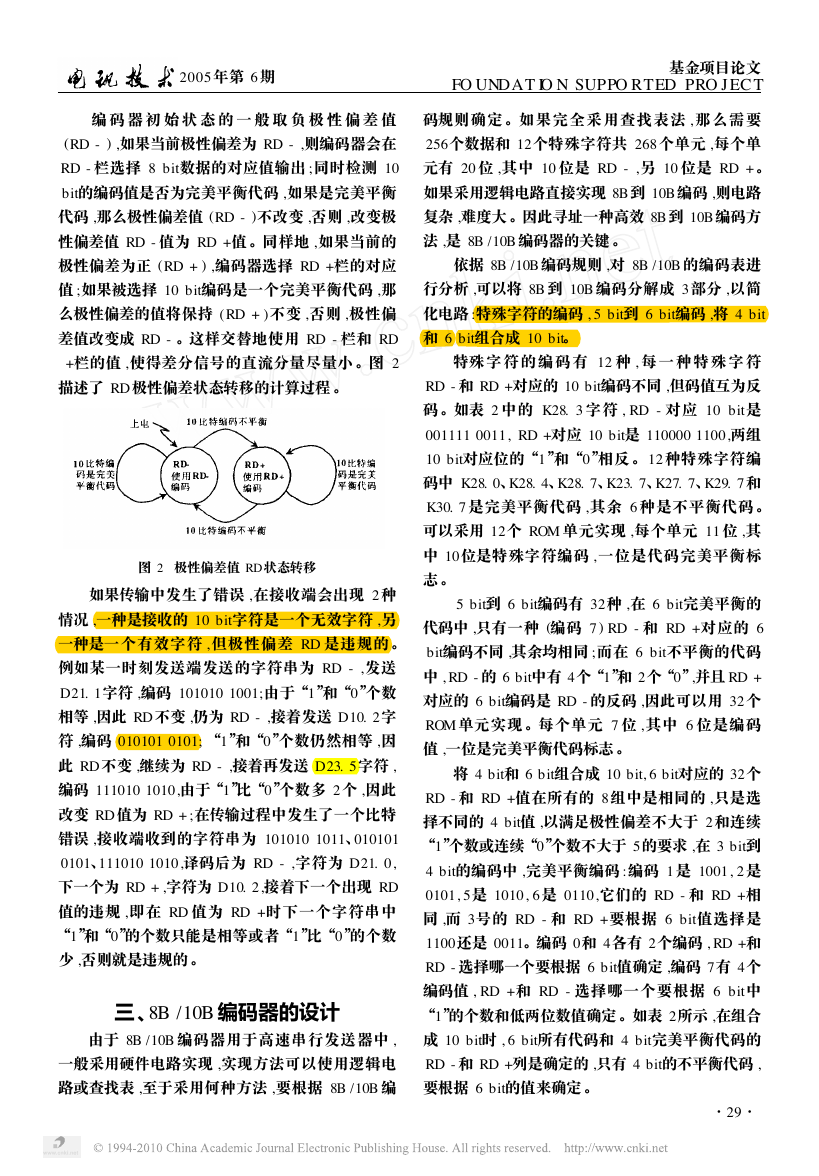

编 码 器 初 始 状 态 的 一 般 取 负 极 性 偏 差 值

(RD - ) ,如果当前极性偏差为 RD - ,则编码器会在

RD - 栏选择 8 bit数据的对应值输出 ;同时检测 10

bit的编码值是否为完美平衡代码 ,如果是完美平衡

代码 ,那么极性偏差值 (RD - )不改变 ,否则 ,改变极

性偏差值 RD - 值为 RD +值 。同样地 ,如果当前的

极性偏差为正 (RD + ) ,编码器选择 RD +栏的对应

值 ;如果被选择 10 bit编码是一个完美平衡代码 ,那

么极性偏差的值将保持 (RD + )不变 ,否则 ,极性偏

差值改变成 RD - 。这样交替地使用 RD - 栏和 RD

+栏的值 ,使得差分信号的直流分量尽量小 。图 2

描述了 RD极性偏差状态转移的计算过程 。

图 2 极性偏差值 RD状态转移

如果传输中发生了错误 ,在接收端会出现 2 种

情况 ,一种是接收的 10 bit字符是一个无效字符 ,另

一种是一个有效字符 ,但极性偏差 RD 是违规的 。

例如某一时刻发送端发送的字符串为 RD - ,发送

D21. 1字符 ,编码 101010 1001;由于“1”和“0”个数

相等 ,因此 RD不变 ,仍为 RD - ,接着发送 D10. 2字

符 ,编码 010101 0101; “1”和“0”个数仍然相等 ,因

此 RD不变 ,继续为 RD - ,接着再发送 D23. 5字符 ,

编码 111010 1010,由于“1”比“0”个数多 2个 ,因此

改变 RD值为 RD + ;在传输过程中发生了一个比特

错误 ,接收端收到的字符串为 101010 1011、010101

0101、111010 1010,译码后为 RD - ,字符为 D21. 0,

下一个为 RD + ,字符为 D10. 2,接着下一个出现 RD

值的违规 ,即在 RD 值为 RD +时下一个字符串中

“1”和“0”的个数只能是相等或者“1”比“0”的个数

少 ,否则就是违规的 。

三 、8B /10B 编码器的设计

由于 8B /10B 编码器用于高速串行发送器中 ,

一般采用硬件电路实现 ,实现方法可以使用逻辑电

路或查找表 ,至于采用何种方法 ,要根据 8B /10B 编

基金项目论文

FO UNDAT IO N SUPPO RTED PRO JECT

码规则确定 。如果完全采用查找表法 , 那么需要

256个数据和 12个特殊字符共 268个单元 ,每个单

元有 20 位 ,其中 10 位是 RD - ,另 10 位是 RD +。

如果采用逻辑电路直接实现 8B到 10B编码 ,则电路

复杂 ,难度大 。因此寻址一种高效 8B到 10B编码方

法 ,是 8B /10B 编码器的关键 。

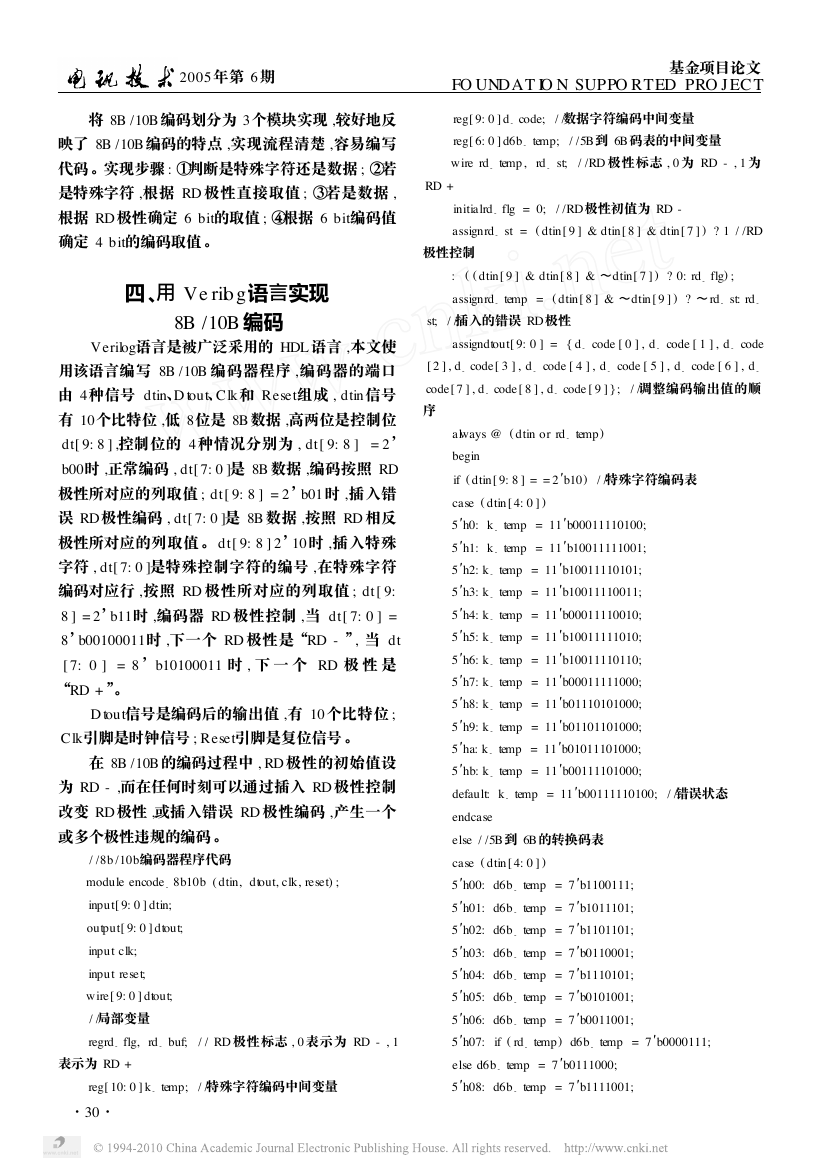

依据 8B /10B 编码规则 ,对 8B /10B 的编码表进

行分析 ,可以将 8B 到 10B 编码分解成 3部分 ,以简

化电路 :特殊字符的编码 , 5 bit到 6 bit编码 ,将 4 bit

和 6 bit组合成 10 bit。

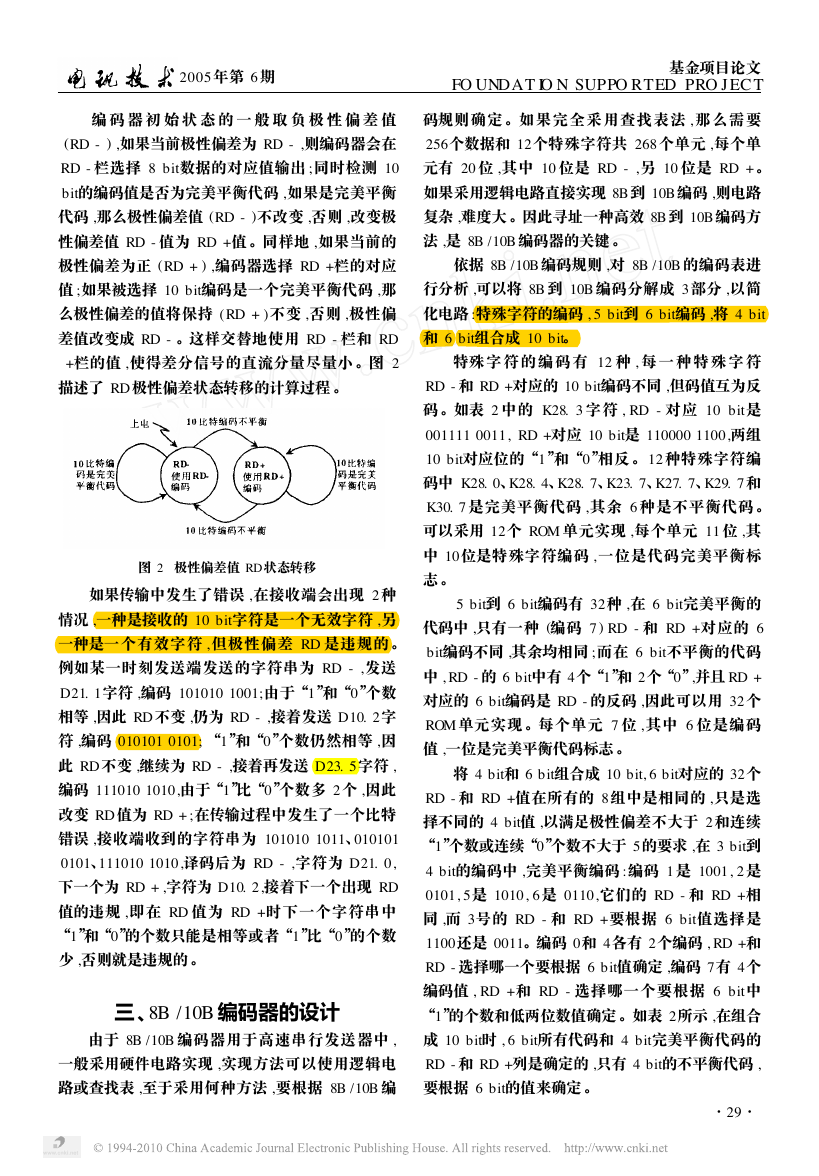

特殊 字 符 的 编 码 有 12 种 , 每 一 种 特 殊 字 符

RD - 和 RD +对应的 10 bit编码不同 ,但码值互为反

码 。如表 2 中的 K28. 3 字符 , RD - 对应 10 bit是

001111 0011, RD +对应 10 bit是 110000 1100,两组

10 bit对应位的“1”和“0”相反 。12 种特殊字符编

码中 K28. 0、K28. 4、K28. 7、K23. 7、K27. 7、K29. 7和

K30. 7 是完美平衡代码 ,其余 6 种是不平衡代码 。

可以采用 12个 ROM 单元实现 ,每个单元 11 位 ,其

中 10位是特殊字符编码 ,一位是代码完美平衡标

志 。

5 bit到 6 bit编码有 32种 ,在 6 bit完美平衡的

代码中 ,只有一种 (编码 7 ) RD - 和 RD +对应的 6

bit编码不同 ,其余均相同 ;而在 6 bit不平衡的代码

中 , RD - 的 6 bit中有 4个“1”和 2个“0”,并且 RD +

对应的 6 bit编码是 RD - 的反码 ,因此可以用 32个

ROM 单元实现 。每个单元 7 位 , 其中 6 位是编码

值 ,一位是完美平衡代码标志 。

将 4 bit和 6 bit组合成 10 bit, 6 bit对应的 32个

RD - 和 RD +值在所有的 8组中是相同的 ,只是选

择不同的 4 bit值 ,以满足极性偏差不大于 2和连续

“1”个数或连续“0”个数不大于 5的要求 ,在 3 bit到

4 bit的编码中 ,完美平衡编码 :编码 1 是 1001, 2是

0101, 5是 1010, 6是 0110,它们的 RD - 和 RD +相

同 ,而 3号的 RD - 和 RD +要根据 6 bit值选择是

1100还是 0011。编码 0和 4各有 2个编码 , RD +和

RD - 选择哪一个要根据 6 bit值确定 ,编码 7有 4个

编码值 , RD +和 RD - 选择哪一个要根据 6 bit中

“1”的个数和低两位数值确定 。如表 2所示 ,在组合

成 10 bit时 , 6 bit所有代码和 4 bit完美平衡代码的

RD - 和 RD +列是确定的 ,只有 4 bit的不平衡代码 ,

要根据 6 bit的值来确定 。

·92·

�

2005 年第 6 期

基金项目论文

FO UNDAT IO N SUPPO RTED PRO JECT

将 8B /10B 编码划分为 3个模块实现 ,较好地反

映了 8B /10B 编码的特点 ,实现流程清楚 ,容易编写

代码 。实现步骤 : ①判断是特殊字符还是数据 ; ②若

是特殊字符 ,根据 RD 极性直接取值 ; ③若是数据 ,

根据 RD极性确定 6 bit的取值 ; ④根据 6 bit编码值

确定 4 bit的编码取值 。

四 、用 Ve rilo g语言实现

8B /10B 编码

Verilog语言是被广泛采用的 HDL 语言 ,本文使

用该语言编写 8B /10B 编码器程序 ,编码器的端口

由 4种信号 dtin、D tout、Clk和 Reset组成 , dtin信号

有 10个比特位 ,低 8位是 8B 数据 ,高两位是控制位

dt[ 9: 8 ] ,控制位的 4 种情况分别为 , dt[ 9: 8 ] = 2’

b00时 ,正常编码 , dt[ 7: 0 ]是 8B 数据 ,编码按照 RD

极性所对应的列取值 ; dt[ 9: 8 ] = 2’b01 时 ,插入错

误 RD极性编码 , dt[ 7: 0 ]是 8B 数据 ,按照 RD 相反

极性所对应的列取值 。 dt[ 9: 8 ] 2’10 时 ,插入特殊

字符 , dt[ 7: 0 ]是特殊控制字符的编号 ,在特殊字符

编码对应行 ,按照 RD 极性所对应的列取值 ; dt [ 9:

8 ] = 2’b11时 ,编码器 RD 极性控制 ,当 dt[ 7: 0 ] =

8’b00100011时 ,下一个 RD 极性是“RD - ”, 当 dt

[ 7: 0 ] = 8 ’b10100011 时 , 下 一 个 RD 极 性 是

“RD + ”。

D tout信号是编码后的输出值 ,有 10个比特位 ;

Clk引脚是时钟信号 ; Reset引脚是复位信号 。

在 8B /10B的编码过程中 , RD 极性的初始值设

为 RD - ,而在任何时刻可以通过插入 RD 极性控制

改变 RD极性 ,或插入错误 RD 极性编码 ,产生一个

或多个极性违规的编码 。

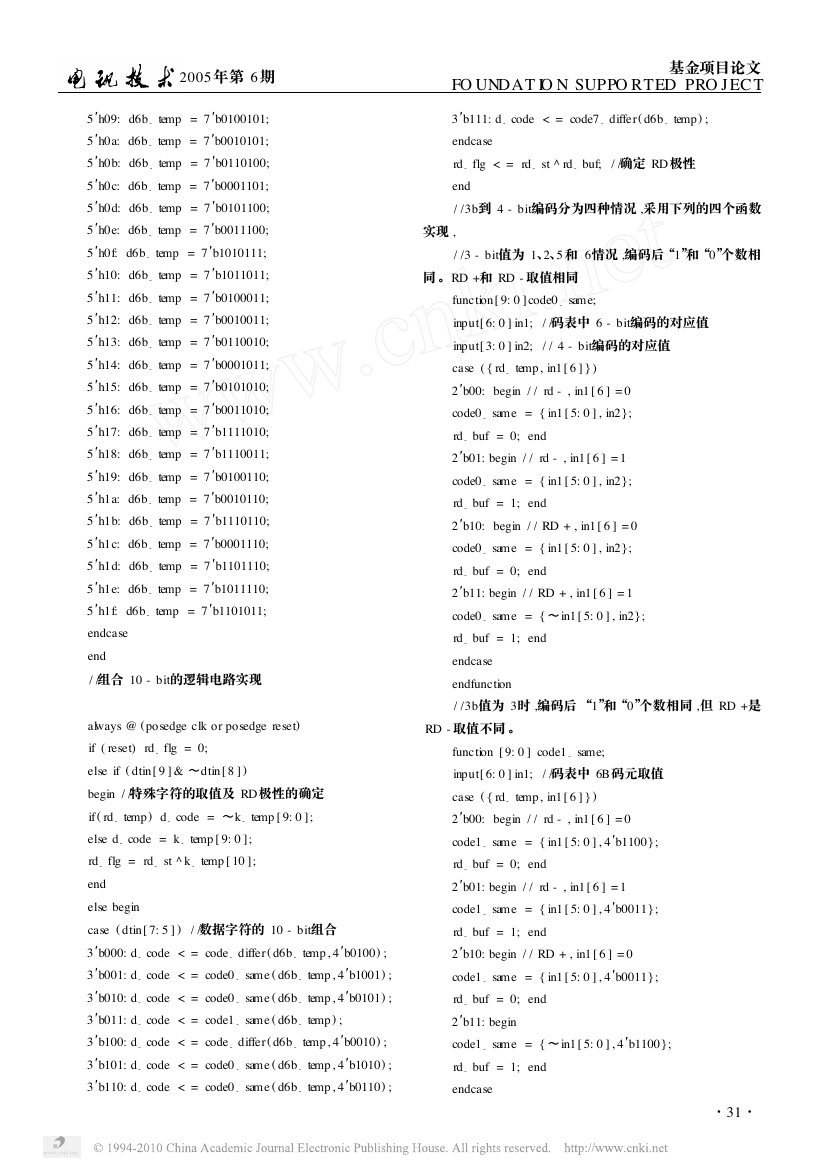

/ /8b /10b编码器程序代码

module encode - 8b10b ( dtin, dtout, clk, reset) ;

input[ 9: 0 ] dtin;

output[ 9: 0 ] dtout;

input clk;

input reset;

wire[ 9: 0 ] dtout;

/ /局部变量

regrd - flg,

表示为 RD +

rd - buf;

/ / RD 极性标志 , 0 表示为 RD - , 1

reg[ 10: 0 ] k - temp;

/ /特殊字符编码中间变量

·03·

reg[ 9: 0 ] d - code;

reg[ 6: 0 ] d6b - temp;

wire rd - temp,

rd - st;

/ /数据字符编码中间变量

/ /5B到 6B码表的中间变量

/ /RD 极性标志 , 0 为 RD - , 1 为

RD +

initialrd - flg = 0;

assignrd - st = ( dtin[ 9 ] & dtin[ 8 ] & dtin[ 7 ] ) ? 1 / /RD

/ /RD极性初值为 RD -

极性控制

( ( dtin[ 9 ] & dtin[ 8 ] & ~dtin[ 7 ] ) ? 0: rd - flg) ;

:

assignrd - temp = ( dtin[ 8 ] & ~dtin[ 9 ] ) ? ~rd - st: rd -

/ /插入的错误 RD极性

st;

assigndtout[ 9: 0 ] = { d - code [ 0 ] , d - code [ 1 ] , d - code

[ 2 ] , d - code[ 3 ] , d - code [ 4 ] , d - code [ 5 ] , d - code [ 6 ] , d -

/ /调整编码输出值的顺

code[ 7 ] , d - code[ 8 ] , d - code [ 9 ] };

序

always @ ( dtin or rd - temp)

begin

if ( dtin[ 9: 8 ] = = 2′b10)

/ /特殊字符编码表

case ( dtin[ 4: 0 ] )

5′h0: k - temp = 11′b00011110100;

5′h1: k - temp = 11′b10011111001;

5′h2: k - temp = 11′b10011110101;

5′h3: k - temp = 11′b10011110011;

5′h4: k - temp = 11′b00011110010;

5′h5: k - temp = 11′b10011111010;

5′h6: k - temp = 11′b10011110110;

5′h7: k - temp = 11′b00011111000;

5′h8: k - temp = 11′b01110101000;

5′h9: k - temp = 11′b01101101000;

5′ha: k - temp = 11′b01011101000;

5′hb: k - temp = 11′b00111101000;

default: k - temp = 11′b00111110100;

endcase

else / /5B到 6B的转换码表

/ /错误状态

case ( dtin[ 4: 0 ] )

5′h00: d6b - temp = 7′b1100111;

5′h01: d6b - temp = 7′b1011101;

5′h02: d6b - temp = 7′b1101101;

5′h03: d6b - temp = 7′b0110001;

5′h04: d6b - temp = 7′b1110101;

5′h05: d6b - temp = 7′b0101001;

5′h06: d6b - temp = 7′b0011001;

5′h07:

else d6b - temp = 7′b0111000;

5′h08: d6b - temp = 7′b1111001;

if ( rd - temp) d6b - temp = 7′b0000111;

�

2005 年第 6 期

5′h09: d6b - temp = 7′b0100101;

5′h0a: d6b - temp = 7′b0010101;

5′h0b: d6b - temp = 7′b0110100;

5′h0c: d6b - temp = 7′b0001101;

5′h0d: d6b - temp = 7′b0101100;

5′h0e: d6b - temp = 7′b0011100;

5′h0f: d6b - temp = 7′b1010111;

5′h10: d6b - temp = 7′b1011011;

5′h11: d6b - temp = 7′b0100011;

5′h12: d6b - temp = 7′b0010011;

5′h13: d6b - temp = 7′b0110010;

5′h14: d6b - temp = 7′b0001011;

5′h15: d6b - temp = 7′b0101010;

5′h16: d6b - temp = 7′b0011010;

5′h17: d6b - temp = 7′b1111010;

5′h18: d6b - temp = 7′b1110011;

5′h19: d6b - temp = 7′b0100110;

5′h1a: d6b - temp = 7′b0010110;

5′h1b: d6b - temp = 7′b1110110;

5′h1c: d6b - temp = 7′b0001110;

5′h1d: d6b - temp = 7′b1101110;

5′h1e: d6b - temp = 7′b1011110;

5′h1f: d6b - temp = 7′b1101011;

endcase

end

/ /组合 10 - bit的逻辑电路实现

always @ (posedge clk or posedge reset)

rd - flg = 0;

if ( reset)

else if ( dtin[ 9 ] & ~dtin[ 8 ] )

begin / /特殊字符的取值及 RD极性的确定

if( rd - temp) d - code = ~k - temp [ 9: 0 ];

else d - code = k - temp [ 9: 0 ];

rd - flg = rd - st ^ k - temp [ 10 ];

end

else begin

/ /数据字符的 10 - bit组合

case ( dtin[ 7: 5 ] )

3′b000: d - code < = code - differ( d6b - temp, 4′b0100) ;

3′b001: d - code < = code0 - same ( d6b - temp, 4′b1001) ;

3′b010: d - code < = code0 - same ( d6b - temp, 4′b0101) ;

3′b011: d - code < = code1 - same ( d6b - temp) ;

3′b100: d - code < = code - differ( d6b - temp, 4′b0010) ;

3′b101: d - code < = code0 - same ( d6b - temp, 4′b1010) ;

3′b110: d - code < = code0 - same ( d6b - temp, 4′b0110) ;

基金项目论文

FO UNDAT IO N SUPPO RTED PRO JECT

3′b111: d - code < = code7 - differ( d6b - temp) ;

endcase

rd - flg < = rd - st ^ rd - buf;

end

/ /3b到 4 - bit编码分为四种情况 ,采用下列的四个函数

/ /确定 RD极性

实现 ,

/ /3 - bit值为 1、2、5 和 6情况 ,编码后“1”和“0”个数相

同 。RD +和 RD - 取值相同

function[ 9: 0 ] code0 - same;

input[ 6: 0 ] in1;

input[ 3: 0 ] in2;

case ( { rd - temp, in1 [ 6 ] } )

2′b00: begin / / rd - , in1 [ 6 ] = 0

/ /码表中 6 - bit编码的对应值

/ / 4 - bit编码的对应值

code0 - same = { in1 [ 5: 0 ] , in2};

rd - buf = 0; end

2′b01: begin / / rd - , in1 [ 6 ] = 1

code0 - same = { in1 [ 5: 0 ] , in2};

rd - buf = 1; end

2′b10: begin / / RD + , in1 [ 6 ] = 0

code0 - same = { in1 [ 5: 0 ] , in2};

rd - buf = 0; end

2′b11: begin / / RD + , in1 [ 6 ] = 1

code0 - same = { ~in1 [ 5: 0 ] , in2};

rd - buf = 1; end

endcase

endfunction

/ /3b值为 3时 ,编码后 “1”和“0”个数相同 ,但 RD +是

RD - 取值不同 。

/ /码表中 6B码元取值

function [ 9: 0 ] code1 - same;

input[ 6: 0 ] in1;

case ( { rd - temp, in1 [ 6 ] } )

2′b00: begin / / rd - , in1 [ 6 ] = 0

code1 - same = { in1 [ 5: 0 ] , 4′b1100};

rd - buf = 0; end

2′b01: begin / / rd - , in1 [ 6 ] = 1

code1 - same = { in1 [ 5: 0 ] , 4′b0011};

rd - buf = 1; end

2′b10: begin / / RD + , in1 [ 6 ] = 0

code1 - same = { in1 [ 5: 0 ] , 4′b0011};

rd - buf = 0; end

2′b11: begin

code1 - same = { ~in1 [ 5: 0 ] , 4′b1100};

rd - buf = 1; end

endcase

·13·

�

2005 年第 6 期

基金项目论文

FO UNDAT IO N SUPPO RTED PRO JECT

else code7 - differ = { in1 [ 5: 0 ] , 4′b0001};

rd - buf = 1; end

2′b11: begin

code7 - differ = { ~in1 [ 5: 0 ] , 4′b1110};

rd - buf = 0; end

endcase

endfunction

endmodule

五 、结束语

8B /10B 编码器是我们设计 SDH 交换芯片的组

成部分 ,在设计中对 8B /10B 编码器进行了功能仿

真 、综合 、时序仿真 ,并在 FPGA 器件上进行测试 。

它可以作为软核嵌入到需要 8B /10B 编码器的电路

设计中 ,也可以作为测试 8B /10B 解码器电路的工

具软核 。

参考文献

[ 1 ] A X W IDMER, P A FRANASZEK. A DC - Balanced,

Partitioned - B lock, 8B / 10B Transm ission Code [ J ].

IBM J. RES. DEVELOP, 1983, 27 (5).

[ 2 ] CYPRESS CY7B923 HOTL INK Transm itter/ Receiver.

CY7B923 HOTL ink datasheet[ Z ]. Cyp ress Sem iconduc

tor Corporation, 2003.

[ 3 ] Actel Corporation.

Imp lementing an 8b /10b Encoder/De

coder for Gigabit Ethernet in the Actel SX FPGA Fam ily

[ EB /OL ]. http: / /www. actel. com / documents/5192650

- 0. pdf, 1998 - 10.

作者简介 :

李宥谋 (1959 - ) ,男 ,陕西西安人 ,副

教授 ,主要研究方向是通信和集成电路设

计 。

endfunction

/ /3b值为 0 和 4, 编码后 “1 ”和“0 ”个数不相同 , 而

RD +和 RD - 取值互为反码情况 。

function[ 9: 0 ] code - differ;

input[ 6: 0 ] in1;

/ / 6B编码取值

/ /4B编码取值

input[ 3: 0 ] in2;

case ( { rd - temp, in1 [ 6 ] } )

2′b00: begin / / rd - , d6b - temp [ 6 ] = 0

code - differ = { in1 [ 5: 0 ] , ~in2};

rd - buf = 1; end

2′b01: begin / / rd - , d6b - temp [ 6 ] = 1

code - differ = { in1 [ 5: 0 ] , in2};

rd - buf = 0; end

2′b10: begin / / RD + , d6b - temp [ 6 ] = 0

code - differ = { in1 [ 5: 0 ] , in2};

rd - buf = 1; end

2′b11: begin / / RD + , d6b - temp [ 6 ] = 1

code - differ = { ~in1 [ 5: 0 ] , ~in2};

rd - buf = 0; end

endcase

endfunction

/ / 3b值为 7时 ,编码后“1”和“0”个数不相同 ,有 4种选

择 ,见表 1。

/ / 6B码元取值

function[ 9: 0 ] code7 - differ;

input[ 6: 0 ] in1;

case ( { rd - temp, in1 [ 6 ] } )

2′b00: begin / / rd - , d6b - temp [ 6 ] = 0

if ( in1 [ 0 ] & in1 [ 1 ] )

code7 - differ = { in1 [ 5: 0 ] , 4′b0111};

else code7 - differ = { in1 [ 5: 0 ] , 4′b1110};

rd - buf = 1; end

2′b01: begin

code7 - differ = { in1 [ 5: 0 ] , 4′b0001};

rd - buf = 0; end

2′b10: begin / / RD + , d6b - temp [ 6 ] = 0

if ( ~ ( in1 [ 0 ] |

code7 - differ = { in1 [ 5: 0 ] , 4′b1000};

in1 [ 1 ] ) )

·23·

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc