CS1231

用户手册

深深圳圳市市芯芯海海科科技技

CS1231 用户手册

REV 1.4

通讯地址:深圳市南山区蛇口南海大道 1079 号花园城数码大厦 A 座 9 楼

邮政编码:518067

公司电话:+(86 755)86169257

传 真:+(86 755)86169057

公司网站:www.chipsea.com

DocID20120709 Rev1

1/20

www.chipsea.com

�

CS1231

目 录

目录

2.1

2.2

2.3

2.4

2.5

1.1

1.2

1.3

1.4

1.5

1.6

1.7

1.8

1 芯片功能说明...........................................................................................................................4

芯片主要功能特性...................................................................................................4

芯片应用场合...........................................................................................................4

芯片基本结构功能描述...........................................................................................5

芯片绝对最大极限值...............................................................................................6

CS1231 数字逻辑特性.............................................................................................7

CS1231 电气特性 .....................................................................................................8

噪声性能.................................................................................................................10

芯片引脚.................................................................................................................11

2 芯片功能模块描述.................................................................................................................12

模拟输入前端.........................................................................................................12

低噪声PGA放大器.................................................................................................13

时钟信号源.............................................................................................................14

复位和断电(POR&power down) ...........................................................................14

SPI串口通信...........................................................................................................15

2.5.1 输出速率.................................................................................................................16

2.5.2 数据格式.................................................................................................................16

2.5.3 数据准备/数据输入输出(

) .......................................................16

2.5.4 串行时钟输入(SCLK)............................................................................................16

2.5.5 数据接收.................................................................................................................17

2.5.6

Standby模式............................................................................................................18

2.5.7 上电顺序.................................................................................................................18

2.5.8

Power down模式.....................................................................................................18

3 芯片的封装.............................................................................................................................20

封装形式.................................................................................................................20

3.1.1 采用TSSOP-16 封装形式.......................................................................................20

3.1.2 采用SOP-16 封装形式 ...........................................................................................20

DRDY /

DOUT

3.1

DocID20120709 Rev1

2/20

www.chipsea.com

�

CS1231

目录

图 目 录

CS1231 原理框图 .....................................................................................................5

图 1

图 2

CS1231 芯片引脚图 ...............................................................................................11

图 3 模拟输入结构图.....................................................................................................12

图 4

PGA结构图.............................................................................................................13

CS1231 时钟信号 ...................................................................................................14

图 5

CS1231 读取数据时序图 .......................................................................................17

图 6

图 7

CS1231 读取数据时序图 .......................................................................................17

图 8

Standby模式时序图................................................................................................18

图 9 上电顺序图.............................................................................................................18

图 10

Power Down模式时序图........................................................................................19

图 11 芯片TSSOP-16 封装尺寸信息...............................................................................20

图 12 芯片SOP-16 封装尺寸信息 ...................................................................................20

表 目 录

CS1231 极限值.........................................................................................................6

表 1

CS1231 数字逻辑特性 .............................................................................................7

表 2

CS1231 电气特性(AVDD = DVDD = 5V)........................................................8

表 3

表 4

CS1231 电气特性(AVDD = DVDD = 3V)........................................................9

表 5 噪声性能表.............................................................................................................10

表 6

PIN脚说明 ..............................................................................................................11

表 7 输出速率设置.........................................................................................................16

表 8 理想输出码和输入信号(1)......................................................................................16

表 9 读取数据时序表.....................................................................................................17

Standby模式时序表................................................................................................18

表 10

表 11

Power Down模式时序表........................................................................................19

DocID20120709 Rev1

3/20

www.chipsea.com

�

CS1231

芯片主要功能特性

1 芯片功能说明

1.1 芯片主要功能特性

集成低噪声 PGA,放大倍数可选 64,128

集成 1 通道 24 位无失码的差分输入 ADC,PGA=128 时 ENOB 为 20.3 位

P-P 噪声:10Hz:183nV;80Hz:421nV

集成 RC 振荡器(±8%),可外接时钟输入

输出速率 10Hz/80Hz 可选

集成 2 线 SPI 通讯接口

INL 小于 0.001%

1.2 芯片应用场合

工业过程控制

电子秤

液体/气体化学分析

血液计

智能变换器

便携式设备

DocID20120709 Rev1

4/20

www.chipsea.com

�

CS1231

芯片基本结构功能

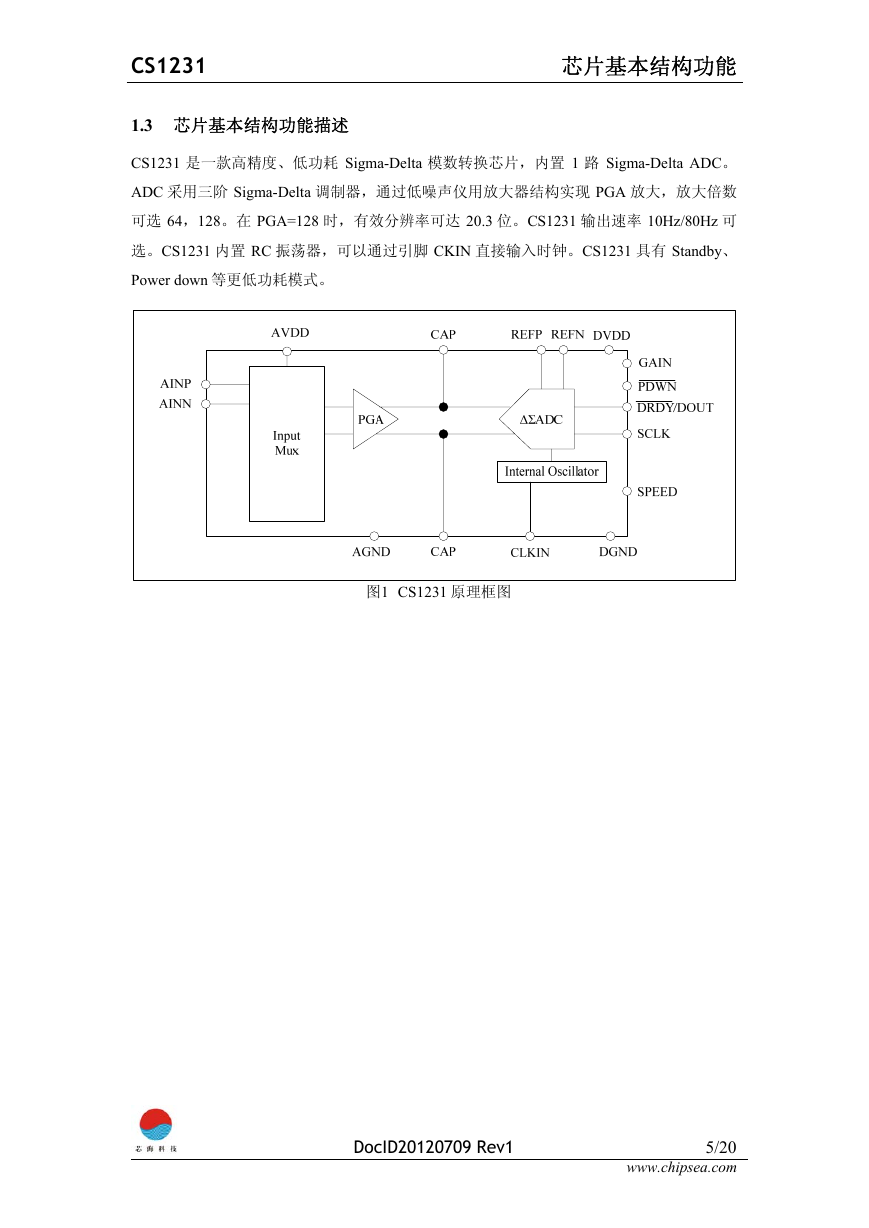

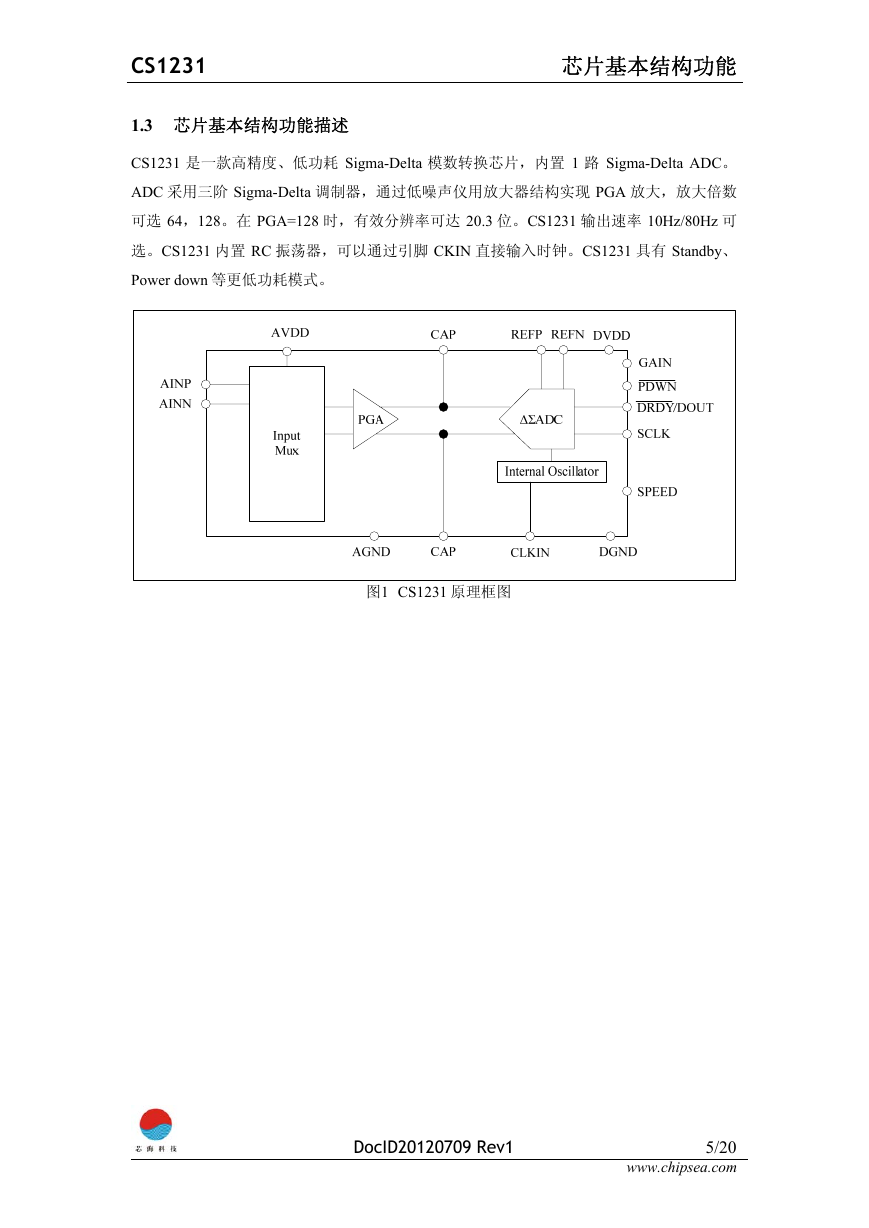

1.3 芯片基本结构功能描述

CS1231 是一款高精度、低功耗 Sigma-Delta 模数转换芯片,内置 1 路 Sigma-Delta ADC。

ADC 采用三阶 Sigma-Delta 调制器,通过低噪声仪用放大器结构实现 PGA 放大,放大倍数

可选 64,128。在 PGA=128 时,有效分辨率可达 20.3 位。CS1231 输出速率 10Hz/80Hz 可

选。CS1231 内置 RC 振荡器,可以通过引脚 CKIN 直接输入时钟。CS1231 具有 Standby、

Power down 等更低功耗模式。

图1 CS1231 原理框图

DocID20120709 Rev1

5/20

www.chipsea.com

�

CS1231

绝对最大极限值

表1 CS1231 极限值

符号

AVDD

DVDD

最小

-0.3

-0.3

-0.3

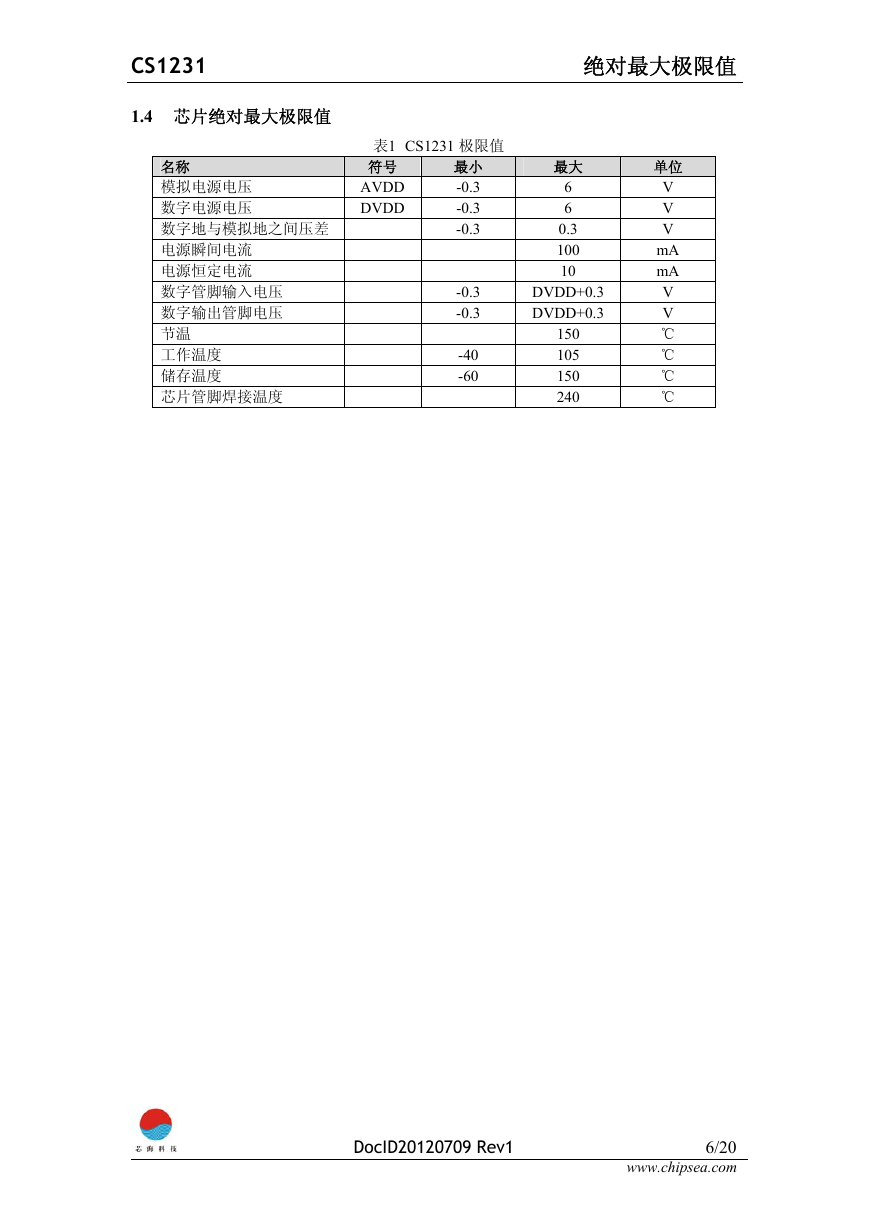

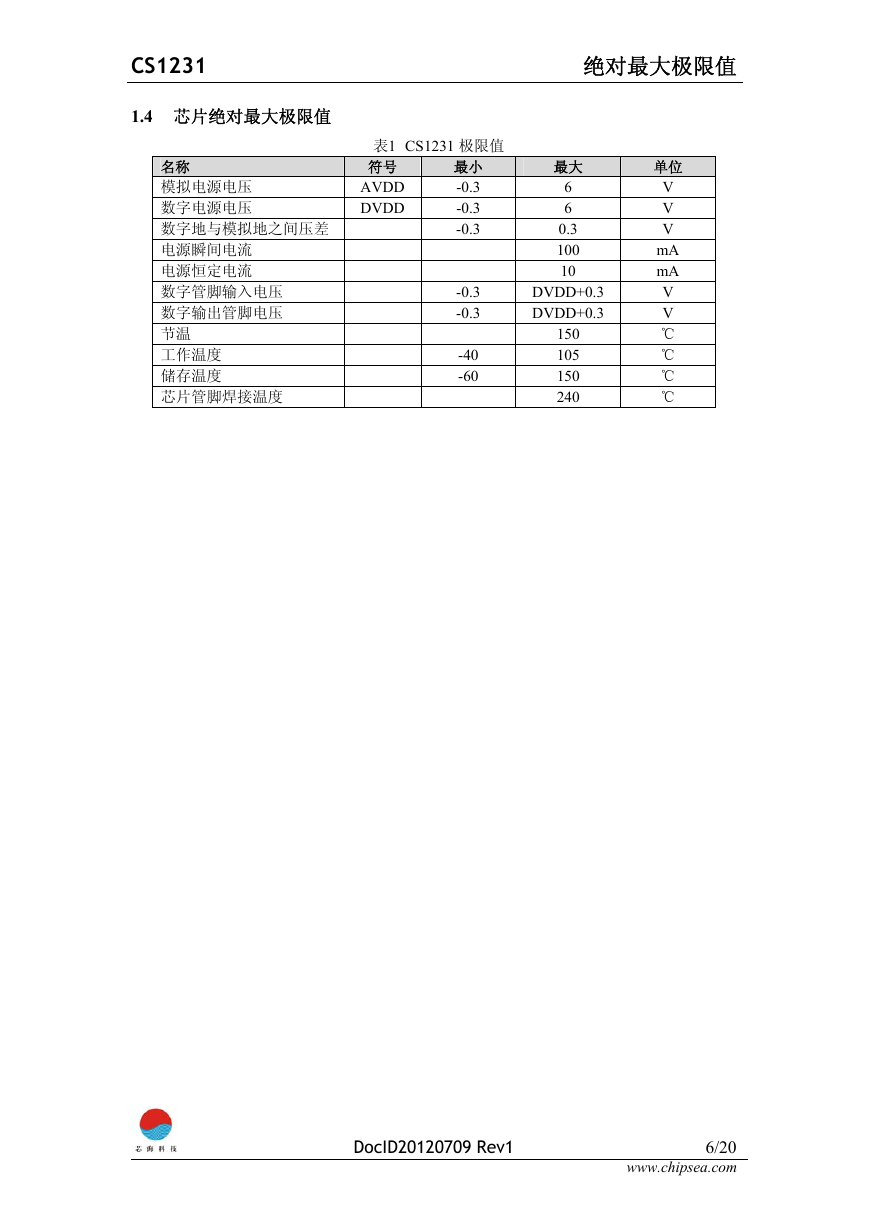

1.4 芯片绝对最大极限值

名称

模拟电源电压

数字电源电压

数字地与模拟地之间压差

电源瞬间电流

电源恒定电流

数字管脚输入电压

数字输出管脚电压

节温

工作温度

储存温度

芯片管脚焊接温度

最大

6

6

0.3

100

10

DVDD+0.3

DVDD+0.3

150

105

150

240

单位

V

V

V

mA

mA

V

V

℃

℃

℃

℃

-0.3

-0.3

-40

-60

DocID20120709 Rev1

6/20

www.chipsea.com

�

CS1231

数字逻辑特性

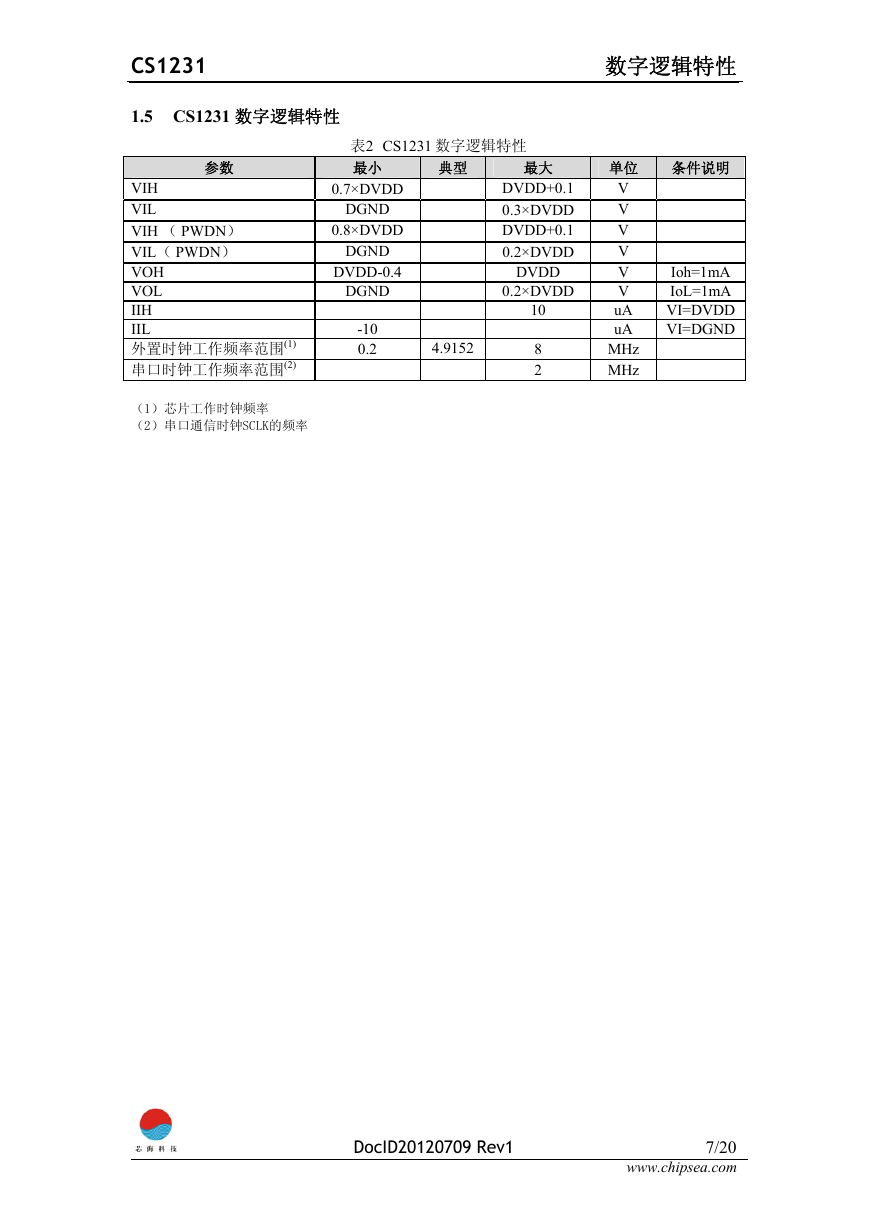

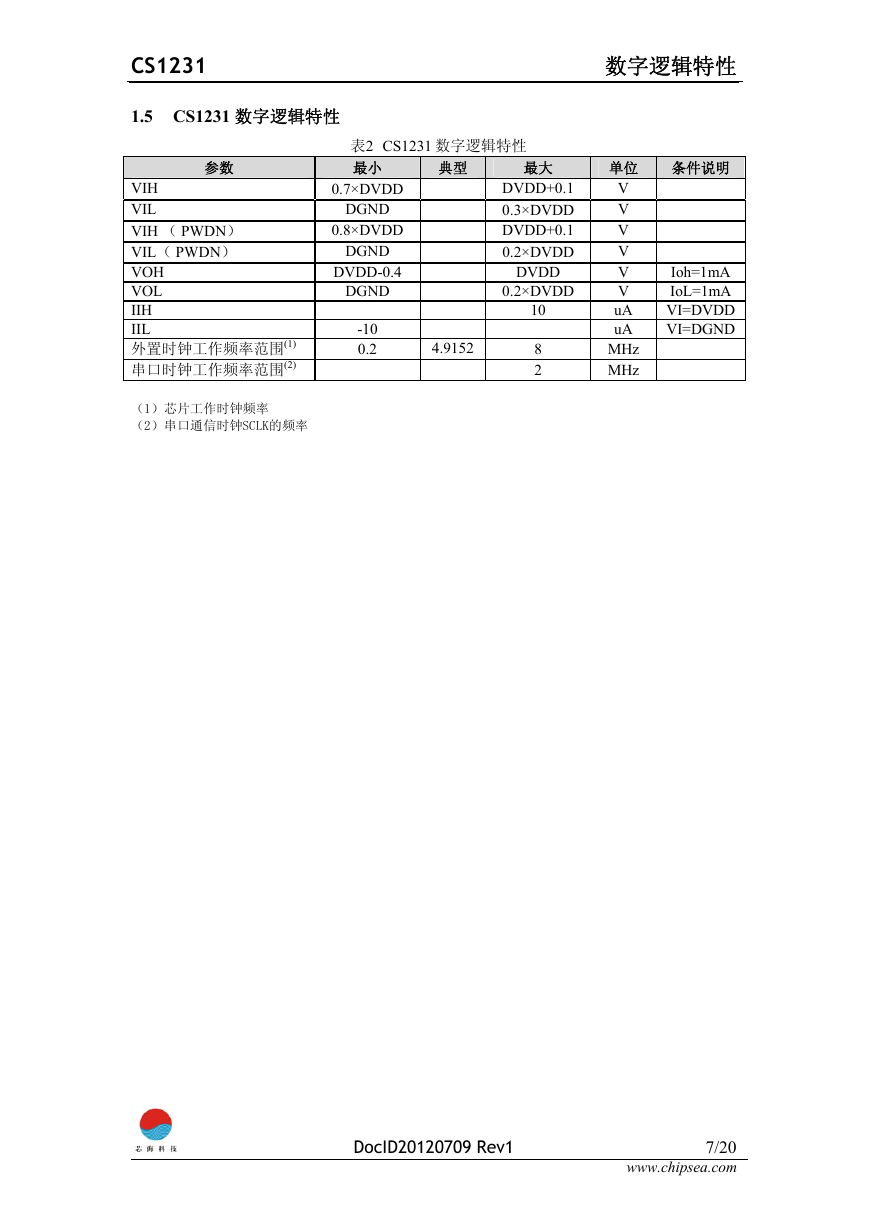

1.5 CS1231 数字逻辑特性

表2 CS1231 数字逻辑特性

最小

典型

最大

0.7×DVDD

DGND

0.8×DVDD

DGND

DVDD-0.4

DGND

-10

0.2

4.9152

DVDD+0.1

0.3×DVDD

DVDD+0.1

0.2×DVDD

DVDD

0.2×DVDD

10

8

2

单位 条件说明

V

V

V

V

V

V

uA

uA

MHz

MHz

Ioh=1mA

IoL=1mA

VI=DVDD

VI=DGND

参数

VIH

VIL

VIH ( PWDN)

VIL( PWDN)

VOH

VOL

IIH

IIL

外置时钟工作频率范围(1)

串口时钟工作频率范围(2)

(1)芯片工作时钟频率

(2)串口通信时钟SCLK的频率

DocID20120709 Rev1

7/20

www.chipsea.com

�

CS1231

电气特性

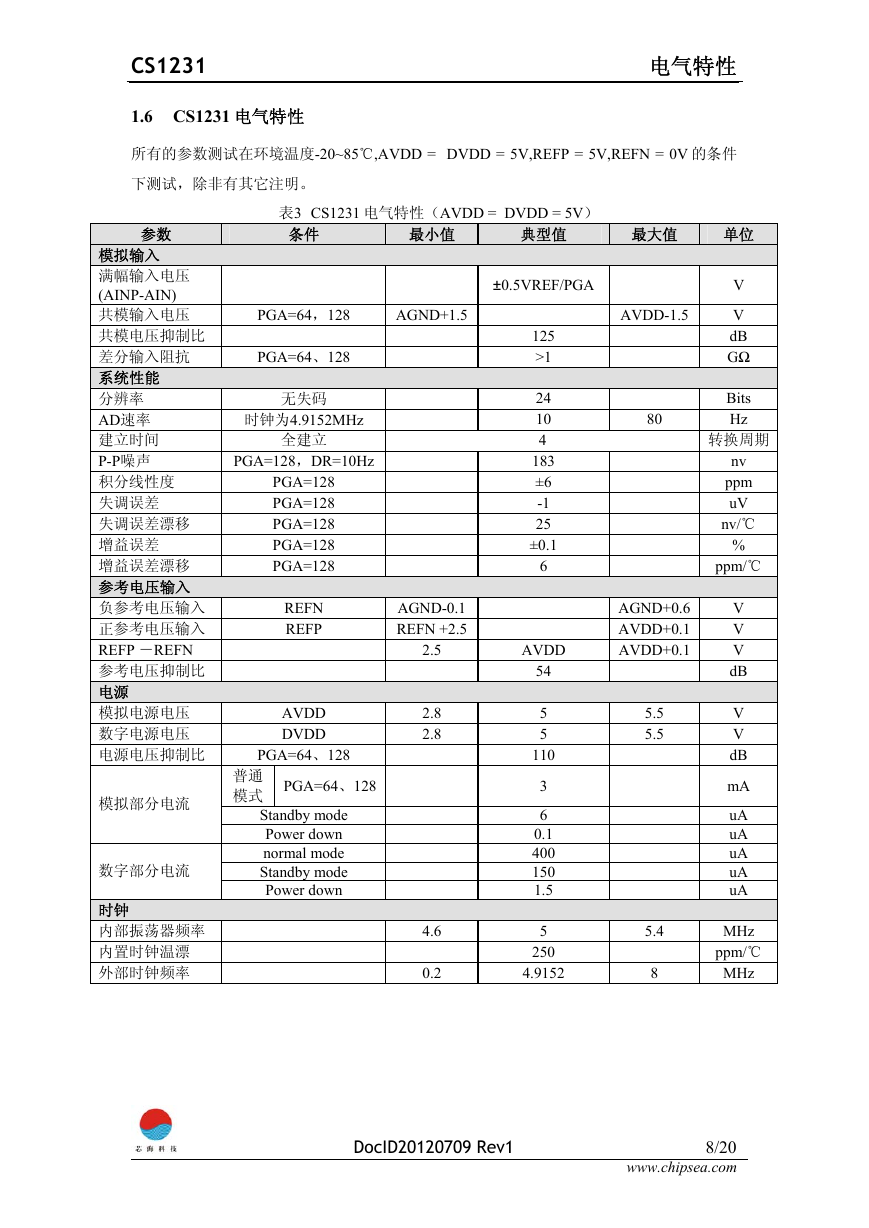

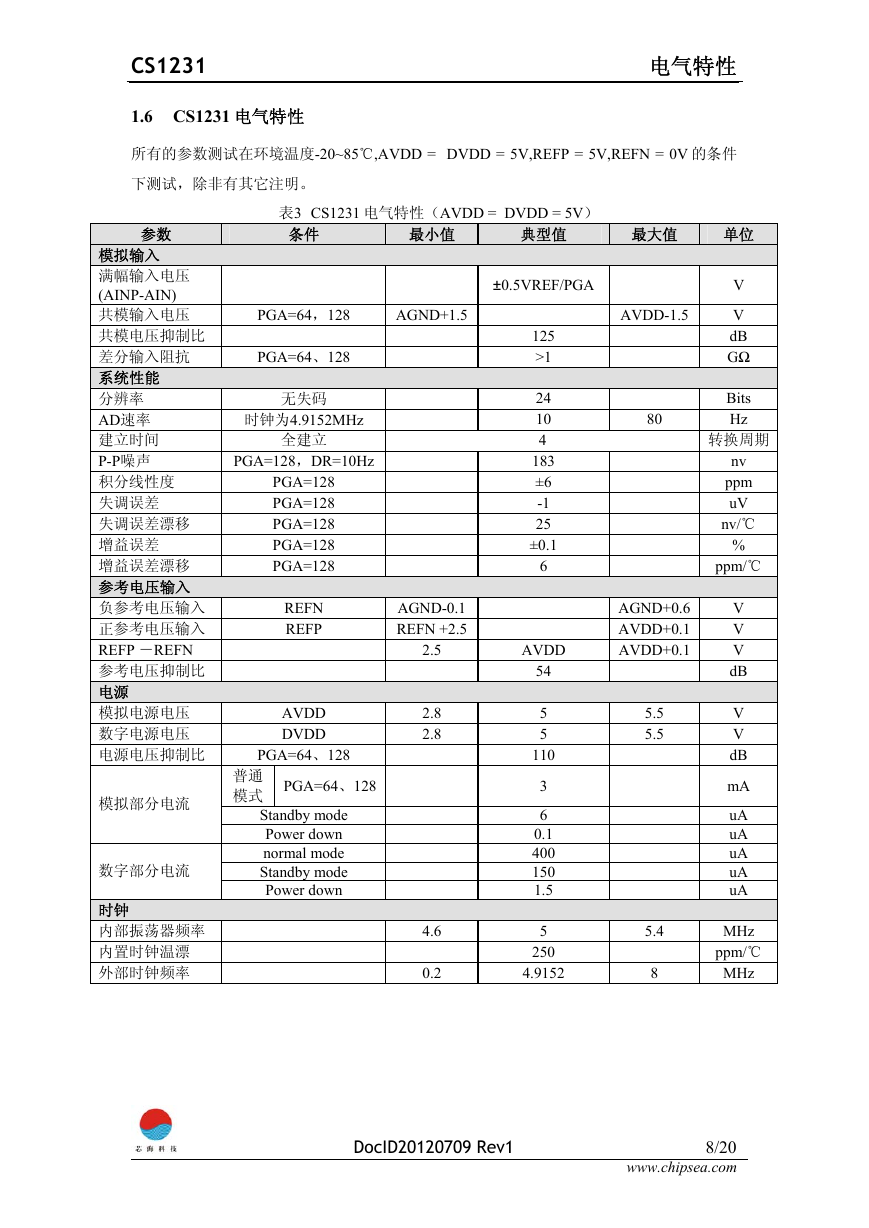

1.6 CS1231 电气特性

所有的参数测试在环境温度-20~85℃,AVDD = DVDD = 5V,REFP = 5V,REFN = 0V 的条件

下测试,除非有其它注明。

参数

模拟输入

满幅输入电压

(AINP-AIN)

共模输入电压

共模电压抑制比

差分输入阻抗

系统性能

分辨率

AD速率

建立时间

P-P噪声

积分线性度

失调误差

失调误差漂移

增益误差

增益误差漂移

参考电压输入

负参考电压输入

正参考电压输入

REFP -REFN

参考电压抑制比

电源

模拟电源电压

数字电源电压

电源电压抑制比

模拟部分电流

数字部分电流

时钟

内部振荡器频率

内置时钟温漂

外部时钟频率

表3 CS1231 电气特性(AVDD = DVDD = 5V)

条件

最小值

典型值

最大值

单位

±0.5VREF/PGA

PGA=64,128

AGND+1.5

PGA=64、128

无失码

时钟为4.9152MHz

全建立

PGA=128,DR=10Hz

PGA=128

PGA=128

PGA=128

PGA=128

PGA=128

REFN

REFP

AVDD

DVDD

PGA=64、128

普通

模式

PGA=64、128

Standby mode

Power down

normal mode

Standby mode

Power down

AGND-0.1

REFN +2.5

2.5

2.8

2.8

4.6

0.2

125

>1

24

10

4

183

±6

-1

25

±0.1

6

AVDD

54

5

5

110

3

6

0.1

400

150

1.5

5

250

4.9152

AVDD-1.5

80

AGND+0.6

AVDD+0.1

AVDD+0.1

5.5

5.5

5.4

8

V

V

dB

GΩ

Bits

Hz

转换周期

nv

ppm

uV

nv/℃

%

ppm/℃

V

V

V

dB

V

V

dB

mA

uA

uA

uA

uA

uA

MHz

ppm/℃

MHz

DocID20120709 Rev1

8/20

www.chipsea.com

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc