//MCBSP 配置,28335 包含两个 MCBSP 通道

void InitMcbsp(void)

{

InitMcbspaGpio();

InitMcbspbGpio();

InitMcbspa_DMA();

InitMcbspb_DMA();

}

void InitMcbspa_DMA(void)//MSP-DMA

{

McbspaRegs.SPCR2.all=0x0000;

// Reset FS generator, sample rate generator &

transmitter

McbspaRegs.SPCR1.all=0x0000;

McbspaRegs.MFFINT.all=0x0;

// Reset Receiver, Right justify word

// Disable all interrupts

McbspaRegs.SPCR1.bit.DLB = 0;

// Enable DLB mode. Comment out for non-DLB mode.

是否内部连接DX与DR

McbspaRegs.SPCR1.bit.CLKSTP = 2;

//使能时钟停止模式

McbspaRegs.RCR2.all=0x0;

// Single-phase frame, 1 word/frame, No

companding

(Receive)

McbspaRegs.RCR1.all=0x0;

McbspaRegs.XCR2.all=0x0;

// Single-phase frame, 1 word/frame, No

companding

(Transmit)

McbspaRegs.XCR1.all=0x0;

McbspaRegs.PCR.bit.FSXM = 1;

McbspaRegs.PCR.bit.FSRM = 1;

// =0选择外部帧同步,=1选择内部帧同步信号

// =0选择外部帧同步,=1选择内部帧同步信号

McbspaRegs.RCR2.bit.RFIG = 1;

McbspaRegs.XCR2.bit.XFIG = 1;

//=1忽略之后的同步信号

//=1忽略之后的同步信号

McbspaRegs.RCR1.bit.RFRLEN1 = 0; //帧长度=X+1

McbspaRegs.RCR2.bit.RDATDLY=0;

//延时接收=0不延时,=1延时一个CLK =2延时2个

CLK

McbspaRegs.PCR.bit.CLKXM = 1;

McbspaRegs.PCR.bit.CLKRM = 0;

//=0输入时钟由外部时钟驱动,

//=0输入时钟由外部时钟驱动,

McbspaRegs.PCR.bit.CLKRP =1;

//=0时钟下降沿接收数据。=1时钟上升沿接收数据,

�

McbspaRegs.PCR.bit.CLKXP =0;

//=0时钟上升沿发送数据。=1时钟下降沿发送数据,

McbspaRegs.PCR.bit.FSXP =1;

//=1帧同步脉冲FSX为低电平有效。

McbspaRegs.SRGR2.bit.CLKSM = 1;

// CLKSM=1 (If SCLKME=0, i/p clock to SRG is

LSPCLK),=1表示MCBSP时钟由CPU提供

McbspaRegs.SRGR1.bit.CLKGDV = 124;

// CLKG frequency = LSPCLK/(CLKGDV+1),时

钟设置,LSPCLK=37.5MHZ,这个需要与用户沟通进行统一时钟,来确定FPER值

McbspaRegs.SRGR2.bit.FSGM = 0;

// Initialize McBSP Data Length

InitMcbspa16bit();

//Enable Sample rate generator

McbspaRegs.SPCR2.bit.GRST=1; // 采样率时钟发生器复位停止

delay_loop();

McbspaRegs.SPCR2.bit.XRST=1; // Release TX from Reset

McbspaRegs.SPCR1.bit.RRST=1; // Release RX from Reset

delay_loop();

McbspaRegs.SPCR2.bit.FRST=1; // Frame Sync Generator reset

// Wait at least 2 SRG clock cycles

}

void InitMcbspb_DMA(void)//MSP-DMA//时钟停止模式

{

McbspbRegs.SPCR2.all=0x0000;

// Reset FS generator, sample rate generator &

transmitter

McbspbRegs.SPCR1.all=0x0000;

McbspbRegs.MFFINT.all=0x0;

// Reset Receiver, Right justify word

// Disable all interrupts

McbspbRegs.SPCR1.bit.DLB = 0;

// Enable DLB mode. Comment out for non-DLB mode.

是否内部连接DX与DR

McbspbRegs.SPCR1.bit.CLKSTP = 2;

//使能时钟停止模式

McbspbRegs.RCR2.all=0x0;

// Single-phase frame, 1 word/frame, No

companding

(Receive)

McbspbRegs.RCR1.all=0x0;

McbspbRegs.XCR2.all=0x0;

// Single-phase frame, 1 word/frame, No

companding

(Transmit)

McbspbRegs.XCR1.all=0x0;

McbspbRegs.PCR.bit.FSXM = 1;

external source

McbspbRegs.PCR.bit.FSRM = 1;

McbspbRegs.RCR2.bit.RFIG = 1;

McbspbRegs.XCR2.bit.XFIG = 1;

// FSX generated internally, FSR derived from an

�

McbspbRegs.PCR.bit.CLKXM = 1;

// CLKX generated internally, CLKR derived from

an external source

McbspbRegs.PCR.bit.CLKRM = 0;

McbspbRegs.SRGR2.bit.CLKSM = 1;

LSPCLK),=1表示MCBSP时钟由CPU提供

//输入时钟由外部时钟驱动

// CLKSM=1 (If SCLKME=0, i/p clock to SRG is

McbspbRegs.SRGR2.bit.FPER = 15;

McbspbRegs.SRGR1.bit.FWID = 0;

McbspbRegs.SRGR1.bit.CLKGDV = 14; // CLKG frequency = LSPCLK/(CLKGDV+1),时钟设置,

// Frame Width = 1 CLKG period,帧同步脉冲宽度

// FPER = 32 CLKG periods,帧同步信号间隔

LSPCLK=37.5MHZ//2.5M

McbspbRegs.SRGR2.bit.FSGM = 0;

// Initialize McBSP Data Length

InitMcbspb8bit();

//Enable Sample rate generator

McbspbRegs.SPCR2.bit.GRST=1; // 采样率时钟发生器复位停止

delay_loop();

McbspbRegs.SPCR2.bit.XRST=1; // Release TX from Reset

McbspbRegs.SPCR1.bit.RRST=1; // Release RX from Reset

delay_loop();

McbspbRegs.SPCR2.bit.FRST=1; // Frame Sync Generator reset

// Wait at least 2 SRG clock cycles

}

//#endif // end DSP28_MCBSPB

void Init_Dma_McBSPB(Uint16 data1[],Uint16 data2[],Uint16 data3[],Uint16

number_t,Uint16 number_r,Uint16 number_ta)

{

// Only 1 NOP needed per Design

EALLOW;

DmaRegs.DMACTRL.bit.HARDRESET = 1;

asm(" NOP");

DmaRegs.CH1.MODE.bit.CHINTE = 0;//禁止中断

// Channel 1, McBSPB transmit

DmaRegs.CH1.BURST_SIZE.all = 0;

DmaRegs.CH1.SRC_BURST_STEP = 0;

DmaRegs.CH1.DST_BURST_STEP = 0;

DmaRegs.CH1.TRANSFER_SIZE = number_t-1;

// 1 word/burst

// no effect when using 1 word/burst

// no effect when using 1 word/burst

// Interrupt every frame (127

bursts/transfer)

DmaRegs.CH1.SRC_TRANSFER_STEP = 1;

// Move to next word in buffer after each word

in a burst

DmaRegs.CH1.DST_TRANSFER_STEP = 0;

DmaRegs.CH1.SRC_ADDR_SHADOW = (Uint32) &data1[0];

// Don't move destination address

// Start address =

buffer

DmaRegs.CH1.SRC_BEG_ADDR_SHADOW = (Uint32) &data1[0];

// Not needed unless

using wrap function

DmaRegs.CH1.DST_ADDR_SHADOW = (Uint32) &McbspbRegs.DXR1.all;

// Start

�

address = McBSPA DXR

DmaRegs.CH1.DST_BEG_ADDR_SHADOW = (Uint32) &McbspbRegs.DXR1.all;

// Not

needed unless using wrap function

DmaRegs.CH1.CONTROL.bit.PERINTCLR = 1;// Clear peripheral interrupt event flag

DmaRegs.CH1.CONTROL.bit.SYNCCLR = 1;

DmaRegs.CH1.CONTROL.bit.ERRCLR = 1;

DmaRegs.CH1.DST_WRAP_SIZE = 0xFFFF;

// Put to maximum - don't want

// Clear sync flag

// Clear sync error flag

destination wrap

DmaRegs.CH1.SRC_WRAP_SIZE = 0xFFFF;

// Put to maximum - don't want

source wrap

DmaRegs.CH1.MODE.bit.SYNCE = 0;

DmaRegs.CH1.MODE.bit.SYNCSEL = 0;

DmaRegs.CH1.MODE.bit.CHINTE = 0;

DmaRegs.CH1.MODE.bit.CHINTMODE = 1;

DmaRegs.CH1.MODE.bit.PERINTE = 1;

DmaRegs.CH1.MODE.bit.PERINTSEL = 16;

// No sync signal

// No sync signal

// Enable channel interrupt

// Interrupt at end of transfer

// =1Enable peripheral interrupt event

// Peripheral interrupt select = McBSP

MXSYNCB

DmaRegs.CH1.CONTROL.bit.PERINTCLR = 1;

// Clear any spurious interrupt flags

// Channel 2, McBSPA Receive

DmaRegs.CH2.MODE.bit.CHINTE = 0;

DmaRegs.CH2.BURST_SIZE.all = 0;

DmaRegs.CH2.SRC_BURST_STEP = 0;

DmaRegs.CH2.DST_BURST_STEP = 0;

DmaRegs.CH2.TRANSFER_SIZE = number_r-1;

DmaRegs.CH2.SRC_TRANSFER_STEP = 0;

DmaRegs.CH2.DST_TRANSFER_STEP = 1;

// 1 word/burst

// no effect when using 1 word/burst

// no effect when using 1 word/burst

// Interrupt every 127 bursts/transfer

// Don't move source address

// Move to next word in buffer after each word

in a burst

DmaRegs.CH2.SRC_ADDR_SHADOW = (Uint32) &McbspaRegs.DRR1.all;

// Start

address = McBSPA DRR

DmaRegs.CH2.SRC_BEG_ADDR_SHADOW = (Uint32) &McbspaRegs.DRR1.all;

// Not

needed unless using wrap function

DmaRegs.CH2.DST_ADDR_SHADOW = (Uint32) &data2[0];

// Start address = Receive

buffer (for McBSP-A)

DmaRegs.CH2.DST_BEG_ADDR_SHADOW = (Uint32) &data2[0];

// Not needed unless using

wrap function

DmaRegs.CH2.CONTROL.bit.PERINTCLR = 1;

// Clear peripheral interrupt event

flag

DmaRegs.CH2.CONTROL.bit.SYNCCLR = 1;

DmaRegs.CH2.CONTROL.bit.ERRCLR = 1;

DmaRegs.CH2.DST_WRAP_SIZE = 0xFFFF;

// Clear sync flag

// Clear sync error flag

// Put to maximum - don't want

destination wrap

DmaRegs.CH2.SRC_WRAP_SIZE = 0xFFFF;

// Put to maximum - don't want

source wrap

�

DmaRegs.CH2.MODE.bit.CHINTE = 0;

DmaRegs.CH2.MODE.bit.CHINTMODE = 1;

DmaRegs.CH2.MODE.bit.PERINTE = 1;

DmaRegs.CH2.MODE.bit.PERINTSEL = 15;

// Enable channel interrupt

// Interrupt at end of transfer

// Enable peripheral interrupt event

// Peripheral interrupt select = McBSP

MRSYNCA

DmaRegs.CH2.CONTROL.bit.PERINTCLR = 1;

// Clear any spurious interrupt flags

// Channel 3, McBSPA TX

DmaRegs.CH3.MODE.bit.CHINTE = 0;//禁止中断

// Channel 3, McBSPA transmit

DmaRegs.CH3.BURST_SIZE.all = 0;

DmaRegs.CH3.SRC_BURST_STEP = 0;

DmaRegs.CH3.DST_BURST_STEP = 0;

DmaRegs.CH3.TRANSFER_SIZE = number_ta-1;

// 1 word/burst

// no effect when using 1 word/burst

// no effect when using 1 word/burst

// Interrupt every frame (127

bursts/transfer)

DmaRegs.CH3.SRC_TRANSFER_STEP = 1;

// Move to next word in buffer after each word

in a burst

DmaRegs.CH3.DST_TRANSFER_STEP = 0;

DmaRegs.CH3.SRC_ADDR_SHADOW = (Uint32) &data3[0];

// Don't move destination address

// Start address =

buffer

DmaRegs.CH3.SRC_BEG_ADDR_SHADOW = (Uint32) &data3[0];

// Not needed unless

using wrap function

DmaRegs.CH3.DST_ADDR_SHADOW = (Uint32) &McbspaRegs.DXR1.all;

// Start

address = McBSPA DXR

DmaRegs.CH3.DST_BEG_ADDR_SHADOW = (Uint32) &McbspaRegs.DXR1.all;

// Not

needed unless using wrap function

DmaRegs.CH3.CONTROL.bit.PERINTCLR = 1;// Clear peripheral interrupt event flag

DmaRegs.CH3.CONTROL.bit.SYNCCLR = 1;

DmaRegs.CH3.CONTROL.bit.ERRCLR = 1;

DmaRegs.CH3.DST_WRAP_SIZE = 0xFFFF;

// Put to maximum - don't want

// Clear sync flag

// Clear sync error flag

destination wrap

DmaRegs.CH3.SRC_WRAP_SIZE = 0xFFFF;

// Put to maximum - don't want

source wrap

DmaRegs.CH3.MODE.bit.SYNCE = 0;

DmaRegs.CH3.MODE.bit.SYNCSEL = 0;

DmaRegs.CH3.MODE.bit.CHINTE = 0;

DmaRegs.CH3.MODE.bit.CHINTMODE = 1;

DmaRegs.CH3.MODE.bit.PERINTE = 1;

DmaRegs.CH3.MODE.bit.PERINTSEL = 14;

// No sync signal

// No sync signal

// Enable channel interrupt

// Interrupt at end of transfer

// =1Enable peripheral interrupt event

// Peripheral interrupt select = McBSPA

TX

}

DmaRegs.CH3.CONTROL.bit.PERINTCLR = 1;

EDIS;

// Clear any spurious interrupt flags

�

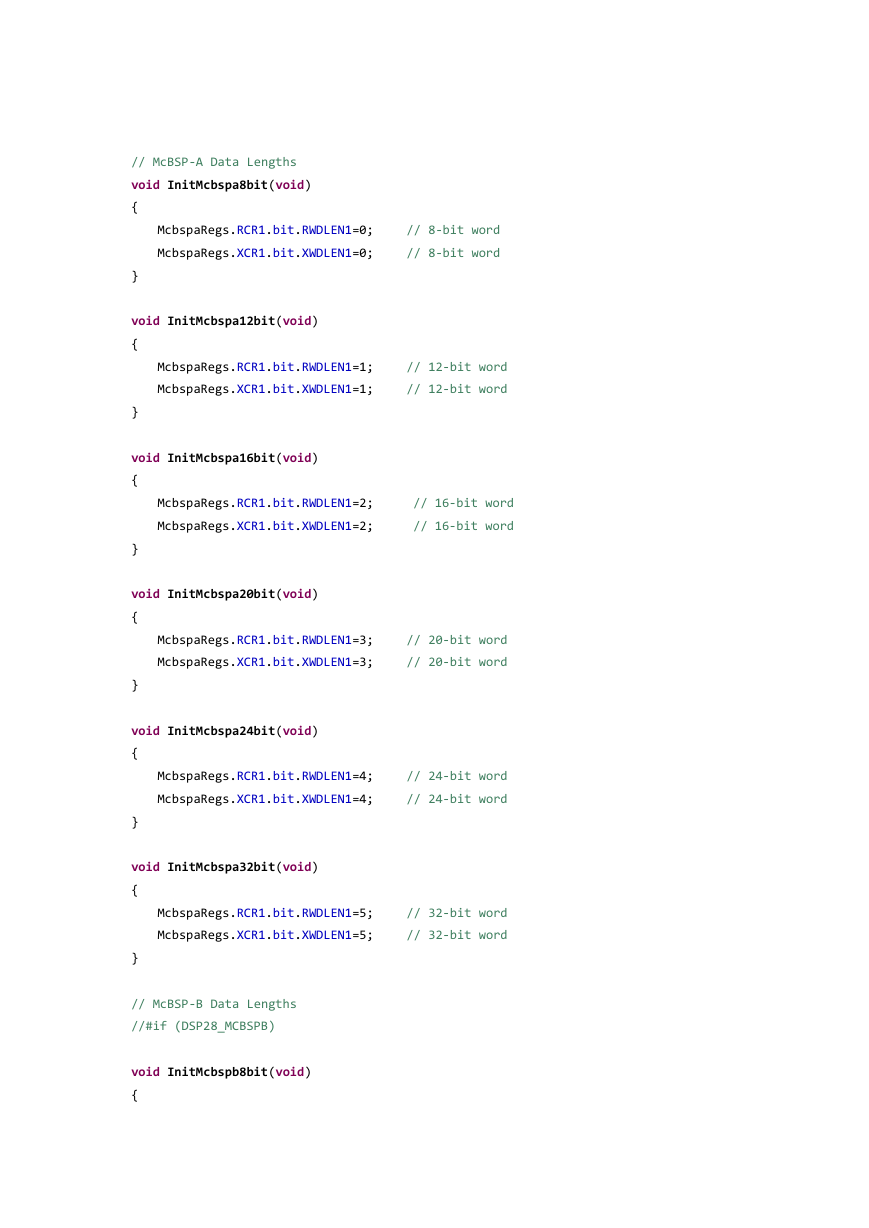

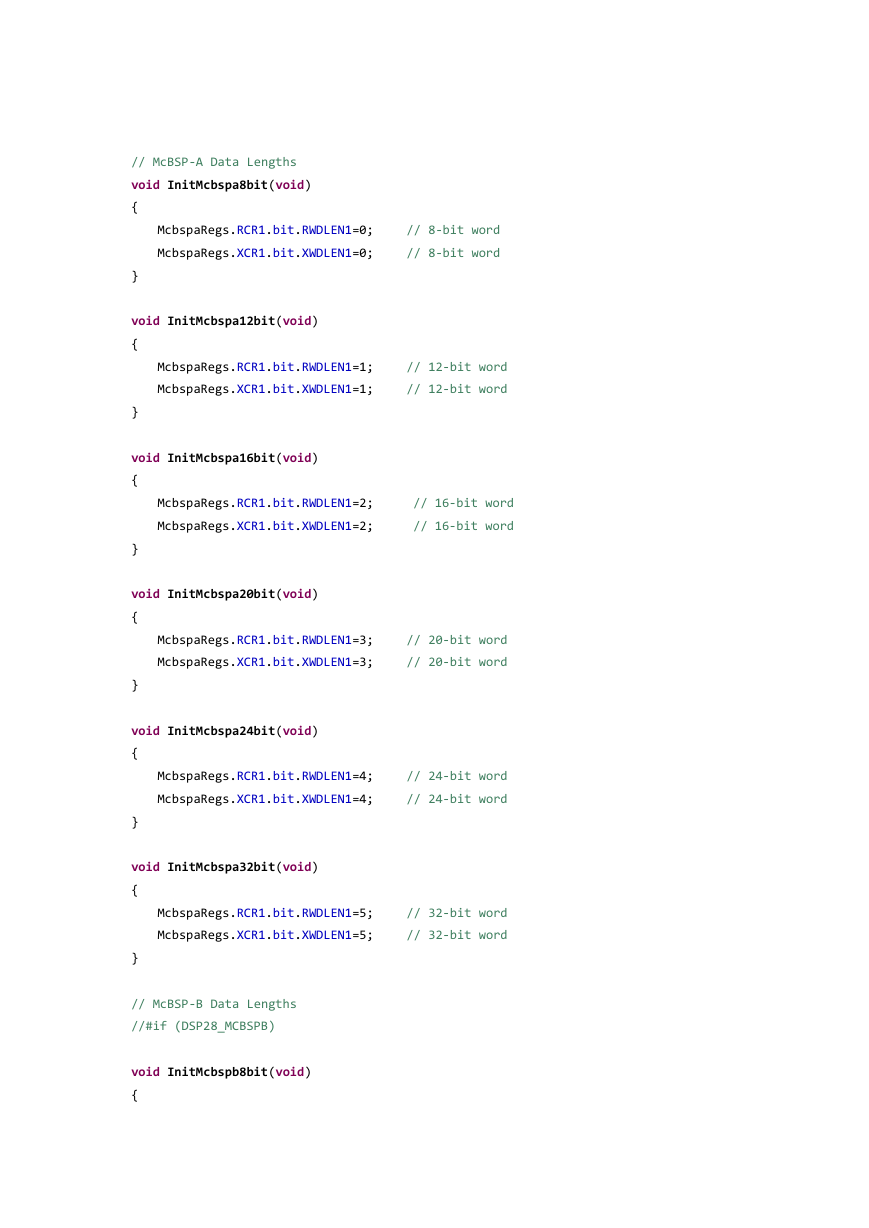

// McBSP-A Data Lengths

void InitMcbspa8bit(void)

{

McbspaRegs.RCR1.bit.RWDLEN1=0;

McbspaRegs.XCR1.bit.XWDLEN1=0;

// 8-bit word

// 8-bit word

}

void InitMcbspa12bit(void)

{

McbspaRegs.RCR1.bit.RWDLEN1=1;

McbspaRegs.XCR1.bit.XWDLEN1=1;

// 12-bit word

// 12-bit word

}

void InitMcbspa16bit(void)

{

McbspaRegs.RCR1.bit.RWDLEN1=2;

McbspaRegs.XCR1.bit.XWDLEN1=2;

// 16-bit word

// 16-bit word

}

void InitMcbspa20bit(void)

{

McbspaRegs.RCR1.bit.RWDLEN1=3;

McbspaRegs.XCR1.bit.XWDLEN1=3;

// 20-bit word

// 20-bit word

}

void InitMcbspa24bit(void)

{

McbspaRegs.RCR1.bit.RWDLEN1=4;

McbspaRegs.XCR1.bit.XWDLEN1=4;

// 24-bit word

// 24-bit word

}

void InitMcbspa32bit(void)

{

McbspaRegs.RCR1.bit.RWDLEN1=5;

McbspaRegs.XCR1.bit.XWDLEN1=5;

// 32-bit word

// 32-bit word

}

// McBSP-B Data Lengths

//#if (DSP28_MCBSPB)

void InitMcbspb8bit(void)

{

�

McbspbRegs.RCR1.bit.RWDLEN1=0;

McbspbRegs.XCR1.bit.XWDLEN1=0;

// 8-bit word

// 8-bit word

}

void InitMcbspb12bit(void)

{

McbspbRegs.RCR1.bit.RWDLEN1=1;

McbspbRegs.XCR1.bit.XWDLEN1=1;

// 12-bit word

// 12-bit word

}

void InitMcbspb16bit(void)

{

McbspbRegs.RCR1.bit.RWDLEN1=2;

McbspbRegs.XCR1.bit.XWDLEN1=2;

// 16-bit word

// 16-bit word

}

void InitMcbspb20bit(void)

{

McbspbRegs.RCR1.bit.RWDLEN1=3;

McbspbRegs.XCR1.bit.XWDLEN1=3;

// 20-bit word

// 20-bit word

}

void InitMcbspb24bit(void)

{

McbspbRegs.RCR1.bit.RWDLEN1=4;

McbspbRegs.XCR1.bit.XWDLEN1=4;

// 24-bit word

// 24-bit word

}

void InitMcbspb32bit(void)

{

McbspbRegs.RCR1.bit.RWDLEN1=5;

McbspbRegs.XCR1.bit.XWDLEN1=5;

// 32-bit word

// 32-bit word

}

//#endif //end DSP28_MCBSPB

void InitMcbspGpio(void)

{

InitMcbspaGpio();

#if DSP28_MCBSPB

InitMcbspbGpio();

#endif

// end DSP28_MCBSPB

}

�

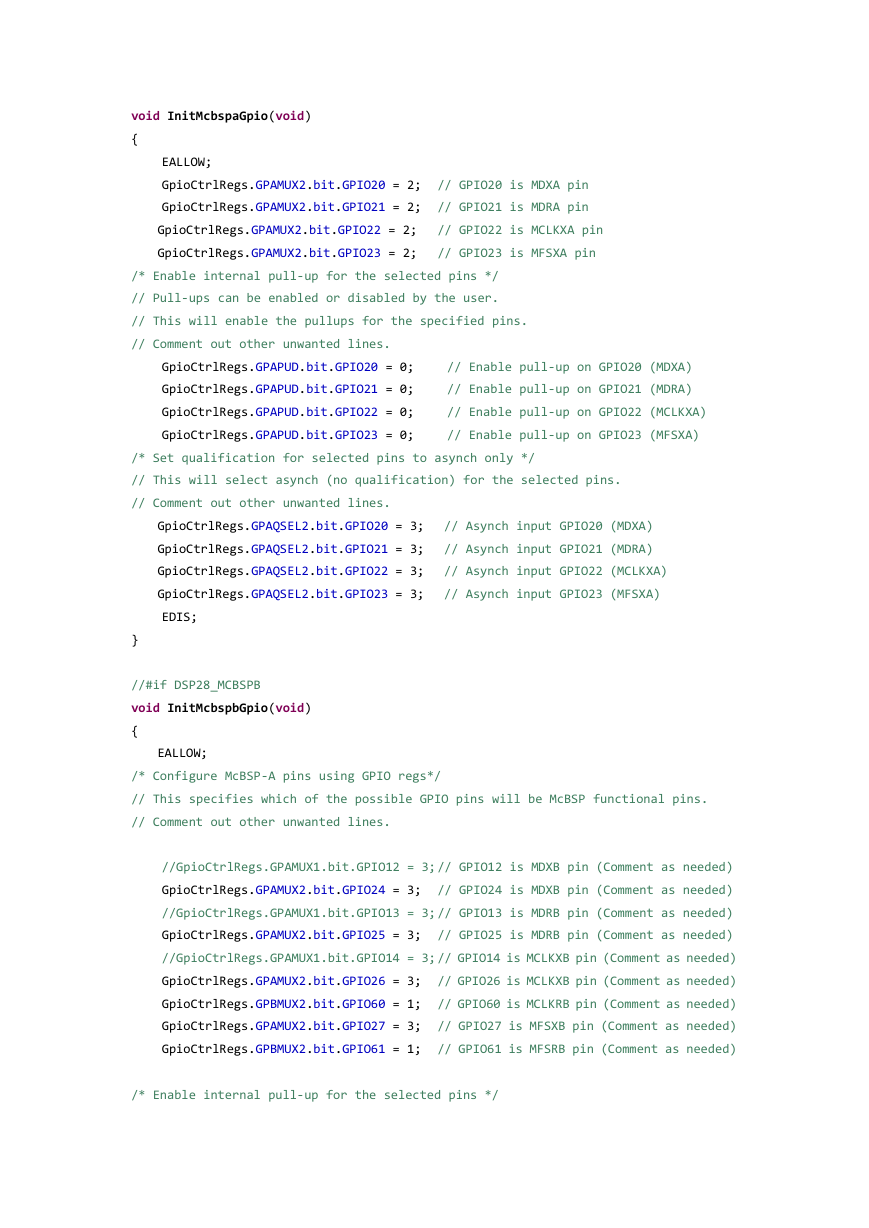

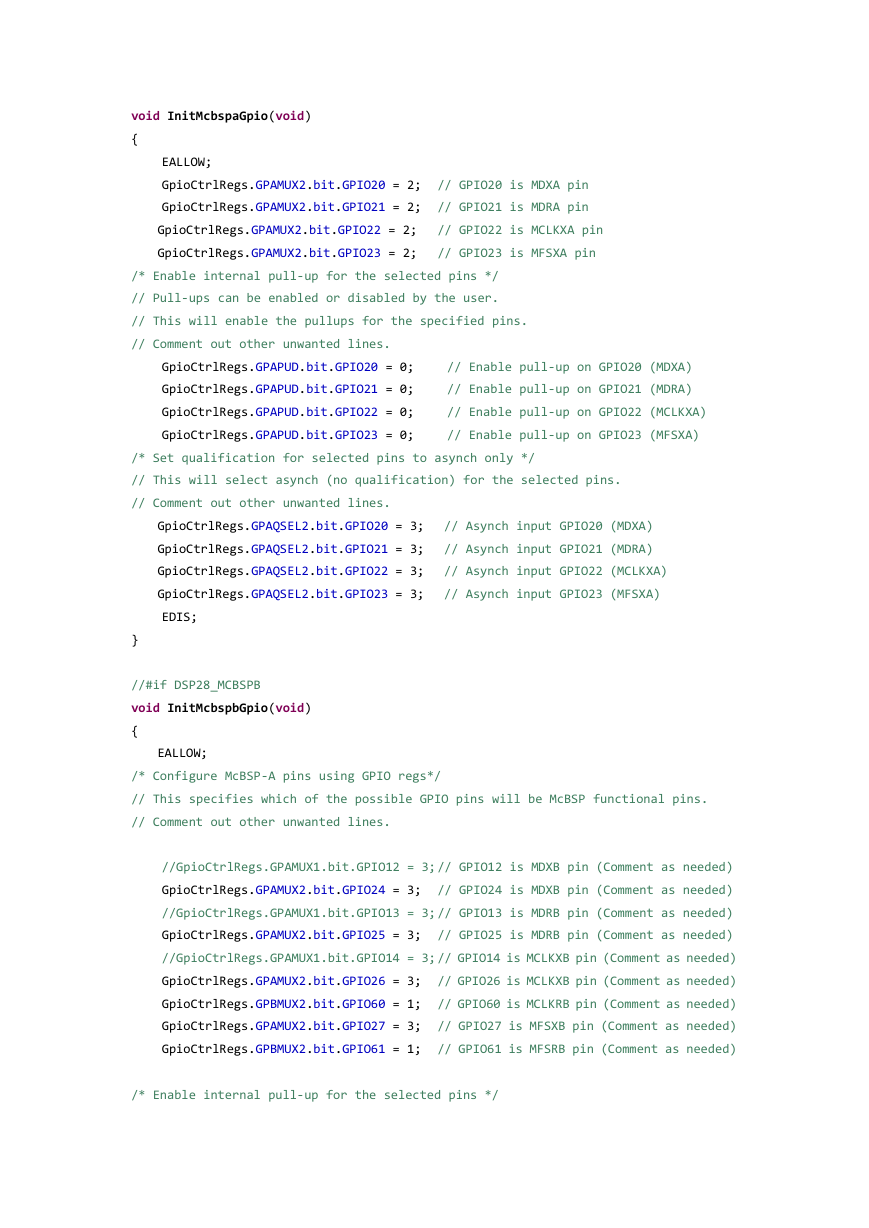

void InitMcbspaGpio(void)

{

EALLOW;

GpioCtrlRegs.GPAMUX2.bit.GPIO20 = 2;

GpioCtrlRegs.GPAMUX2.bit.GPIO21 = 2;

GpioCtrlRegs.GPAMUX2.bit.GPIO22 = 2;

GpioCtrlRegs.GPAMUX2.bit.GPIO23 = 2;

// GPIO20 is MDXA pin

// GPIO21 is MDRA pin

// GPIO22 is MCLKXA pin

// GPIO23 is MFSXA pin

/* Enable internal pull-up for the selected pins */

// Pull-ups can be enabled or disabled by the user.

// This will enable the pullups for the specified pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAPUD.bit.GPIO20 = 0;

GpioCtrlRegs.GPAPUD.bit.GPIO21 = 0;

GpioCtrlRegs.GPAPUD.bit.GPIO22 = 0;

GpioCtrlRegs.GPAPUD.bit.GPIO23 = 0;

// Enable pull-up on GPIO20 (MDXA)

// Enable pull-up on GPIO21 (MDRA)

// Enable pull-up on GPIO22 (MCLKXA)

// Enable pull-up on GPIO23 (MFSXA)

/* Set qualification for selected pins to asynch only */

// This will select asynch (no qualification) for the selected pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAQSEL2.bit.GPIO20 = 3;

GpioCtrlRegs.GPAQSEL2.bit.GPIO21 = 3;

GpioCtrlRegs.GPAQSEL2.bit.GPIO22 = 3;

GpioCtrlRegs.GPAQSEL2.bit.GPIO23 = 3;

EDIS;

// Asynch input GPIO20 (MDXA)

// Asynch input GPIO21 (MDRA)

// Asynch input GPIO22 (MCLKXA)

// Asynch input GPIO23 (MFSXA)

}

//#if DSP28_MCBSPB

void InitMcbspbGpio(void)

{

EALLOW;

/* Configure McBSP-A pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be McBSP functional pins.

// Comment out other unwanted lines.

//GpioCtrlRegs.GPAMUX1.bit.GPIO12 = 3;// GPIO12 is MDXB pin (Comment as needed)

GpioCtrlRegs.GPAMUX2.bit.GPIO24 = 3;

// GPIO24 is MDXB pin (Comment as needed)

//GpioCtrlRegs.GPAMUX1.bit.GPIO13 = 3;// GPIO13 is MDRB pin (Comment as needed)

GpioCtrlRegs.GPAMUX2.bit.GPIO25 = 3;

// GPIO25 is MDRB pin (Comment as needed)

//GpioCtrlRegs.GPAMUX1.bit.GPIO14 = 3;// GPIO14 is MCLKXB pin (Comment as needed)

GpioCtrlRegs.GPAMUX2.bit.GPIO26 = 3;

// GPIO26 is MCLKXB pin (Comment as needed)

// GPIO60 is MCLKRB pin (Comment as needed)

GpioCtrlRegs.GPBMUX2.bit.GPIO60 = 1;

// GPIO27 is MFSXB pin (Comment as needed)

GpioCtrlRegs.GPAMUX2.bit.GPIO27 = 3;

GpioCtrlRegs.GPBMUX2.bit.GPIO61 = 1;

// GPIO61 is MFSRB pin (Comment as needed)

/* Enable internal pull-up for the selected pins */

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc